Supply voltage tolerant phase-locked loop circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

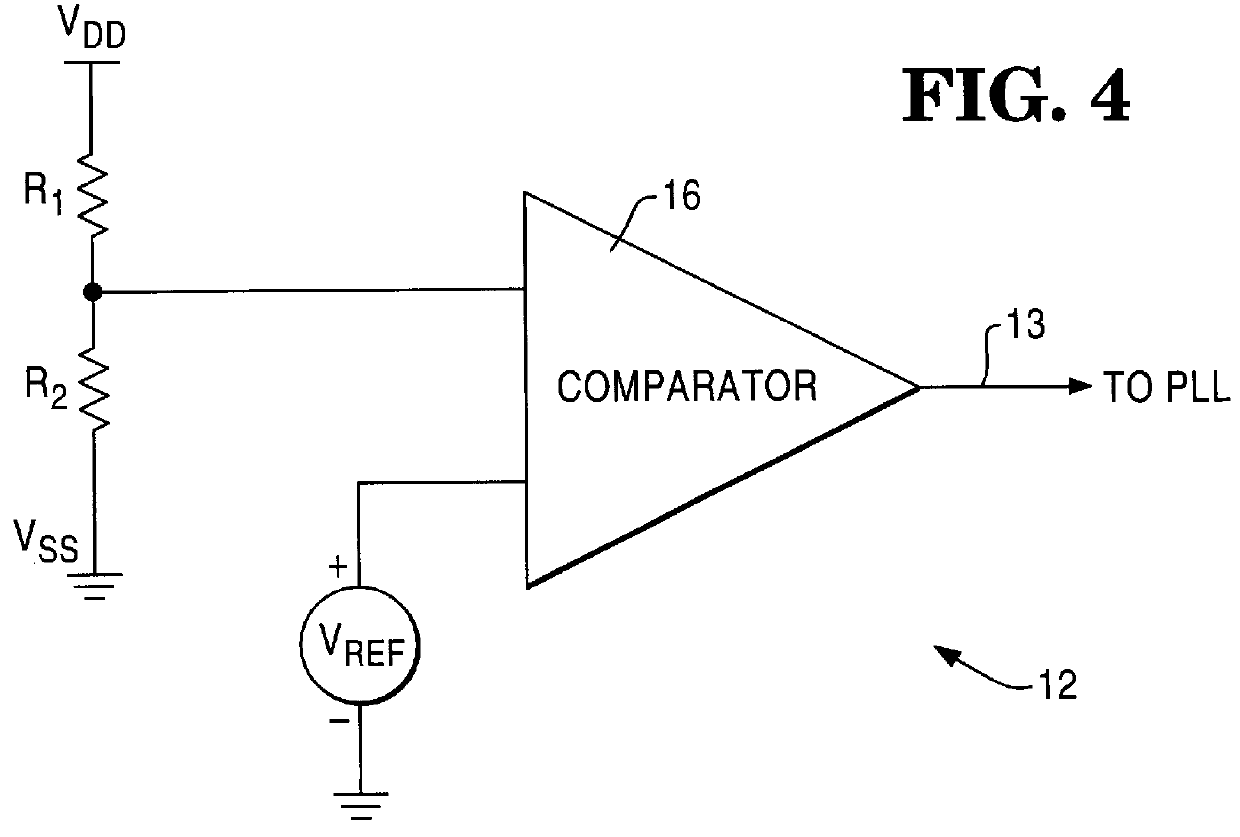

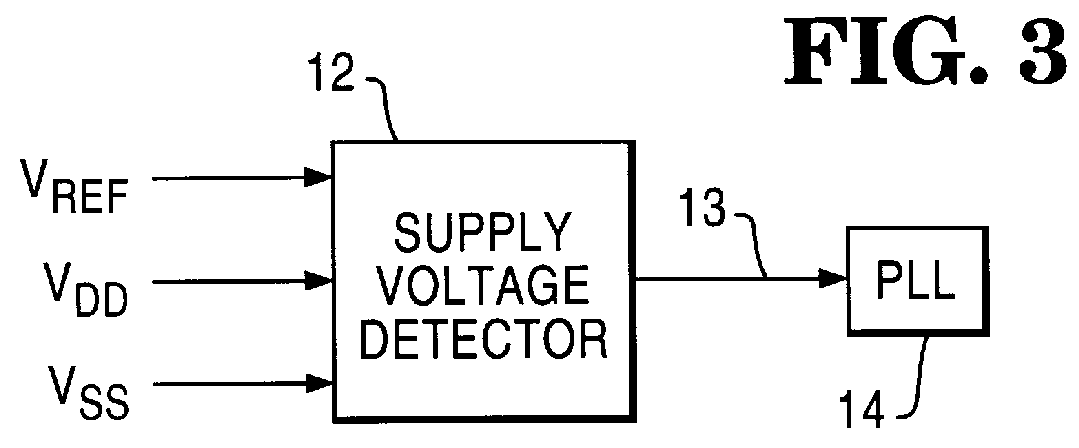

FIG. 3 shows how to adjust the frequency range of a PLL based on supply voltage. First, the power supply voltage level is detected by detector 12. The detector output 13 is coupled to the PLL 14. Supply voltage detector 12 operates by comparing the supply voltage VDD with a reference voltage VREF which is independent of the supply voltage. The reference voltage VREF can come from an external voltage regulator or be generated on-chip by a bandgap reference voltage source. Since the reference voltage VREF will generally be lower than the supply voltage VDD, the reference voltage cannot be compared directly with the supply voltage. Rather, the supply voltage is scaled and compared with the reference voltage. There are many possible ways to scale down the supply voltage. One way is to use a voltage divider as shown in FIG. 4. If all that is needed is to operate the PLL at 3.3 V and 5 V, a divide-by-two voltage divider R1 / R2 is used to scale the supply voltage VDD from 3.3 V to 1.65 V an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More