Regulating board of static var compensator based on floating point DSP and FPGA

A technology of static var compensation and floating point numbers, which is applied in the directions of reactive power adjustment/elimination/compensation, electrical variable adjustment, control/regulation system, etc., to achieve fast calculation speed, super strong resistance to strong electromagnetic interference, and high integration Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

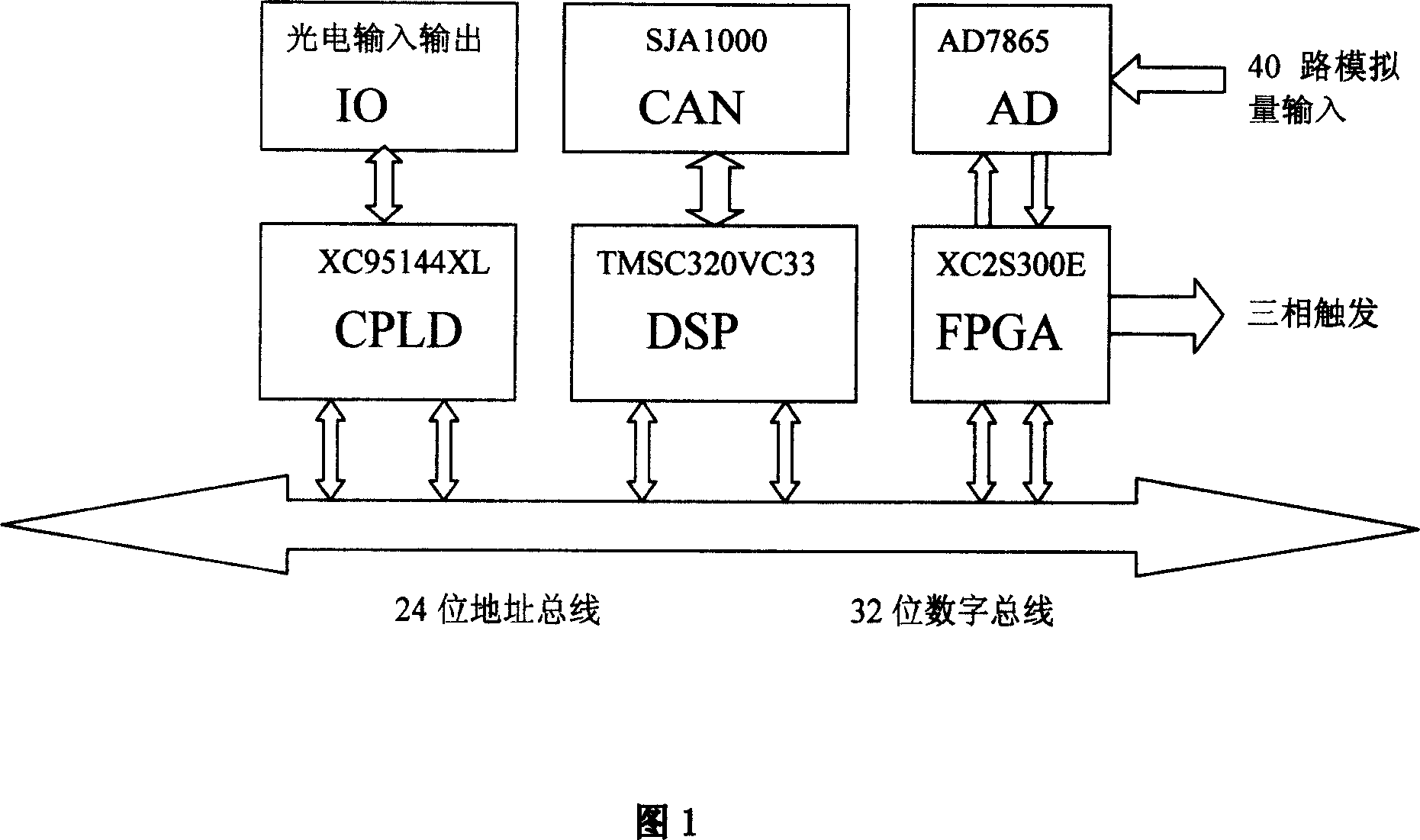

[0012] Referring to the accompanying drawings, a static var compensator regulating board is mainly composed of a 32-bit floating-point digital processing chip (DSP) and an ultra-large-scale field programmable logic gate array (FPGA). The regulating board circuit also includes 40-way 14-bit analog-to-digital conversion chips, digital phase-locked loop PLL, CAN controller and 8-way photoelectric isolation input and output circuits and other auxiliary external devices. All circuits are integrated on a pluggable 4-layer printed circuit board, so that the CPU bus does not go out of the circuit board.

[0013] The principle and function design of each circuit are as follows:

[0014] 1) The DSP circuit is TMS320VC33 floating-point DSP of American TI Company, including 8MBFLASH and 2MBRAM externally. The DSP includes a 24-bit address bus, a 32-bit digital bus, and a main frequency of 100MHz. The DSP is programmed in C language and calculates floating-point numbers. Its main function...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More