Patents

Literature

32 results about "Floating point dsp" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

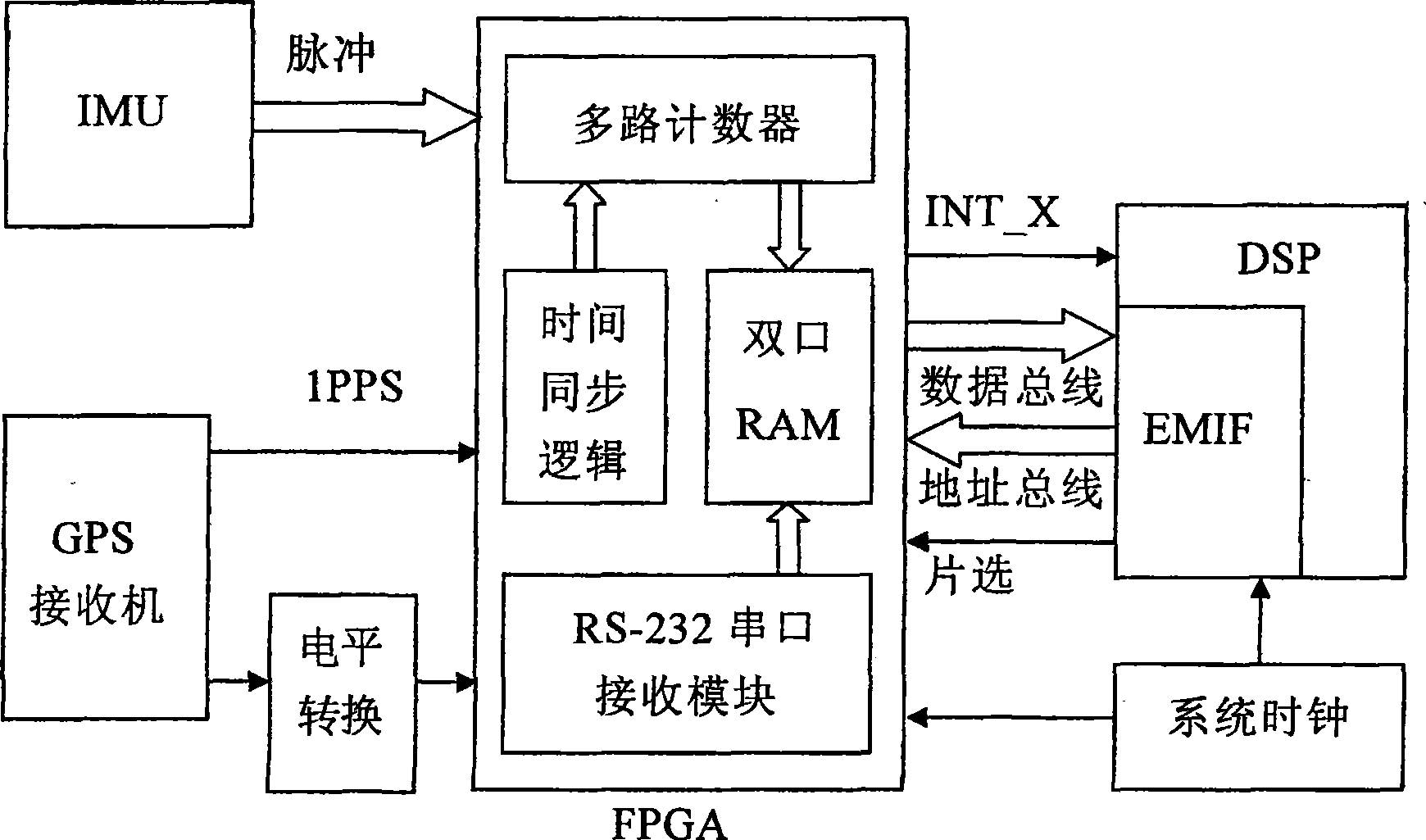

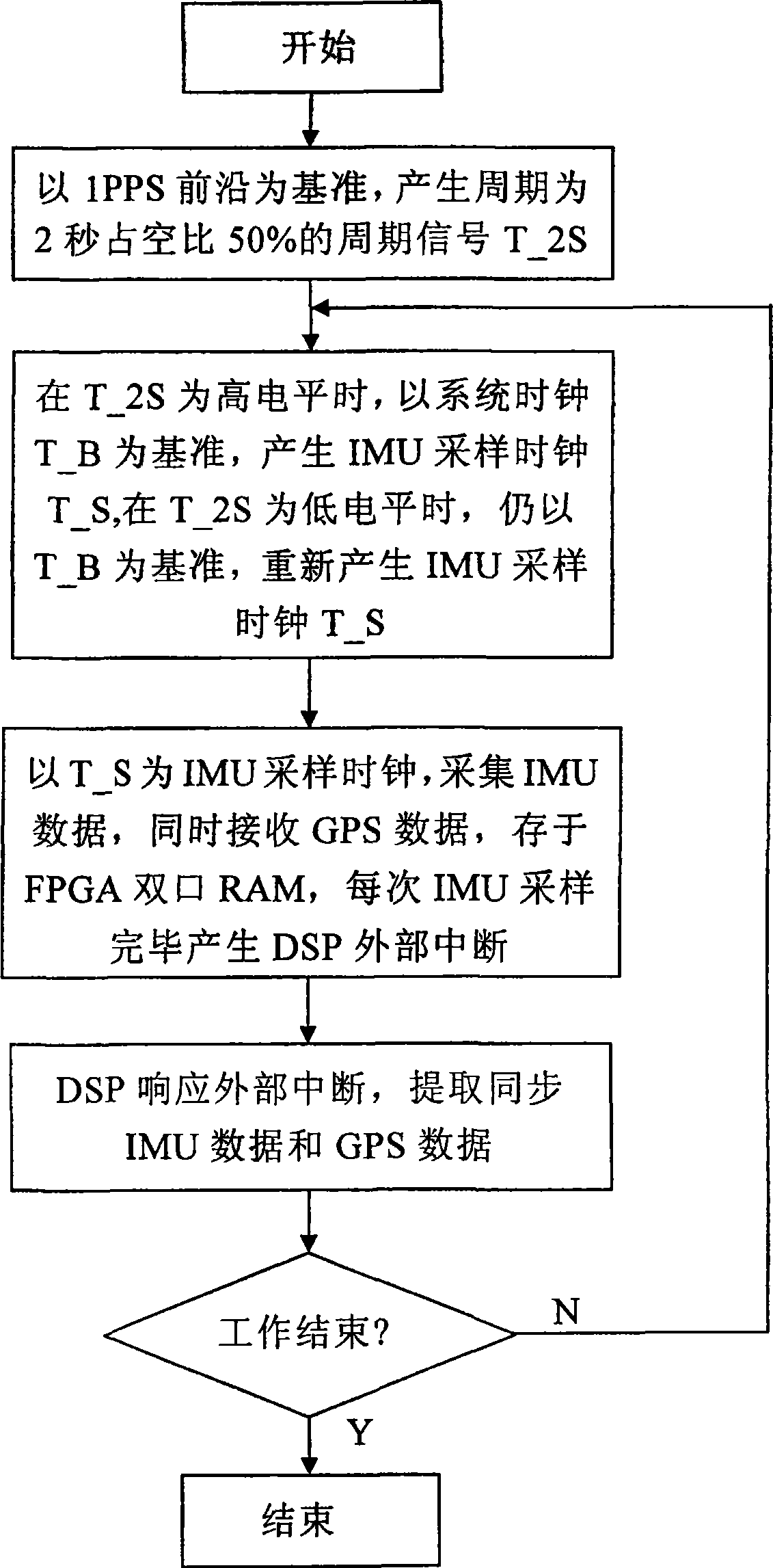

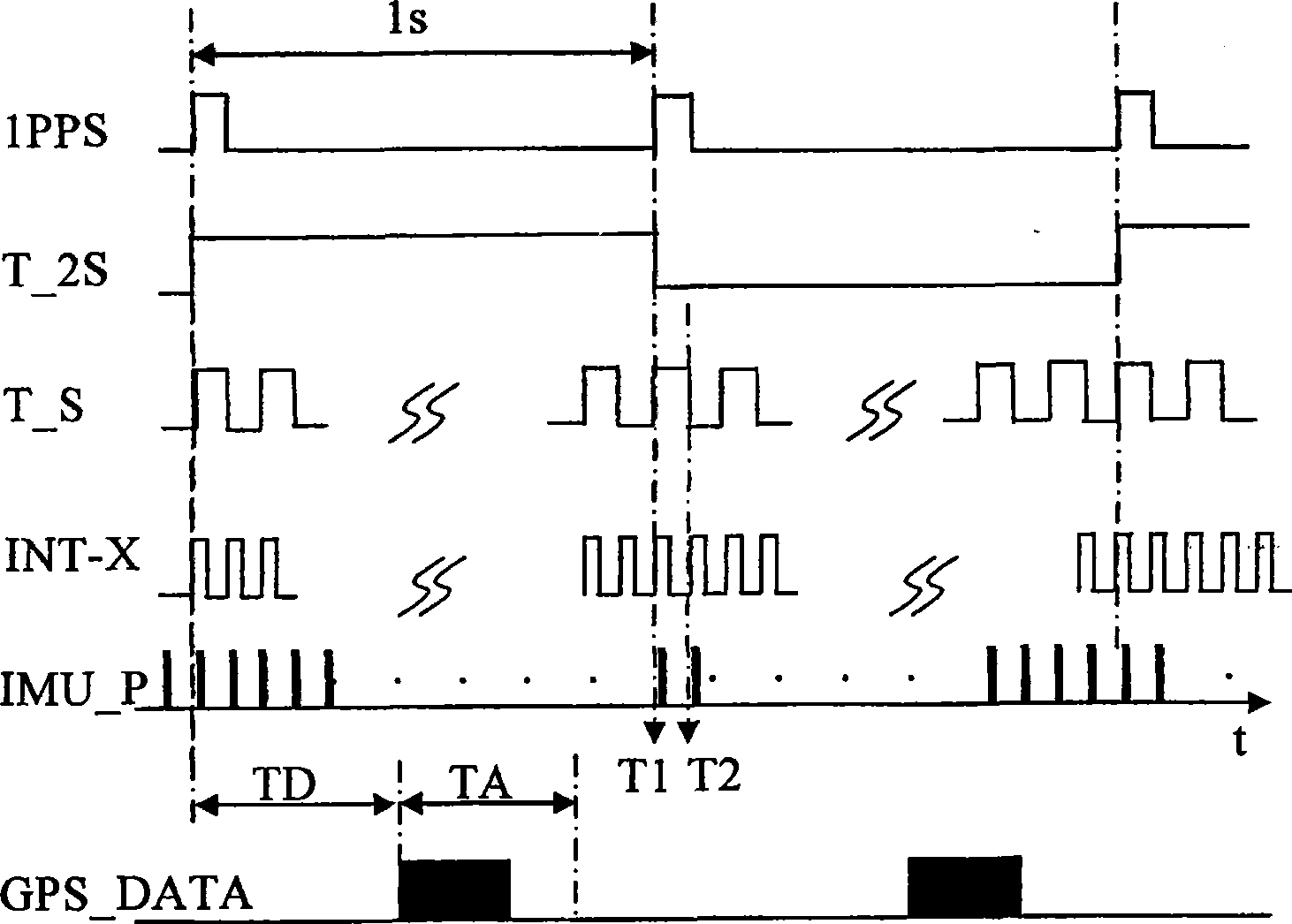

SDINS/GPS combined guidance system time synchronism and synchronous data extraction method

InactiveCN101105401AHardware time synchronizationCompact hardwareInstruments for road network navigationPulse automatic controlGuidance systemData acquisition

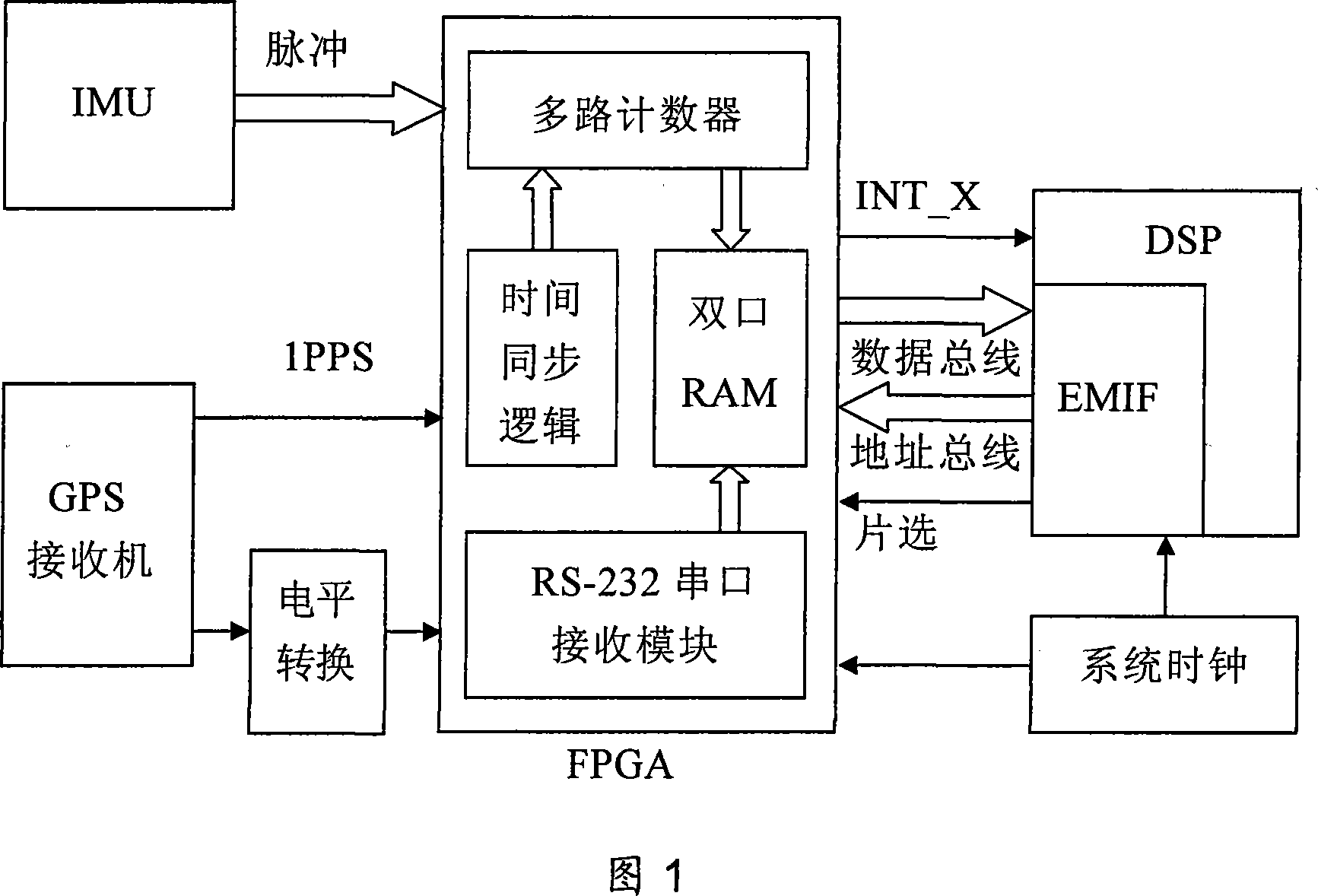

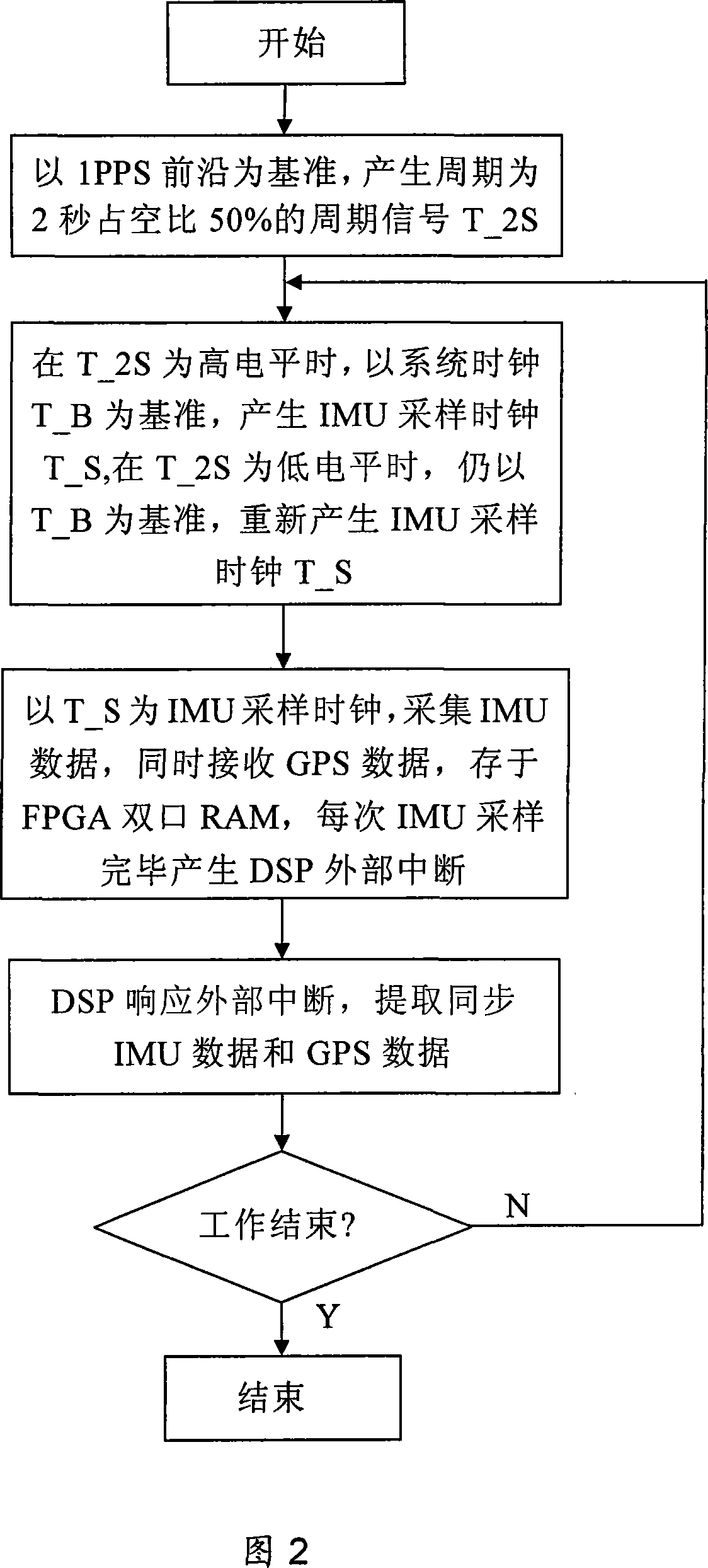

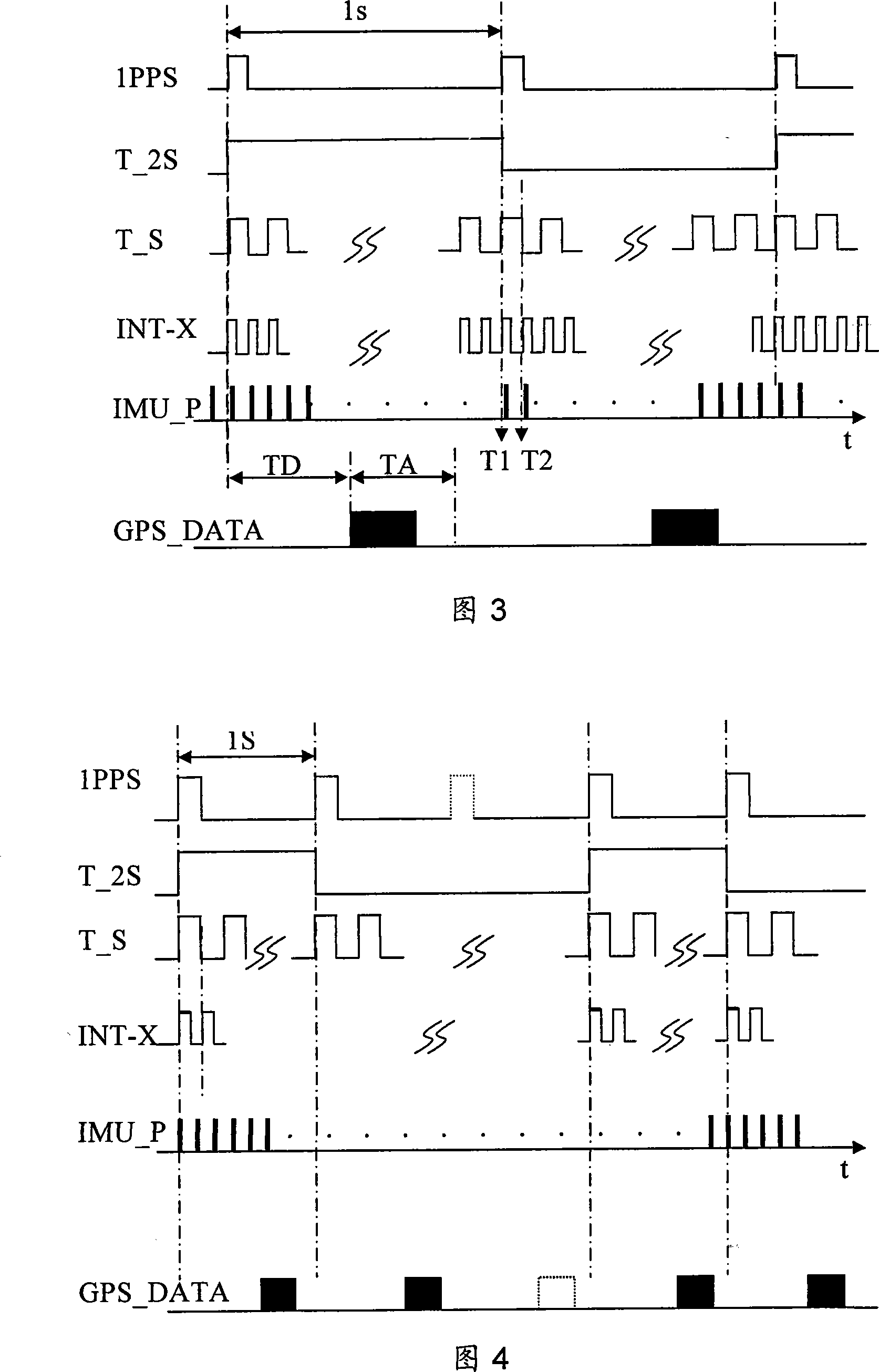

The invention relates to a SDINS / GPS integrated navigation system time synchronization method and synchronous data acquisition method. 1 PPS pulse of a GPS receiver is used as a reference to generate an IMU sampling clock, and the pulse signal outputted from the IMU is counted by a counter in the FPGA, so that IMP data sampling is synchronous with 1 PPS, and the synchronization of IMU data and GPS data is realized. GPS data is received through a serial port for realizing VHDL language. The floating point DSP responds the external interruption of the FPGA, reads the IMU data inside the FPGA, and acquires synchronous IMU data and reads GPS data in accordance with the IMU synchronization marks and GPS reading marks. The invention adopts hardware synchronization and time synchronization, leading to good stability. It can realize re-synchronization with 1 PPS, so as to provide high-precision synchronous data for integrated navigation computation and improve the overall performance of integrated navigation system. The DSP acquires synchronous data with interrupt mode and hardly occupies the DSP resource for computation, leading to good real-time performance.

Owner:BEIHANG UNIV

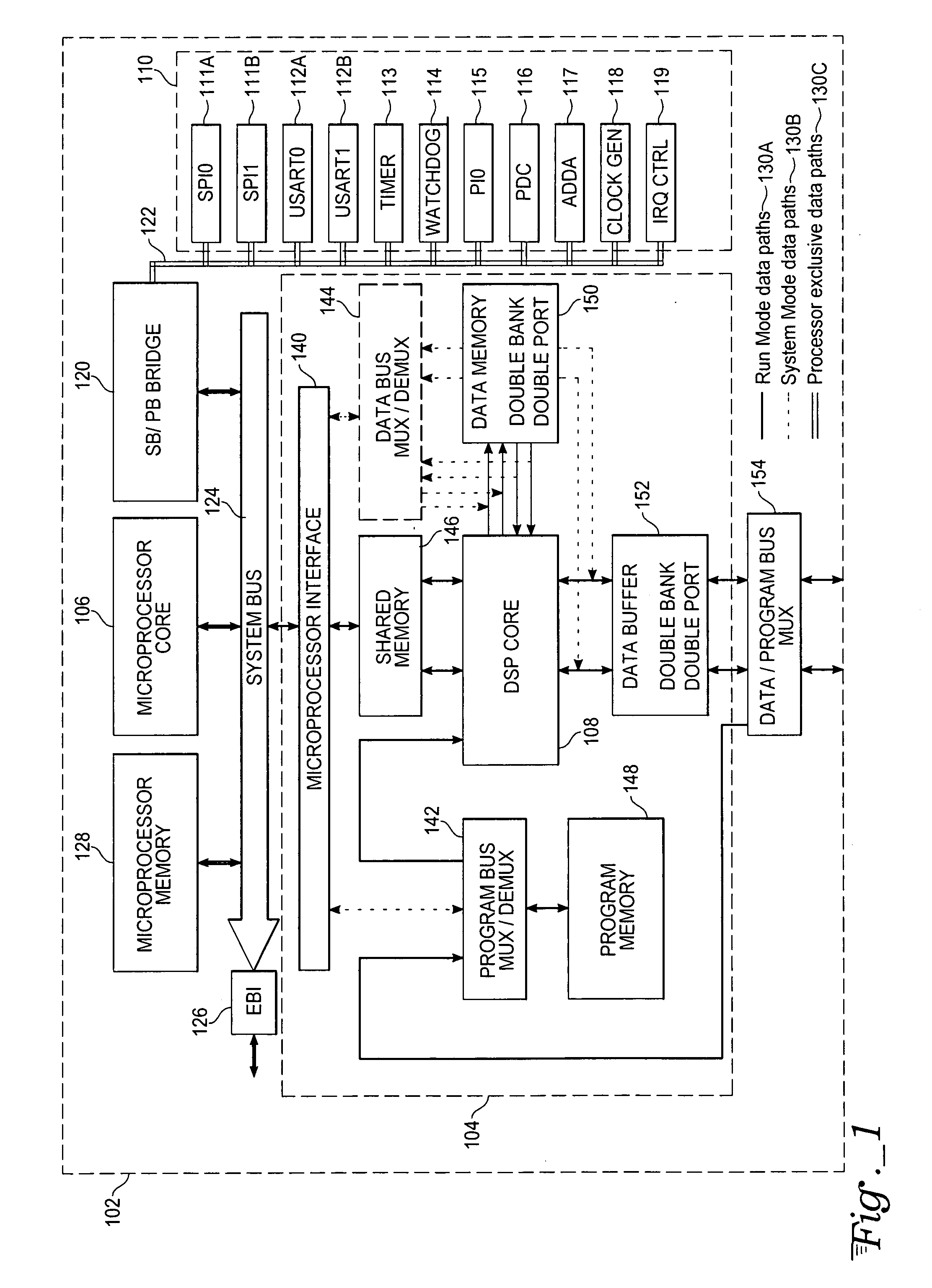

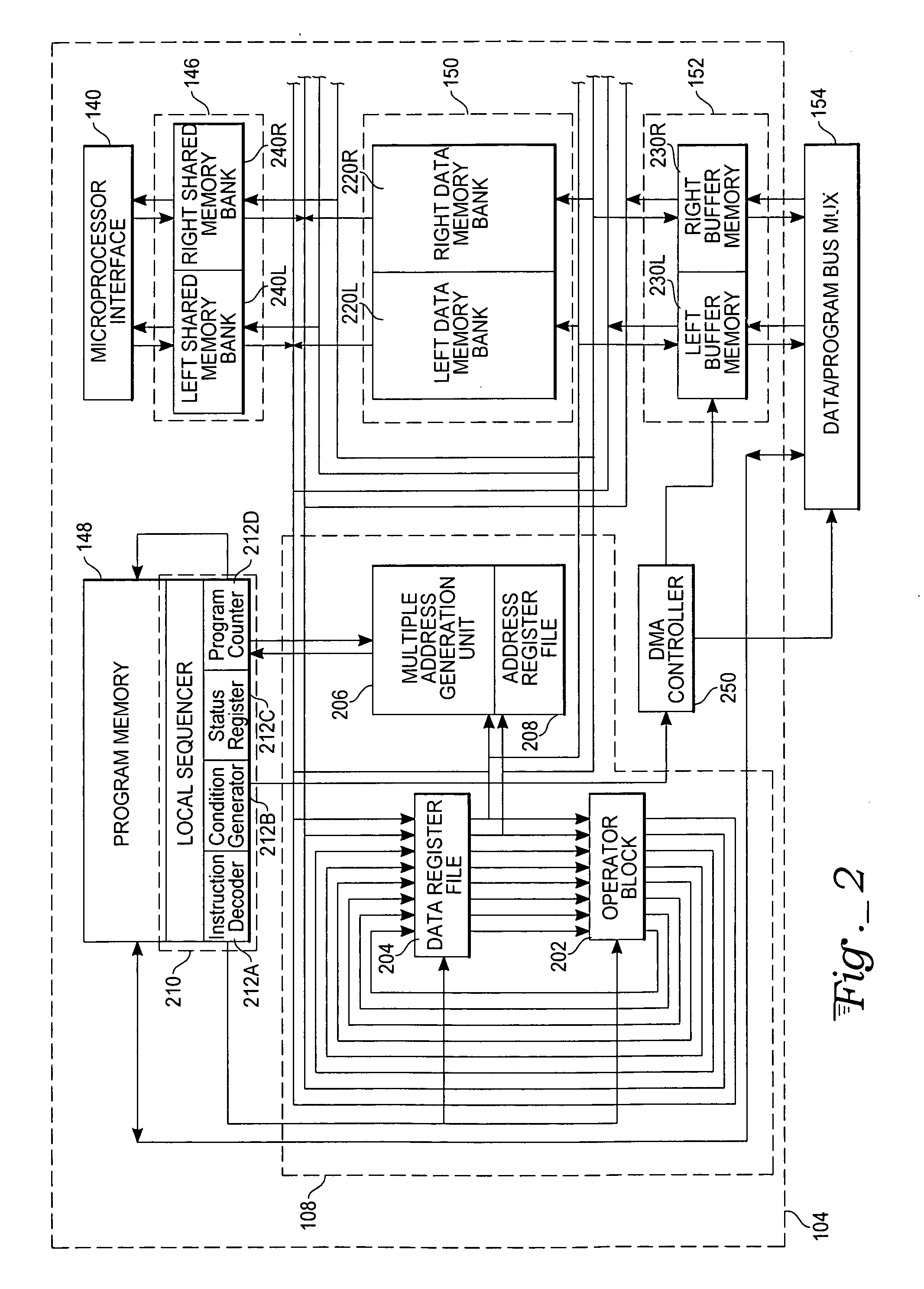

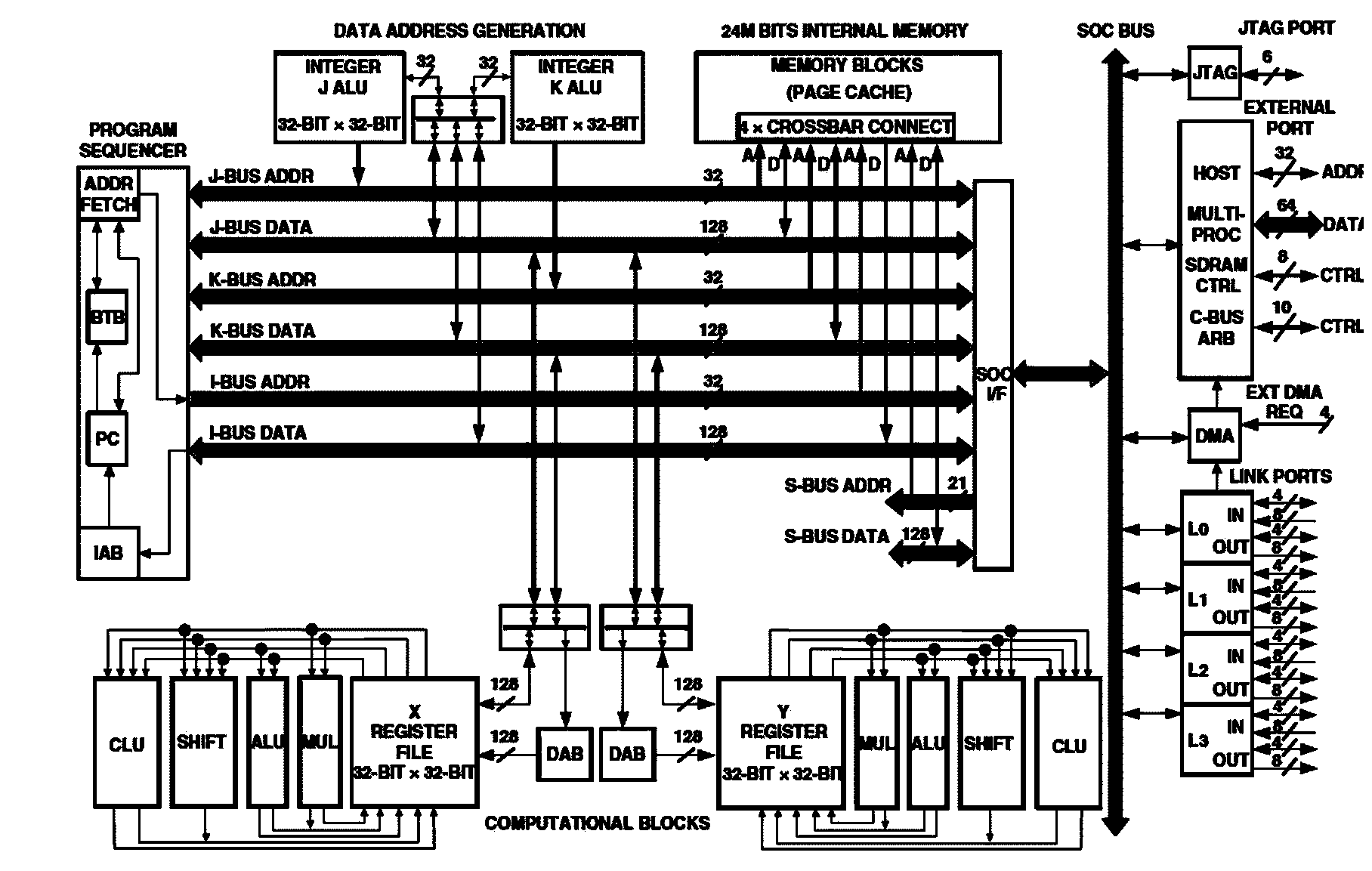

Dual-processor complex domain floating-point DSP system on chip

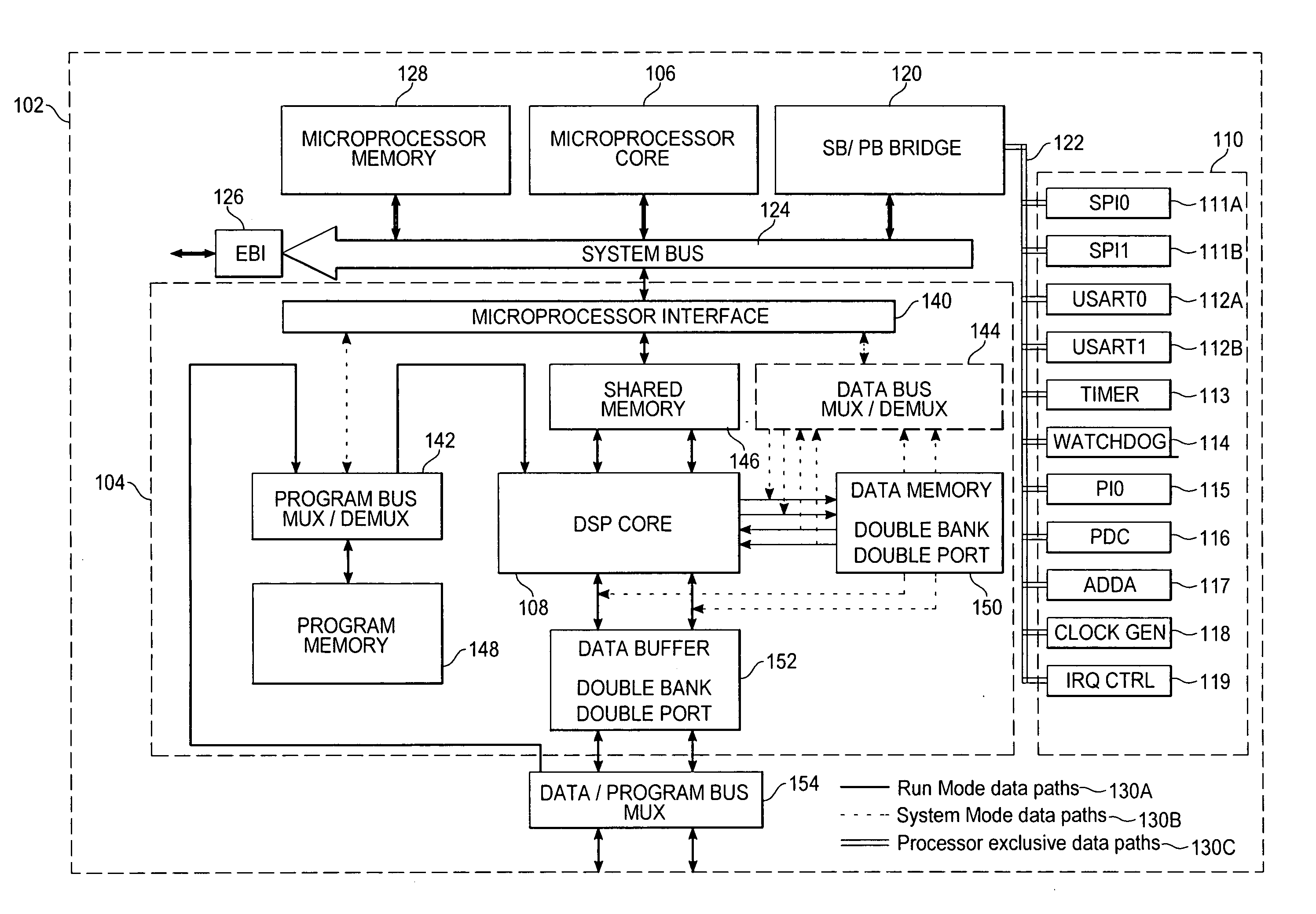

ActiveUS20050216702A1No performance lossReduce in quantityArchitecture with single central processing unitSpecific program execution arrangementsProcessing coreReal arithmetic

A system for digital signal processing, configured as a system on chip (SoC), combines a microprocessor core and digital signal processor (DSP) core with floating-point data processing capability. The DSP core can perform operations on floating-point data in a complex domain and is capable of producing real and imaginary arithmetic results simultaneously. This capability allows a single-cycle execution of, for example, FFT butterflies, complex domain simultaneous addition and subtraction, complex multiply accumulate (MULACC), and real domain dual multiply-accumulators (MACs). The SoC may be programmed entirely from a microprocessor programming interface, using calls from a DSP library to execute DSP functions. The cores may also be programmed separately. Capability for programming and simulating the entire SoC are provided by a separate programming environment. The SoC may have heterogeneous processing cores in which either processing core may act as master or slave, or both cores may operate simultaneously and independently.

Owner:ATMEL CORP

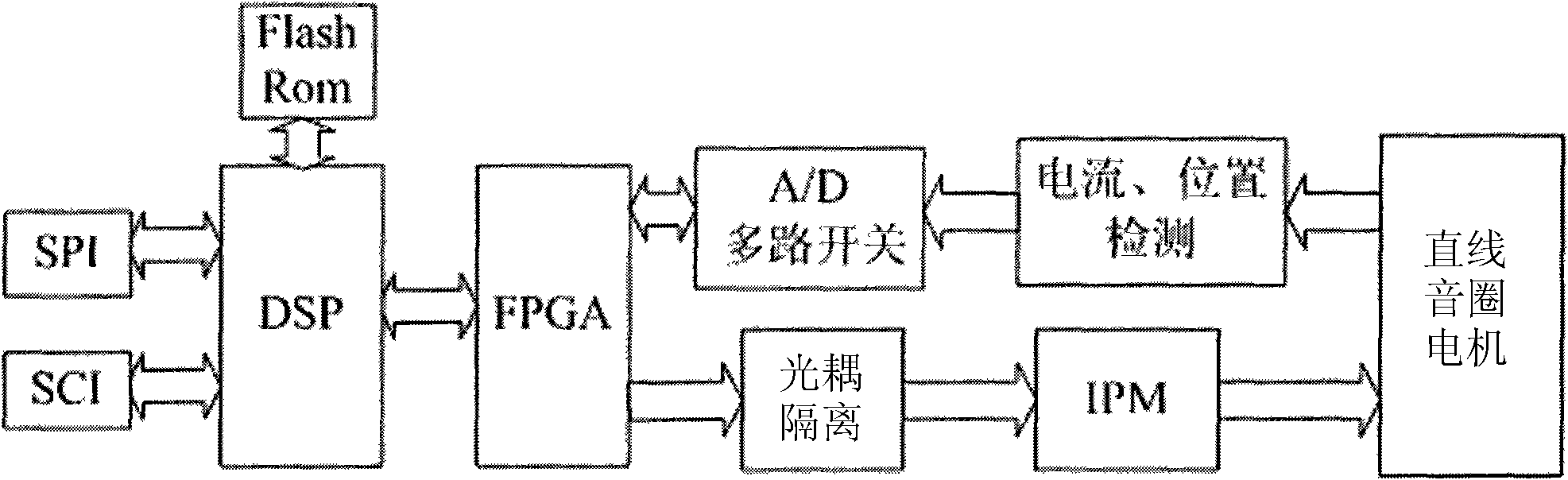

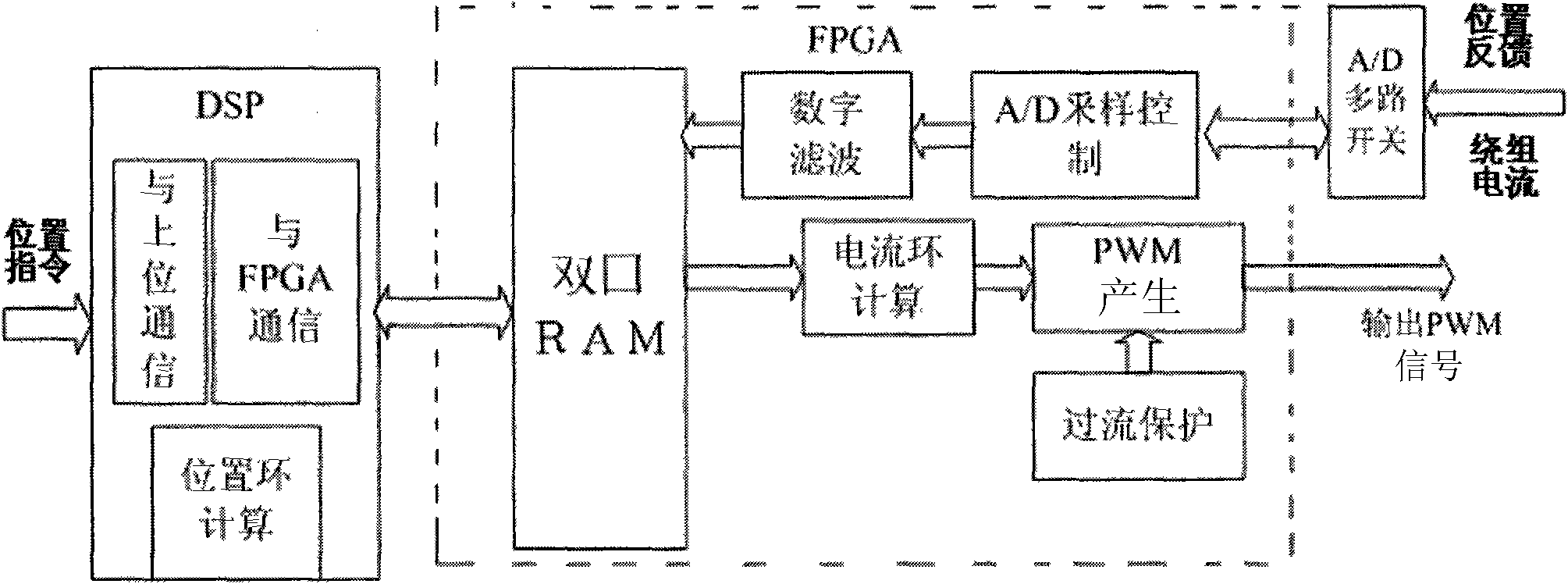

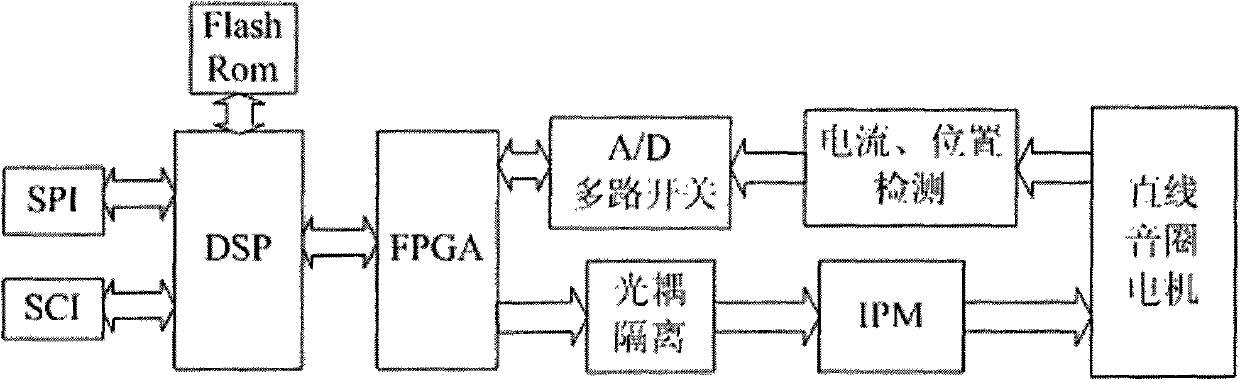

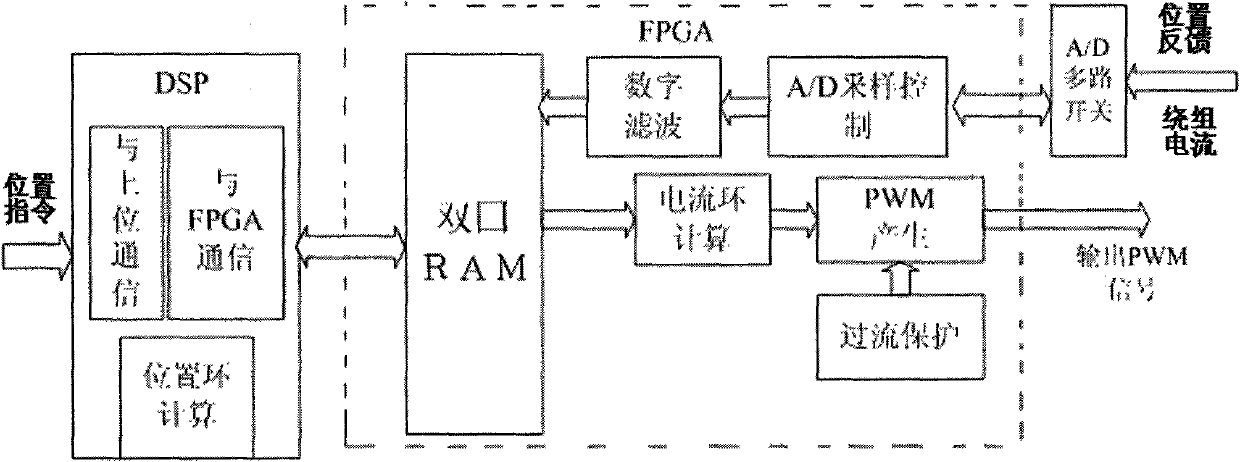

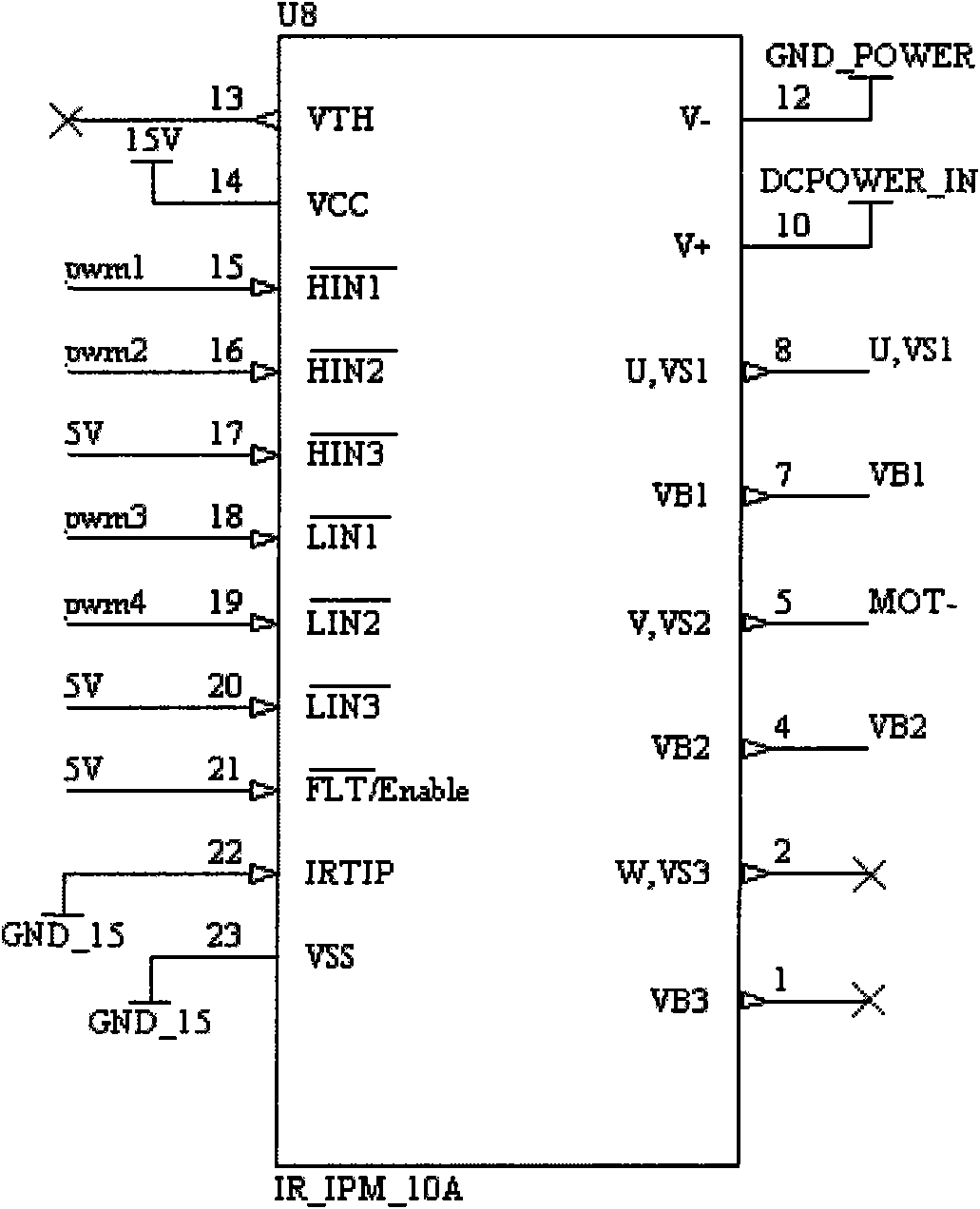

Full digital driving controller of permanent magnetic linear voice coil motor used for direct driving valve

InactiveCN101576745AIncrease sampling rateHighly integratedAC motor controlElectric motor controlExtensibilityField programmable logic devices

The invention relates to a full digital driving controller of a permanent magnetic linear voice coil motor used for a direct driving valve, consisting of three parts: a digital controller, a power circuit and a signal detection circuit; the digital controller circuit comprises a 32-bit floating point DSP, a field programmable logic device FPGA and an external Flash ROM; the power circuit comprises a high-speed optical coupling isolation circuit, and an H-bridge power main circuit consisting of intelligent power modules IPM; the signal detection circuit comprises an A / D converter, a multi-path analogue switch, a Hall current sensor used for detecting the moving coil winding current, a non-contact eddy current displacement sensor used for detecting the position of the moving coil and an amplification and active power filter circuit for analogue signals. The full digital driving controller of the permanent magnetic linear voice coil motor used for the direct driving valve has the advantages of high integration, good extensibility, high reliability, high frequency response and high precision.

Owner:BEIHANG UNIV

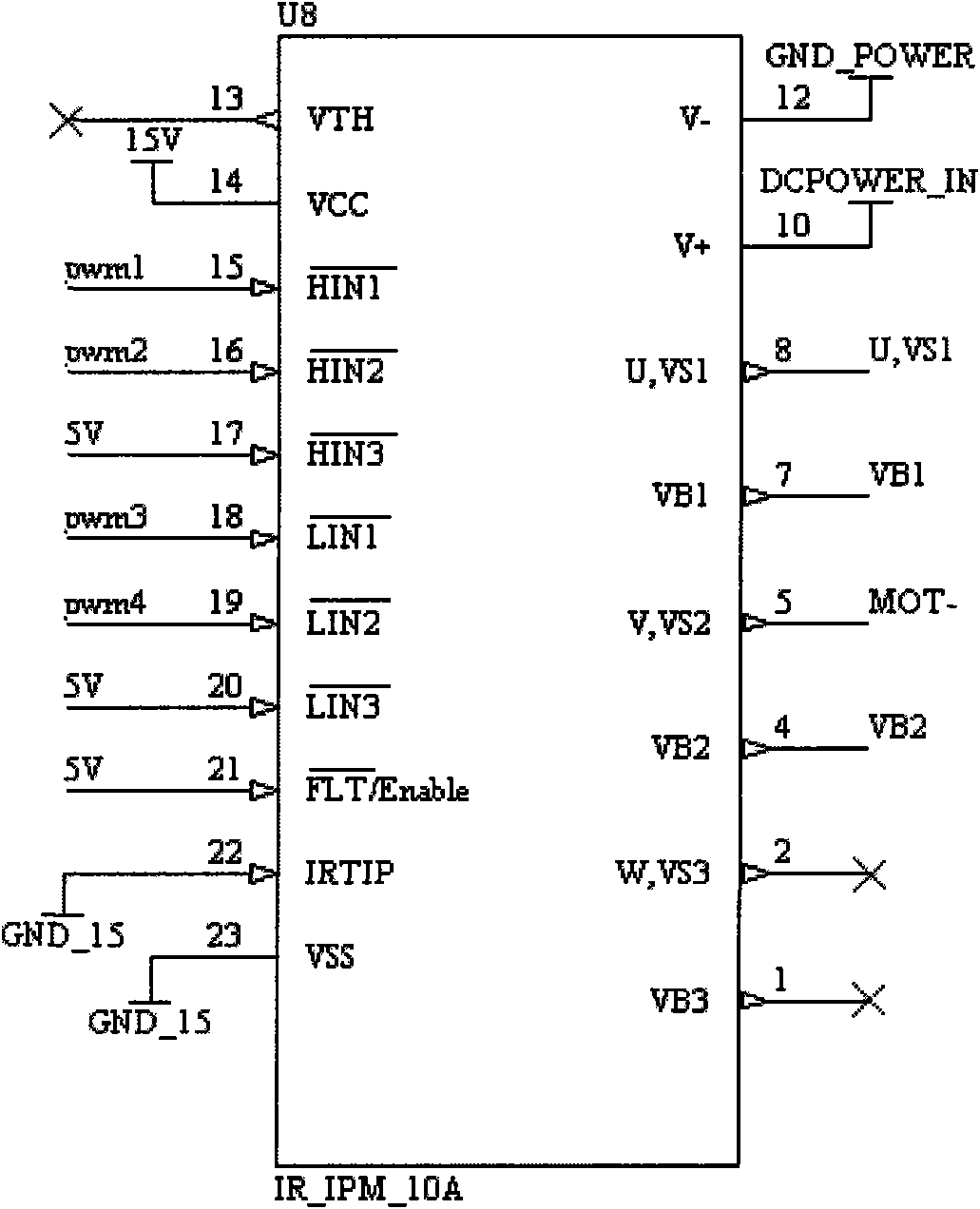

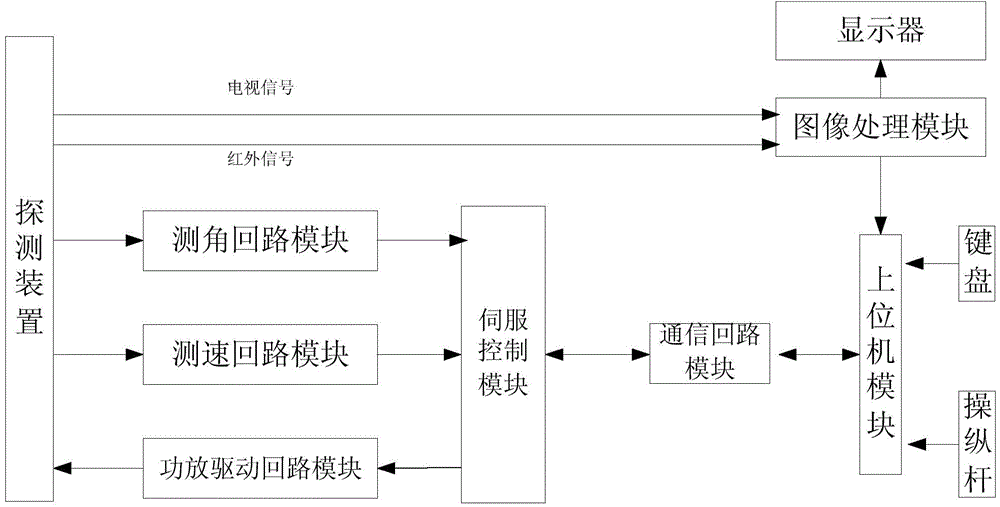

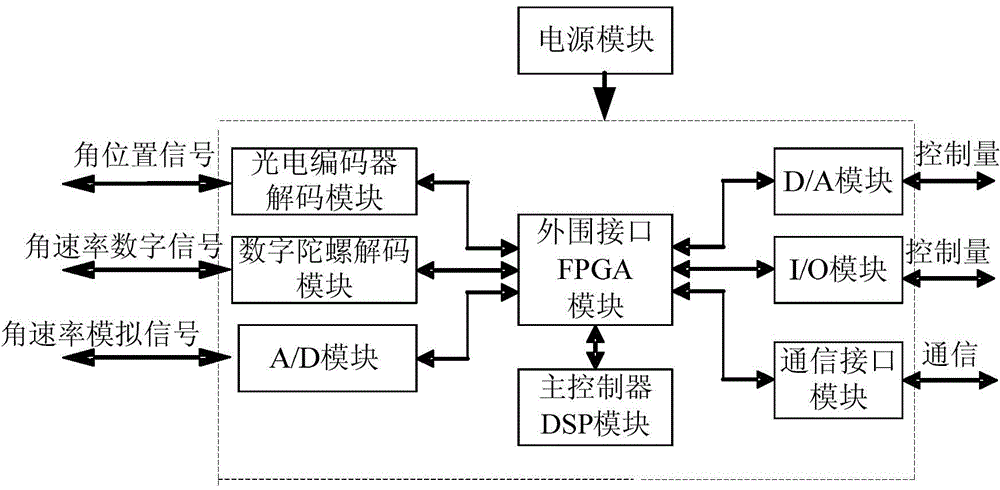

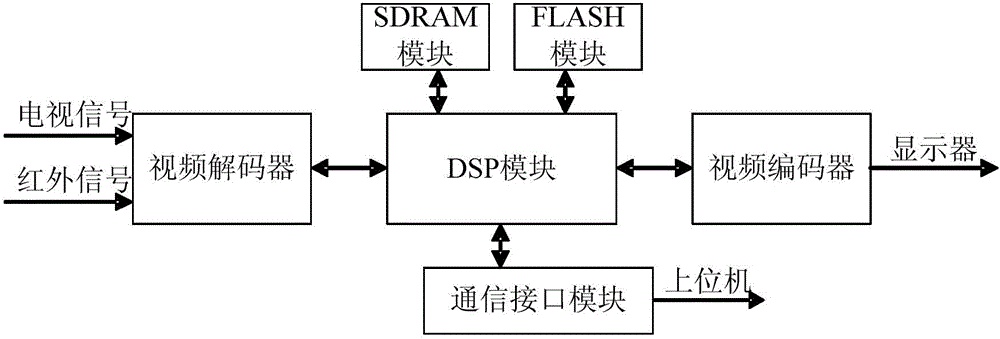

TMX320F28335 floating point DSP (Digital Signal Processor) based two-shaft photoelectric tracking system

InactiveCN104615153AImprove tracking accuracyEasy to installControl using feedbackImaging processingComputer module

The invention provides a TMX320F28335 floating point DSP (Digital Signal Processor) based two-shaft photoelectric tracking system, belongs to the technical field of control of servo movement, and aims at solving the problems of low tracking precision and inconvenient mounting, dismounting and repairing due to the DSP based control for the two-shaft photoelectric tracking system in the prior art. The system comprises a detection device, a servo control module, an angle measuring loop module, a speed measuring loop module, a power amplification driving loop module, a communication loop module, an upper computer module and an image processing module; the angle position information and angle rate information measured by a photoelectric encoder and a gyro of the detection device are respectively sent to the servo control module through the angle measuring loop module and the speed measuring loop module; the image processing module is used for processing the acquired module to obtain the miss distance of a characteristics target; the servo control module is used for acquiring control quantity according to the angle position information, the angle rate information, the miss distance, an instruction of an upper computer and a set working mode and sending to the power amplification driving loop module to drive the detection device to track the characteristics target on real time. The system is applied to the field of military tracking.

Owner:HARBIN INST OF TECH

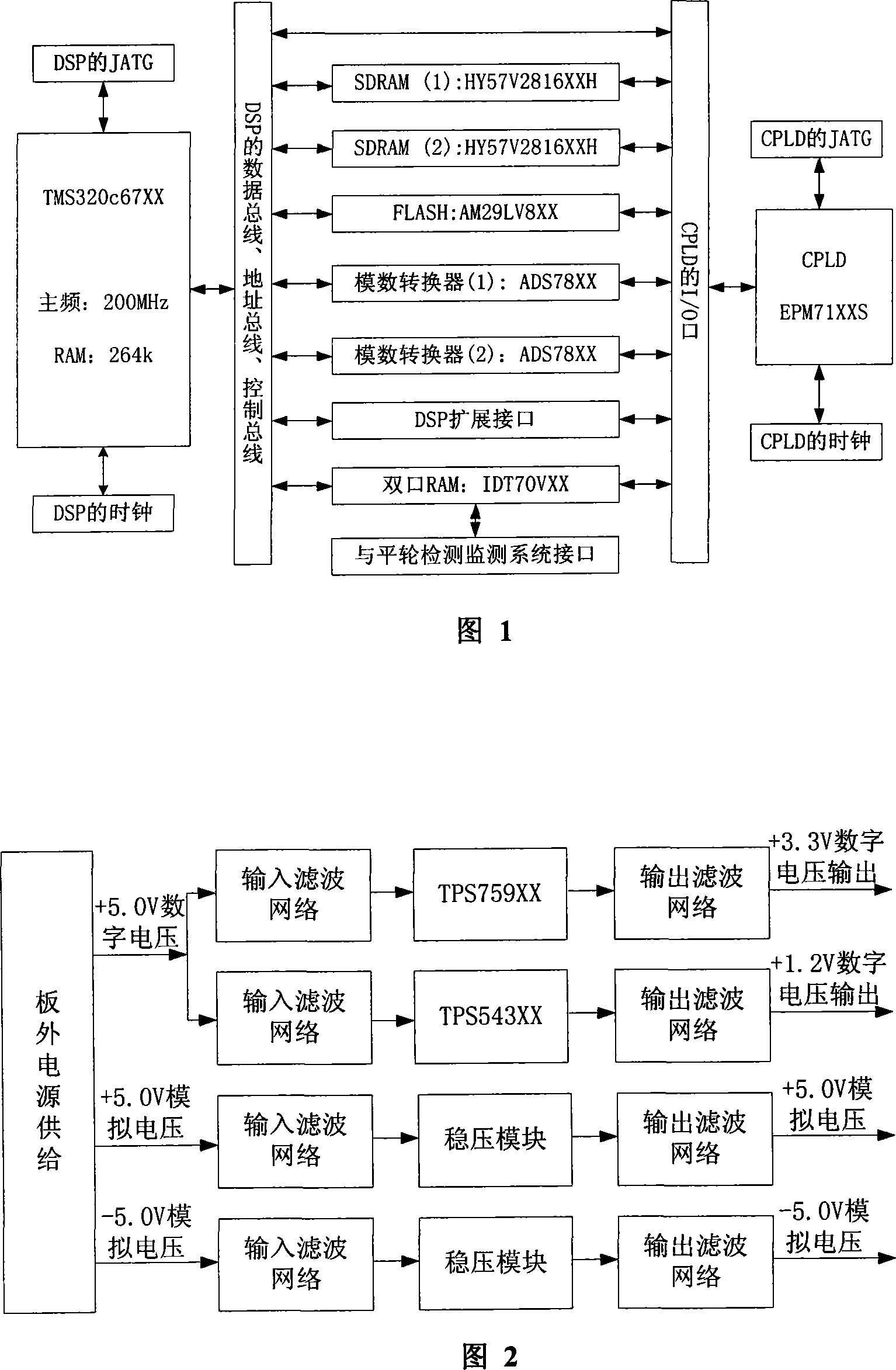

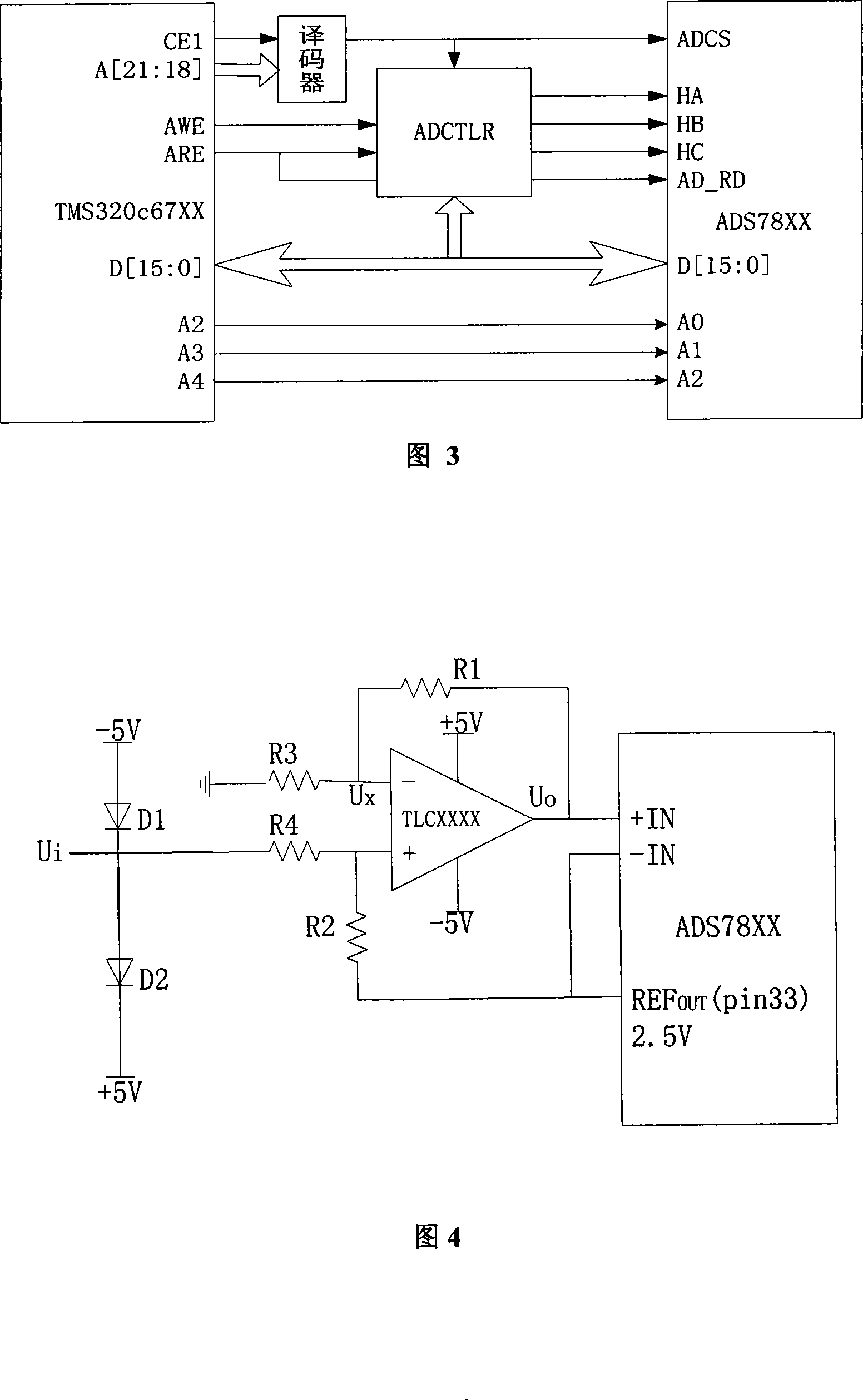

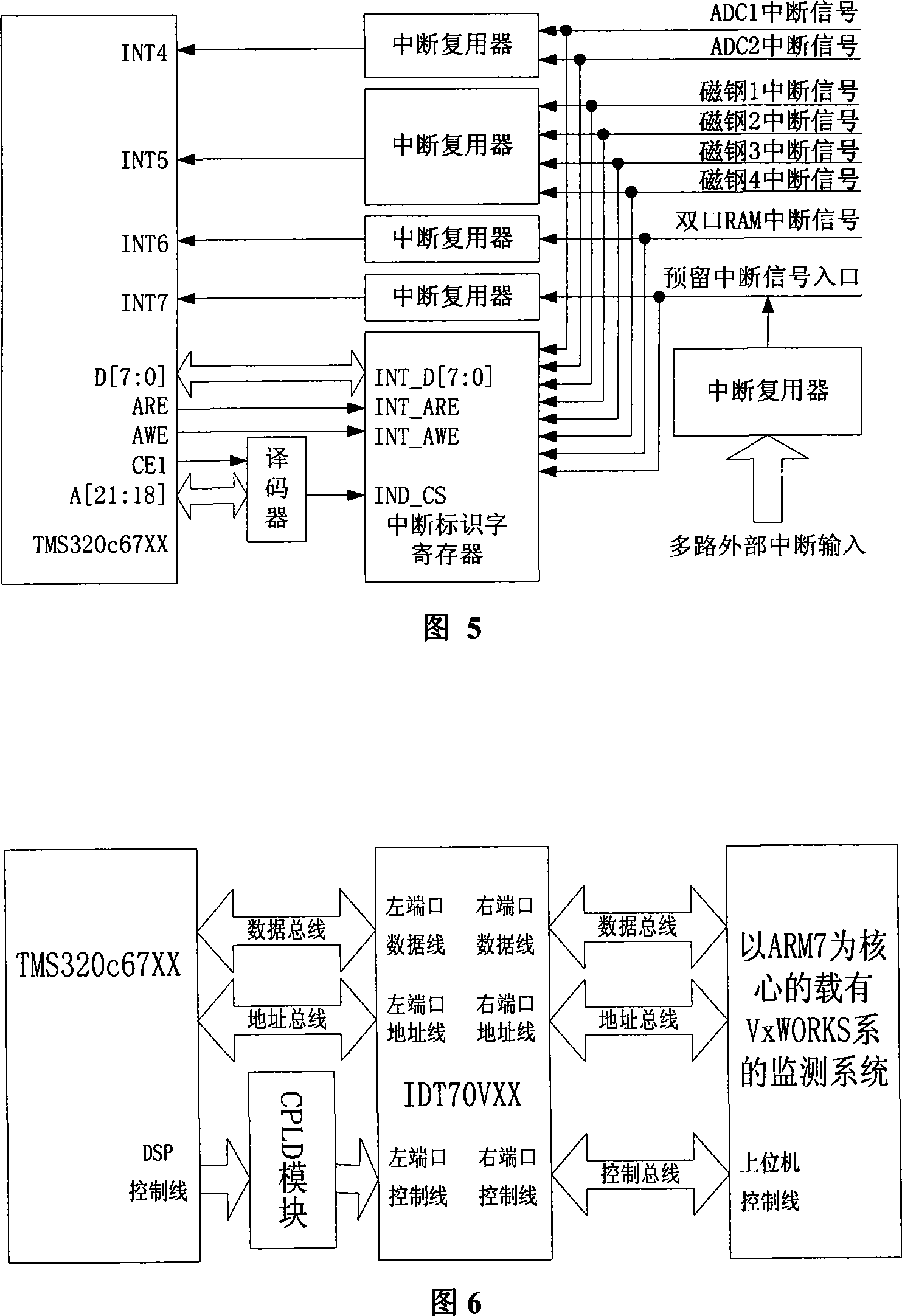

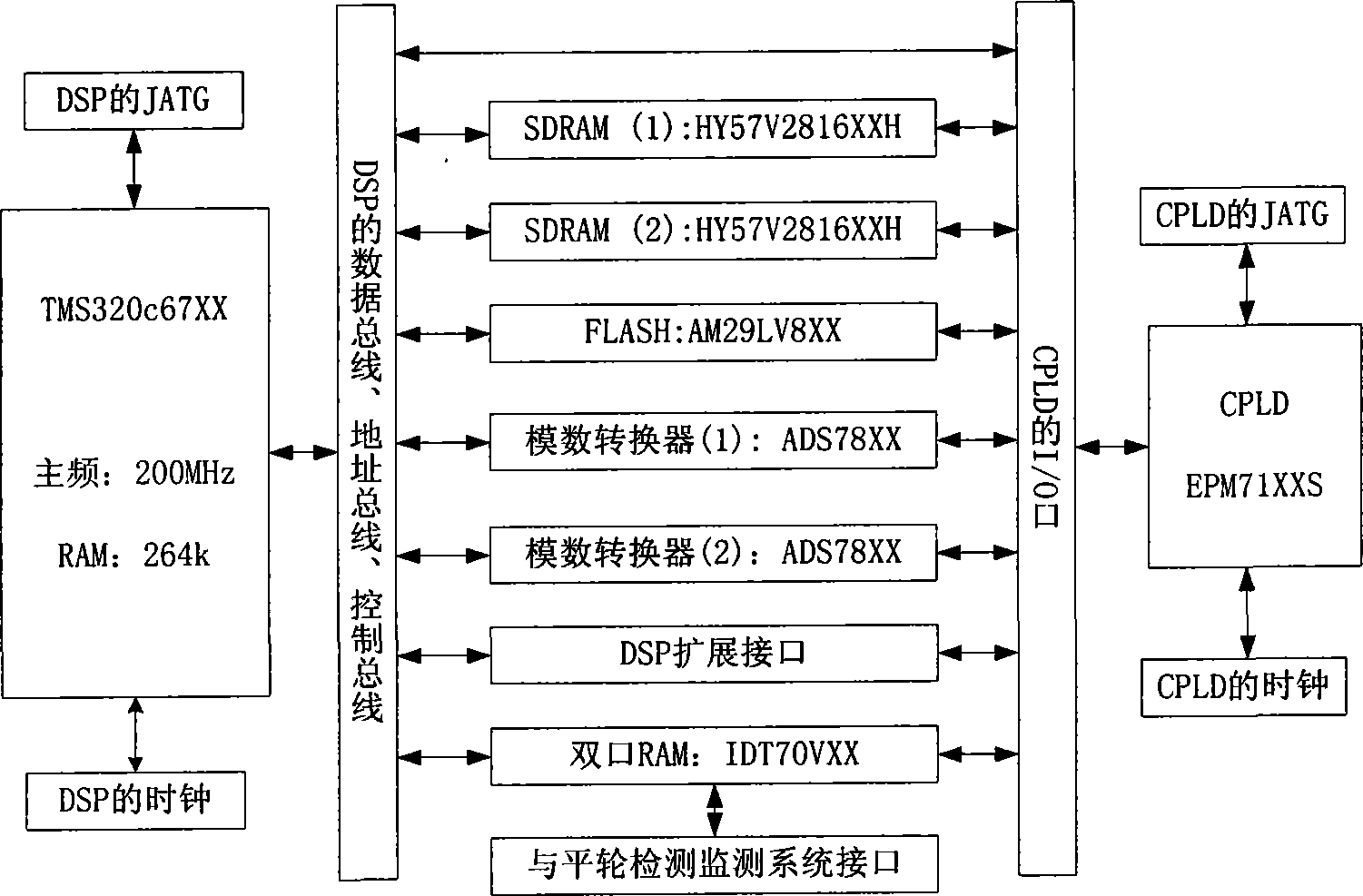

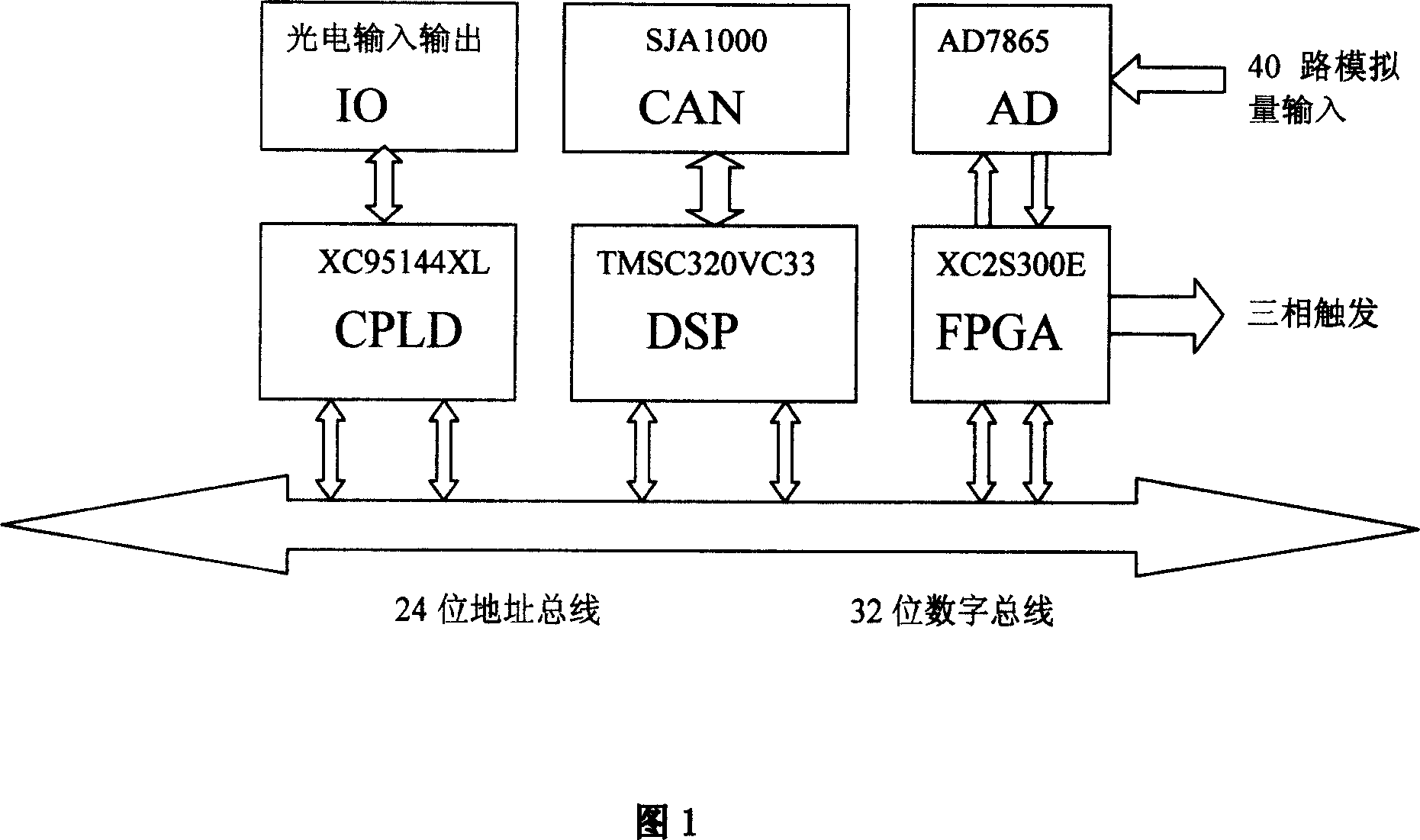

System for data acquisition and signal treatment of testing flat wheel

InactiveCN101206162AHigh precisionHigh speedRailway vehicle testingInput/output processes for data processingProgrammable logic deviceData acquisition

The invention provides a flat wheel detection data acquisition and signal processing system, which consists of seven parts, namely a power module, an AD sampling input front end conditioning module, an AD sampling conversion module, a data program memory module, an interruption management module, a high speed communication module and a reset module. The invention applies a high speed floating point DSP chip, a high speed low consumption double 12-bit parallel A / D converter, a dual-ported RAM chip and a complicated programmable logic device to the flat wheel detection data acquisition and signal processing system, develops a data acquisition and processing system taking the high speed floating point DSP as a core processor, and improves the speed, accuracy and stability of flat wheel detection data acquisition and processing (in addition, the system control, communication and monitoring is handled by ARM-VxWORK, and communication takes a form of network card.), thereby improving the performance index of the whole flat wheel detection system.

Owner:HARBIN ENG UNIV

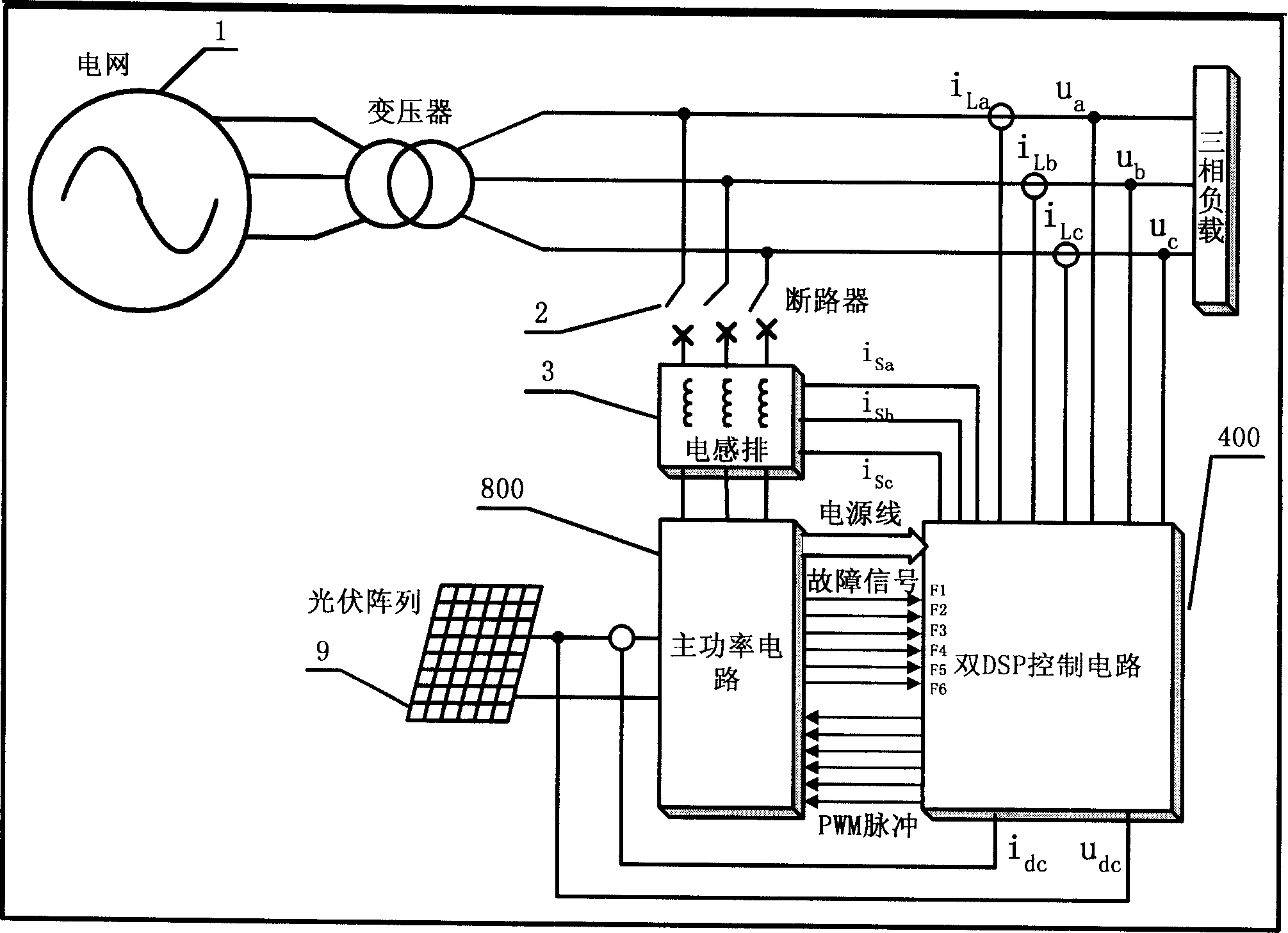

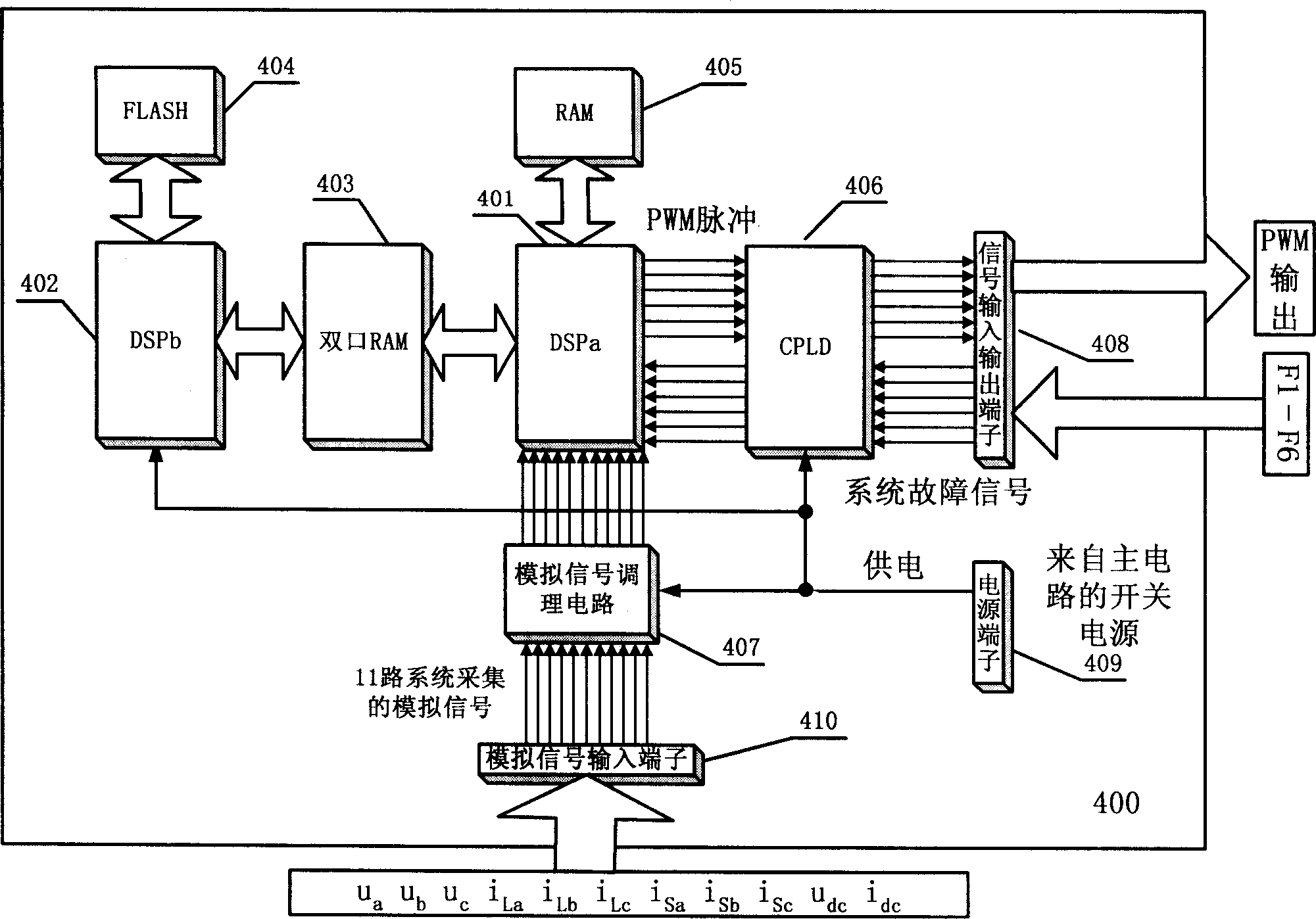

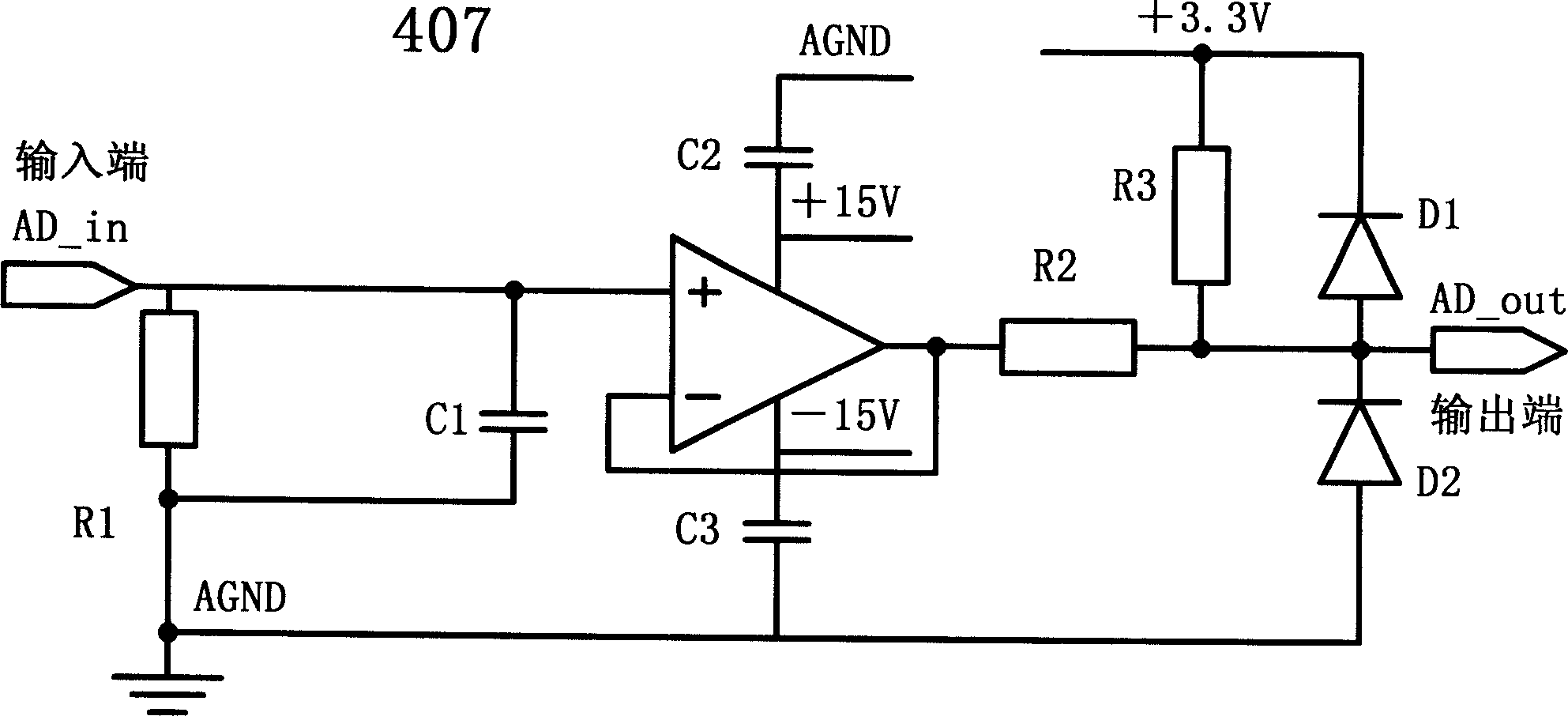

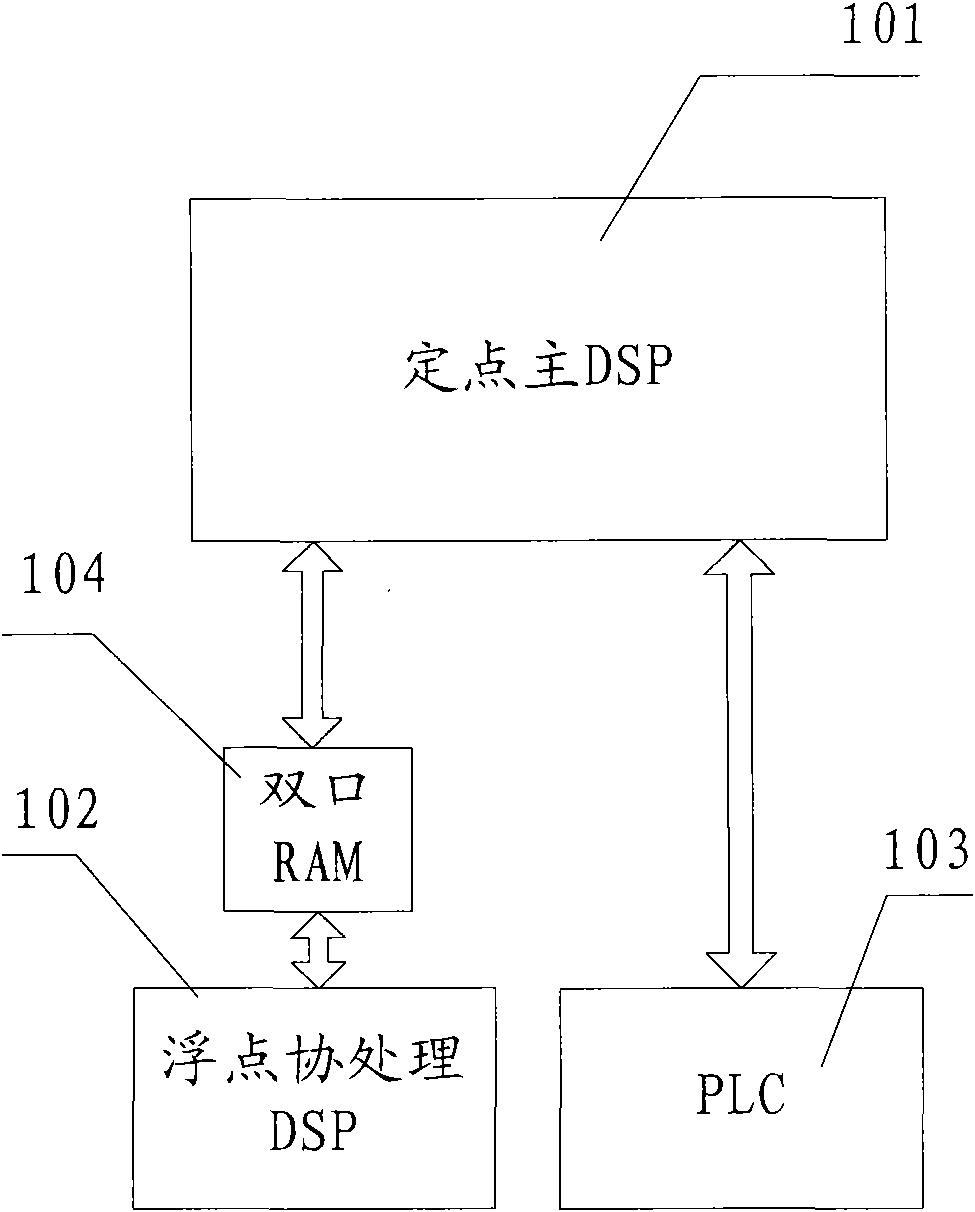

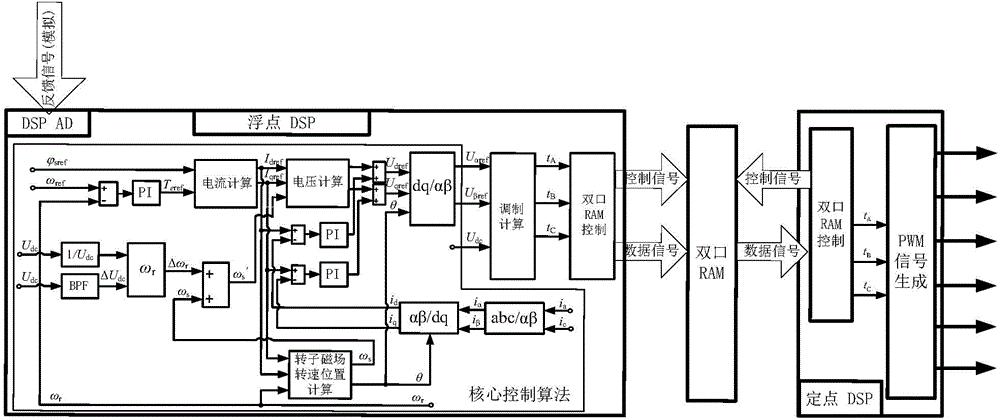

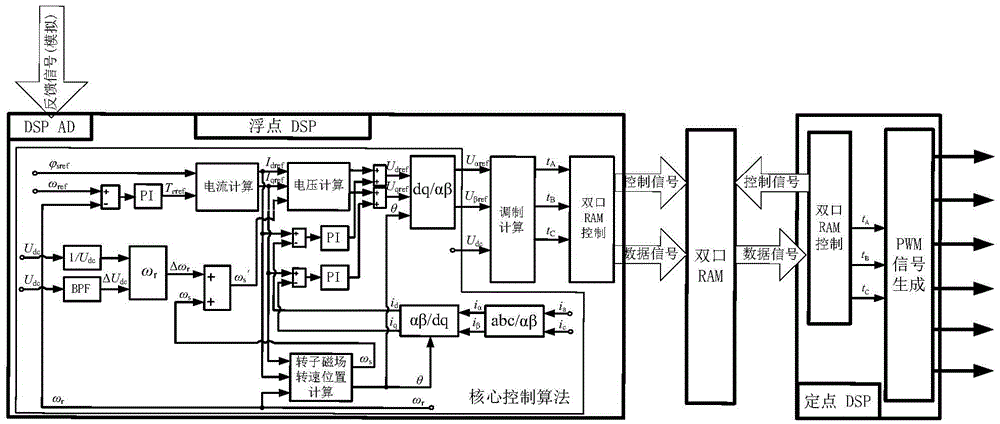

Dual-DSP control circuit of photovoltaic grid-connected device with STATCOM function

InactiveCN1877951AEasy to control speedIncrease computing speedFlexible AC transmissionSingle network parallel feeding arrangementsSolar batteryPwm signals

The invention discloses a double-DSP control circuit of photovoltaic interconnected device with STATCOM function, which comprises the following parts: locating DSP chip, high-speed RAM chip, floating-point DSP chip, 16-bit FLASH chip, double-hole RAM chip, CPLD chip and signal adjusting circuit. The control circuit gathers each item electric quantity signal of photovoltaic signal, which generates PWM signal of control device interconnected inverter through combination calculation of signal disposal and two DSP. The double-DSP control circuit sends active power to electric net in the working time of photovoltaic interconnected device, which improves the utility of solar battery.

Owner:王剑 +1

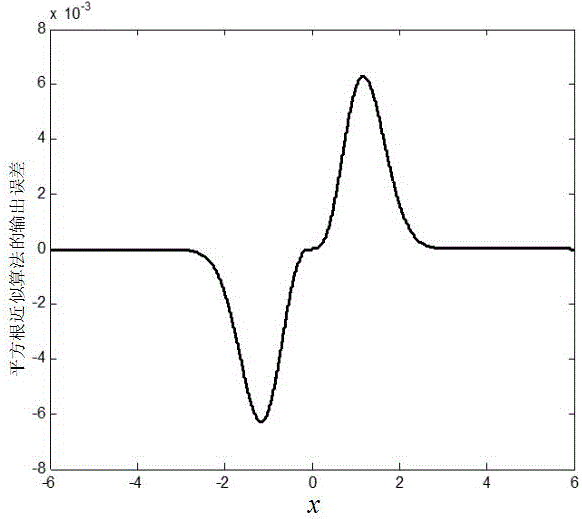

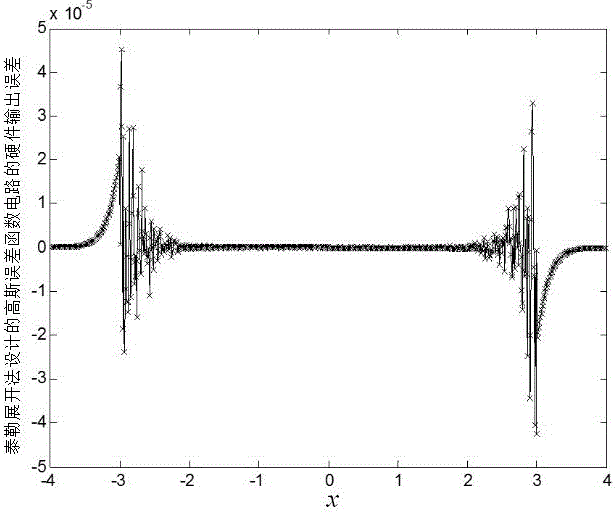

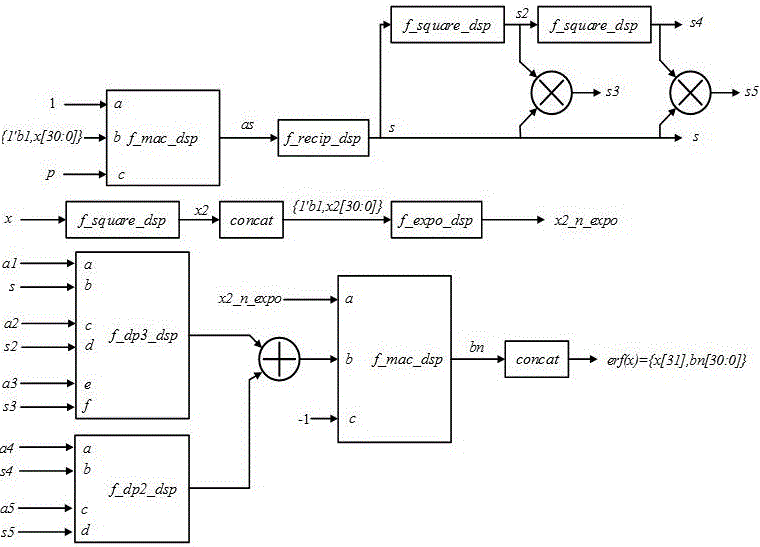

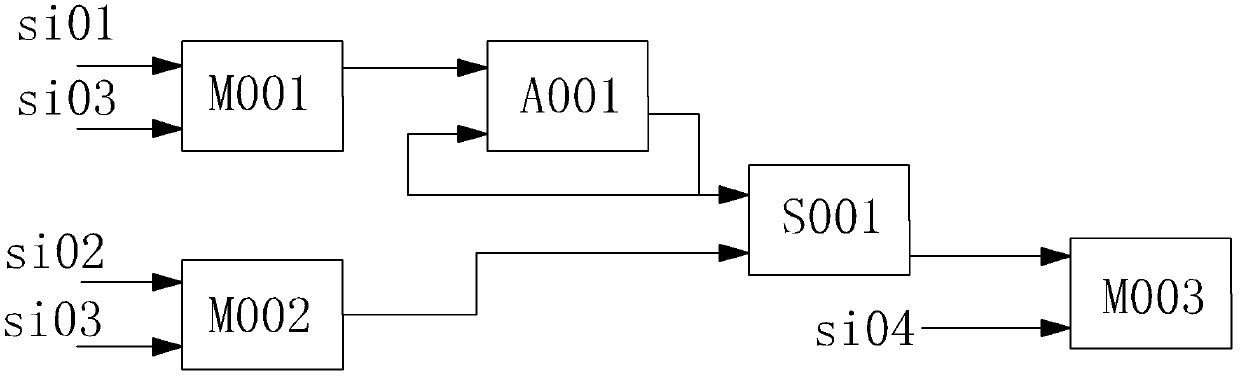

Gaussian error function circuit applied to neural networks

ActiveCN106682732AHigh precisionReduce complexityDigital data processing detailsPhysical realisationNerve networkBinary multiplier

The invention discloses a Gaussian error function circuit applied to neural networks. The Gaussian error function circuit comprises three squarers, two multipliers, two multiplier-adders, two dot product digital signal processors, an adder, a derivation DSP, and an exponent DSP. The DSPs are Design Ware floating-point DSPs from Synopsys. The circuit has a simple structure, uses DSPs easy to obtain, and is easy to implement. Compared with the traditional Taylor expansion method implementation scheme, the circuit has very obvious advantages in terms of precision, area and speed, and especially, the precision is at least two orders of magnitude higher. Meanwhile, the circuit can be implemented using a Verilog code, and has nothing to do with any specific process, so that the circuit can be applied to different processes very easily and is of very strong portability. The Gaussian error function circuit can be applied to the design of various hardware circuits related to neural networks as a soft-core IP.

Owner:ZHEJIANG UNIV

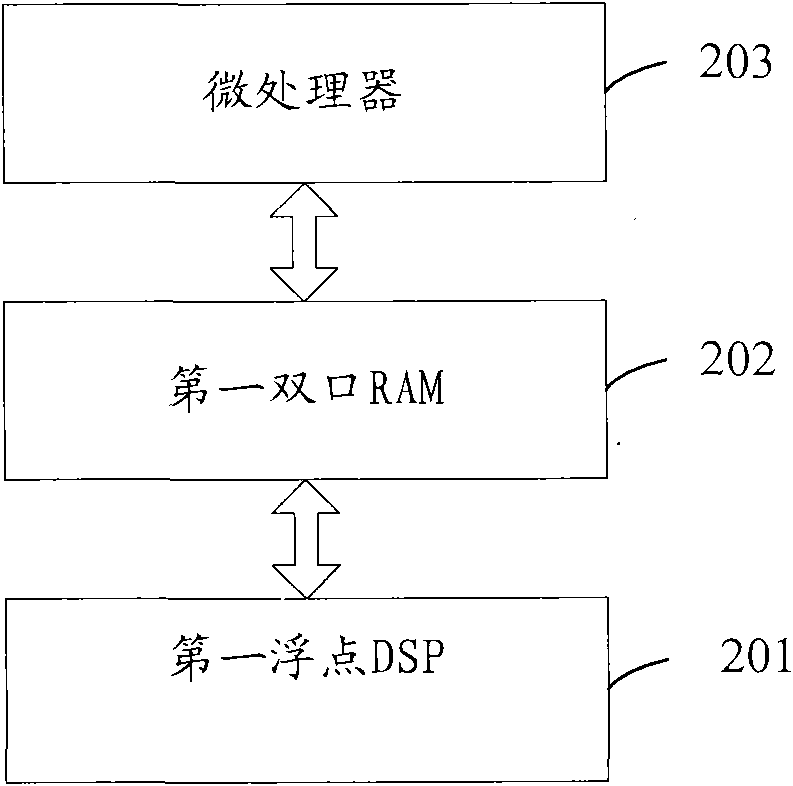

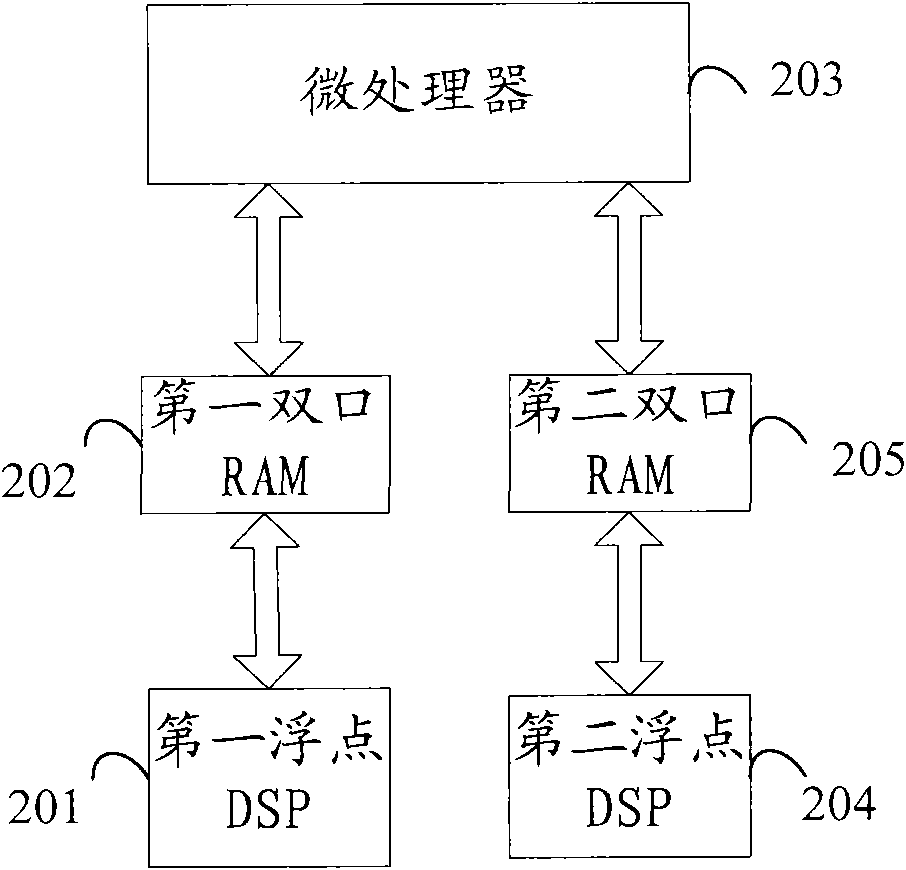

Real-time controller of universal frequency converter

InactiveCN101795085ALow costAccurate calculation abilityDc-ac conversion without reversalEngineeringDual-ported RAM

The invention provides a real-time controller of a universal frequency converter, which comprises a first floating-point DSP, a first dual-port RAM and a microprocessor, wherein the microprocessor is used for sending control command information to the first floating-point DSP via the first dual-port RAM; the operation information of the first floating-point DSP is sent to an upper machine via the first dual-port RAM; the first floating-point DSP is used for reading the external voltage signal and current signal and carrying out algorithm operation according to the voltage signal, the current signal and the control command information, and PWM control pulse is generated by the operation result to realize rectifier control. The real-time controller of the universal frequency converter has higher real-time property and low cost.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

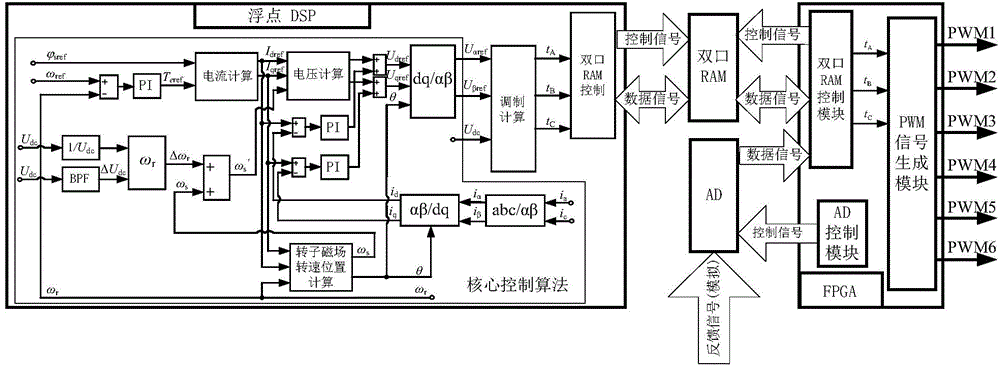

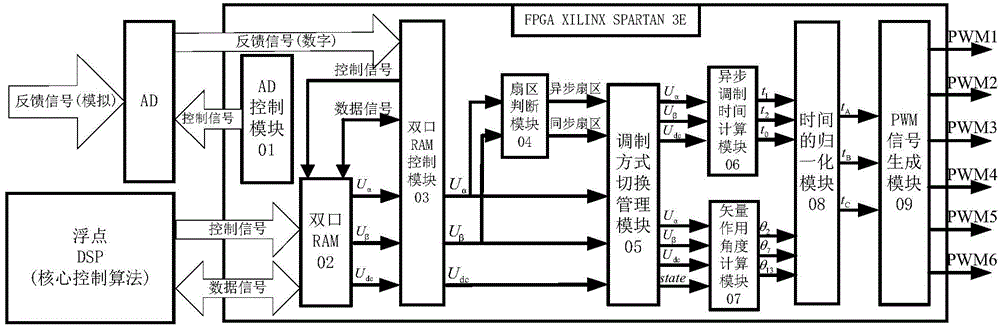

Low-carrier-wave-ratio on-line computation multi-mode space vector pulse width modulation soft core

ActiveCN103956951AAdapt to external complex conditionsGood smooth switching abilityElectronic commutation motor controlAC motor controlCarrier signalAlternating current

Owner:SOUTHWEST JIAOTONG UNIV

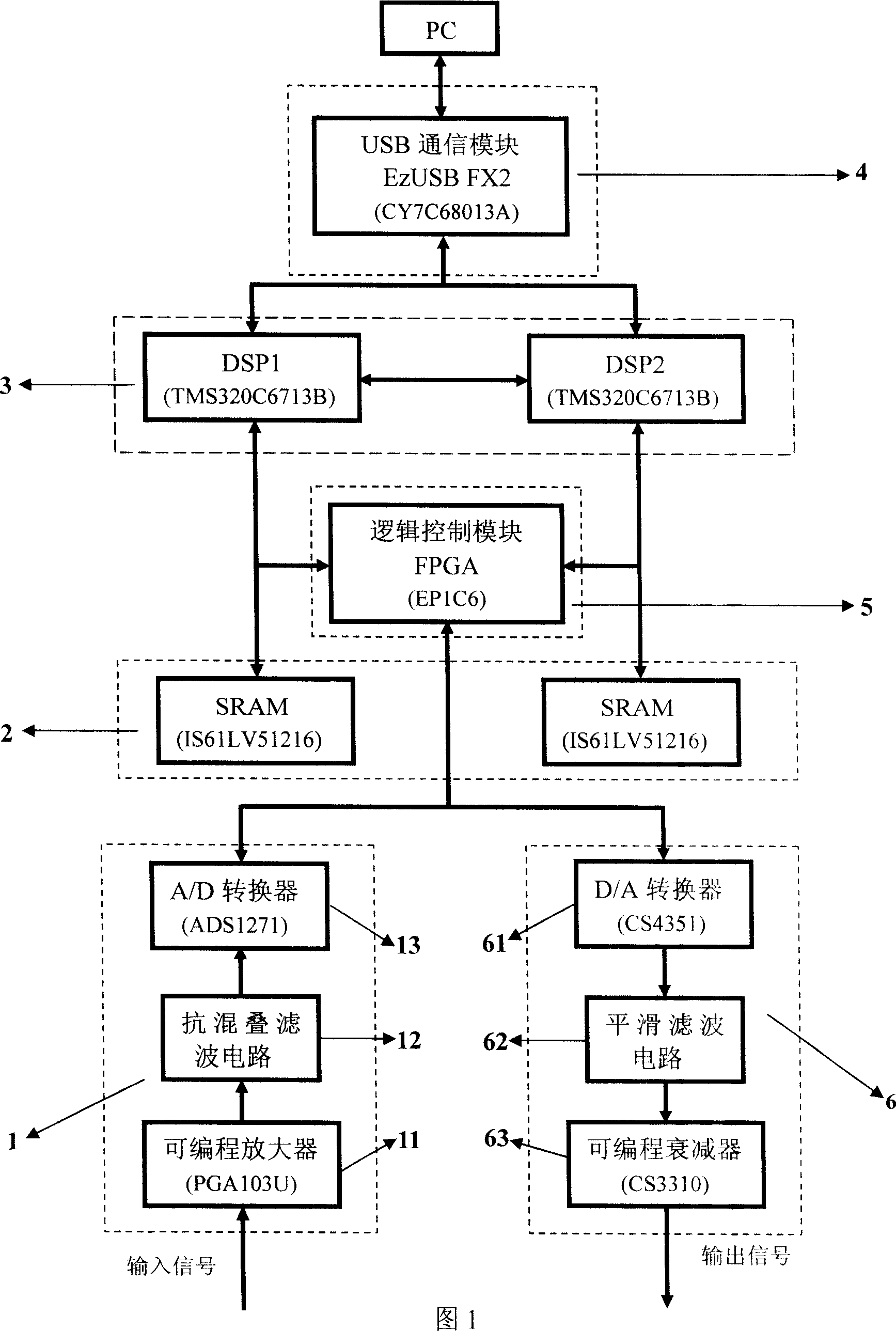

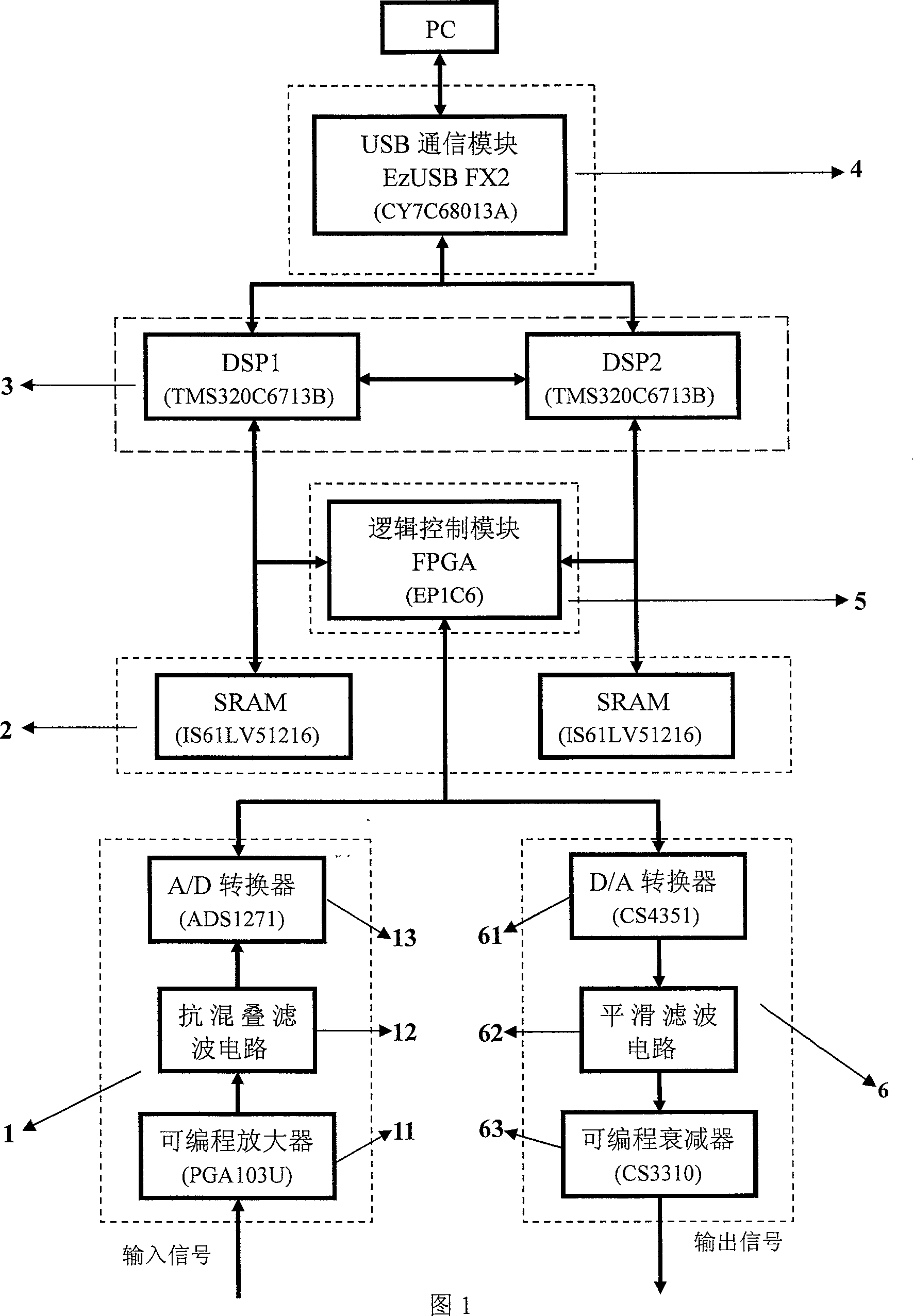

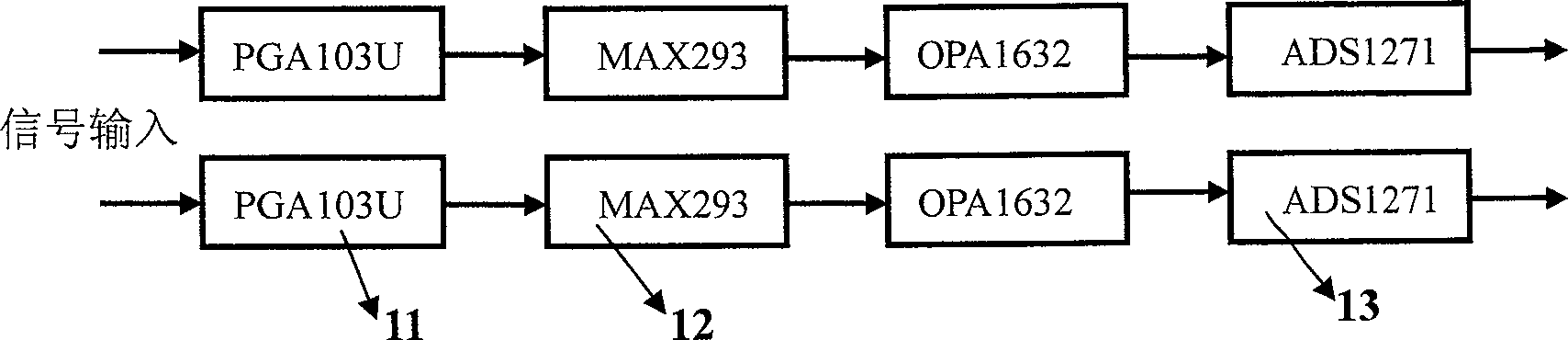

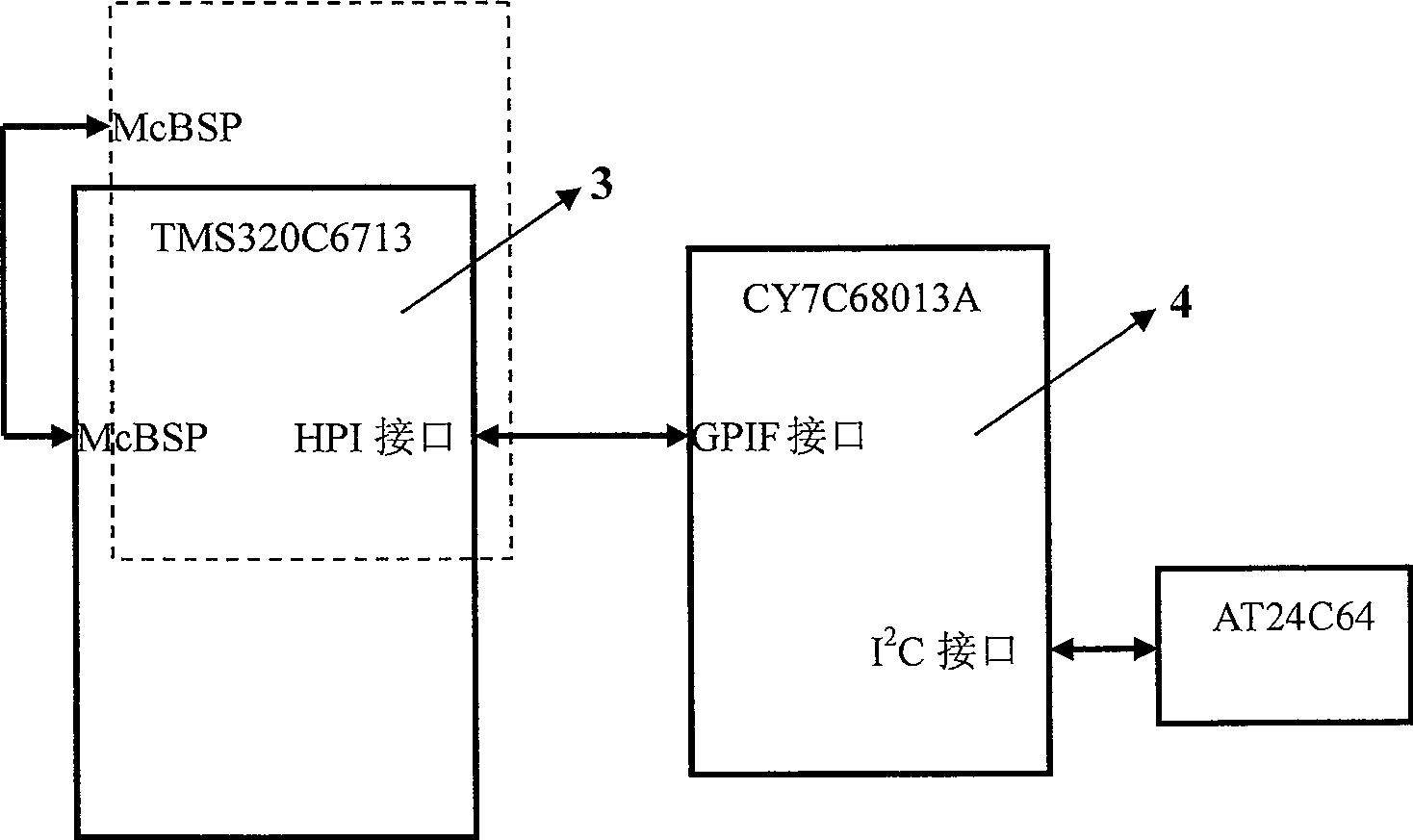

Portable vibration controller using USB interface

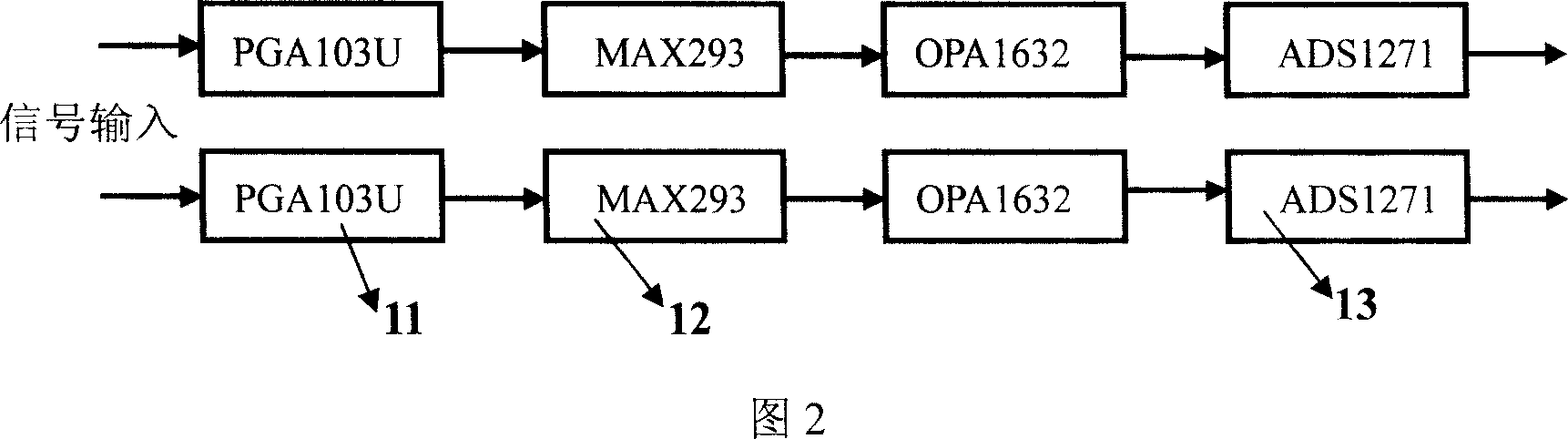

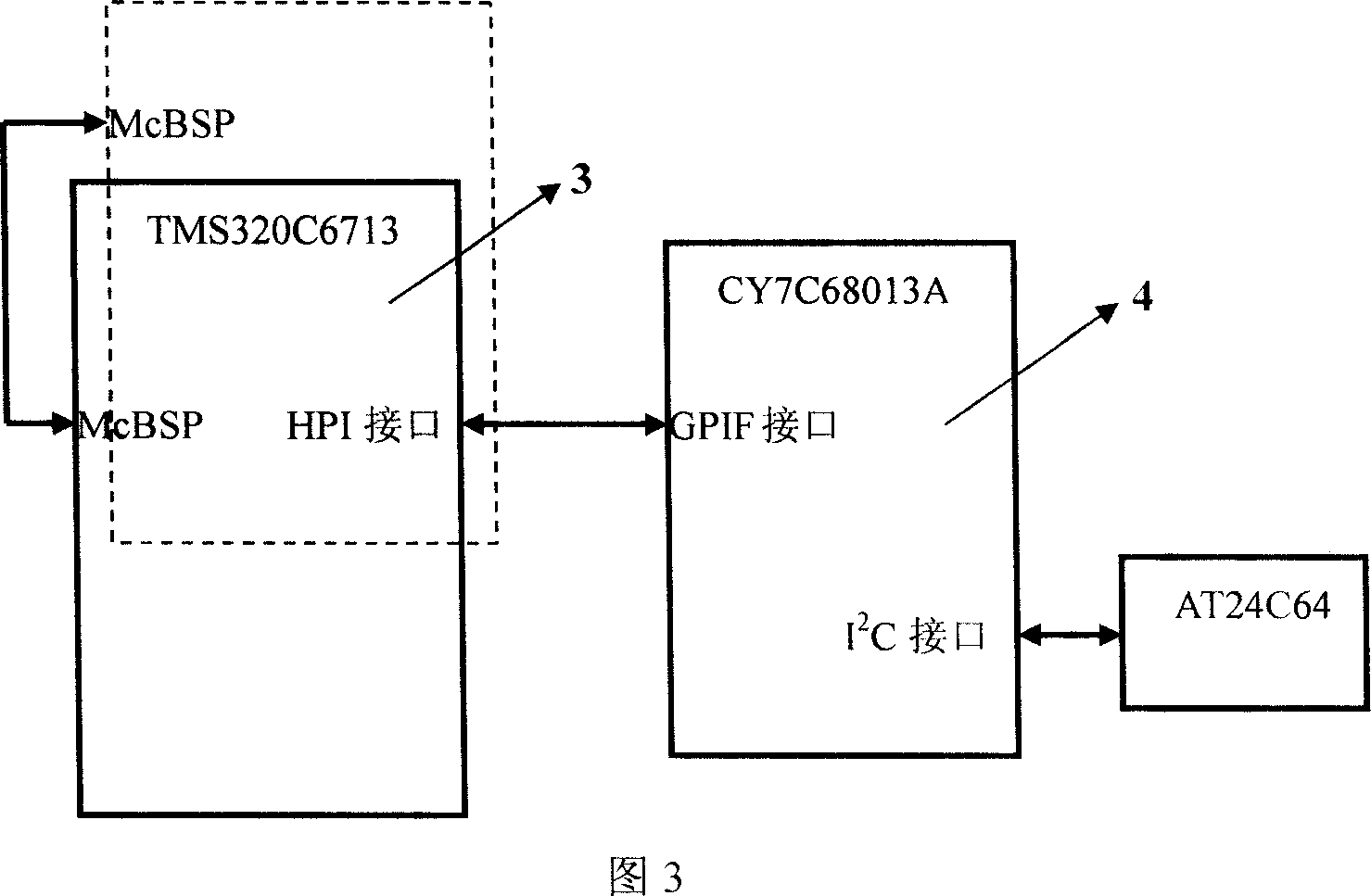

InactiveCN101046685AEasy to moveEasy to carryComputer controlSimulator controlChannel dataVibration control

The present invention relates to a portable vibration controller adopting USB interface. Said portable vibration controller includes the following several portions: dual-channel data acquisition module, signal processing module, data storage module, signal output module, logic control module and USB communication module. Said invention is simple in structure and is high in accuracy.

Owner:SHANGHAI UNIV

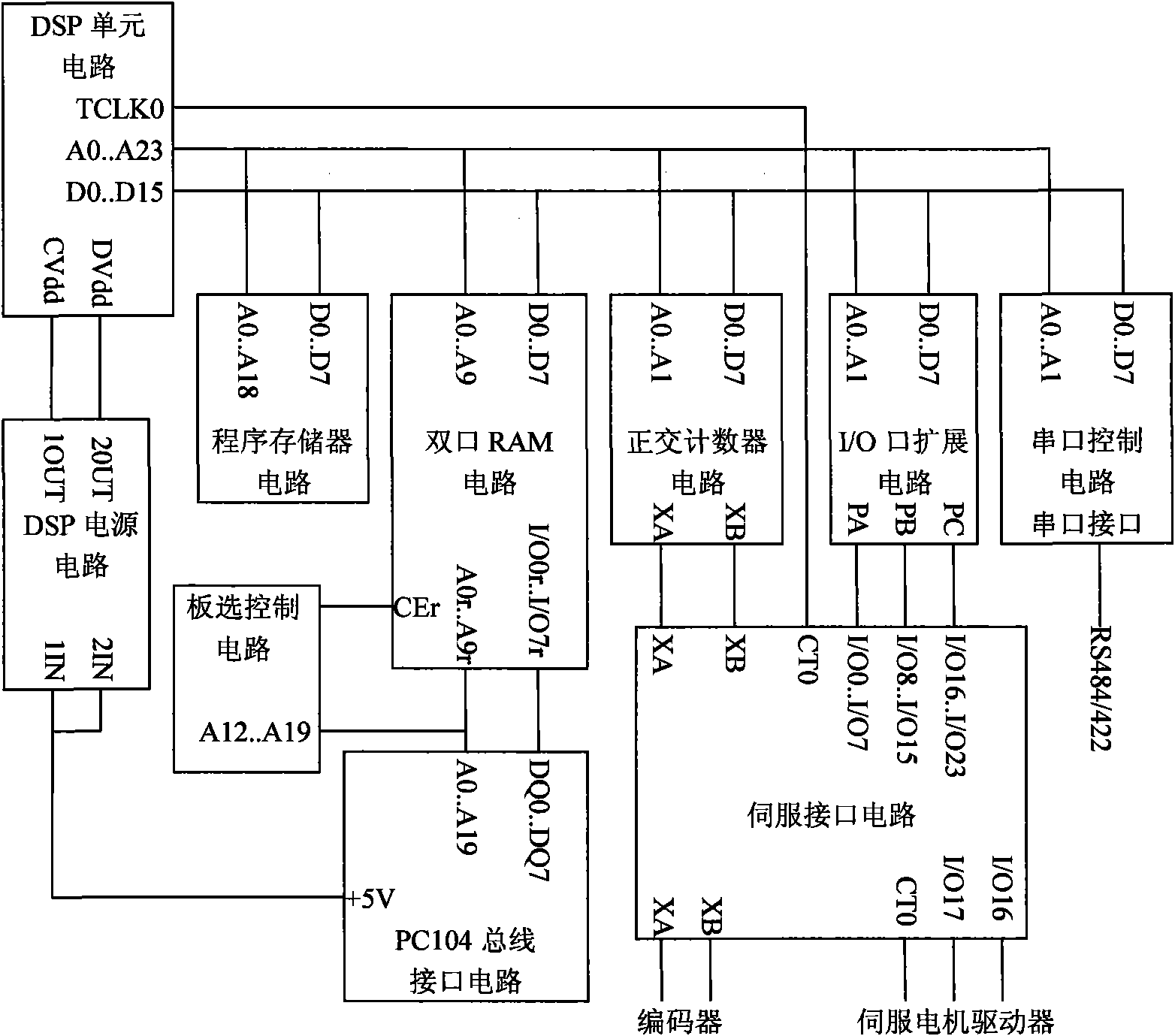

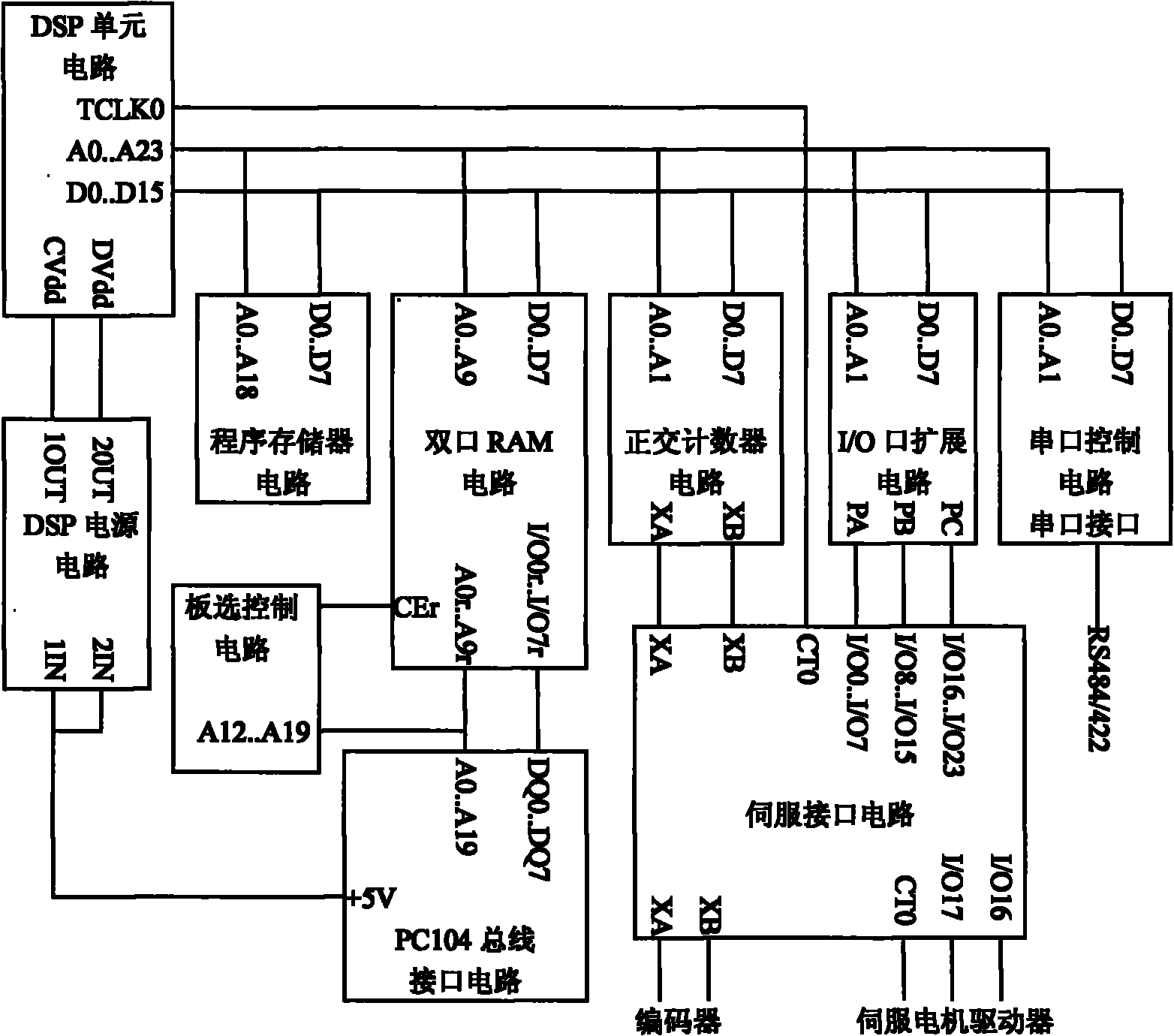

Servo motion control device based on floating-point DSP

InactiveCN101860296AHigh control precisionStrong real-time controlSingle motor speed/torque controlAC motor angular speed controlBus interfaceSoftware

The invention relates to a servo motion control device based on a floating-point DSP, which comprises a DSP unit circuit, a power circuit, a program memory circuit, a dual-port RAM circuit, a PC104 bus interface circuit, a board election control circuit, an orthogonal counter circuit, an I / O port expansion circuit, a servo interface circuit and a serial port control circuit. The invention can realize the high-precision motion control of the AC servo motor with the photoelectric encoder as the feedback through the software based on the floating-point DSP, including the angular position, angular rate, angular vibration and other motion modes, and not only can be used as the expansion board of the PC104 bus, but also can be used as the independent motion controller. Moreover, the invention has the advantages of high performance of real-time control, high flexibility of expansion and high control accuracy of the control system, and can be applied in the turntable system and servo platform of the field of the inertial navigation testing equipment and other fields requiring the accurate control of angular motion such as robots and the like.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES

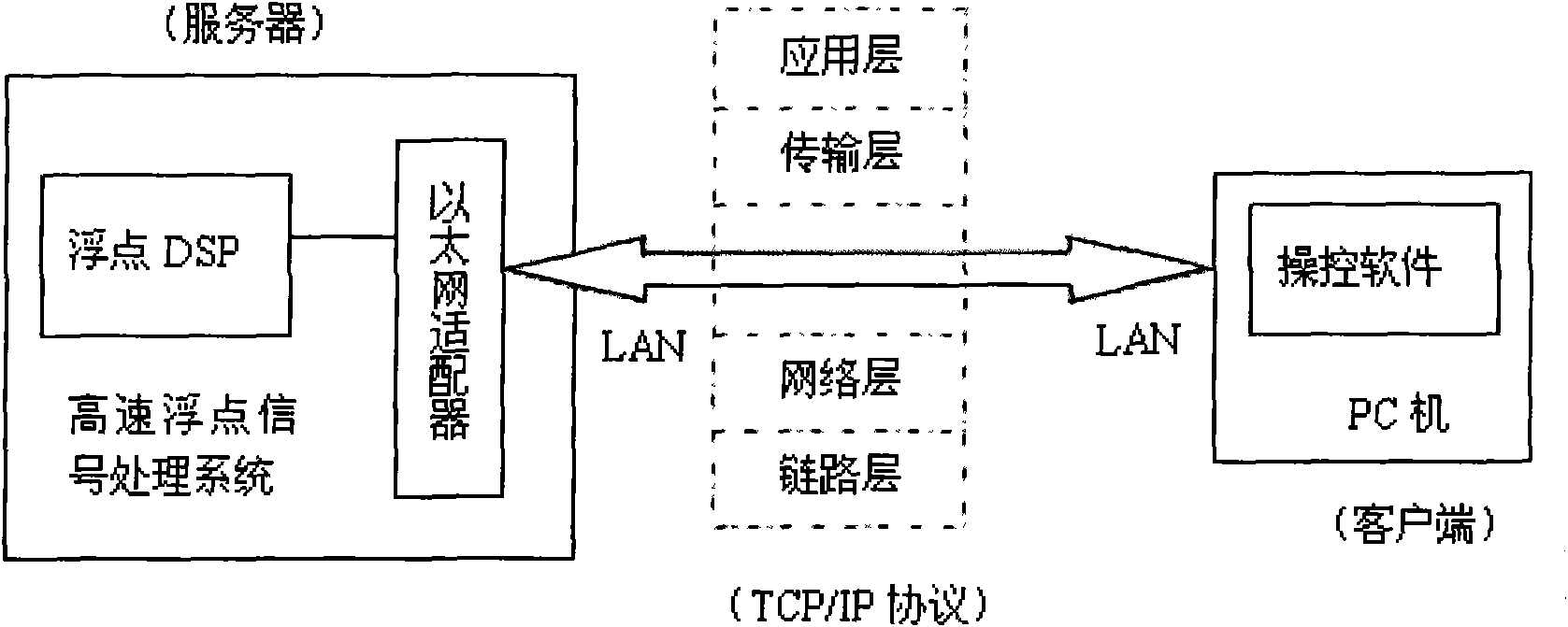

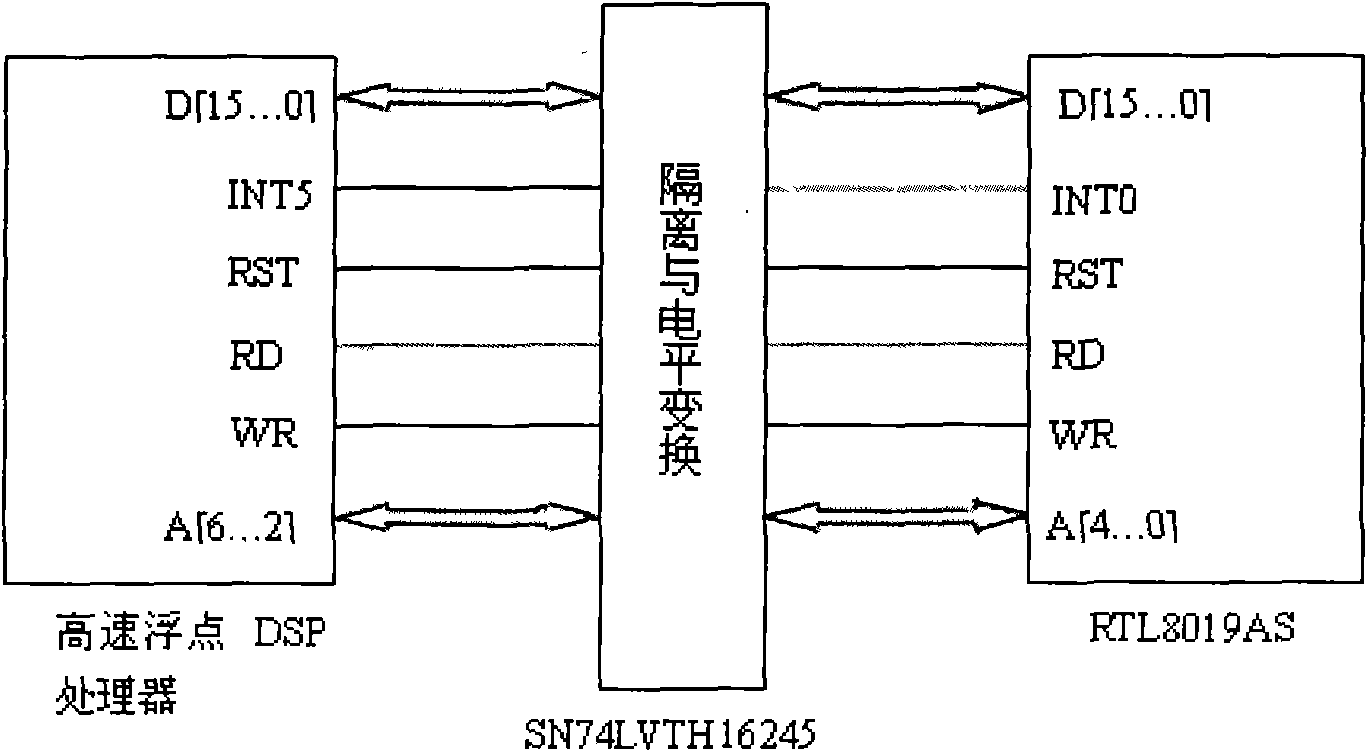

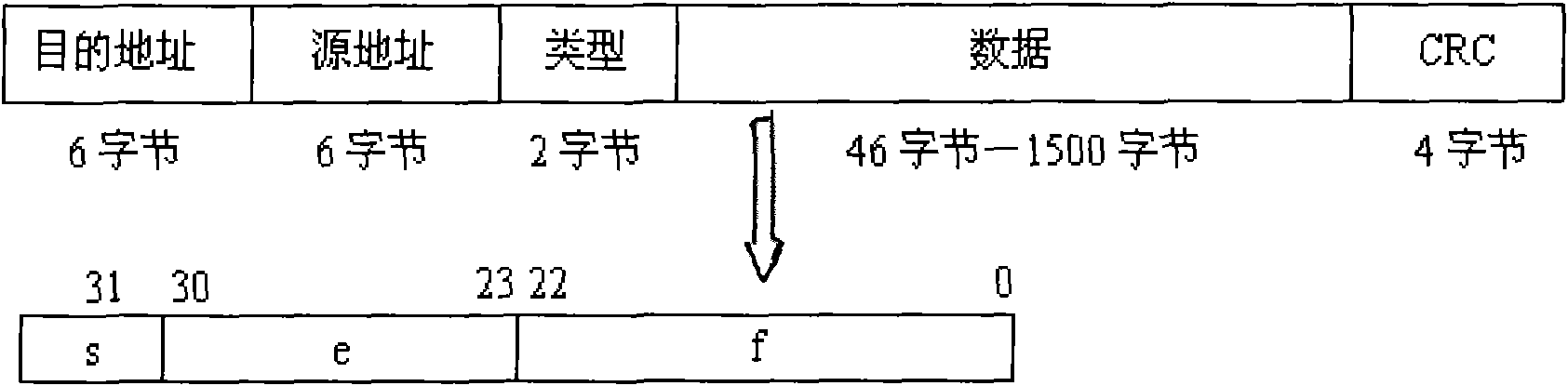

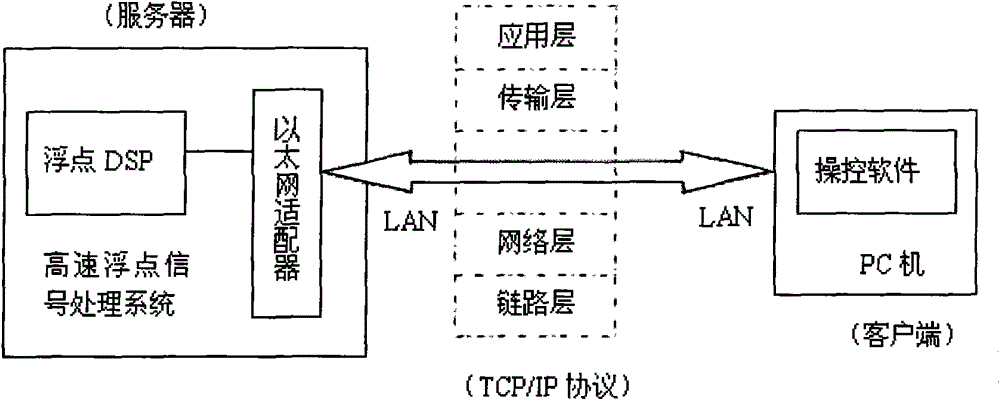

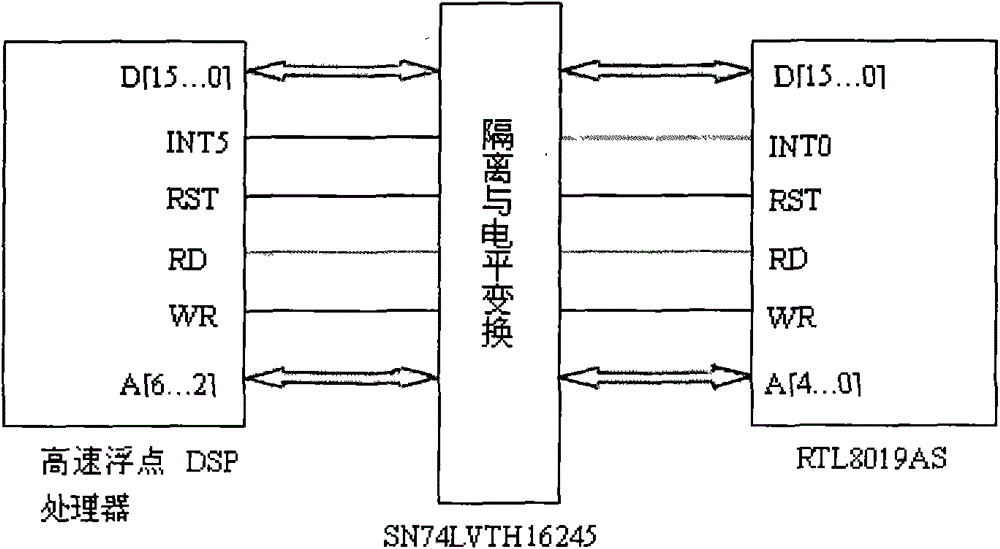

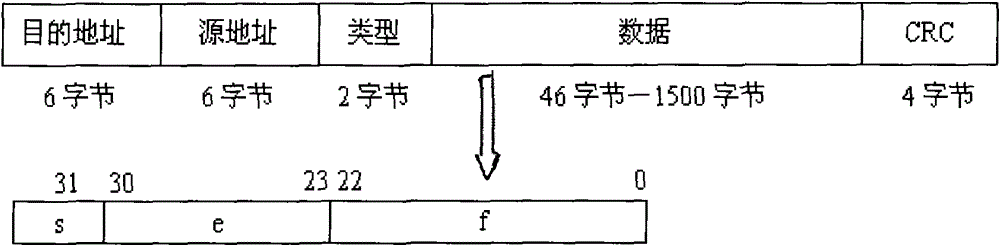

Technology for realizing Ethernet interface and TCP/IP protocol for high-speed floating point DSP processor

InactiveCN101594364AImplement the underlying driverTransmissionSpecific program execution arrangementsComputer programmingData transmission

The invention provides an Ethernet interface proposal for a high-speed floating point DSP processor aiming at characteristics thereof, and efficiently realizes the TCP / IP protocol on the DSP high-speed floating point processor. The technology comprises hardware logic design of an interface, bottom drive realization of an Ethernet adapter, realization of the TCP / IP protocol on the floating point DSP processor and communication program design of an upper computer. The technology solves the problem that the high-speed floating point DSP processor cannot carry out high-speed data transmission. The technology has strong universality, and is applicable to any floating point processor.

Owner:ANHUI INST OF OPTICS & FINE MECHANICS - CHINESE ACAD OF SCI

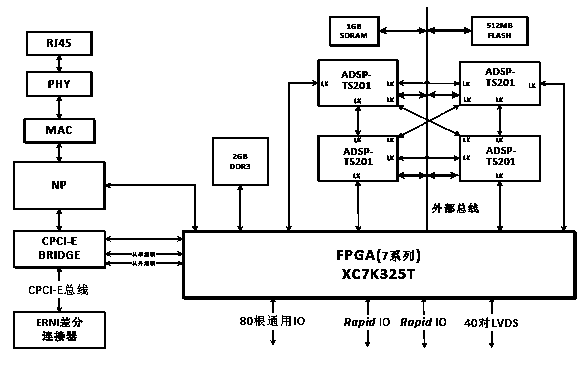

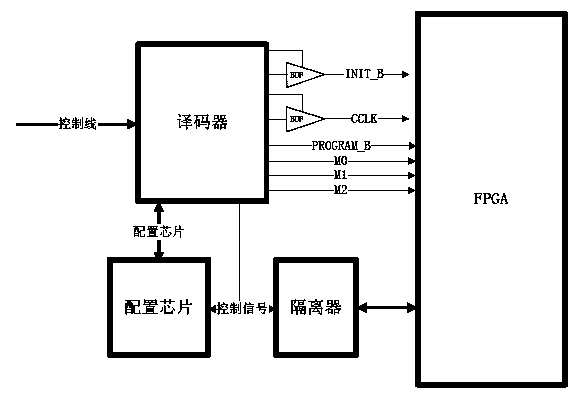

Multi-DSP parallel processing board based on CPCI-E bus

InactiveCN103885362AFast transmissionReduce volumeProgramme controlComputer controlParallel processingData transmission

The invention relates to the design architecture of a multi-DSP parallel processing board based on a CPCI-E bus. The multi-DSP parallel processing board comprises four TS201 floating point DSPs and an XC7K325TFPGA, wherein each DSP is connected with the other three DSPs through full duplex LINK ports, and the four DSPs are connected with a FPGA through data buses and full duplex LINK ports. The PFGA is connected with a CPCI-Express bridge through a self-defined high-speed interface. According to the multi-DSP parallel processing board, electrified free switching is achieved for the LINK port loading mode of a TS201 array and the passive and active loading modes of the FPGA through the CPCI-E bus, high-speed data transmission of a DSP processing array is achieved through the serial difference characteristics of the CPCI-E bus and the external cache of the FPGA, and the multi-DSP parallel processing board has the advantages of being high in bus transmission speed, small in size, flexible in interface method, large in onboard cache and high in expansibility.

Owner:CHENGDU ZHIHENG BONA TECH

SDINS/GPS combined guidance system time synchronism and synchronous data extraction method

InactiveCN100498232CHardware time synchronizationCompact hardwareInstruments for road network navigationPulse automatic controlGuidance systemData acquisition

Owner:BEIHANG UNIV

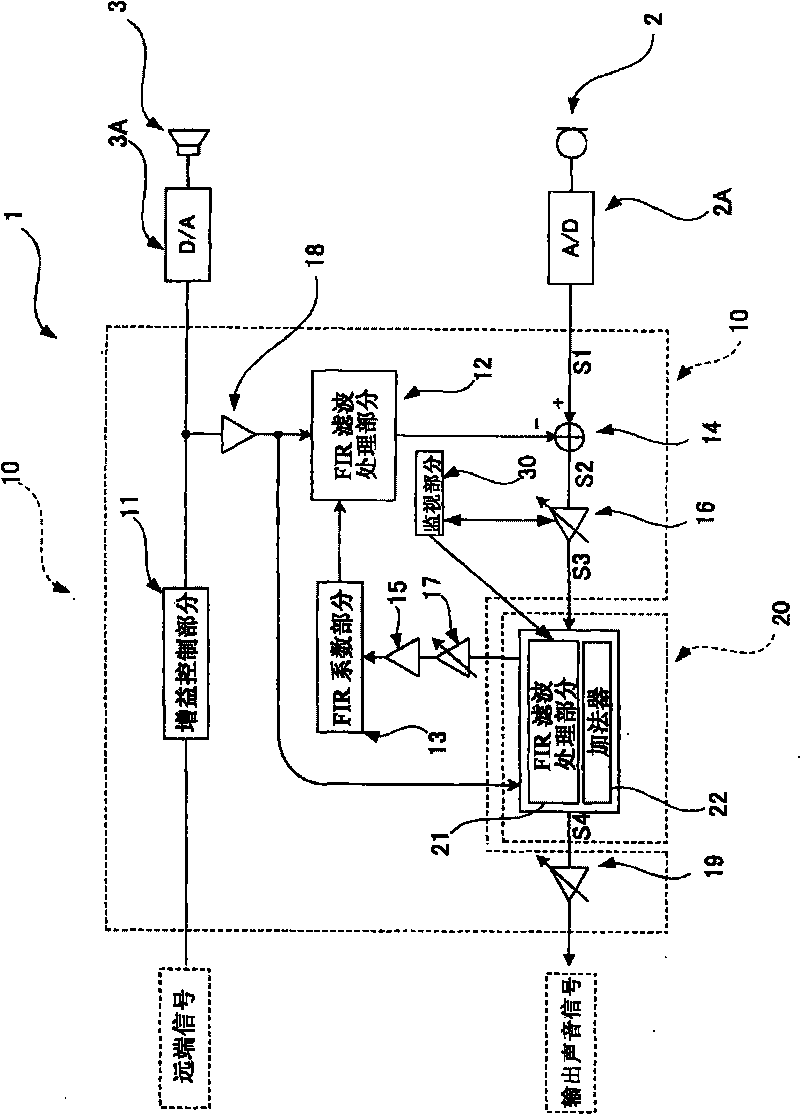

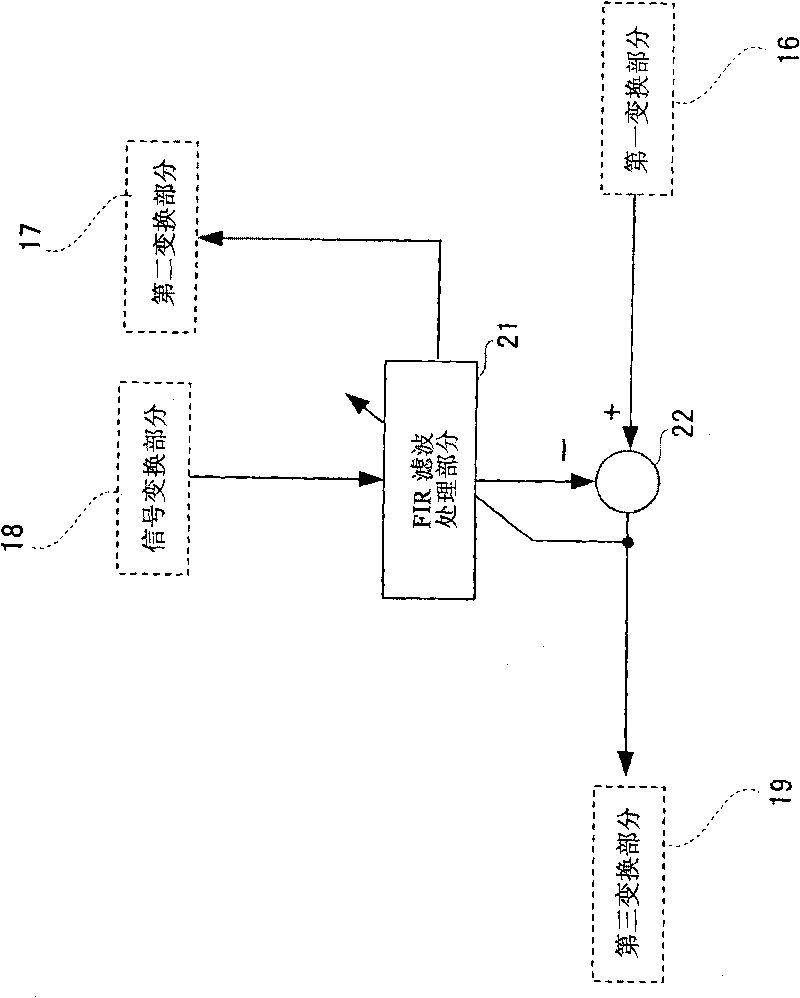

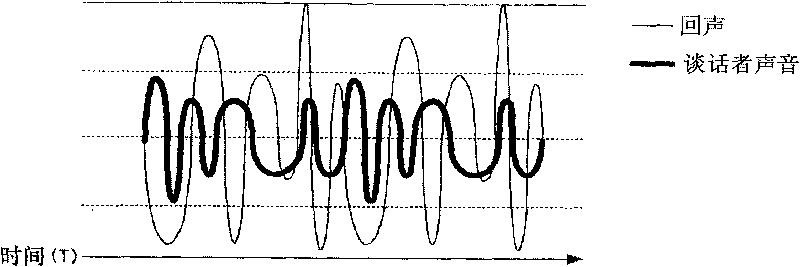

Echo canceller

InactiveCN101765982AInterconnection arrangementsSubstation speech amplifiersFixed point dspComputer science

It is an object to provide an echo canceller that can be configured to more effectively suppress an echo, with the suppression of increase in costs, than a case of filter processing carried out by a signal in the fixed point form. An echo canceller (1) is provided with a floating point DSP unit (10) and a fixed point DSP unit (20). The floating point DSP unit (10) is comprised of an FIR filter processing unit (12), an adder (14) and a first converting unit (16). The FIR filter processing unit (12) generates a pseudo echo signal in the floating point form and the adder (14) subtracts the pseudo echo signal from a collected sound signal to generate a first correction signal. The first converting unit (16) converts the first correction signal into the one in the fixed point form for the adjustment of a gain. The fixed point DSP unit (20) is comprised of a FIR filter processing unit (21) and an adder (22). The FIR filter processing unit (21) generates a pseudo echo signal in the fixed point form, and the adder (22) subtracts the pseudo echo signal from the first correction signal converted into the fixed point form to generate an output signal.

Owner:YAMAHA CORP

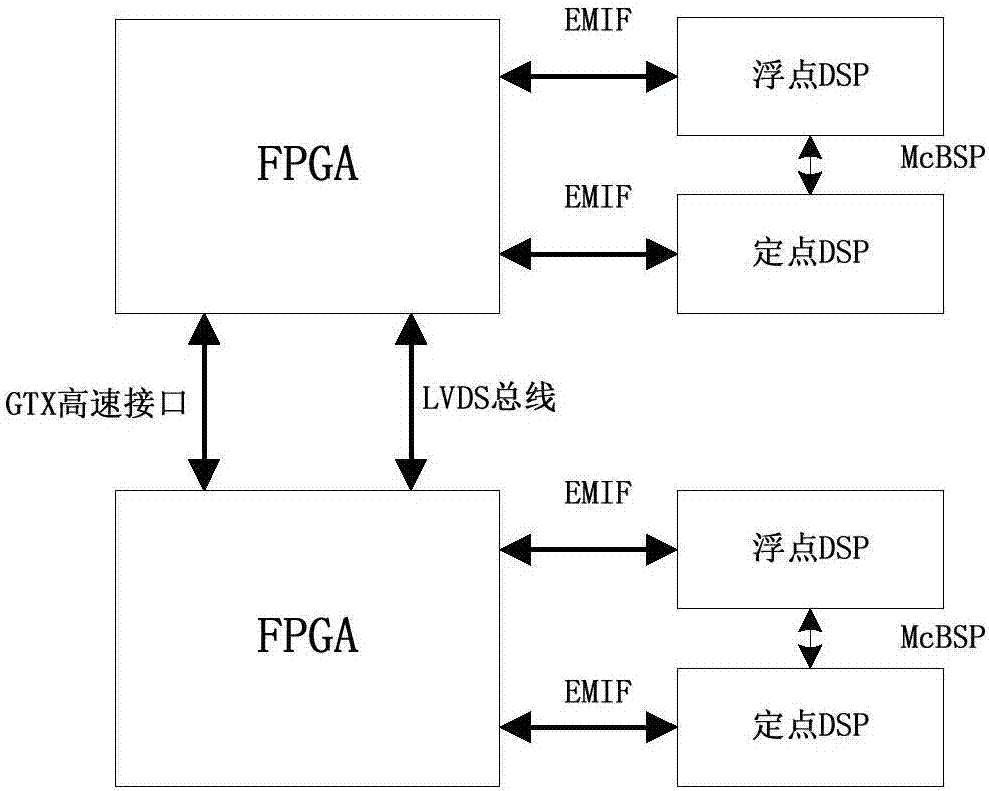

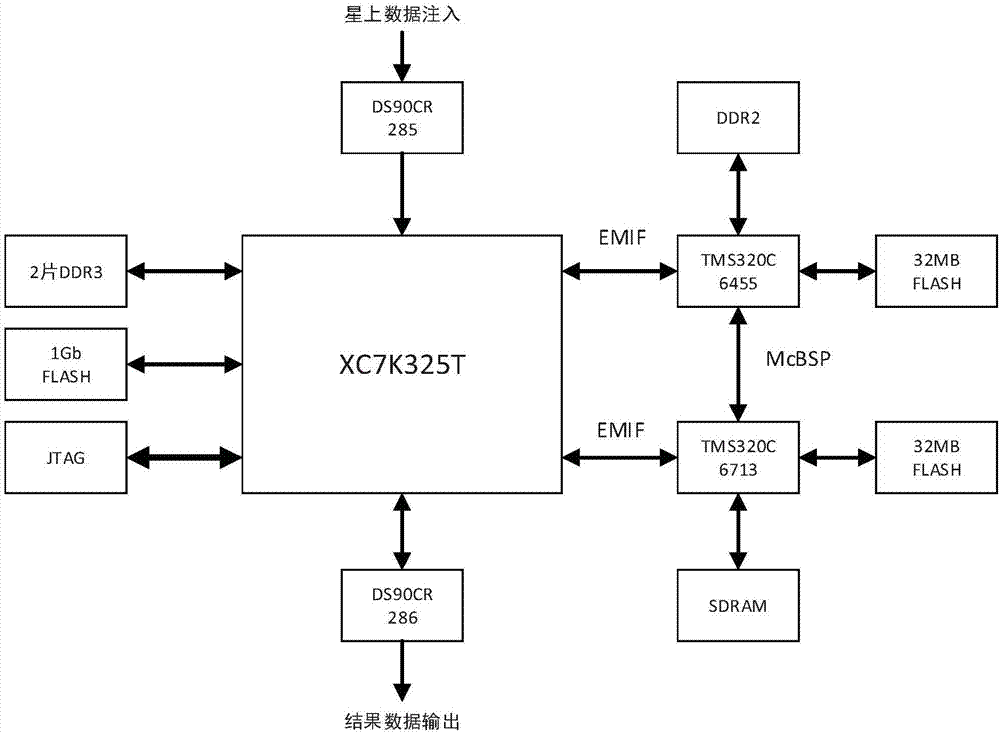

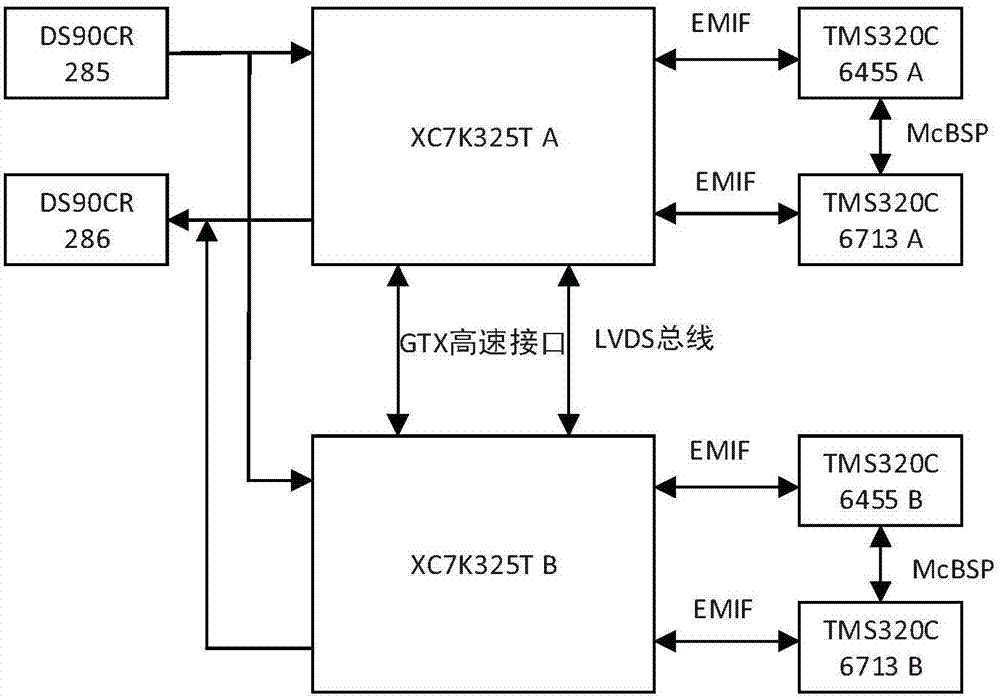

Simulation evaluation device for images processing on satellite

InactiveCN107967198AWide range of assessmentWide coverageFaulty hardware testing methodsFixed point dspImaging processing

The invention discloses a simulation evaluation device for images processing on a satellite. The device comprises fixed point DSPs, floating point DSPs, and FPGA and FPGA connected to the fixed pointDSPs and the floating point DSPs; the device is used for conducting simulation evaluation to the satellite images processing on the FPGA and a satellite borne ASIC, when conducting fixed point evaluation and floating point evaluation, the processing of images on the satellite is divided into fixed point processing and floating point processing, the fixed point processing is finished on the fixed point DSP, the floating point processing is finished on the floating point DSP, the FPGA is used for data interaction and synchronization between the fixed point processing and the floating point processing, finally, the operating performances of the fixed point and the floating point are obtained. At the same time, the processing structure of two FPGAs connected to the fixed point DSPs and the floating point DSPs, can simulate the redundant design of images processing system on the satellite. The simulation evaluation device for images processing on the satellite has an ability of multi-dimensional evaluation of images processing on the satellite, and the advantages of big evaluation range and wide coverage.

Owner:HUAZHONG UNIV OF SCI & TECH

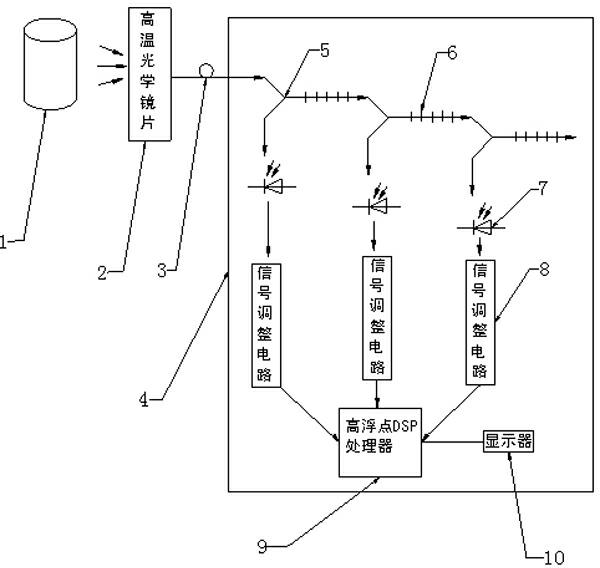

Device and method for measuring multi-FBG (fiber bragg grating) colorimetric transient temperature

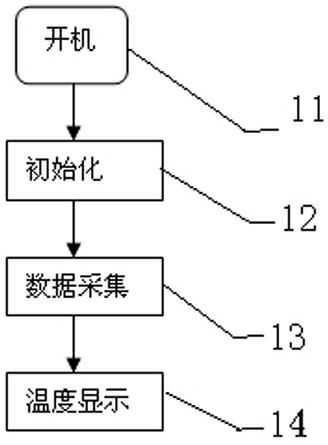

InactiveCN102692283AQuick responseSuitable for long-distance non-contact high temperature measurementThermometers using physical/chemical changesInternal memoryGrating

The invention discloses a temperature measuring method, comprising the following steps: (1) a high temperature optical lens picking up infrared radiation lights on a surface of a high temperature object, (2) transferring the infrared radiation lights to a control room through optical fibers, (3) in the control room inputting the optical fibers into a fiber bragg grating (FBG) optical grating through an input end of an Y type optical splitter, outputting the light reflected by the FBG optical grating through an output end of the Y type optical splitter and outputting to a detector (4), converting light signals reflected by each stage of the FBG optical grating into weak electronic signals by a corresponding avalanche photo diode (APD) infrared detector, inputting the electronic signals after regulated by a signal regulation circuit into an A / D conversion module of a high-speed floating point digital signal processor (DSP), (5) the high-speed floating point DSP performing filtration, colorimetric computation, temperature lookup, temperature fitting to the data of the A / D conversion module, and finally displaying the temperature in a curve manner on a liquid crystal displayer, thus the detection being more accurate and intuitive.

Owner:TAIYUAN UNIVERSITY OF SCIENCE AND TECHNOLOGY

System for data acquisition and signal treatment of testing flat wheel

InactiveCN101206162BHigh precisionImprove efficiencyRailway vehicle testingInput/output processes for data processingProgrammable logic deviceData acquisition

Owner:HARBIN ENG UNIV

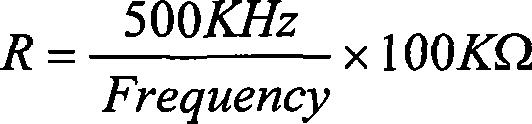

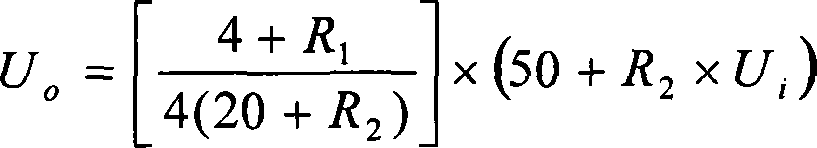

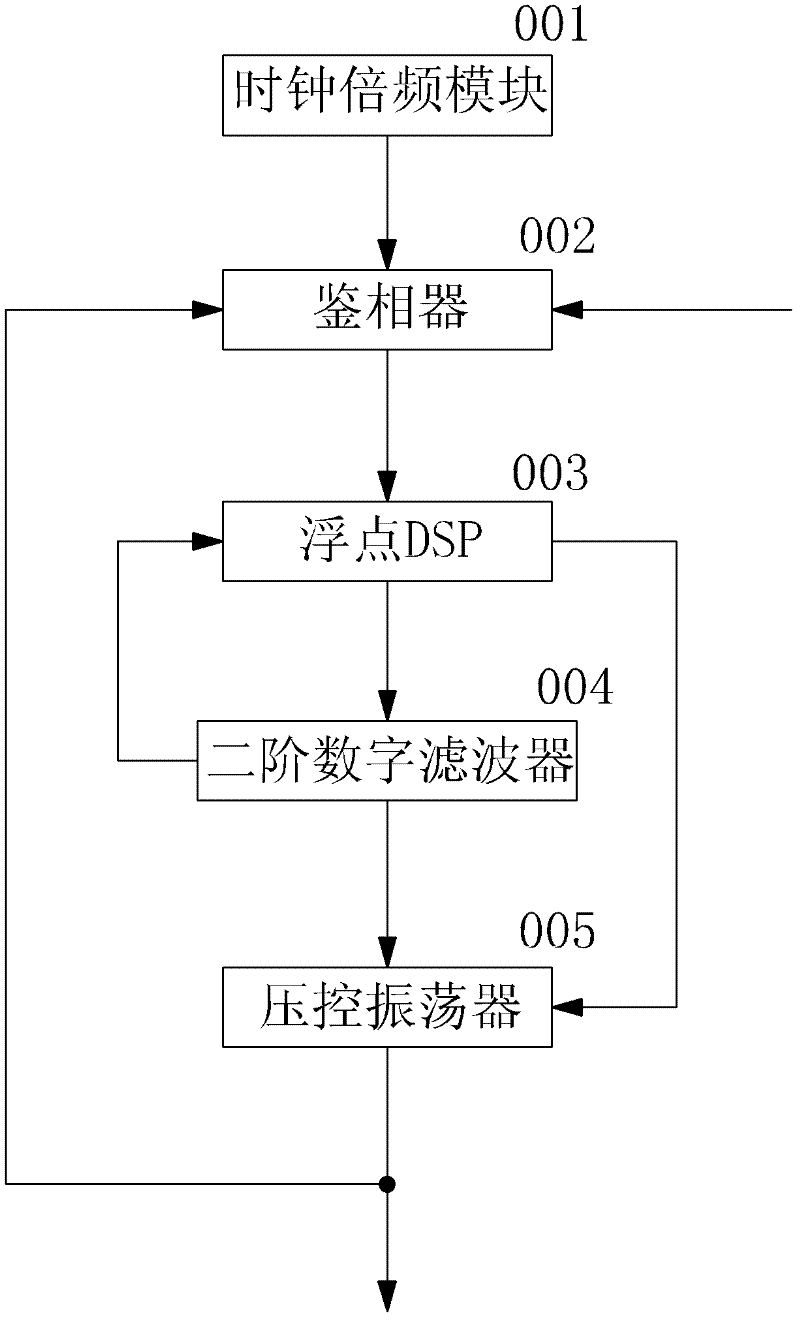

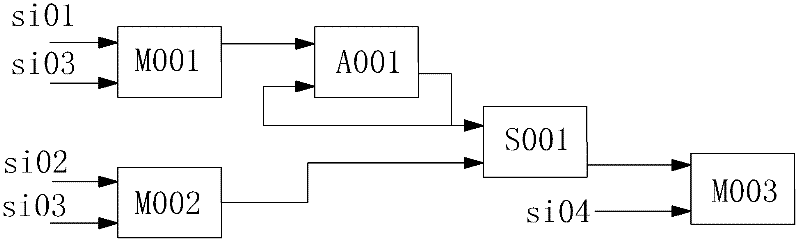

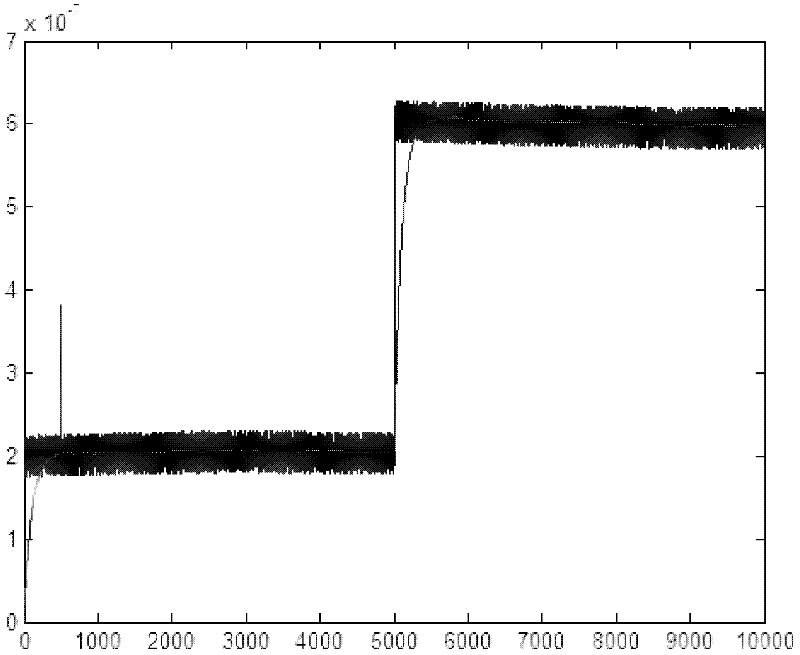

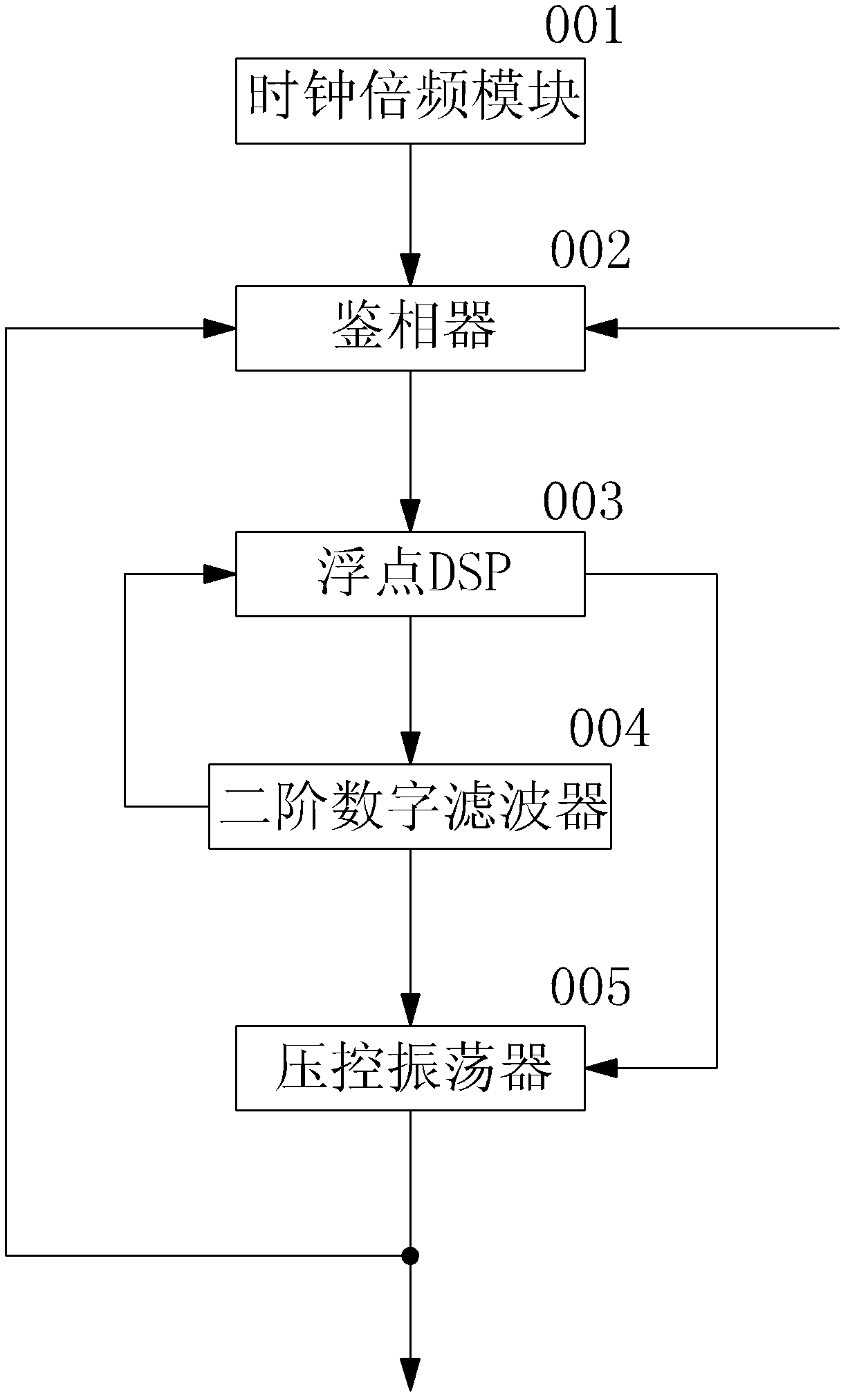

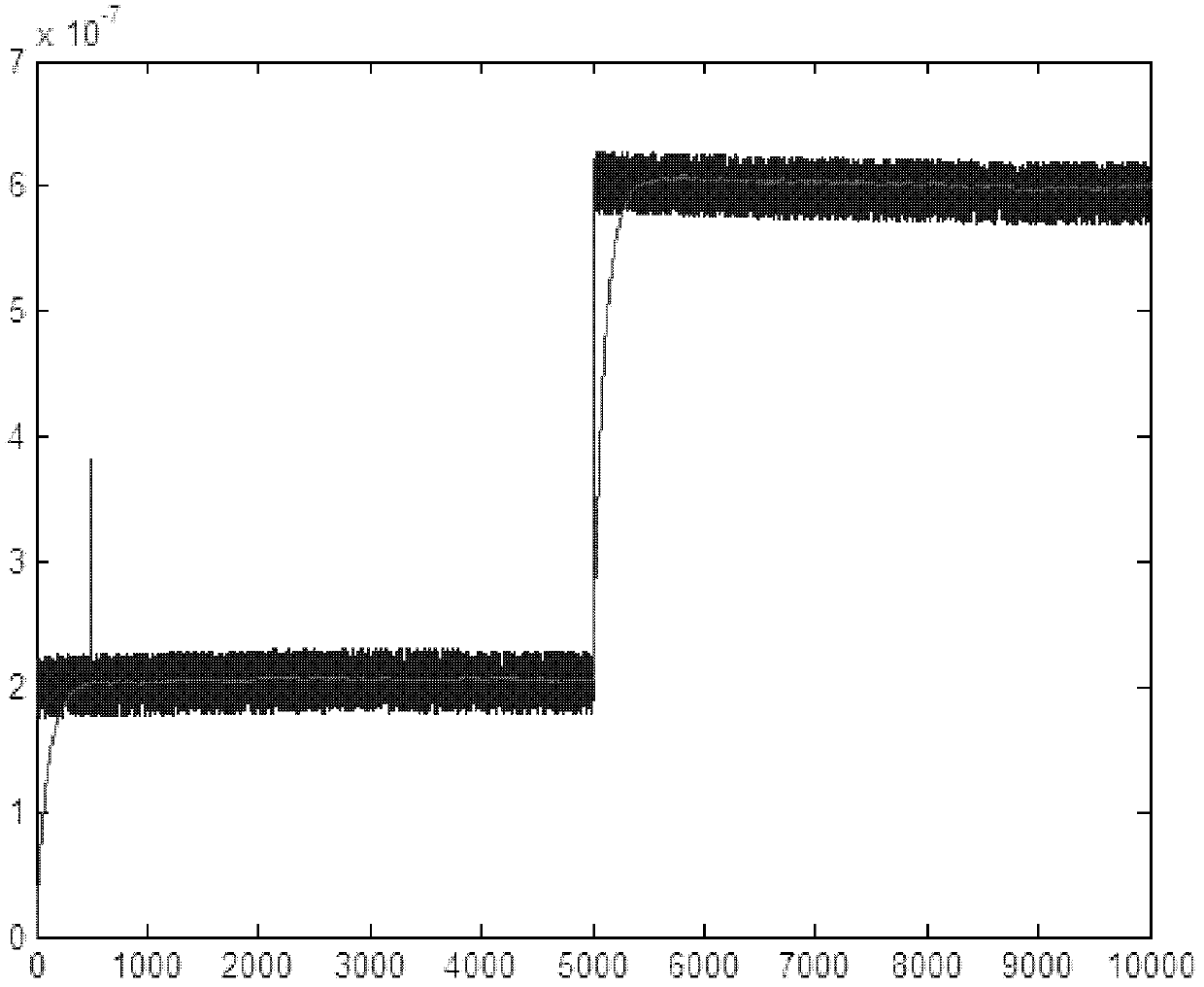

1PPS (pulse per second) latch and control method

ActiveCN102346443AImprove stabilitySmooth changeDigital technique networkSimulator controlDiscriminatorPhase difference

The invention discloses a 1PPS (pulse per second) latch which comprises a clock frequency multiplication module, a phase discriminator, a floating point DSP (digital signal processor), a two-order digital filter and a voltage-controlled oscillator. The satellite 1PPS and local 1PPS input by a receiver are subjected to phase discrimination; the phase difference output by the digital phase discriminator is subjected to data type conversion and then output to the two-order digital filter; the result output by the two-order digital filter is subjected to data type conversion and then output to the voltage-controlled oscillator; and the voltage-controlled oscillator generates local 1PPS. The invention also provides a control method using the latch.

Owner:北斗天汇(北京)科技有限公司

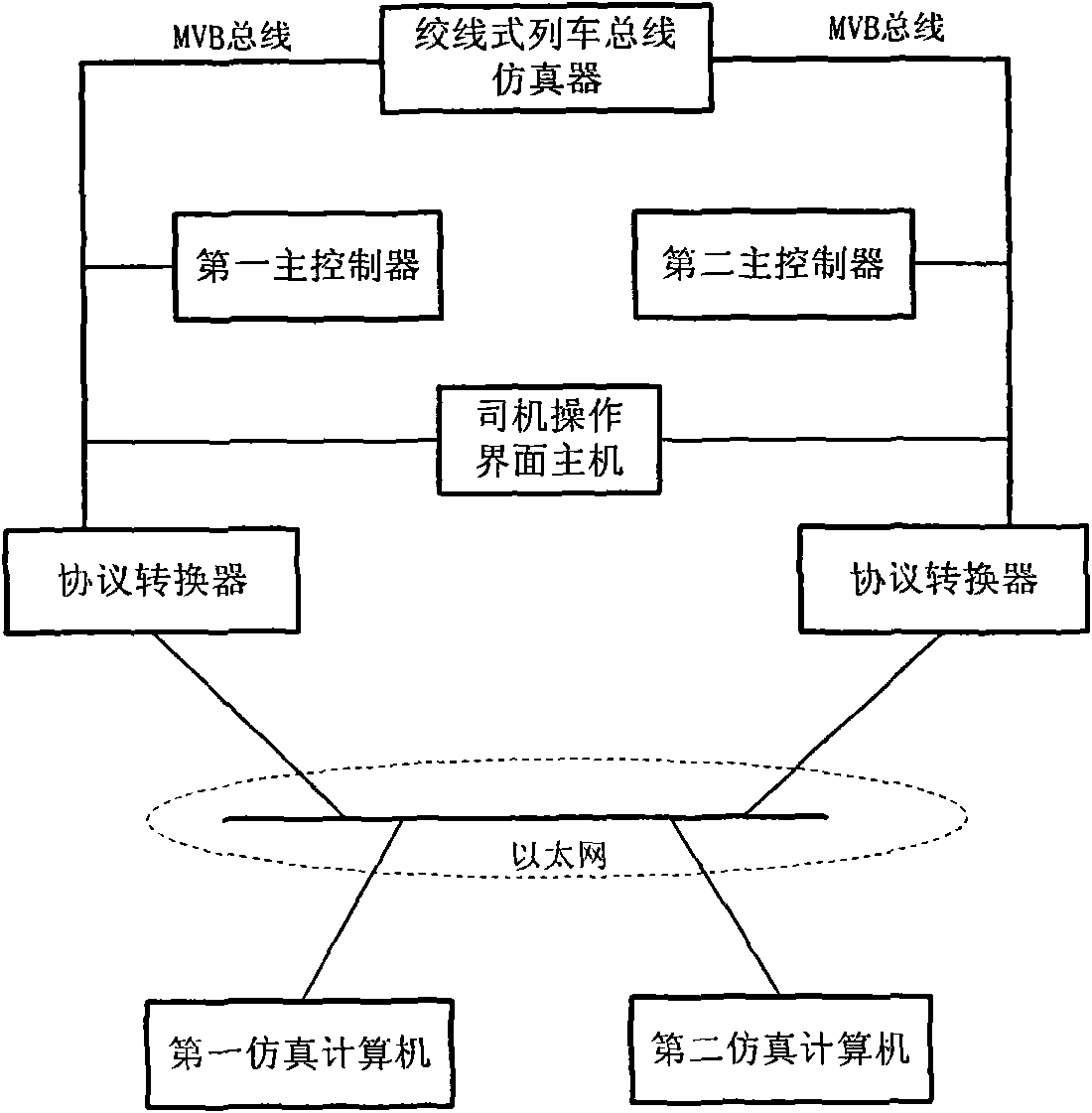

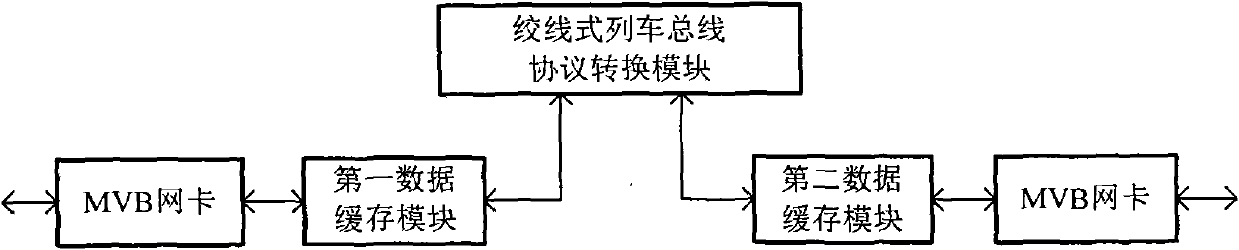

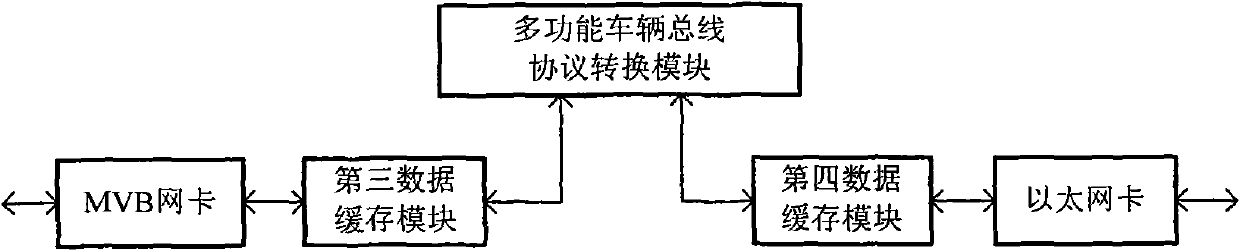

Simulation device for network control logic verification of motor train unit

ActiveCN102075523BConvenient verificationImprove verification efficiencyTransmissionEthernet protocolNetwork control

The invention relates to a simulation device for network control logic verification of a motor train unit, and belongs to the technical field of traffic control. The simulation device comprises first and second master controllers, a wire train bus simulator, a driver operating interface host, first and second protocol converters, and first and second simulation computers. The master control unitsof the device are realized by adopting a high-performance floating point digital signal processor (DSP) of target identification (TI) and mount two multifunctional vehicle buses respectively; a wire train bus is realized through a simulator to connect the two multifunctional vehicle buses, and realizes data transceiving function under a wire train bus protocol on the interior; the interaction of the master control units and the motor train unit equipment is realized by adopting an Ethernet, a personal computer (PC) machine is further accessed to the Ethernet through an Ethernet card, and conversion of a multifunctional vehicle bus protocol and an Ethernet protocol is realized in the PC machine; and finally, the PC machine of the simulation motor train unit equipment is accessed to the Ethernet. The device has high verification efficiency, strong reusability and low cost, and is convenient to maintain.

Owner:北京协同创新轨道交通研究院有限公司

Full digital driving controller of permanent magnetic linear voice coil motor used for direct driving valve

InactiveCN101576745BIncrease sampling rateHighly integratedAC motor controlElectric motor controlExtensibilityField programmable logic devices

The invention relates to a full digital driving controller of a permanent magnetic linear voice coil motor used for a direct driving valve, consisting of three parts: a digital controller, a power circuit and a signal detection circuit; the digital controller circuit comprises a 32-bit floating point DSP, a field programmable logic device FPGA and an external Flash ROM; the power circuit comprisesa high-speed optical coupling isolation circuit, and an H-bridge power main circuit consisting of intelligent power modules IPM; the signal detection circuit comprises an A / D converter, a multi-pathanalogue switch, a Hall current sensor used for detecting the moving coil winding current, a non-contact eddy current displacement sensor used for detecting the position of the moving coil and an amplification and active power filter circuit for analogue signals. The full digital driving controller of the permanent magnetic linear voice coil motor used for the direct driving valve has the advantages of high integration, good extensibility, high reliability, high frequency response and high precision.

Owner:BEIHANG UNIV

Method for carrying out IPPS signal control

InactiveCN105450219AImprove stabilitySmooth changePulse automatic controlDiscriminatorPhase difference

The invention discloses a method for carrying out IPPS signal control, and the method comprises the steps: inputting a satellite IPPS signal and a local IPPS signal into a phase discriminator; carrying out the floating point DSP data type conversion of a phase difference value outputted by the phase discriminator into a floating point type; carrying out second-order digital filtering modeling through matlab, achieving a filter structure with the adjustable coefficient in a second-order digital filter based an FPGA through the VHDL language, and carrying out the smoothing filtering of the phase difference value of the floating point type; carrying out the floating point DSP data type conversion of an output value of the second-order digital filter into an integral type through a floating point DSP; outputting the integral data to a digital voltage-controlled oscillator through the floating point DSP; adjusting the IPPS output phase through the voltage-controlled oscillator according to the input data; enabling the IPPS signal outputted by the voltage-controlled oscillator to serve as an input signal, and feeding back the signal to the phase discriminator.

Owner:王晓伟

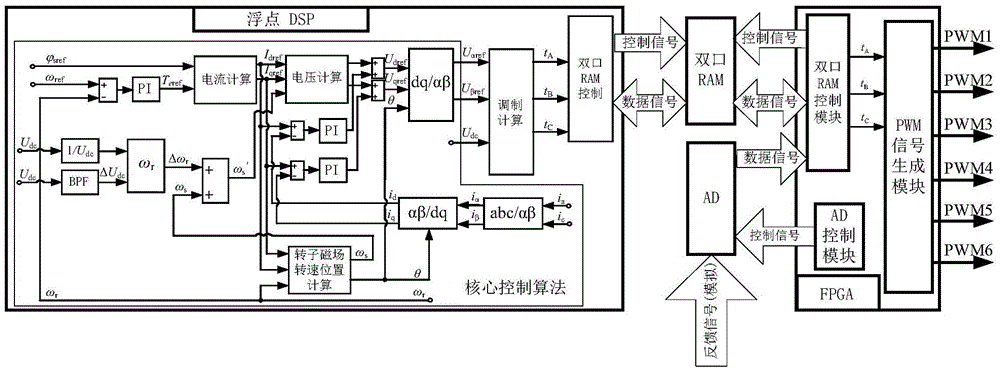

Regulating board of static var compensator based on floating point DSP and FPGA

ActiveCN100362443CImprove calculation accuracyHighly integratedFlexible AC transmissionReactive power adjustment/elimination/compensationElectromagnetic interferenceLogic gate

Owner:CHINA ELECTRIC POWER RES INST +1

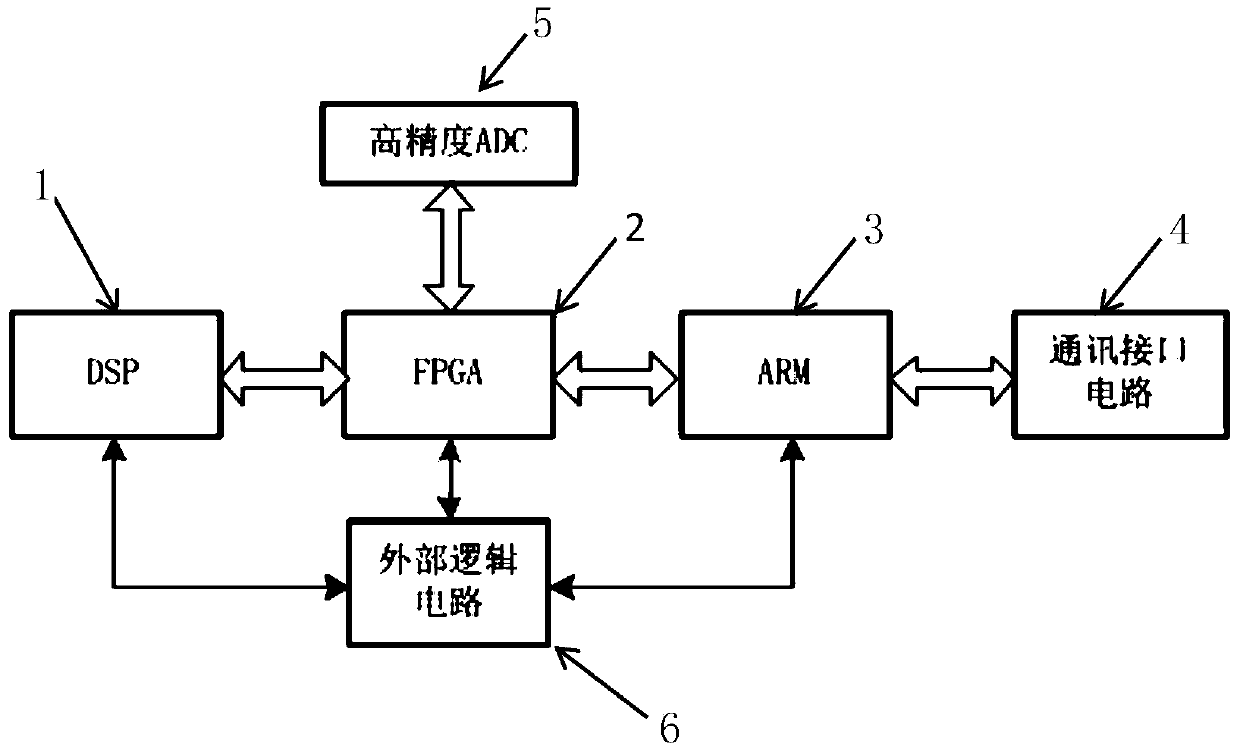

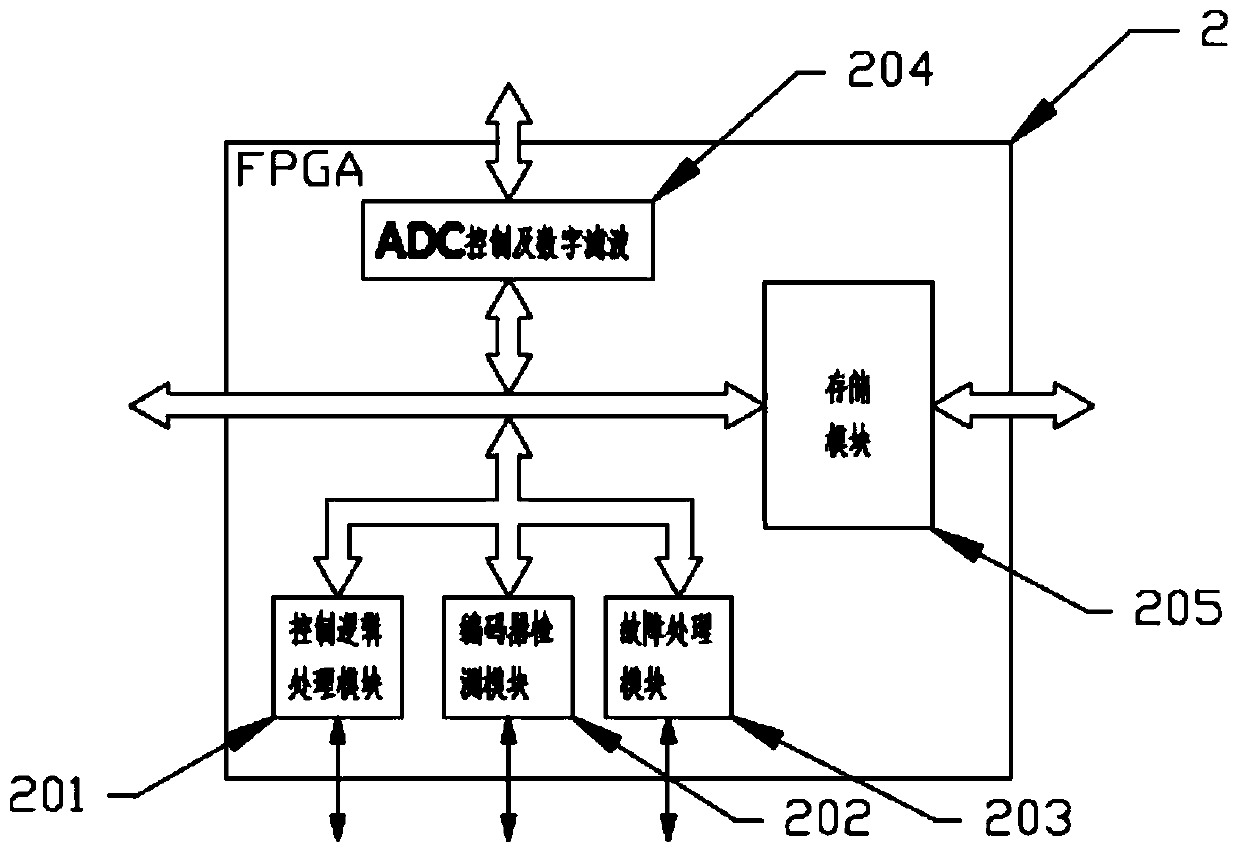

A high-performance inverter controller

ActiveCN105373041BClear division of laborTimely Implementation of Protection StrategiesProgramme controlComputer controlFrequency changerClosed loop

The invention provides a high-performance variable frequency controller, the controller adopts a floating-point DSP core (1), an FPGA core (2), and an ARM core (3) three-core framework, and the floating-point DSP core (1) is used to realize Various control algorithms of the motor, including VF control, open-loop vector control, and closed-loop vector control; the FPGA core (2) is used to realize various control logic processing of frequency converters, encoder speed measurement, fault handling, ADC control and digital filtering and the storage of frequency converter signals; the ARM core (3) is used to realize various communication protocols required by the frequency converter, including USB, SCI, SPI, CAN, SDIO, Ethernet; the floating-point DSP core (1) and Between the FPGA cores (2) and between the FPGA cores (2) and the ARM cores (3), a bus connection is used, and between the floating-point DSP cores (1) and the ARM cores (3) are carried out by the FPGA core (2). High speed parallel communication. Each MCU of the controller has a clear division of labor and can adapt to the communication needs of various advanced automated production lines.

Owner:WISDRI WUHAN AUTOMATION

1PPS (pulse per second) latch and control method

ActiveCN102346443BImprove stabilitySmooth changeDigital technique networkSimulator controlDiscriminatorPhase difference

The invention discloses a 1PPS (pulse per second) latch which comprises a clock frequency multiplication module, a phase discriminator, a floating point DSP (digital signal processor), a two-order digital filter and a voltage-controlled oscillator. The satellite 1PPS and local 1PPS input by a receiver are subjected to phase discrimination; the phase difference output by the digital phase discriminator is subjected to data type conversion and then output to the two-order digital filter; the result output by the two-order digital filter is subjected to data type conversion and then output to the voltage-controlled oscillator; and the voltage-controlled oscillator generates local 1PPS. The invention also provides a control method using the latch.

Owner:北斗天汇(北京)科技有限公司

Portable vibration controller by adopting USB interface

InactiveCN100465830CEasy to moveEasy to carryComputer controlSimulator controlChannel dataVibration control

The present invention relates to a portable vibration controller adopting USB interface. Said portable vibration controller includes the following several portions: dual-channel data acquisition module, signal processing module, data storage module, signal output module, logic control module and USB communication module. Said invention is simple in structure and is high in accuracy.

Owner:SHANGHAI UNIV

Technology for realizing Ethernet interface and TCP/IP protocol for high-speed floating point DSP processor

InactiveCN101594364BImplement the underlying driverTransmissionSpecific program execution arrangementsComputer programmingData transmission

The invention provides an Ethernet interface proposal for a high-speed floating point DSP processor aiming at characteristics thereof, and efficiently realizes the TCP / IP protocol on the DSP high-speed floating point processor. The technology comprises hardware logic design of an interface, bottom drive realization of an Ethernet adapter, realization of the TCP / IP protocol on the floating point DSP processor and communication program design of an upper computer. The technology solves the problem that the high-speed floating point DSP processor cannot carry out high-speed data transmission. The technology has strong universality, and is applicable to any floating point processor.

Owner:ANHUI INST OF OPTICS & FINE MECHANICS - CHINESE ACAD OF SCI

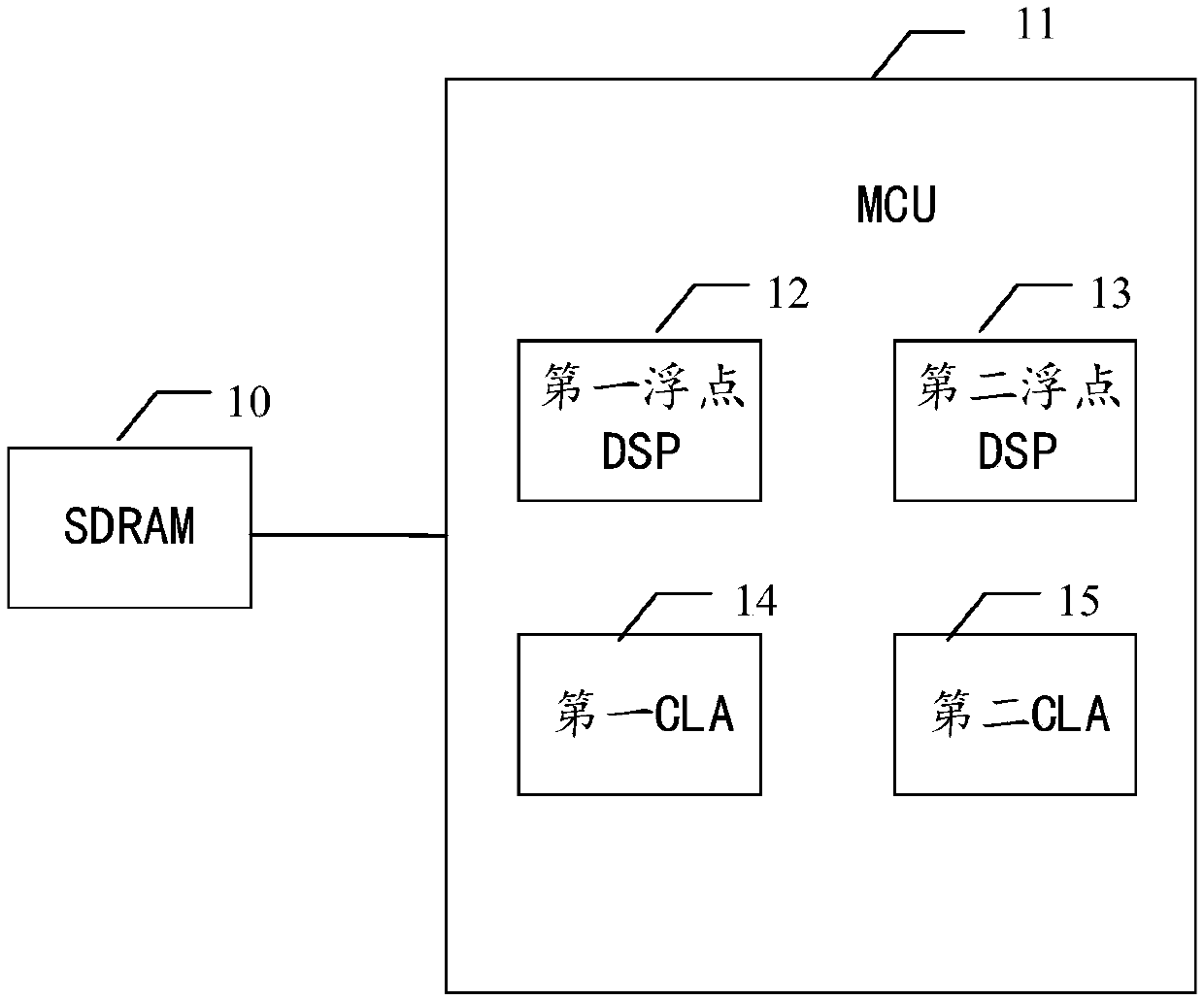

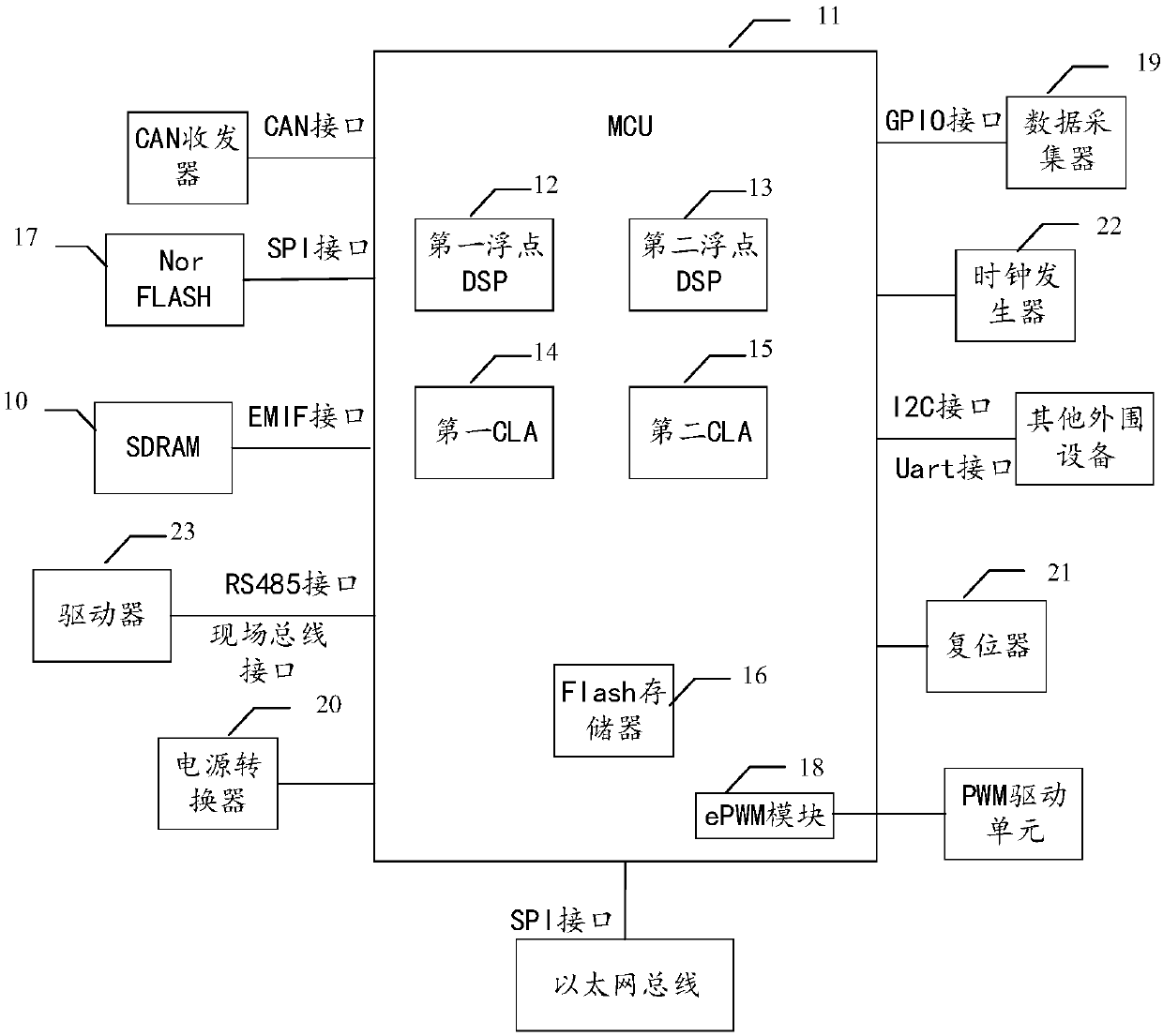

Frequency converter controller

PendingCN110568781AProcessing speedImprove throughputProgramme controlComputer controlFrequency changerVariable-frequency drive

The invention discloses a frequency converter controller comprising the following parts of an SDRAM for buffering input signals and / or output signals; and an MCU connected to the SDRAM for processingthe input signals and / or output signals, wherein the MCU comprises a first floating point DSP and a second floating point DSP for algorithmically controlling the input signals and / or output signals; and a first CLA and a second CLA for logically controlling the input signals and / or output signals. It can be seen that by embedding two floating point DSPs and two CLAs in the MCU of the frequency inverter controller, the processing speed of the input signals and / or output signals of the controller can be greatly improved, and the buffering of the input signals and / or output signals by the SDRAM greatly improves the controller's throughput of interactive data, thereby solving the problems of slow data processing speed and low throughput during the data interaction process of the frequency inverter controller in the prior art.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

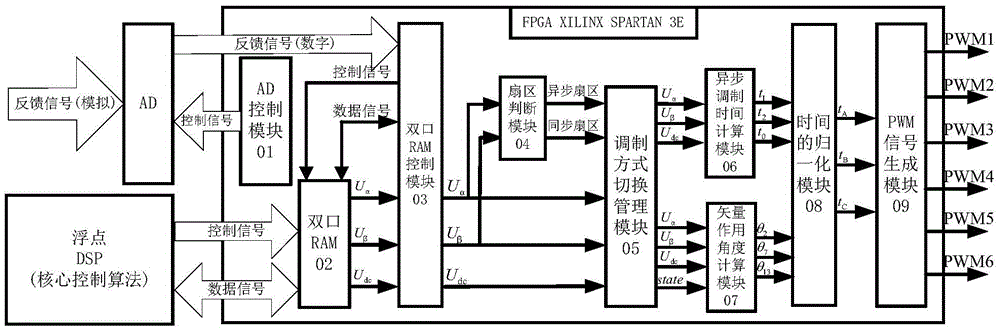

Low Carrier Ratio Online Computing Multi-mode Space Vector Pulse Width Modulation Soft Core

ActiveCN103956951BAdapt to external complex conditionsGood smooth switching abilityElectronic commutation motor controlAC motor controlCarrier signalAlternating current

The invention discloses a low-carrier-wave-ratio on-line computation multi-mode space vector pulse width modulation soft core which can complete on-line computation multi-mode space vector pulse width modulation in a high-power three-phase alternating current asynchronous motor control system. The low-carrier-wave-ratio on-line computation multi-mode space vector pulse width modulation soft core mainly comprises an AD control module 01, a double-port RAM 02 based on FPGA, a double-port RAM control module 03, a section judgment module 04, a modulation mode switchover management module 05, an asynchronous modulation time computation module 06, a vector action angle computation module 07, a time normalization module 08 and a PWM signal generation module 09. The low-carrier-wave-ratio on-line computation multi-mode space vector pulse width modulation soft core not only has the advantages of high speeds and high reliability of a hardware circuit, but also has good module reusability and transportability, and is good in steady-state performance and dynamic-state performance. When serving as a motor control system coprocessor, the low-carrier-wave-ratio on-line computation multi-mode space vector pulse width modulation soft core liberates a core controller (a floating point DSP) from a large amount of sine and cosine computation and periodic events occupying too many resources, better runs a motor core control algorithm and improves the performance of the control system.

Owner:SOUTHWEST JIAOTONG UNIV

Novel automatic device

InactiveCN105867234AAchieve protectionReduce wasteProgramme controlComputer controlSingle chipDual-ported RAM

The invention relates to a novel automatic device, and belongs to the technical field of automation. The novel automatic device comprises a protective CPU and a control CPU, wherein the protective CPU is used for completing the protection function of the automatic device, and the control CPU is used for completing the control function of the automatic device. A 32-bit floating point DSP TMS320C32 chip of the TI company is adopted in the protective CPU, a 32-bit Samsung S3C44B0X processor based on an ARM kernel is adopted in the control CPU, and the protective CPU and the control CPU are in communication connection through a dual-port RAM and a CPLD single chip microcomputer. The device is simplified, function repetition of some components is avoided, hardware resource waste is reduced, and reliability of the device is improved.

Owner:CHANGZHOU INST OF LIGHT IND TECH