Multi-DSP parallel processing board based on CPCI-E bus

A parallel processing and bus technology, applied in instruments, computer control, simulators, etc., can solve the problems of no TS201 application, high technical level requirements, difficulties, etc., to save the number of external wiring, small size, fast transmission speed Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

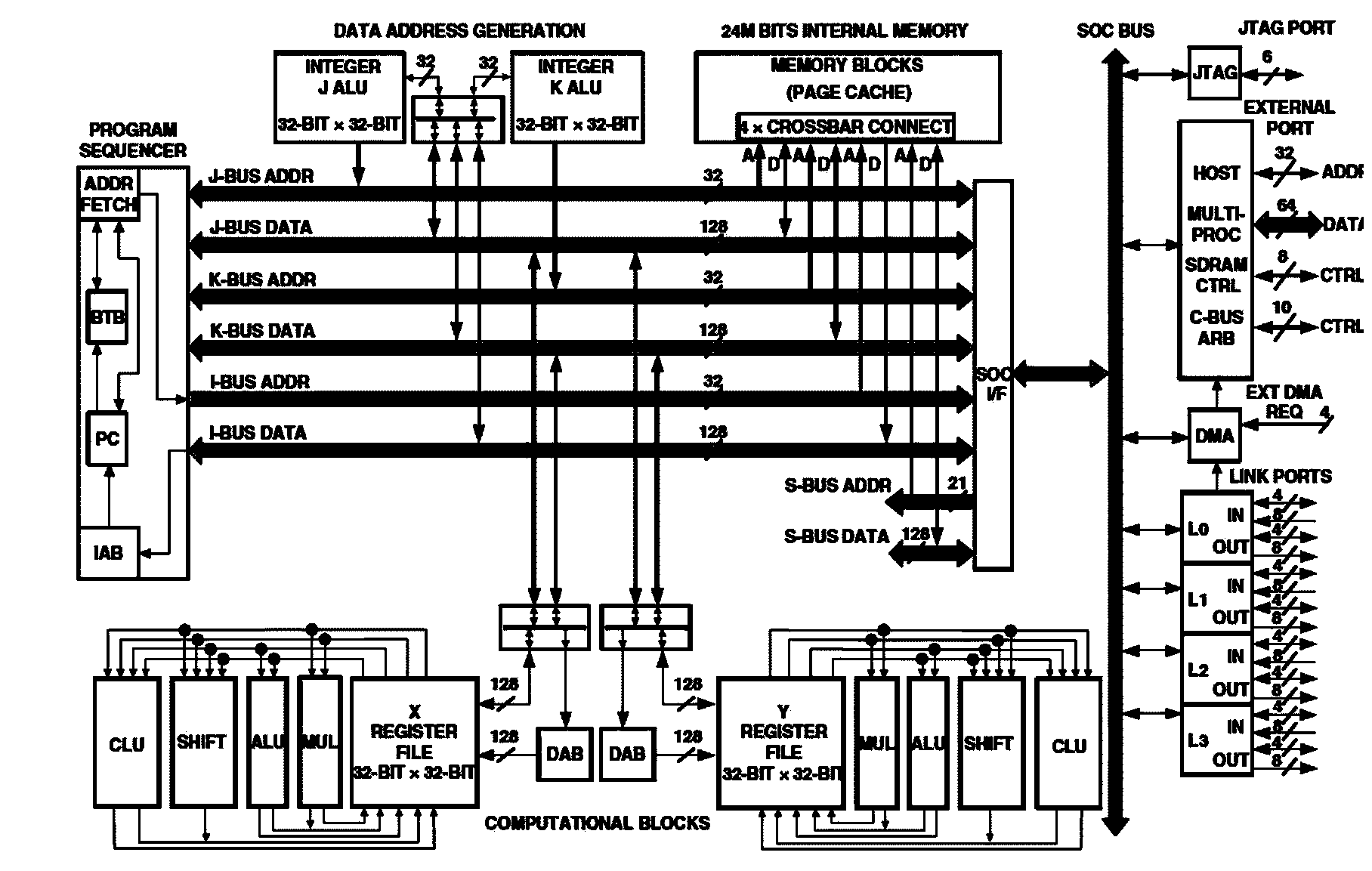

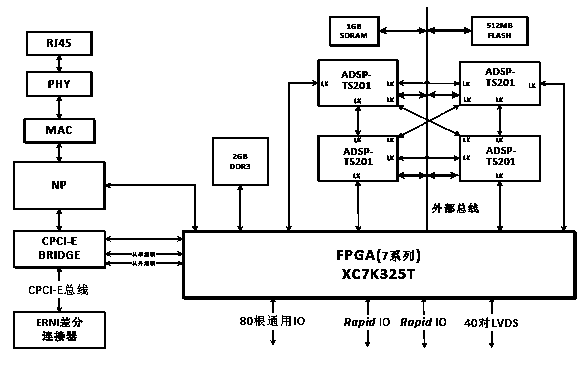

[0035] Such as figure 2As shown, the multi-DSP parallel processing board (model BN904) based on the CPCI-E bus includes four TigerSharc201 (ie TS201) floating-point DSP processors from ADI and one Xilinx 7 series XC7K325T FPGA, each TigerSharc201 floating-point The DSP processors communicate with the other three TigerSharc201 floating-point DSP processors through the LINK port (ie figure 2 Each TigerSharc201 floating-point DSP processor is connected to the other three TigerSharc201 floating-point DSP processors through the LINK port, and the four TigerSharc201 floating-point DSP processors are connected to the full-duplex LINK port through the data bus. Connect with the FPGA of XC7K325T; the FPGA of the XC7K325T is connected to the CPCI-Express bridge through a custom high-speed interface, the CPCI-Express bridge is connected to the NP (network processor) through the parallel expansion port, and the FPGA of the XC7K325T is also connected to four TigerSharc201 floating-point...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More