Full-chip interconnecting line power consumption optimum layout stage buffer planning method

An interconnection and buffer technology, applied in the field of interconnection design optimization, can solve the problems of increasing the complexity of power network design, random distribution of low-voltage modules, and inability to directly transplant.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

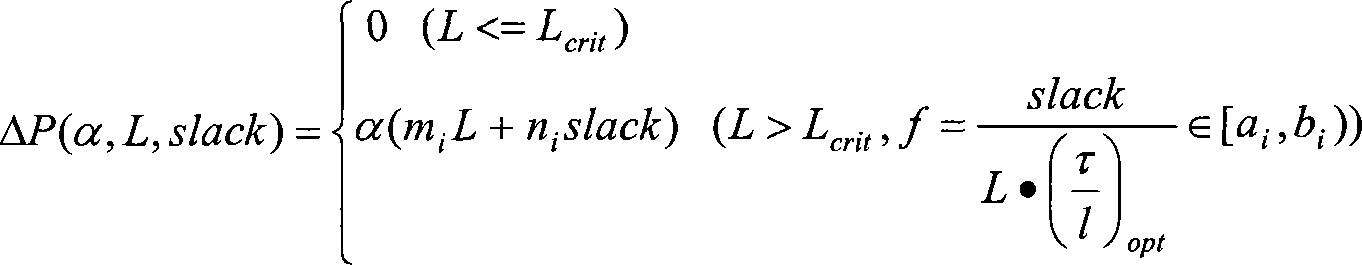

[0115] This part takes n30 in the international benchmark test circuit example GSRC as an example, adopts .18um process parameters, and explains the present invention according to the steps described above.

[0116] The following table shows the definitions and values of some process-related parameters:

[0117] Table 1: List of Process Parameters

[0118] r

Wire resistance per unit length (Ω / μm)

0.008

c

Line capacitance per unit length (fF / μm)

0.269

V DD

1.8

f clk

Working frequency(GHz)

1.2

c 0

Buffer Input Capacitance per Unit Size (fF)

1.9

r s

Unit Size Buffer Output Resistance (Ω)

36300

c p

Buffer Output Capacitance per Unit Size (fF)

4.8

I offn

Buffer leakage current per unit size (uA)

0.2

I short

Snubber short-circuit current per unit size (uA)

65

R d

Dri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More