HSDPA co-processor for mobile terminals

A technology for processing blocks and filters, applied in transmitter/receiver shaping networks, digital transmission systems, baseband system components, etc., can solve HSDPA increased design, inefficiency, difficulties, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

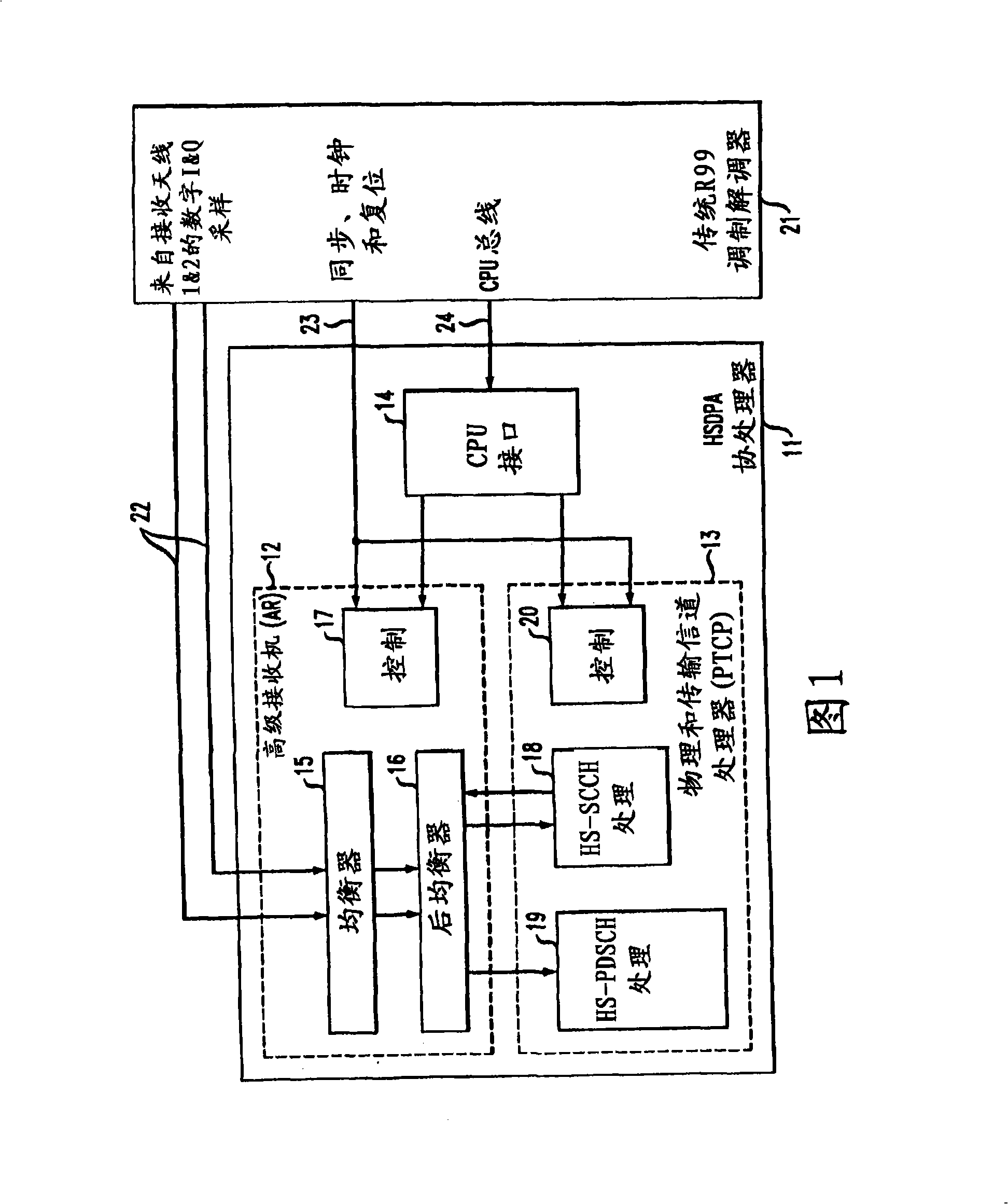

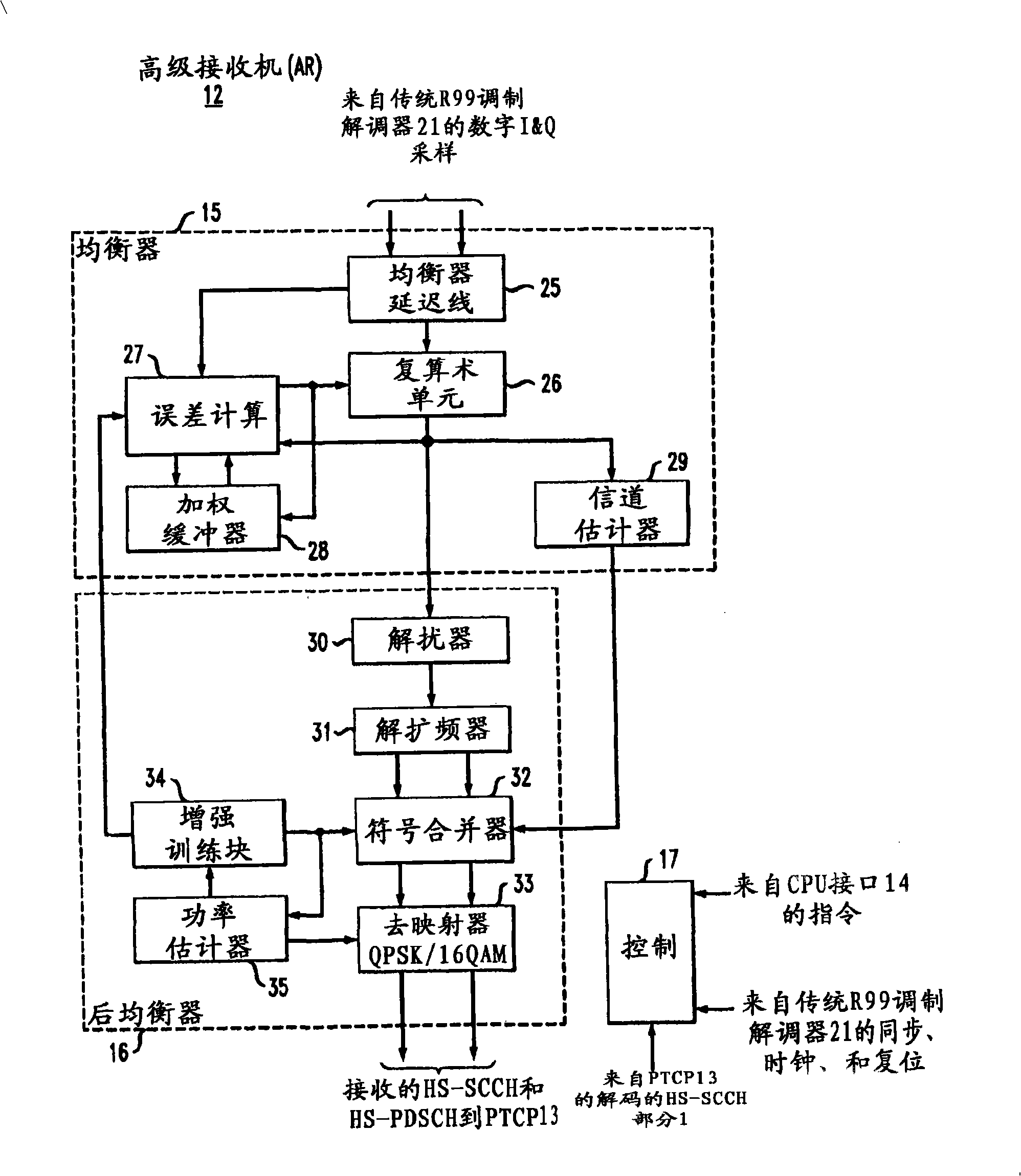

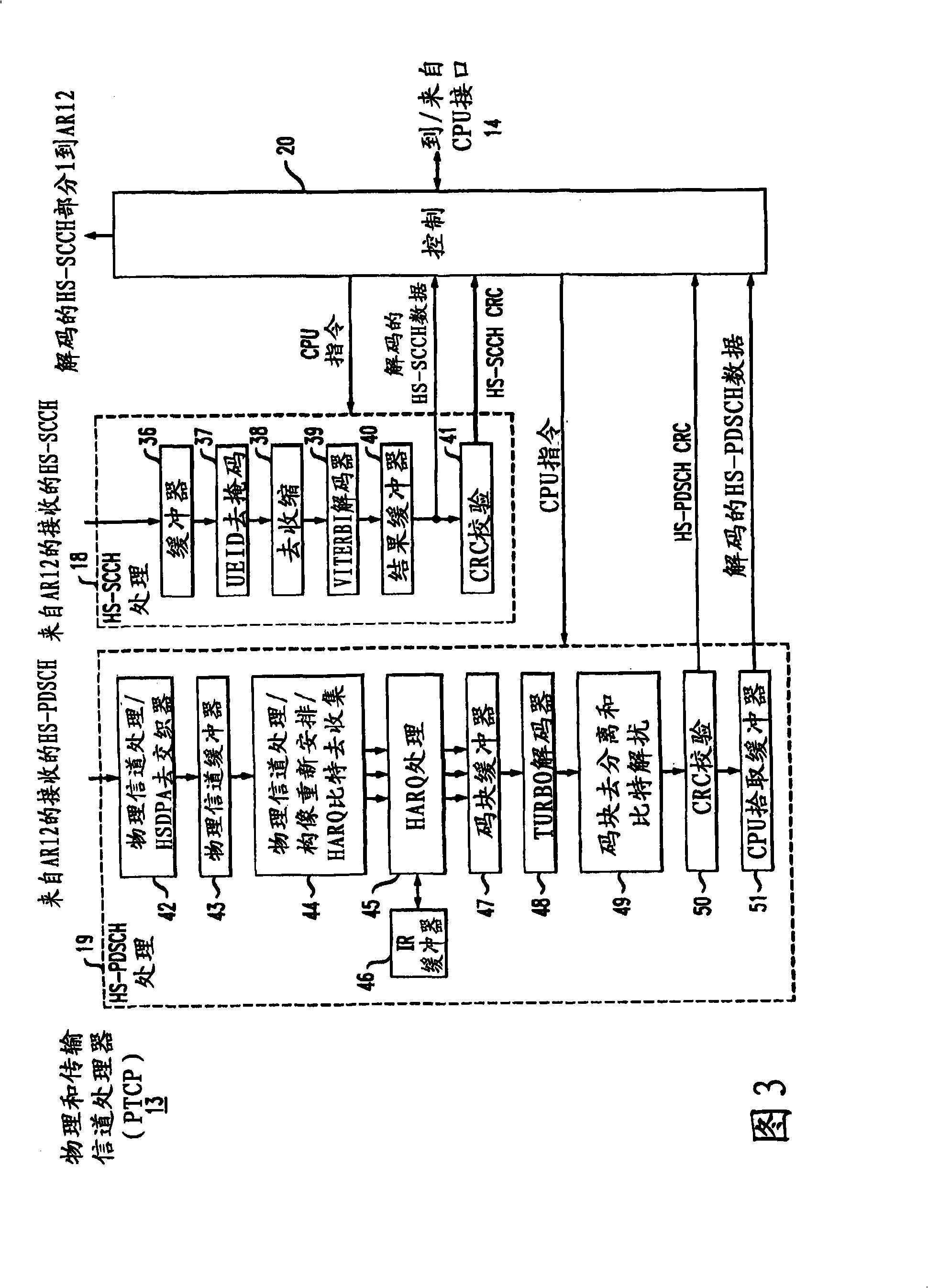

[0048] Figure 1 illustrates an exemplary HSDPA coprocessor 11 according to one embodiment of the present invention. The coprocessor 11 has two main functional hardware blocks, an advanced receiver (AR) 12 and a physical and transport channel processor (PTCP) 13 , and further includes a CPU interface 14 .

[0049] Coprocessor 11 performs all layer-1 (L1) digital baseband processing for HS-SCCH control channel and HS-PDSCH data channel and is designed to coexist with legacy R99 modem 21, which implements all HSDPA non-L1 functions described in the HSDPA standard . Legacy modem 21 provides all front-end support, including filtering, automatic frequency control, automatic gain control, multipath hunting, high-level interfaces, synchronization, and related functions. The legacy modem 21 also provides uplink (UL) support for transmitting the HS-DPCCH channel containing the CQI and ACK / NACK values determined by the coprocessor 11 .

[0050] The co-processor 11 has a hardware data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More