Method for loading on-site programmable gate array FPGA, apparatus and system

A gate array, loading unit technology, applied in CAD circuit design, special data processing applications, instruments, etc., can solve problems such as low efficiency and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

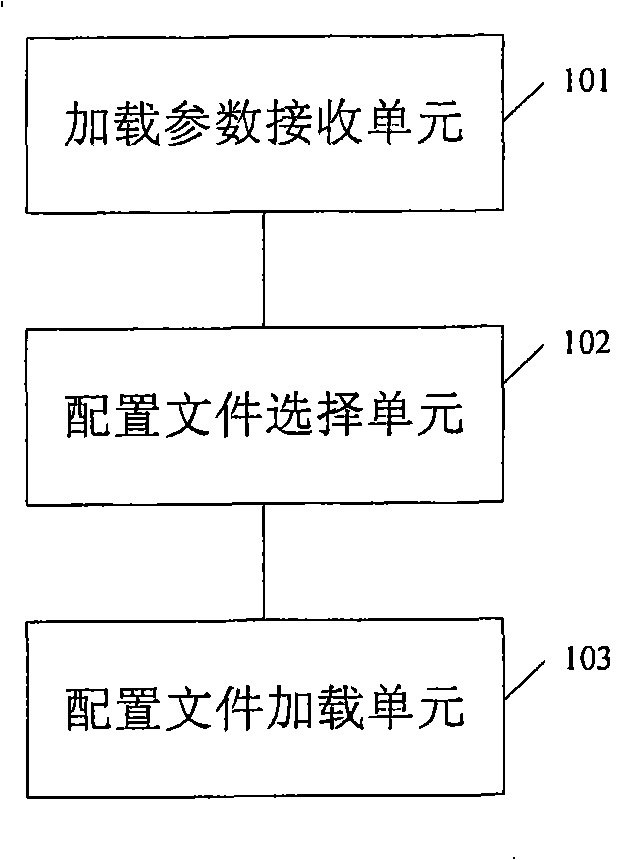

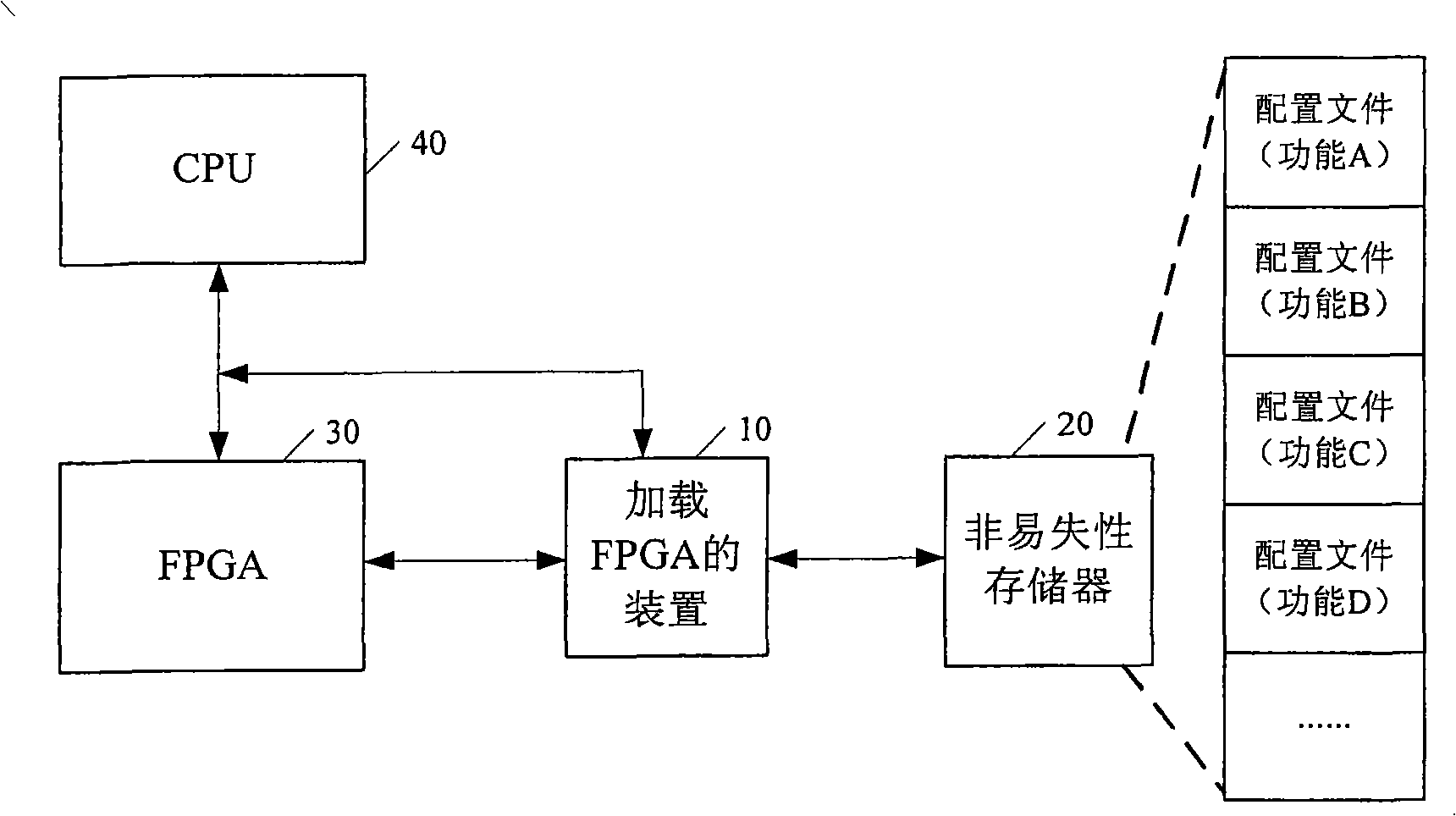

[0018] figure 1 A schematic diagram of a device for loading an FPGA according to an embodiment of the present invention. As shown in the figure: a device for loading FPGA in an embodiment of the present invention includes: a loading parameter receiving unit 101 for receiving a configuration file loading parameter of a field programmable gate array; a configuration file selection unit 102 for according to the configuration file The loading parameter selects a configuration file from multiple configuration files; the configuration file loading unit 103 is configured to load the selected configuration file into the FPGA. The means for loading the FPGA may also be used to store said plurality of configuration files corresponding to different functions.

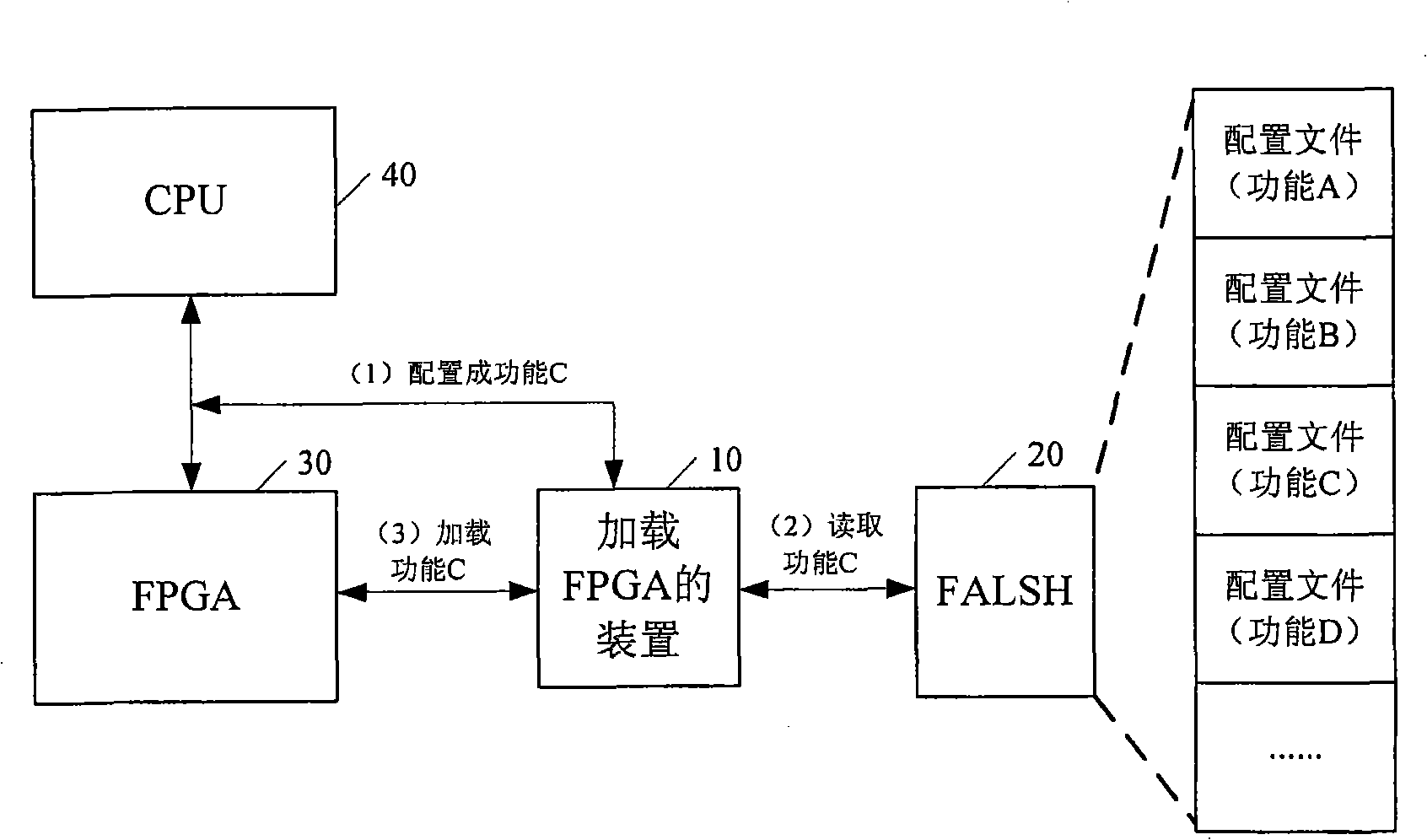

[0019] The device of the embodiment of the present invention stores multiple configuration f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More