Floating-point multiply-add fused unit compatible with double-precision and double-single-precision and compatibility processing method thereof

A processing method and single-precision technology, which can be used in electrical digital data processing, digital data processing components, instruments, etc., and can solve the problems of adding floating-point multiplier-adders and increasing area overhead floating-point multiplier-adders.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

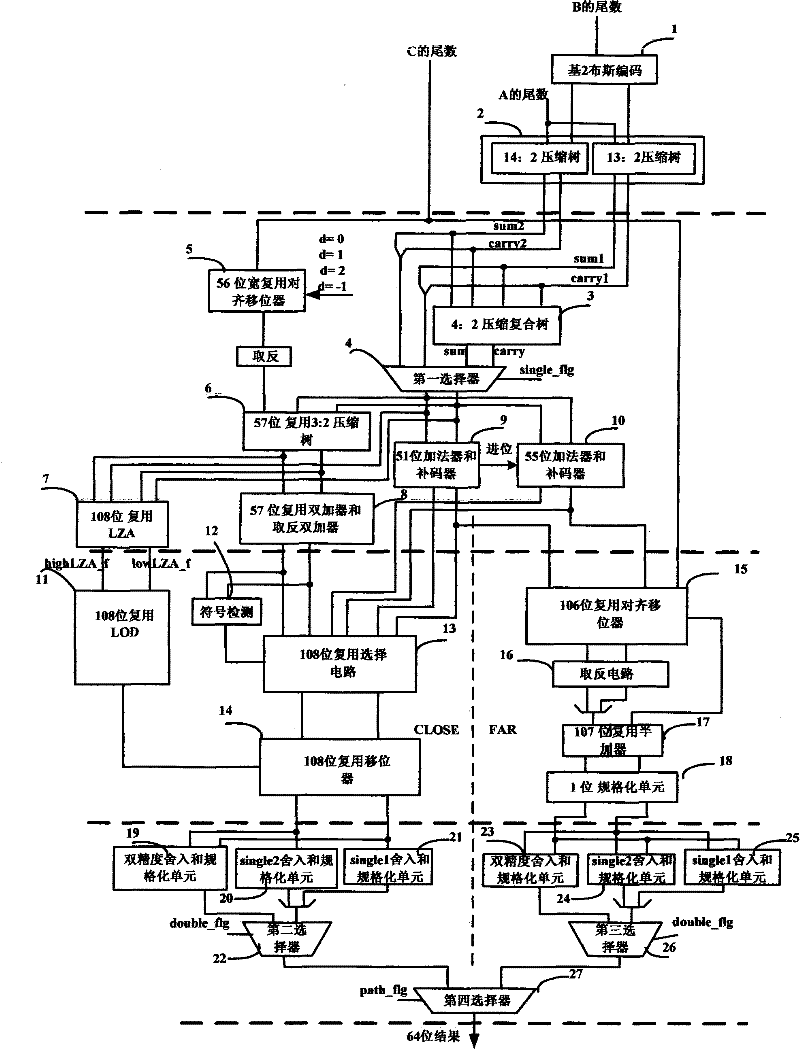

[0048] In order to make the object, technical solution and advantages of the present invention clearer, the floating-point multiply-accumulator and its floating-point multiply-accumulate processing method of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention rather than limit the present invention.

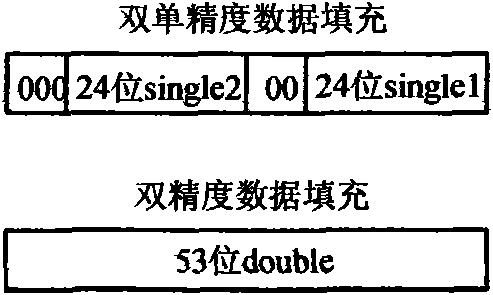

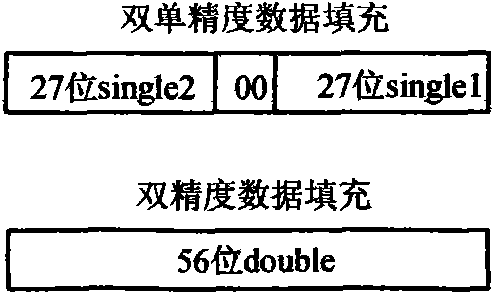

[0049] In order to reduce the delay of the floating-point multiplier-adder, the floating-point multiplier-accumulator in the embodiment of the present invention adopts a dual-path algorithm, and on the basis of the dual-path algorithm, double-precision and double-single-precision operations are performed on the two paths for multiplexing.

[0050] The two-path algorithm is to calculate the exponent difference d1=exp(A)-(exp(B)+exp(C) according to the exponent of the data operand A, the exponen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More