Potential pull-up circuit and pull-down circuit of I/O port of integrated circuit

An integrated circuit and potential technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problems of large power consumption, large current, and increased potential pull-up circuit area, etc., to achieve The effect of strong anti-noise interference ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

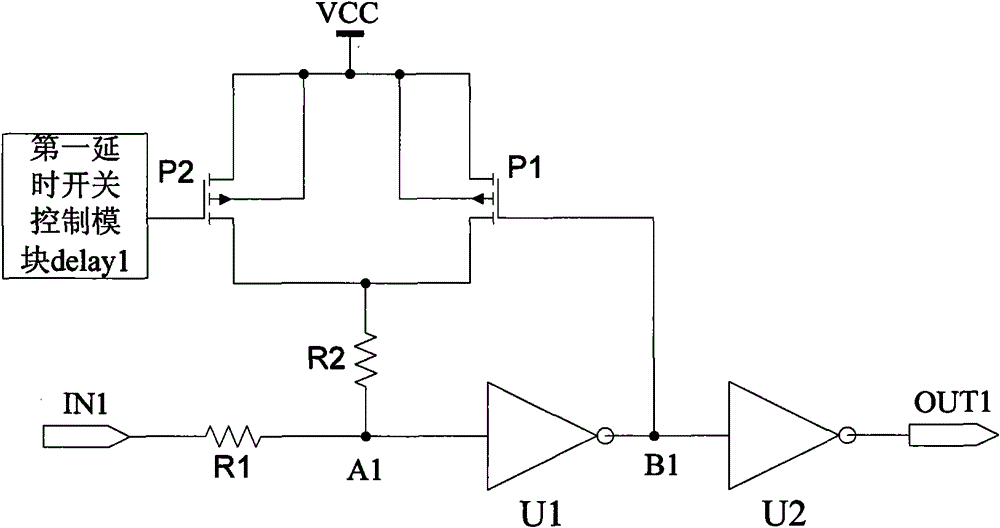

[0020] Embodiment 1: a potential pull-up circuit of the I / O port of an integrated circuit, such as figure 2 As shown, it includes a first delay switch control module delay1, a first PMOS transistor P1, a second PMOS transistor P2, a first inverter U1, a second inverter U2, a first resistor R1 and a second resistor R2, The first terminal of the first resistor R1 is the input terminal IN1 of the entire potential pull-up circuit, and the second terminal of the first resistor R1 is respectively connected to the input terminal of the first inverter U1 and the first terminal of the second resistor R2, The second end of the second resistor R2 is respectively connected to the drain of the first PMOS transistor P1 and the drain of the second PMOS transistor P2, and the gate of the second PMOS transistor P2 is connected to the first delay switch control module delay1, The source of the second PMOS transistor P2, the substrate of the second PMOS transistor P2, the source of the first PM...

Embodiment 2

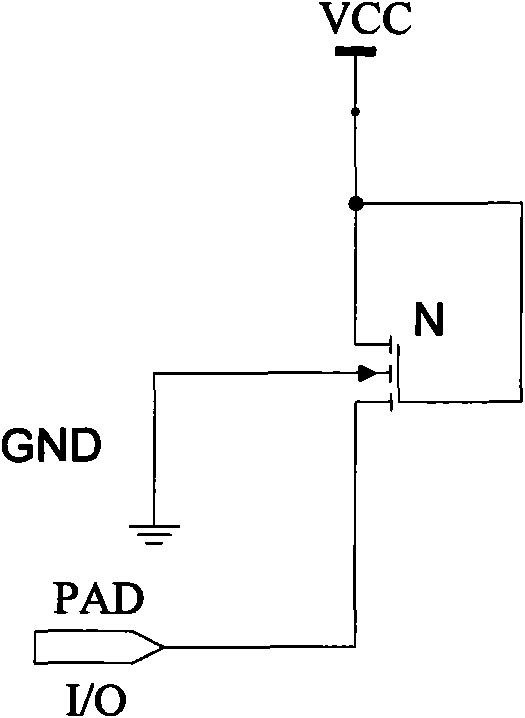

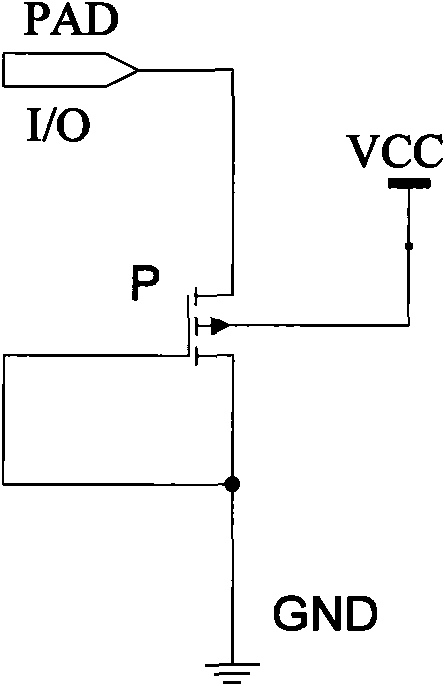

[0027] Embodiment two: a potential pull-down circuit of the I / O port of an integrated circuit, such as image 3 As shown, it includes a second delay switch control module delay2, a first NMOS transistor N1, a second NMOS transistor N2, a third inverter U3, a fourth inverter U4, a third resistor R3 and a fourth resistor R4, The first terminal of the third resistor R3 is the input terminal IN2 of the entire potential pull-down circuit, the second terminal of the third resistor R3 is respectively connected to the input terminal of the third inverter U3 and the first terminal of the fourth resistor R4, the second The second ends of the four resistors R4 are respectively connected to the drain of the first NMOS transistor N1 and the drain of the second NMOS transistor N2, the gate of the first NMOS transistor N1 is connected to the second delay switch control module delay2, the second The source of an NMOS transistor N1, the substrate of the first NMOS transistor N1, the source of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com