Pull-up resistor circuit

A resistance circuit, voltage technology, applied in the direction of logic circuit, logic circuit connection/interface layout, electrical components, etc., to eliminate backflow current and improve reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

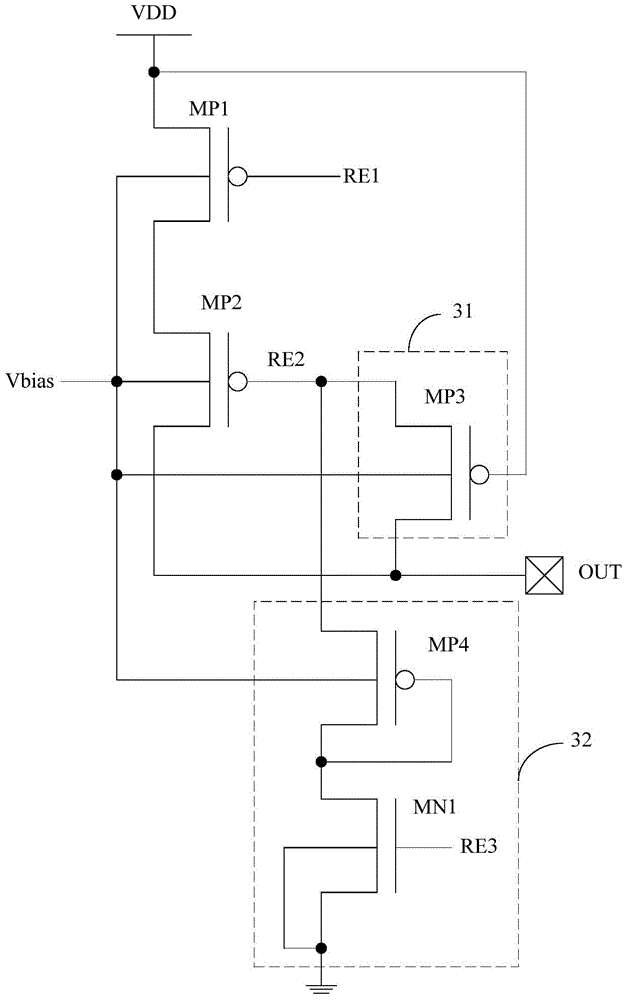

[0055] image 3 is a circuit diagram of the pull-up resistor circuit of this embodiment. refer to image 3 , the pull-up resistor circuit includes a power supply terminal VDD, an output terminal OUT, a first PMOS transistor MP1, a second PMOS transistor MP2 and a control signal generating unit.

[0056] The power supply terminal VDD, the output terminal OUT, the first PMOS transistor MP1 and the second PMOS transistor MP2 are connected with figure 2 Similar and will not be repeated here. The control signal generation unit includes a first switch unit 31 and a second switch unit 32 .

[0057] In this embodiment, the first switch unit 31 includes a third PMOS transistor MP3, the second switch unit 32 includes a fourth PMOS transistor MP4 and a first NMOS transistor MN1, and when the first switch unit 31 is turned on The impedance is smaller than the impedance when the second switch unit 32 is turned on. Therefore, when the first switch unit 31 and the second switch unit 32...

Embodiment 2

[0074] Figure 4 is a circuit diagram of the pull-up resistor circuit of this embodiment. refer to Figure 4 , the pull-up resistor circuit includes a power supply terminal VDD, an output terminal OUT, a first PMOS transistor MP1, a second PMOS transistor MP2 and a control signal generating unit.

[0075] The power supply terminal VDD, the output terminal OUT, the first PMOS transistor MP1 and the second PMOS transistor MP2 are connected with figure 2 Similar and will not be repeated here. The control signal generation unit includes a first switch unit 41 and a second switch unit 42 , the impedance of the first switch unit 41 is smaller than the impedance of the second switch unit 42 when it is turned on. The first switch unit 41 includes a third PMOS transistor MP3, and for the third PMOS transistor MP3, reference may be made to the description in Embodiment 1.

[0076] The second switch unit 42 includes a second NMOS transistor MN2 and a third NMOS transistor MN3.

[0...

Embodiment 3

[0086] The pull-up resistor circuit of this embodiment includes a power supply terminal, an output terminal, a first PMOS transistor, a second PMOS transistor, and a control signal generating unit, and also includes a bias voltage generating circuit suitable for generating a bias voltage Vbias. The power supply terminal, output terminal, first PMOS transistor, second PMOS transistor and control signal generation unit are similar to those in Embodiment 1 and Embodiment 2, and will not be repeated here.

[0087] Figure 5 is a circuit diagram of the bias voltage generation circuit of this embodiment. refer to Figure 5 , the bias voltage generating circuit includes a fifth PMOS transistor MP5 and a sixth PMOS transistor MP6.

[0088] Specifically, the gate of the fifth PMOS transistor MP5 is connected to the drain of the sixth PMOS transistor MP6 and the output terminal OUT, and the source of the fifth PMOS transistor MP5 is connected to the power supply terminal VDD and the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More