Reading and writing operation method and equipment of FPGA (Field Programmable Gate Array) equipment in DDR (Double Data Rate) interface

A technology for writing operations and devices, applied in the field of communications, which can solve the problems of single DDR system structure and inability to meet system diversity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 4

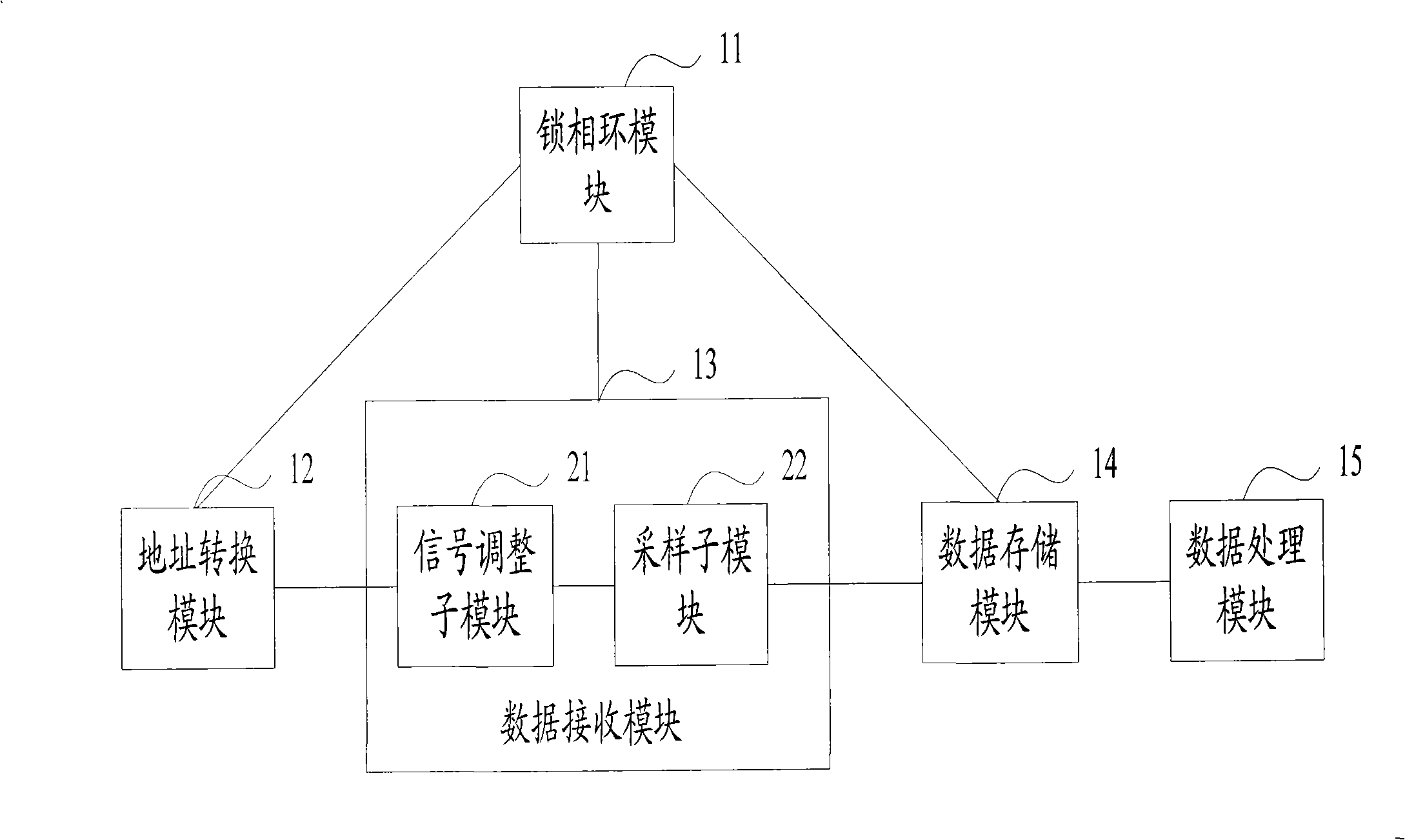

[0098] The FPGA device in Embodiment 4 may further include a data processing module 36 for processing data stored in the FPGA; or, processing data received from devices other than the FPGA. The data output by the data output module 34 may be data obtained and processed by the data processing module 36 from other devices other than the DDR controller. Therefore, the FPGA device in Embodiment 4 can unidirectionally transmit data to the DDR controller. It is also possible to write the data sent by the DDR controller into the RAM of the FPGA. After the data processing module inside the FPGA processes the written data, it is then read out by the DDR controller to realize bidirectional data exchange between the DDR controller and the FPGA device. transmission.

[0099] Take the second PLL module 32 to adjust the phase of the clock signal as an example below, as shown in Figure 4 (b), the second PLL module 32 can include an input port 41, an adjustment component 42 and an output port...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More