Out-of-order execution microprocessor and operating method therefor

A technology of microprocessors and operating methods, applied in machine execution devices, concurrent instruction execution, etc., can solve problems such as large power supply and microprocessor physical space, consumption, and large storage space for color bit arrays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

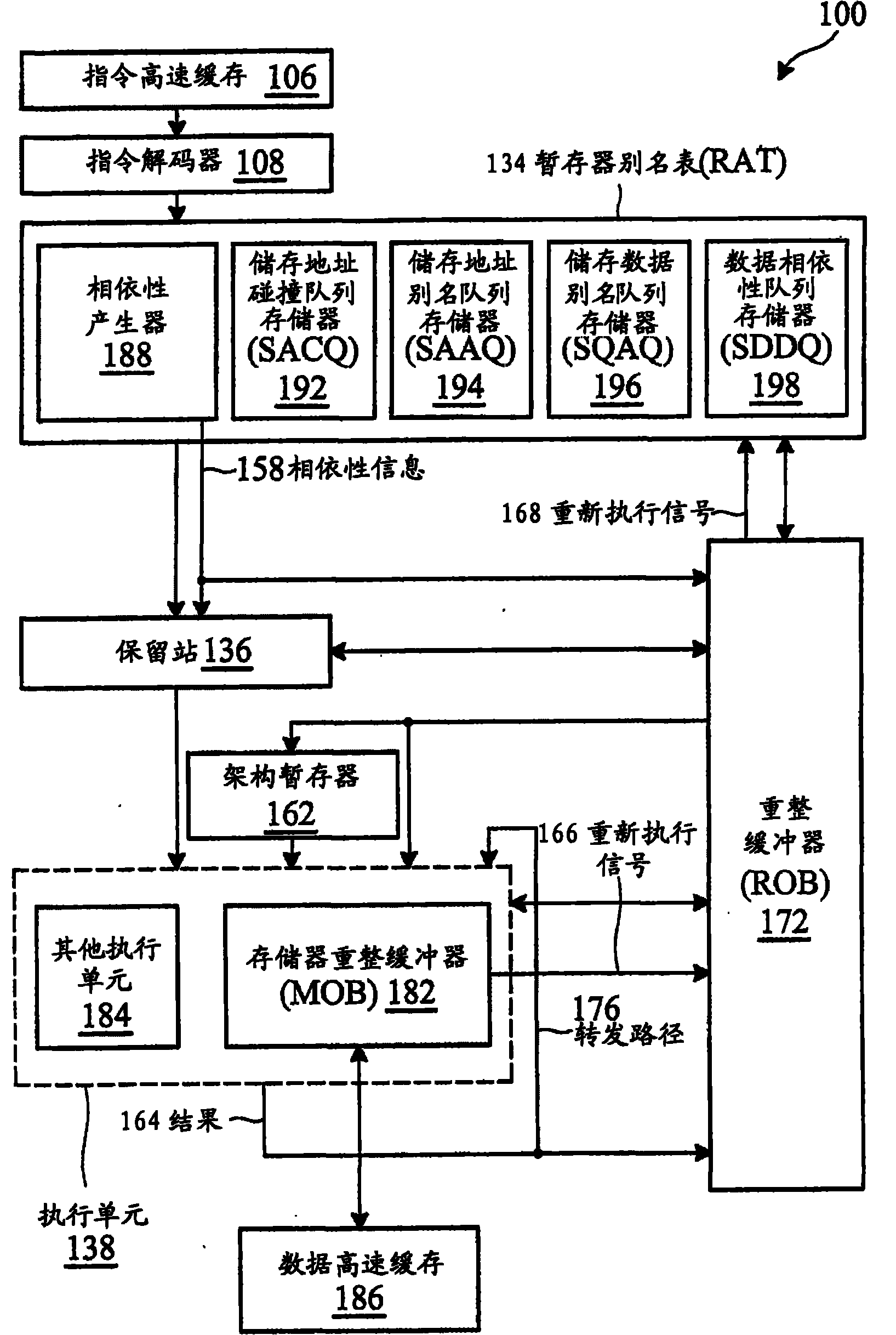

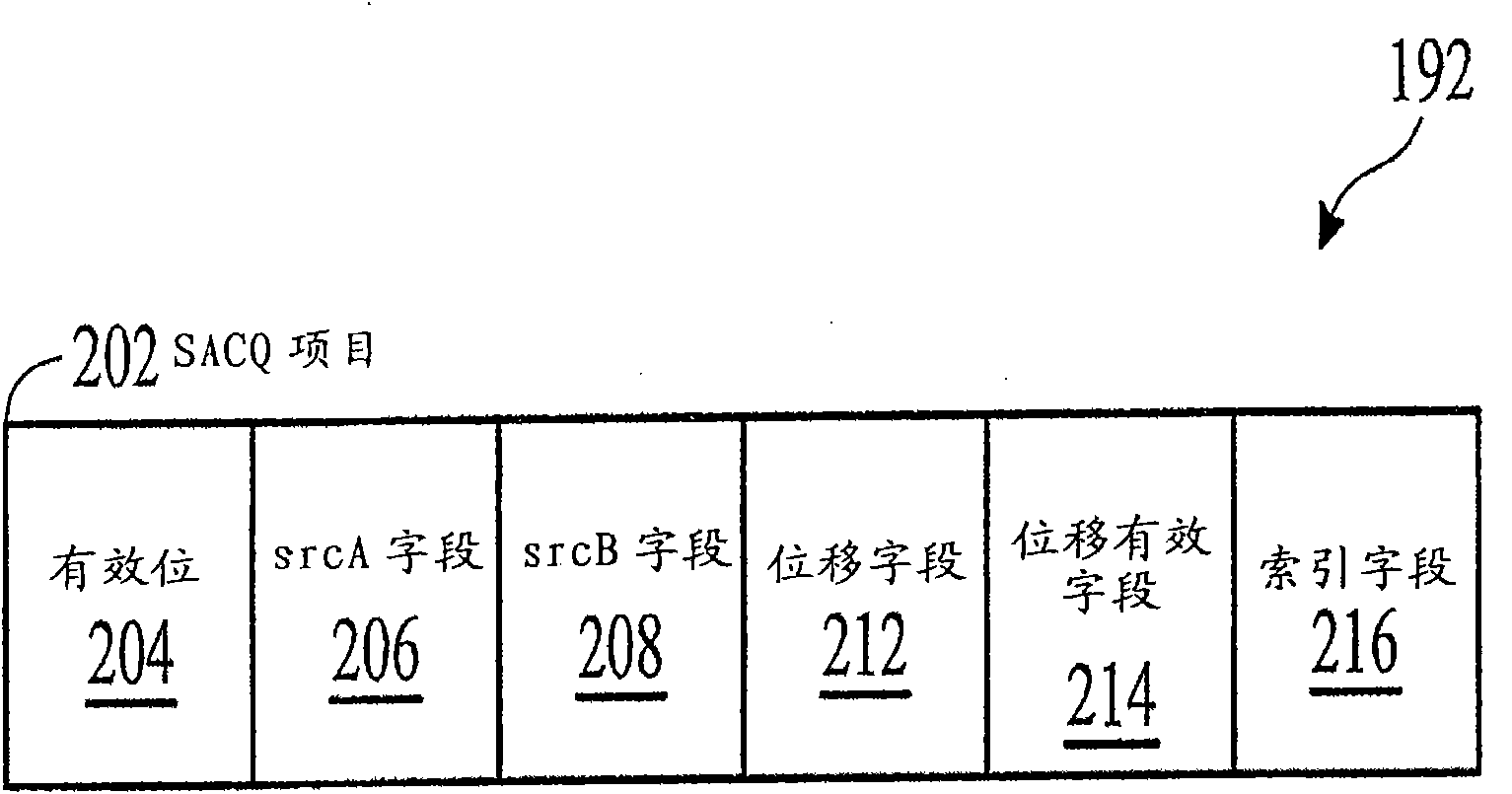

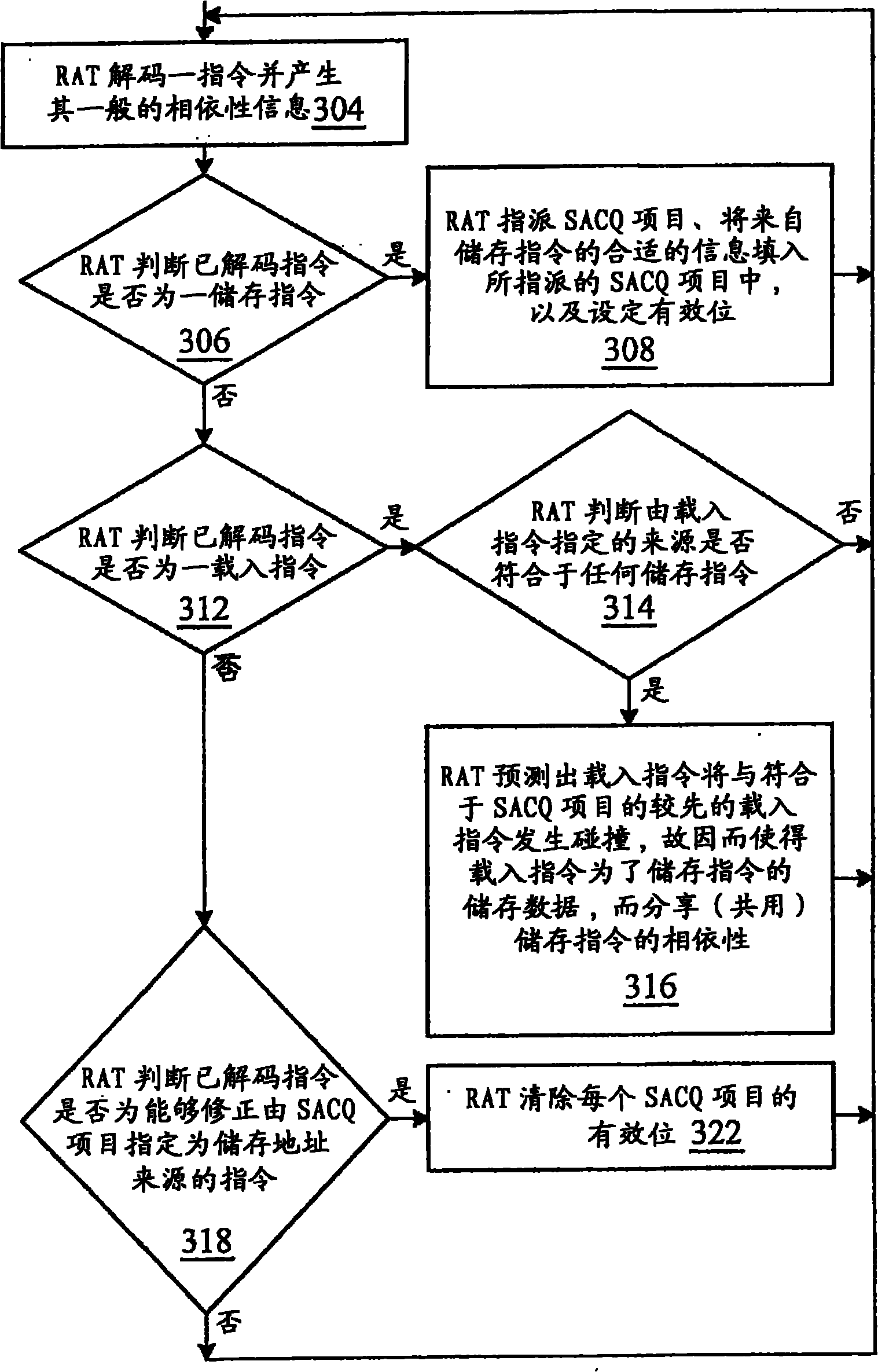

[0026] Embodiments described herein are pipelined non-sequential execution microprocessors to reduce the number of re-executions of load instructions when store collisions occur. The microprocessor includes a register alias table (register alias table, RAT) to predict when a load instruction will have a store collision, and to make the load instruction have a dependency relationship with an additional instruction (additional instruction), and the load instruction is usually There will be no dependency on this add-on. In this paper, the additional instruction that the loaded instruction depends on through the RAT is called a dependee instruction. This additional or extended dependency causes the microprocessor's issue logic to wait until the dependent instruction has been executed (ie, its execution result has been produced) before issuing the load instruction. Therefore, the execution result of the dependent instruction can be sent (delivered) to the load instruction, or can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com