Semiconductor element, packaging structure and forming method of semiconductor element

A semiconductor and component technology, applied in the field of bump structure technology, can solve the problem of high risk of short circuit and achieve the effect of avoiding short circuit or bridging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

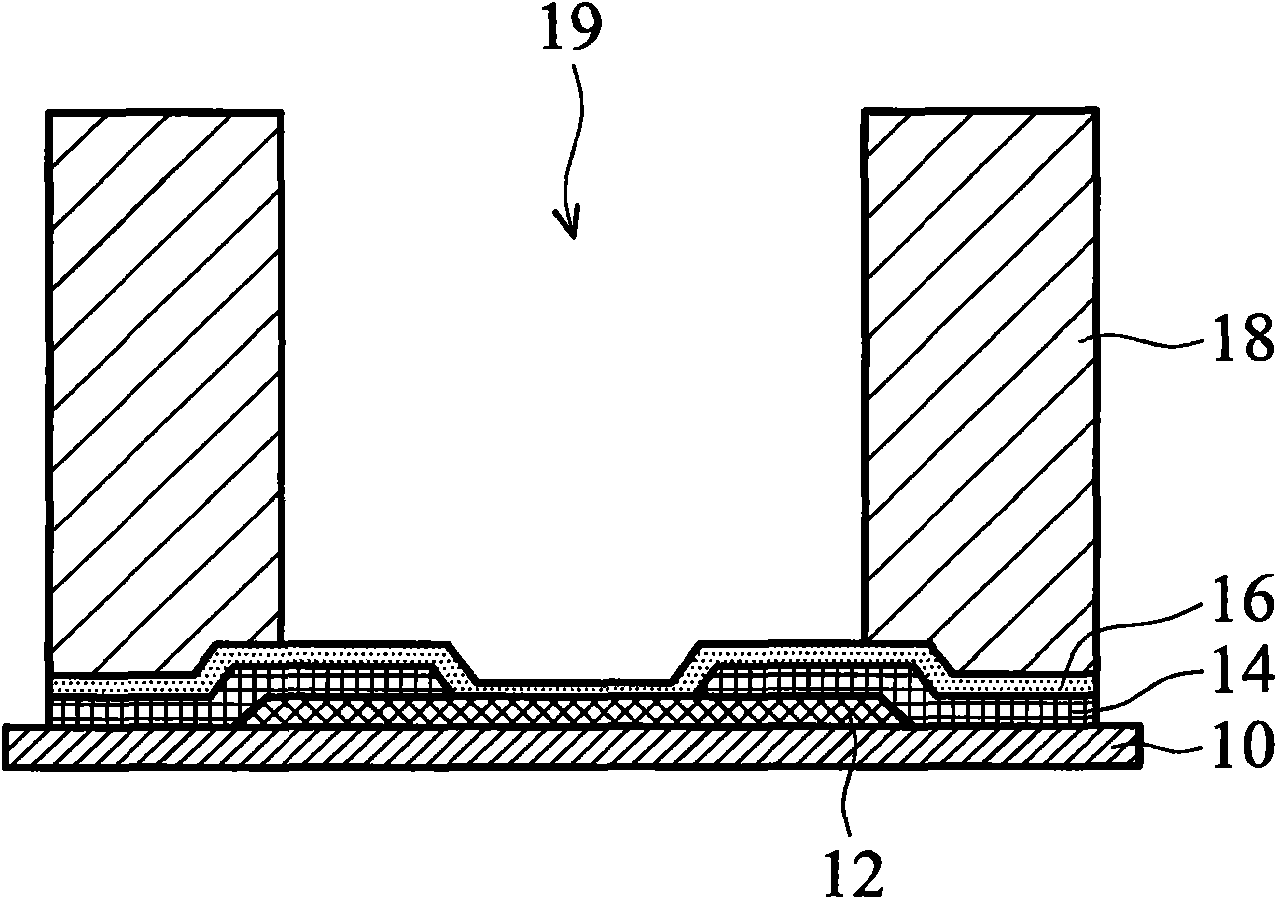

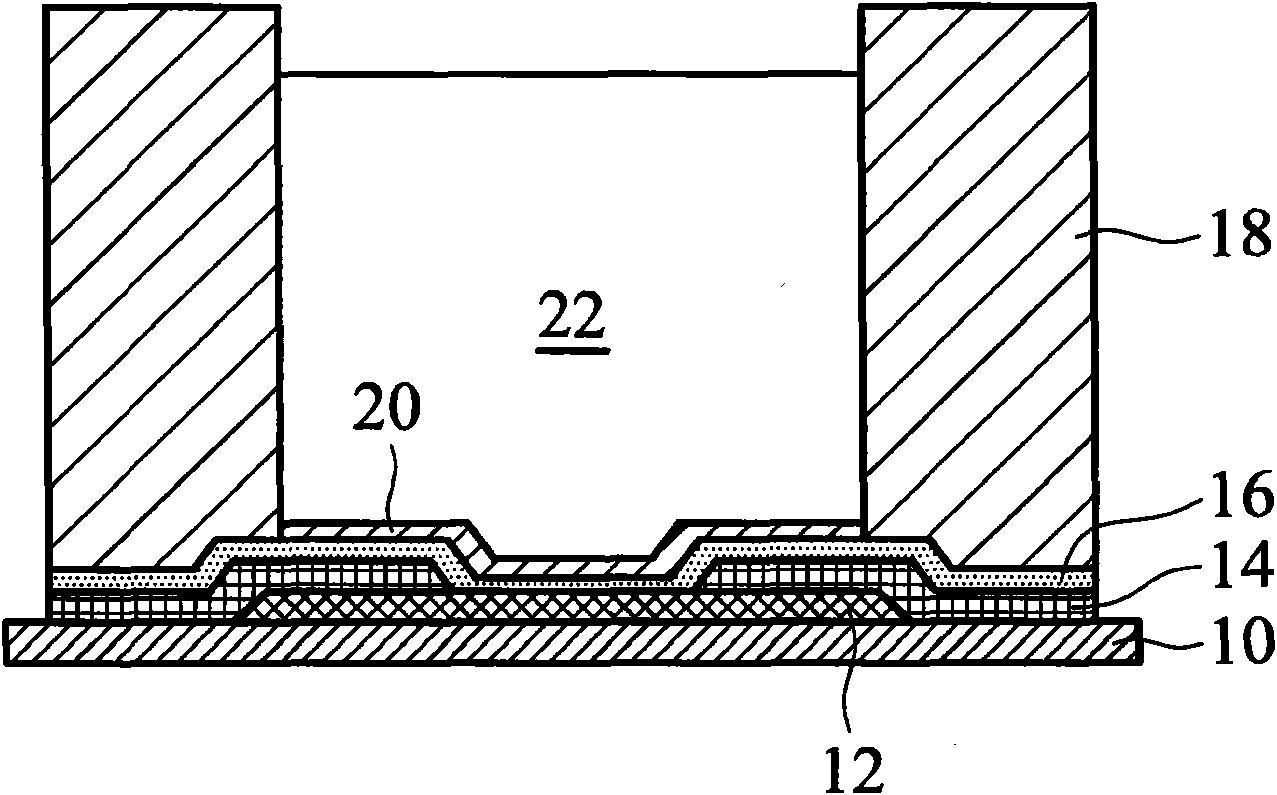

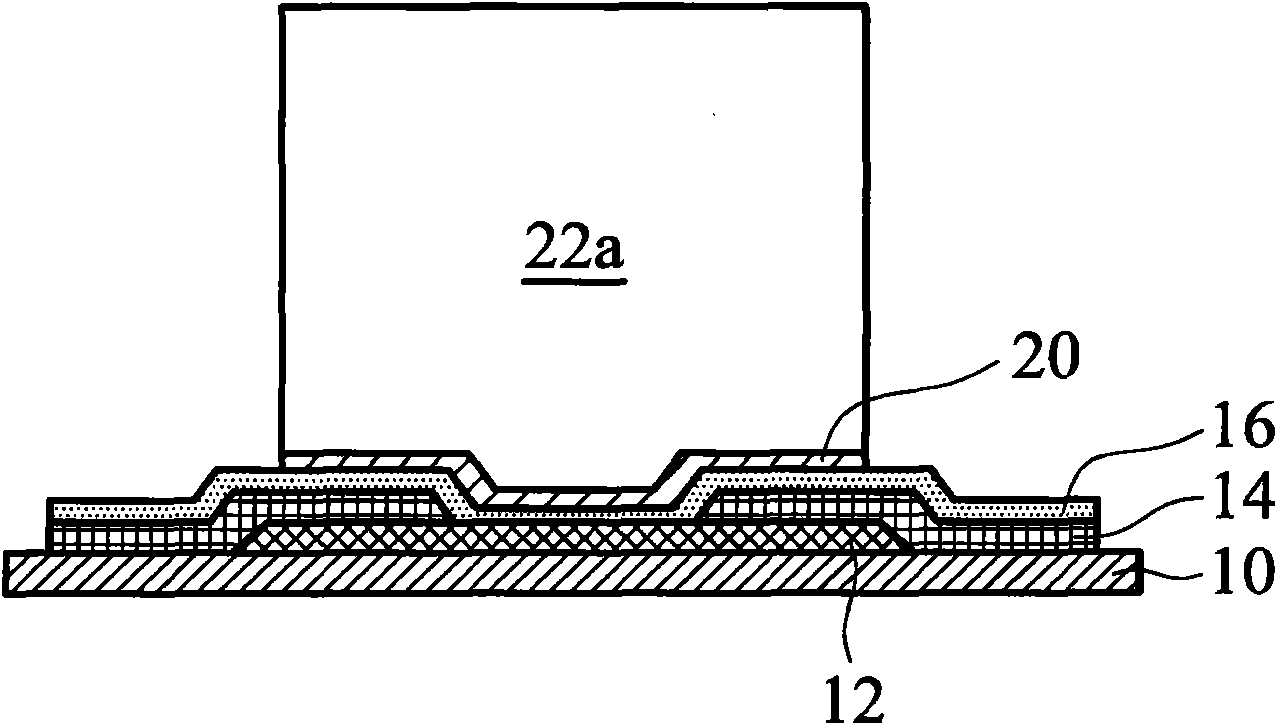

[0014] The bumping process in semiconductor devices described below can be applied to flip-chip packaging, wafer-level chip-scale packaging (WLCSP), three-dimensional integrated circuit (3D-IC) stacking, and / or any advanced packaging technologies. Embodiments relate to solder bumps for semiconductor devices and methods of forming the same. In the following description, various specific examples will be preceded to facilitate those skilled in the art to have a comprehensive understanding of the present invention. However, those skilled in the art should understand that the actual operation does not need to fully comply with these special cases. In some instances, structures and processes well known in the art have not been described in detail to avoid unnecessarily obscuring the disclosure. In the following description, "an embodiment" refers to a particular feature, structure, or structure in which at least one embodiment is combined. Thus, references to "an embodiment" in d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More