Lead frame of high-power chip package structure and manufacturing method thereof

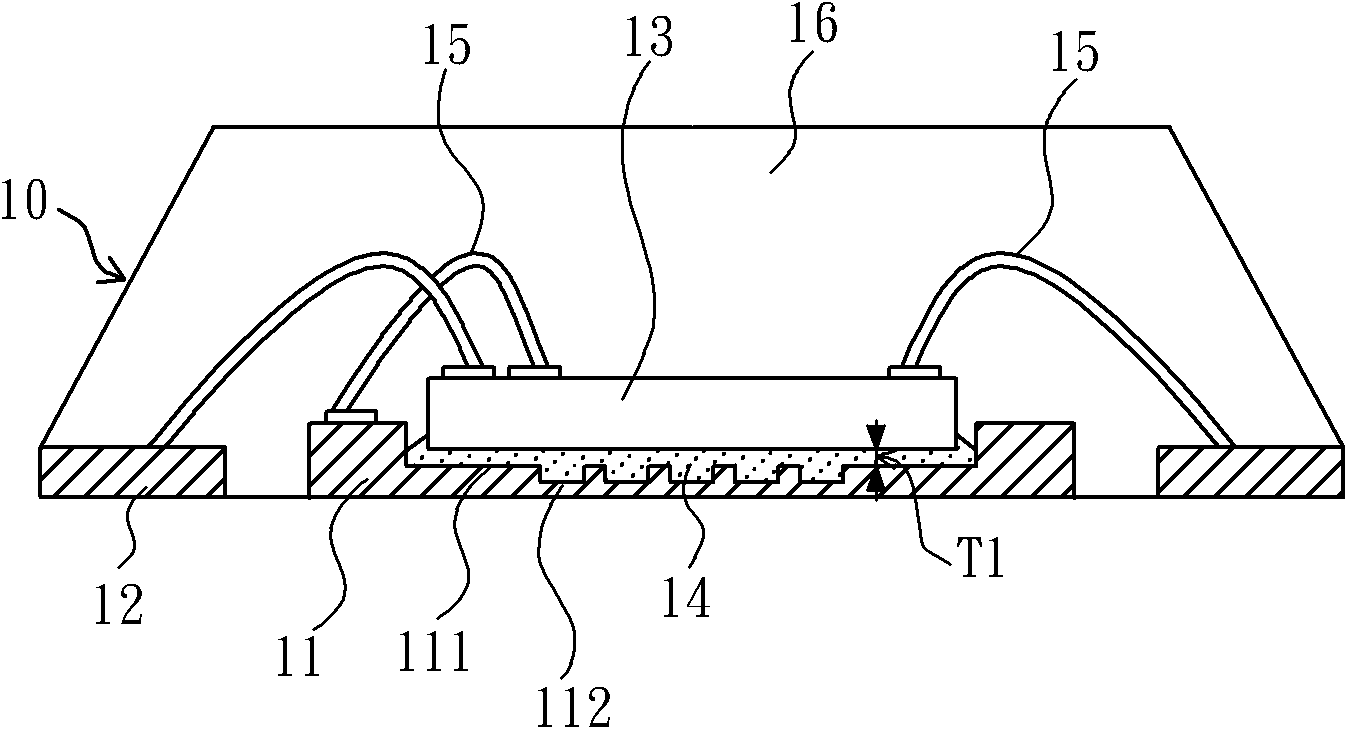

A manufacturing method and a technology of chip packaging, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as large amount of materials used, reduced reliability of packaging structure 10, service life, and peeling off

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The following descriptions of the various embodiments refer to the accompanying drawings to illustrate specific embodiments in which the present invention can be practiced. Furthermore, the directional terms mentioned in the present invention, such as "up", "down", "front", "back", "left", "right", "inside", "outside" or "side", etc., It is only for orientation with reference to the attached drawings. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention.

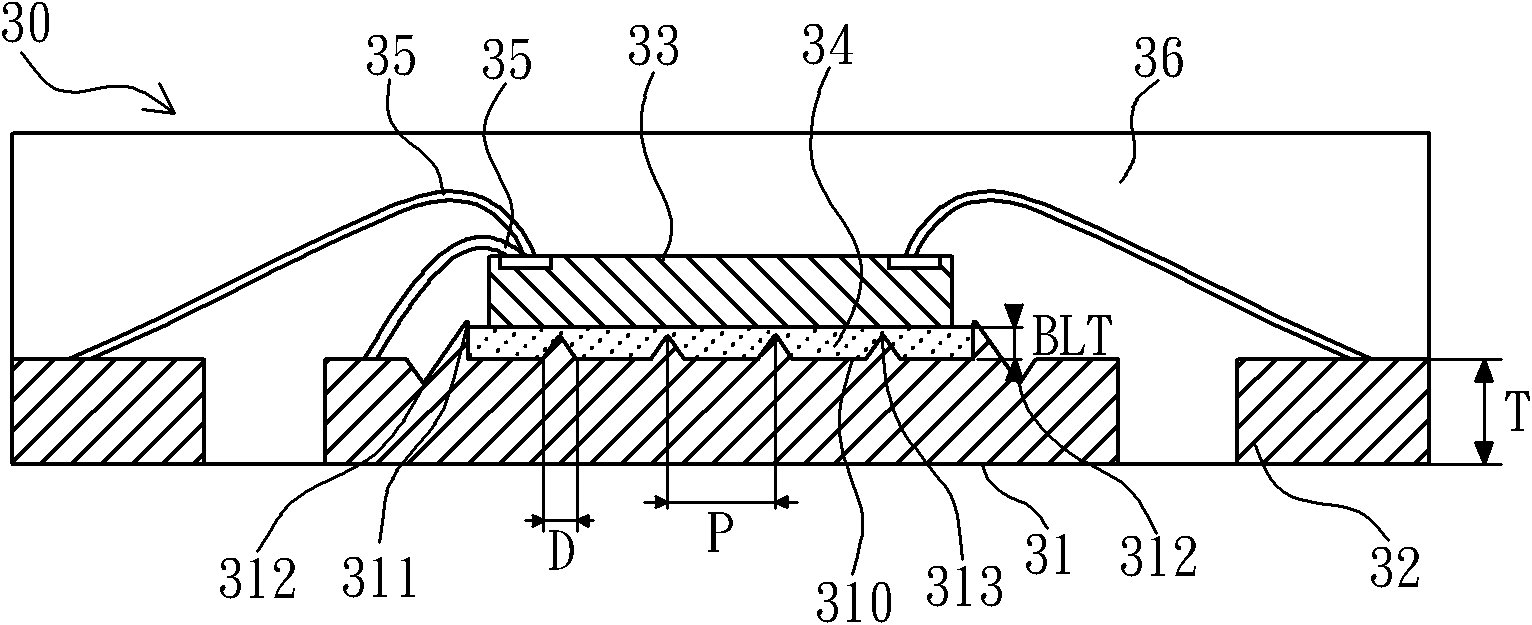

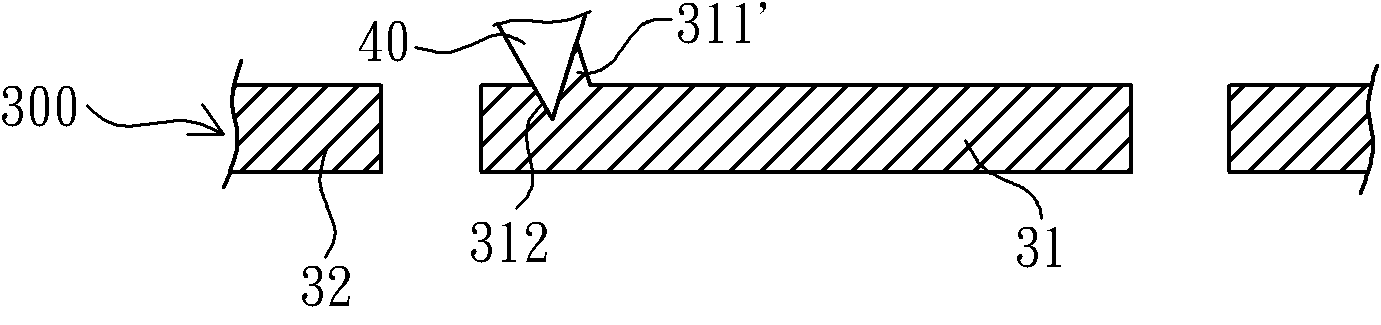

[0037] Please refer to figure 2 As shown, it discloses the high-power chip packaging structure 30 of the first embodiment of the present invention, which mainly includes a chip holder 31, several contacts 32, a high-power chip 33, an adhesive layer 34, several wires 35 and a Packaging adhesive 36, wherein the chip holder 31 and several contacts 32 are collectively referred to as a lead frame (unit), the present invention will be us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More