Patents

Literature

252results about How to "Improve packaging yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

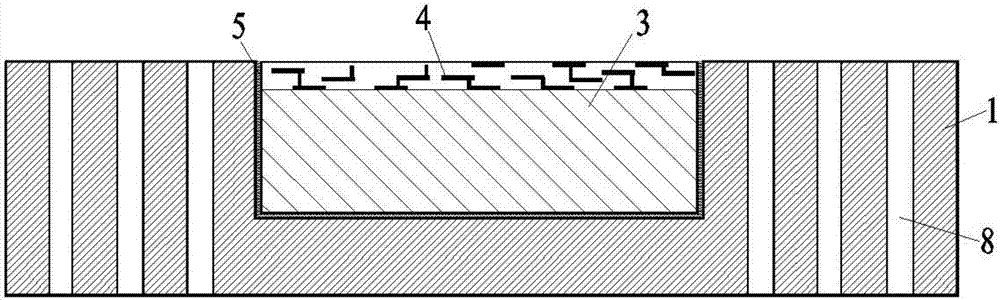

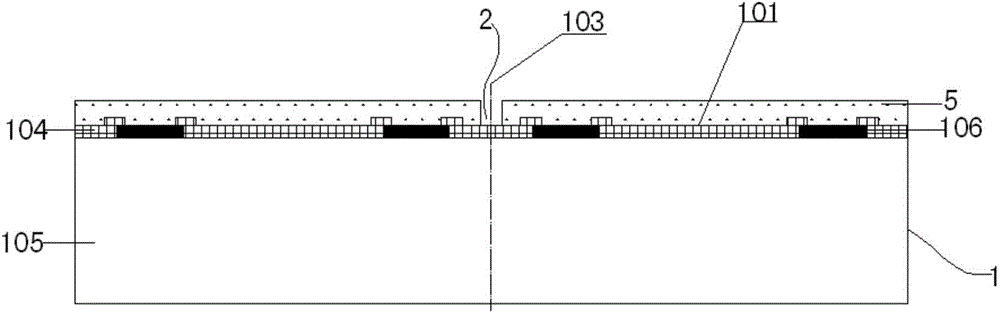

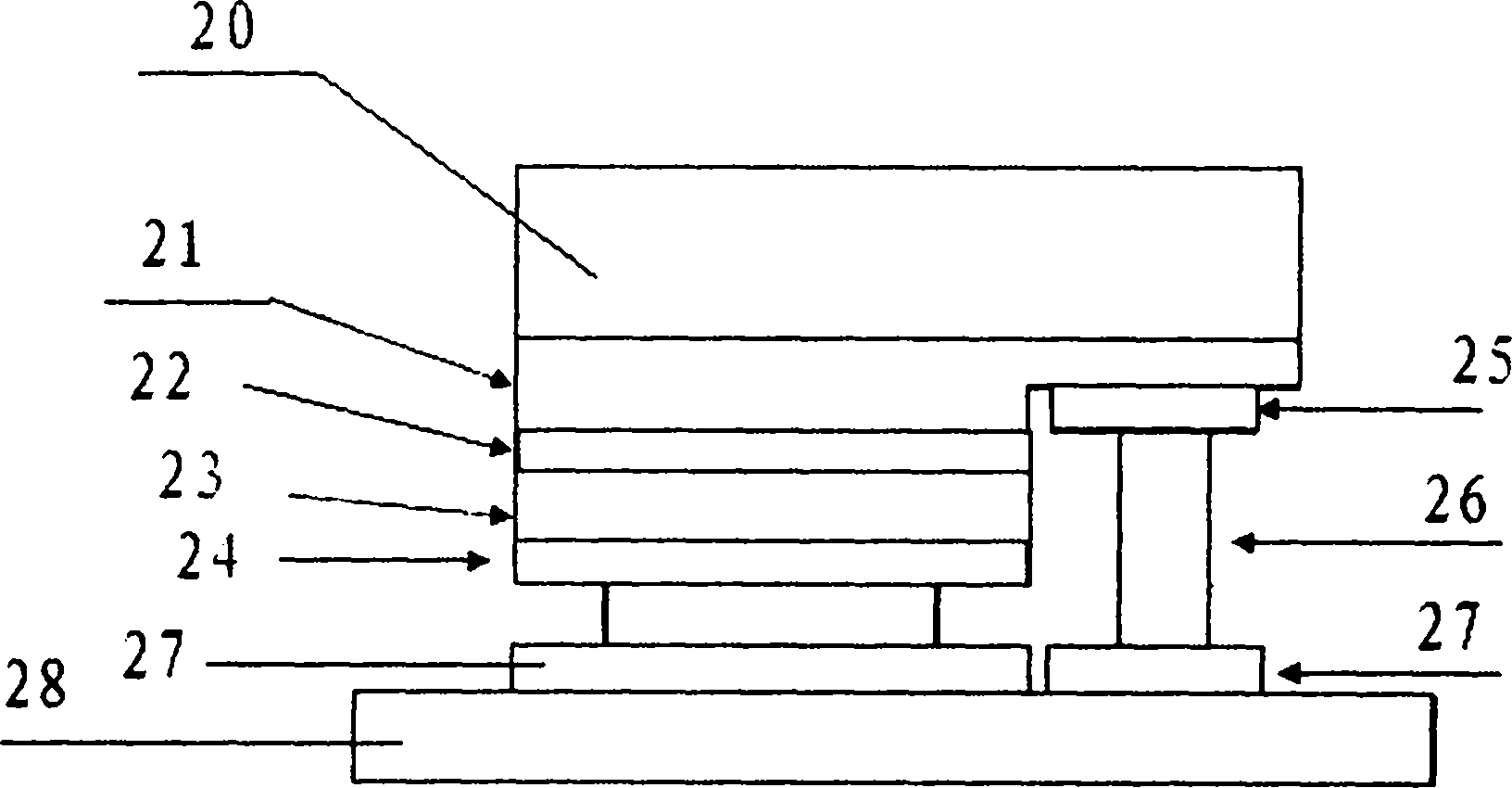

Flat non down-lead encapsulation piece and method for producing the same

ActiveCN101442035APrevent and eliminate delamination defectsLow water absorptionSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingHigh rate

The invention discloses a flat non-lead packaging part and a production method thereof. The flat non-lead packaging part comprises a lead frame carrier, wherein the carrier is adhered with an IC chip. The front side of the lead frame carrier is provided with pits. The periphery of the front side of the lead frame carrier is provided with two circles of waterproof grooves. The back side of the lead frame carrier is provided two circles of anti-overflow grooves. The production method comprises the processes of washer thinning and slicing, core loading, press welding, plastic package, plating, printing and cutting and coiling. The method strengthens the bonding forces between the adhesive and the lead frame carrier and the IC chip and eliminates and reduces the rate of a lamination defect generated on the surface of the IC chip. The two circles of waterproof grooves are provided on the periphery of the carrier, the plastic packaging materials are embedded in the grooves so as to prevent moisture from entering the chip. The two circles of anti-overflow grooves arranged on the edge of the carrier have functions of preventing the lamination defect, moisture and material overflow. The method has the advantages of high rate of finished product, good reliability and convenient use, and effectively improves the reliability and excellent packaging rate of products.

Owner:TIANSHUI HUATIAN TECH

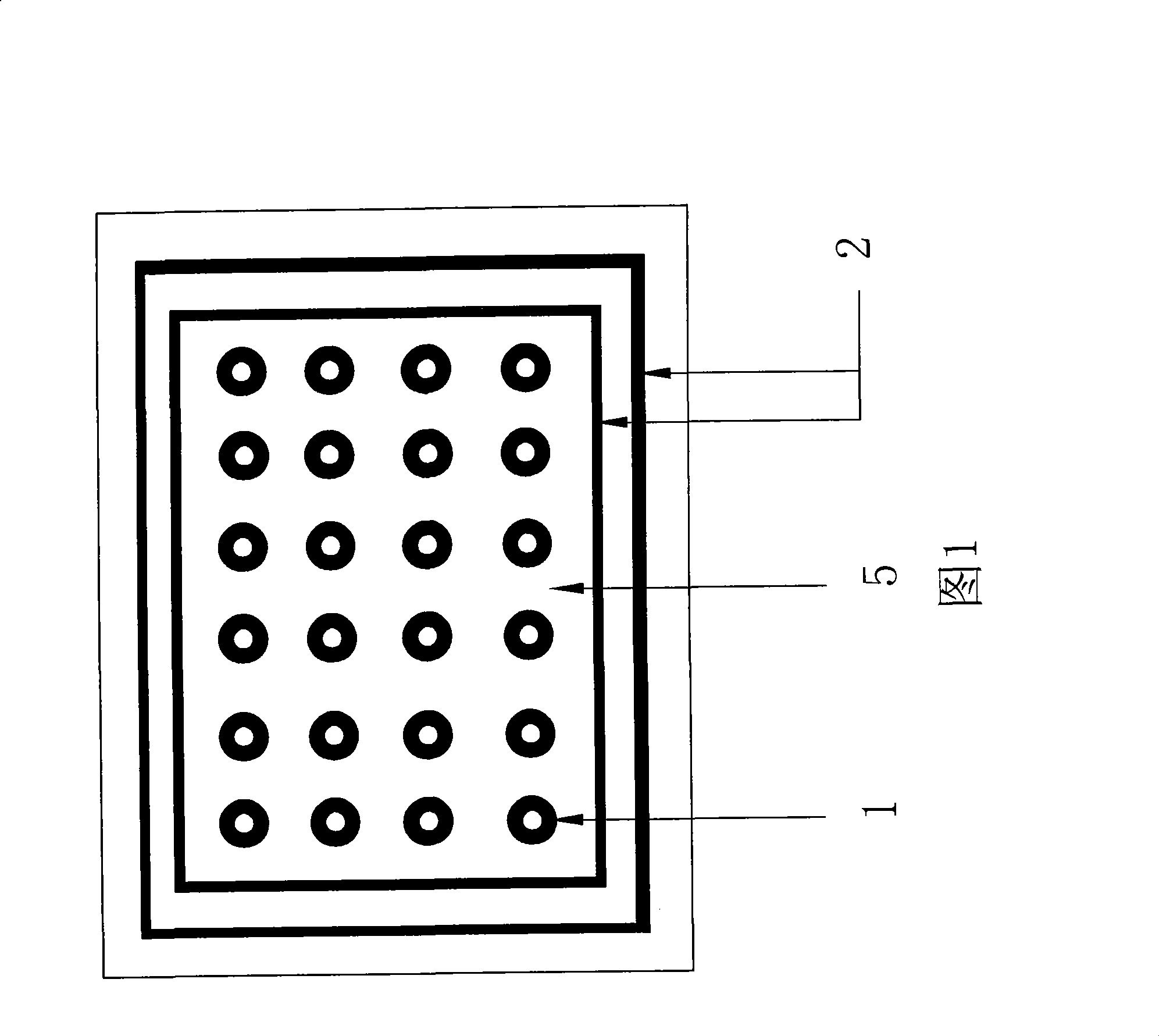

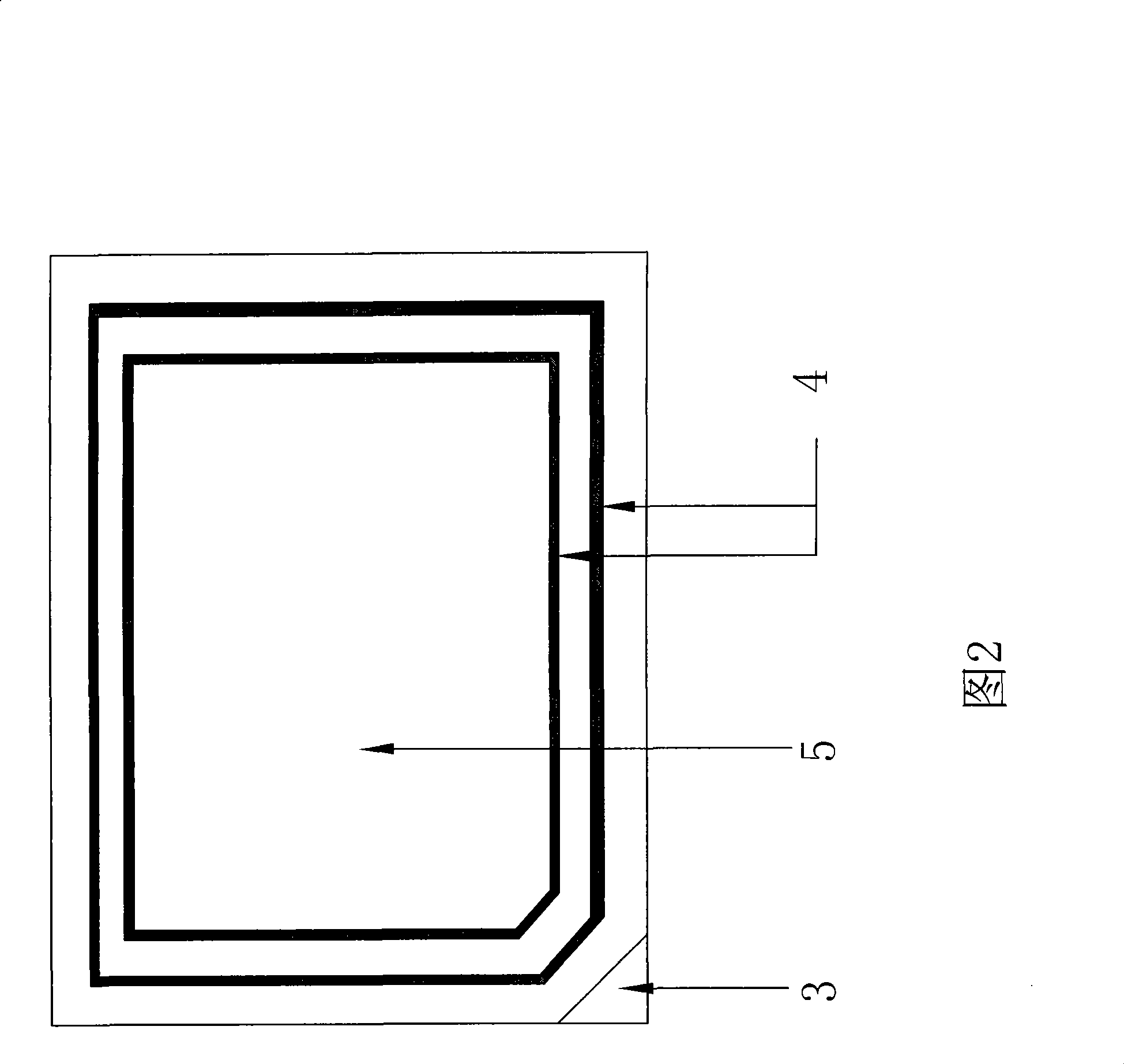

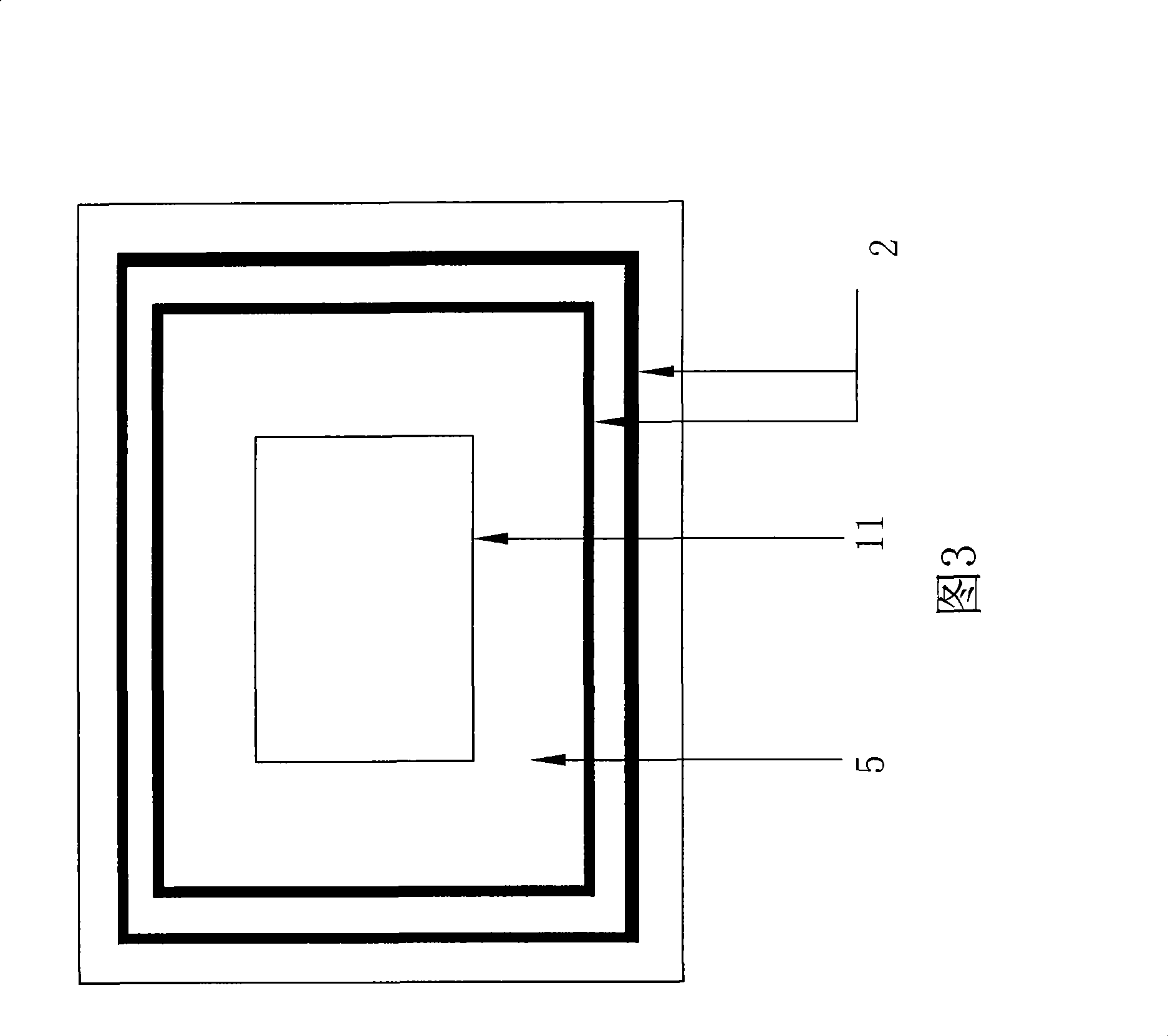

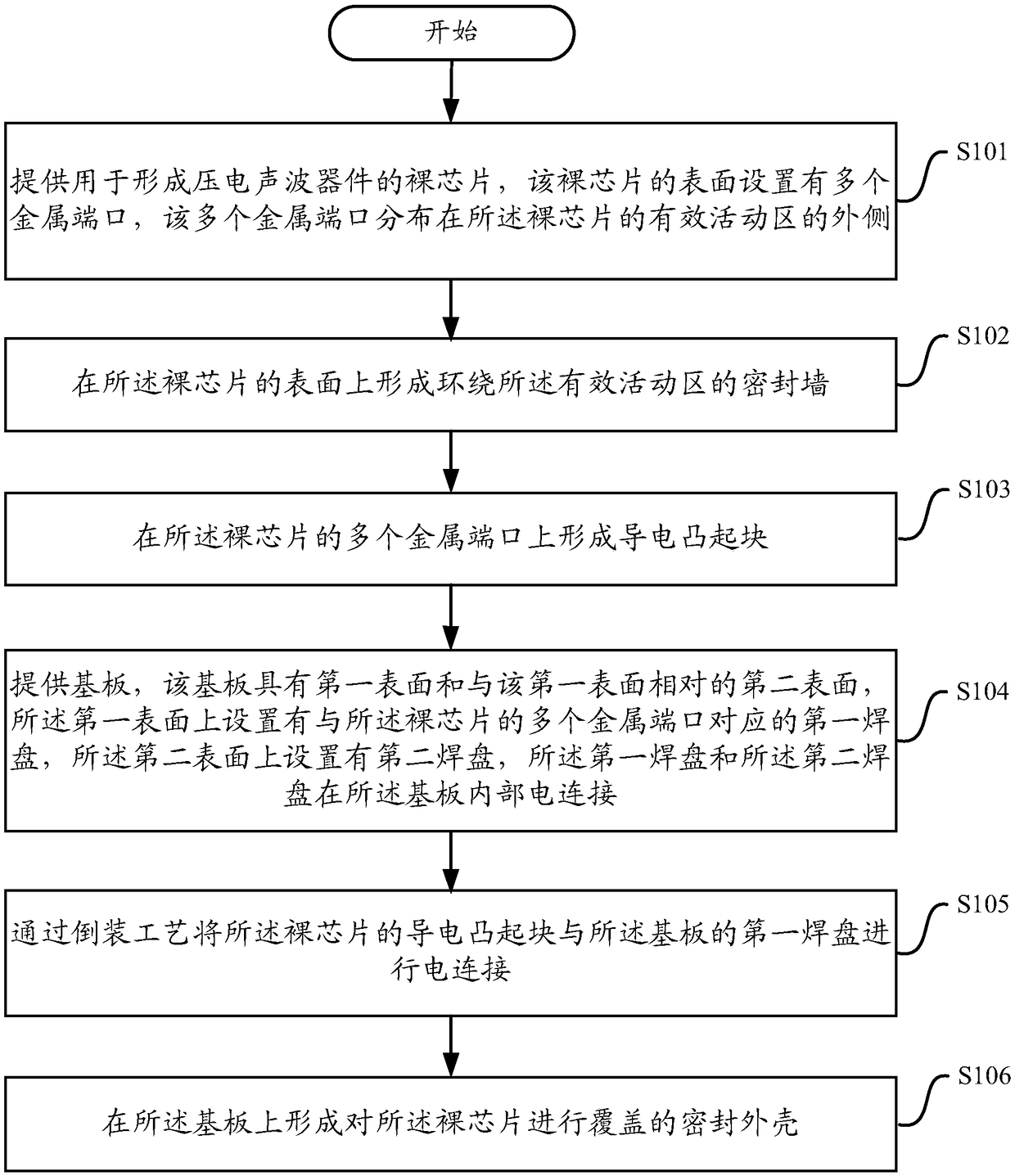

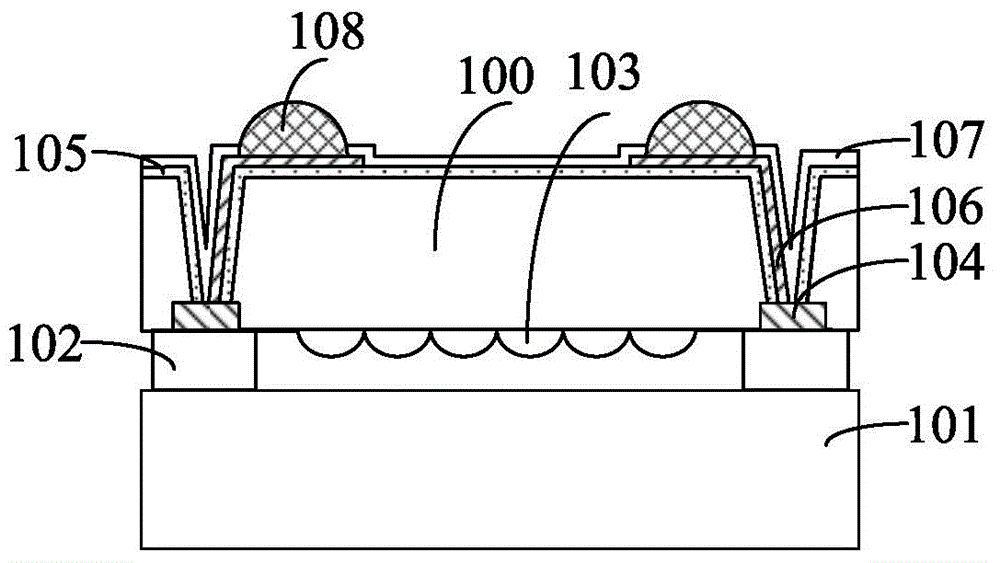

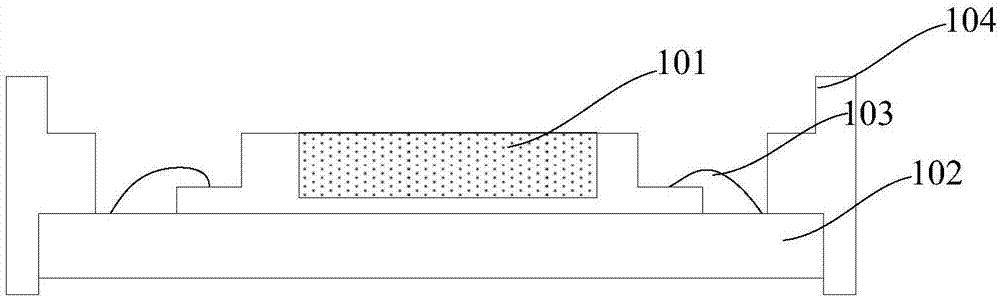

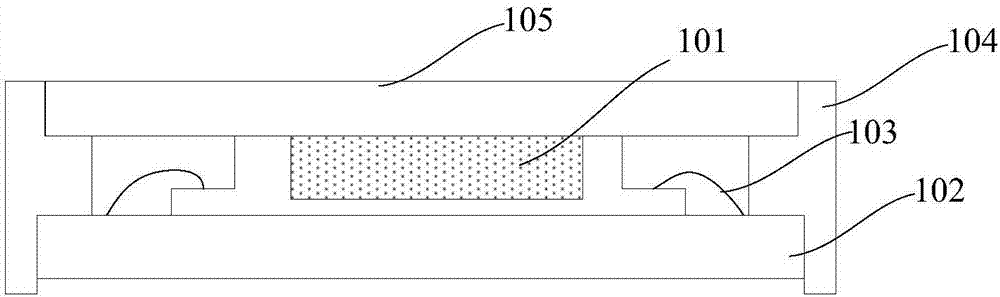

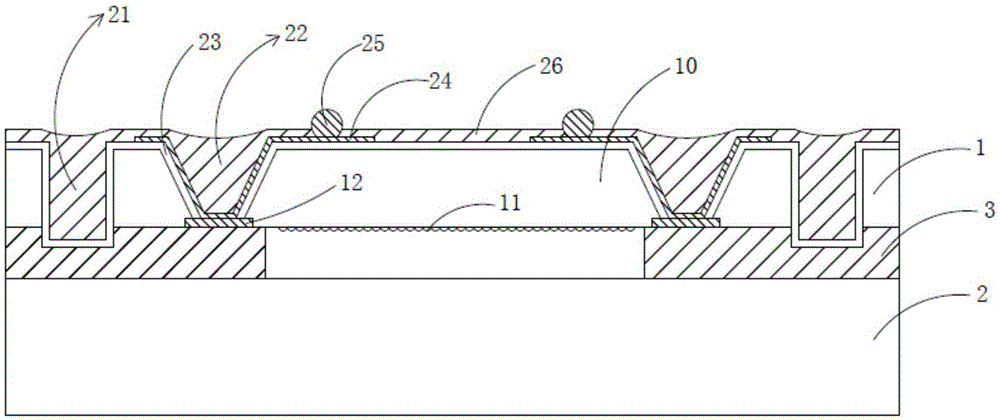

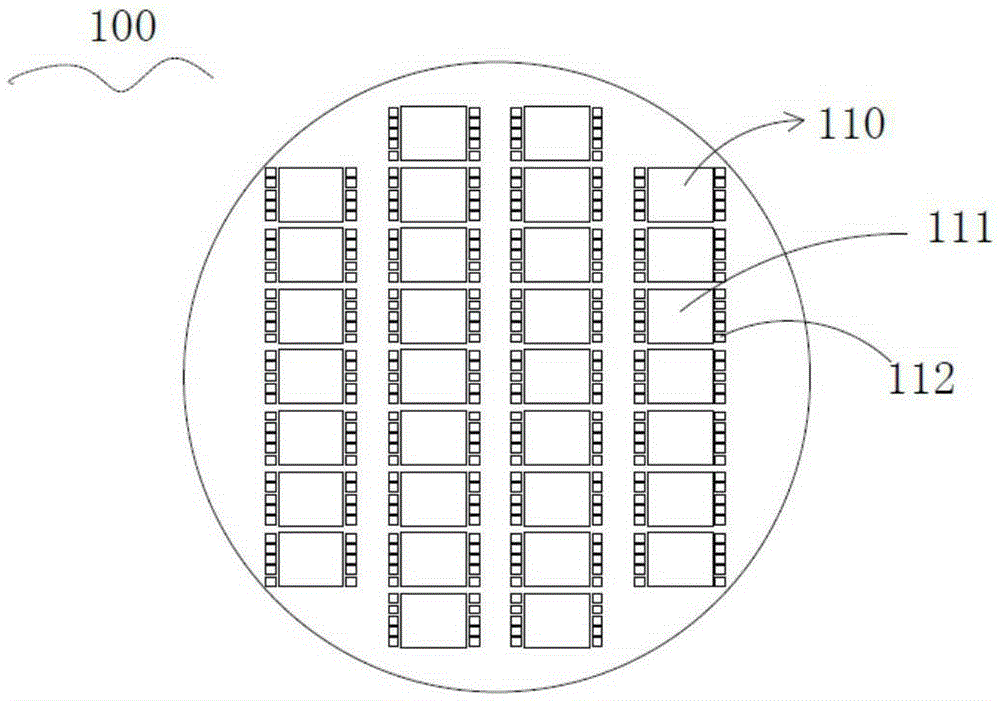

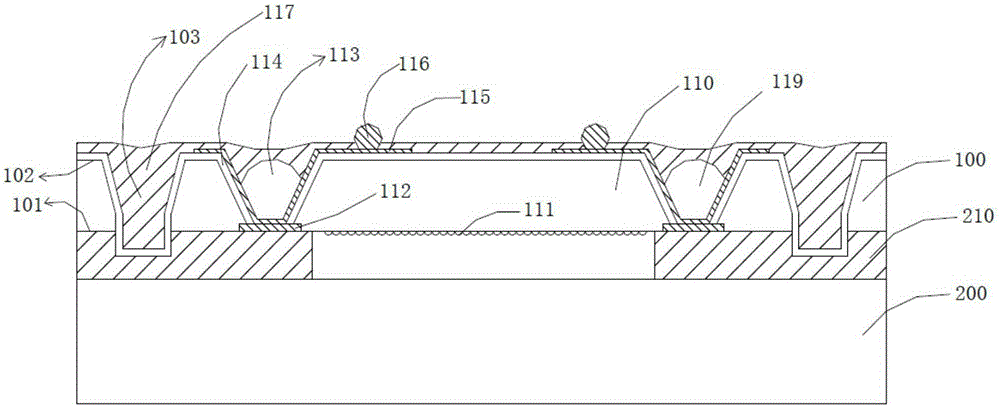

Packaging method and packaging structure of piezoelectric acoustic wave device

The invention provides a packaging method of a piezoelectric acoustic wave device. The packaging method comprises the following steps: providing a bare chip, wherein multiple metal ports are arrangedon the surface of the bare chip, and the multiple metal ports are distributed on the outer side of an effective active region of the bare chip; forming a sealing wall surrounding the effective activeregion on the surface of the bare chip; forming conductive convex blocks on the multiple metal ports of the bare chip; providing a base plate, wherein a first welding pad corresponding to the multiplemetal ports of the bare chip is arranged on one surface of the base plate, and a second welding pad is arranged on the other surface of the base plate; electrically connecting the conductive convex blocks of the bare chip with the first welding pad of the base plate through the flip-chip process; and forming a sealing outer shell, covering the bare chip, on the base plate. Correspondingly, the invention further provides a packaging structure of the piezoelectric acoustic wave device. By implementation of the packaging method of the piezoelectric acoustic wave device and the packing structureof the piezoelectric acoustic wave device, the instability of a traditional sealing process is transferred to the surface of the base plate, so that the effective active region of the piezoelectric acoustic wave device is effectively protected.

Owner:SUZHOU HUNTERSUN ELECTRONICS CO LTD

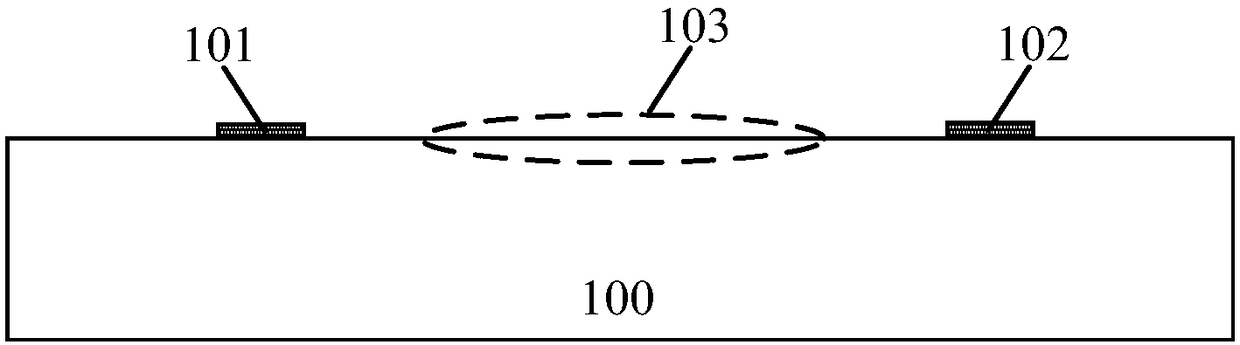

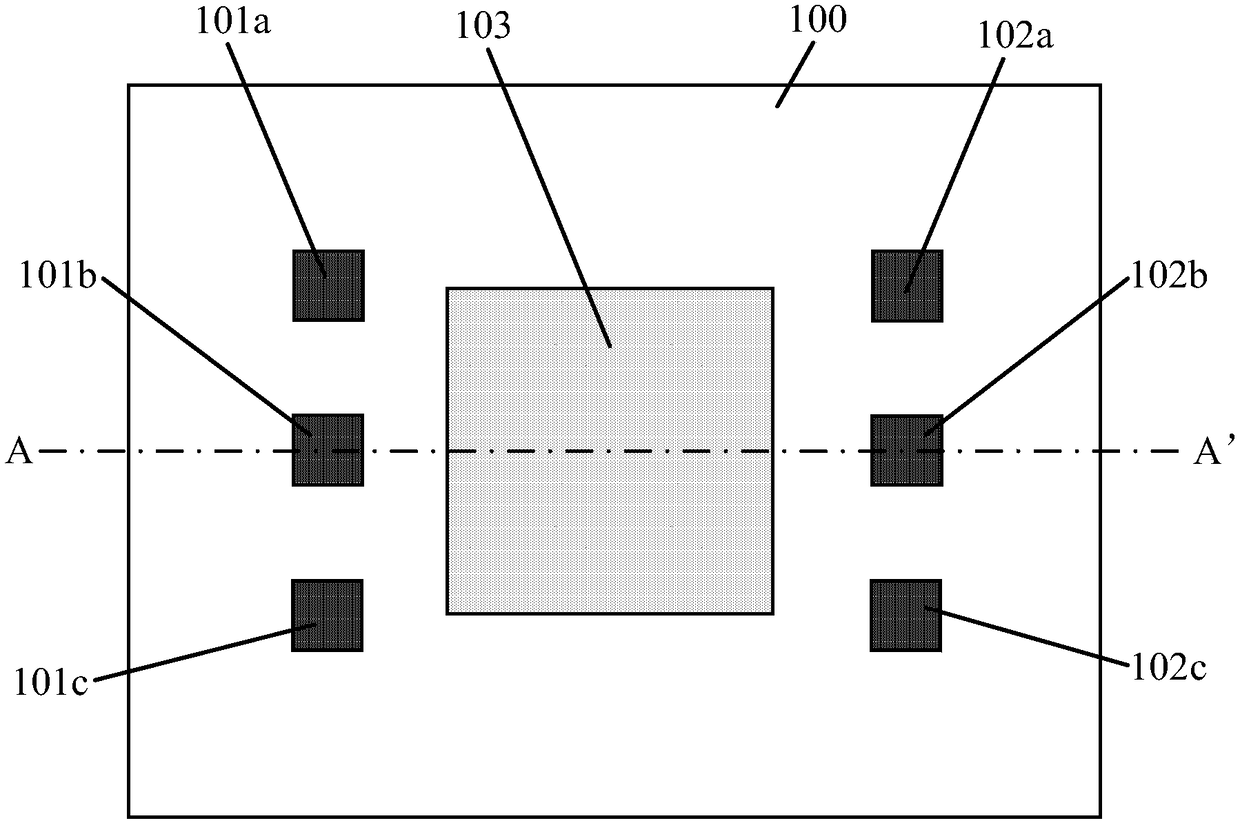

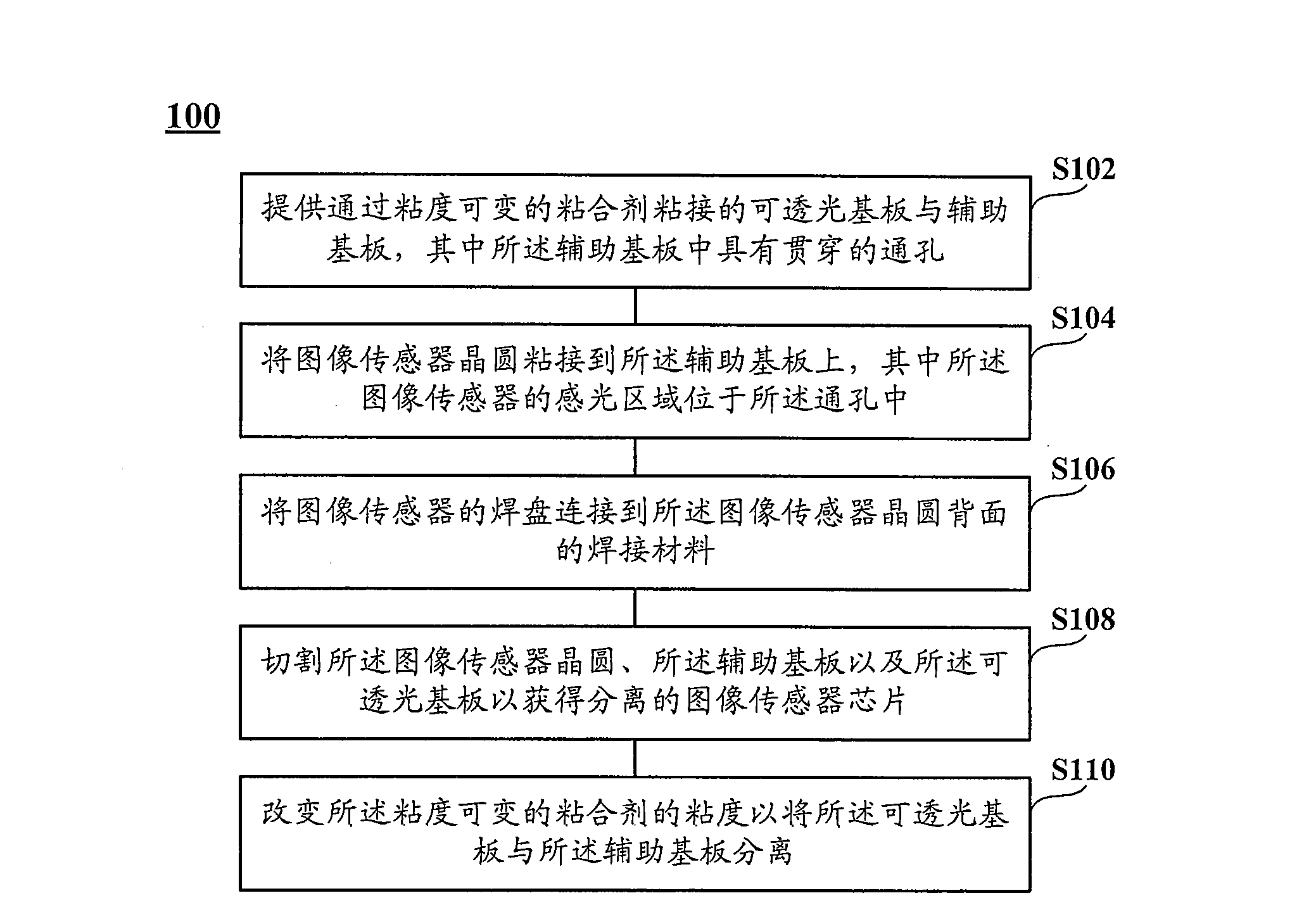

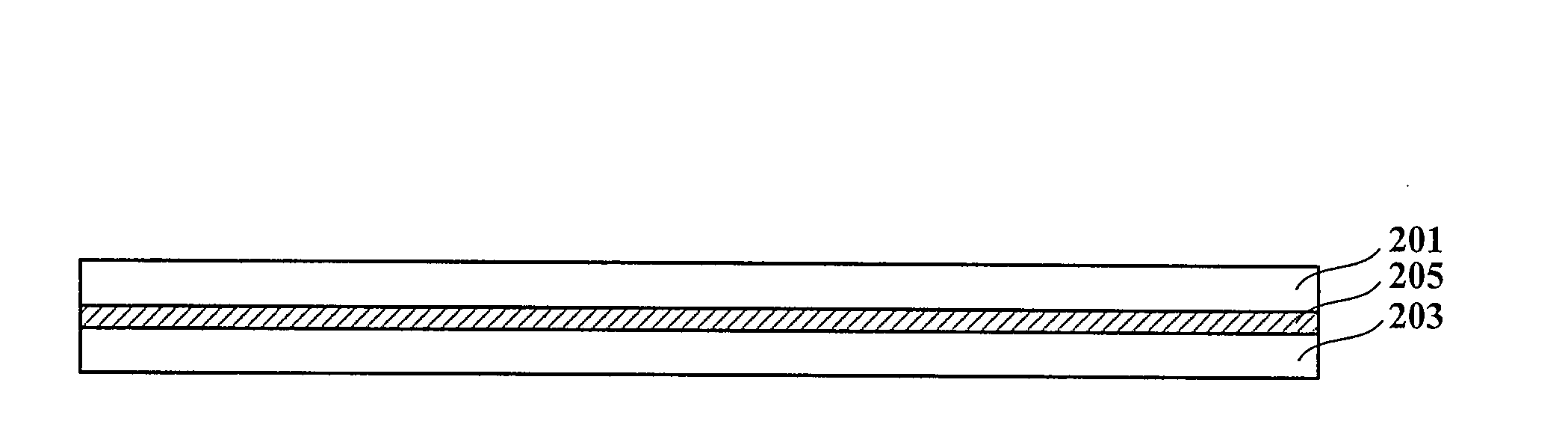

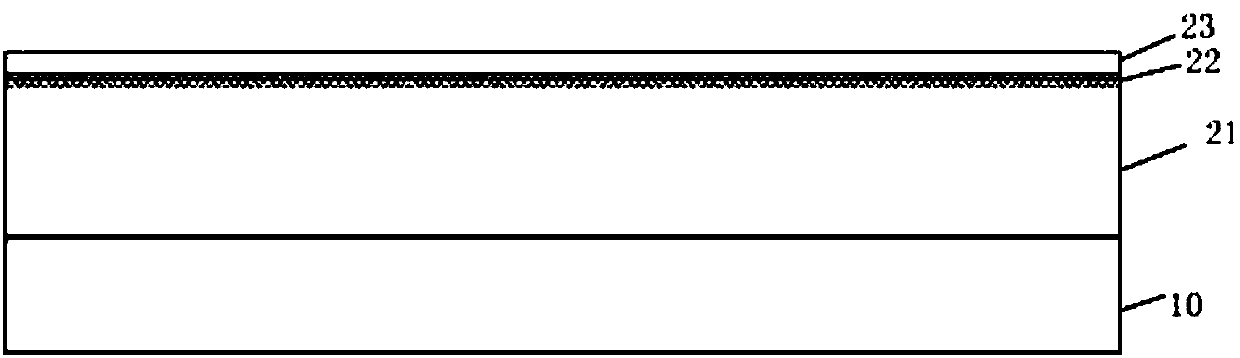

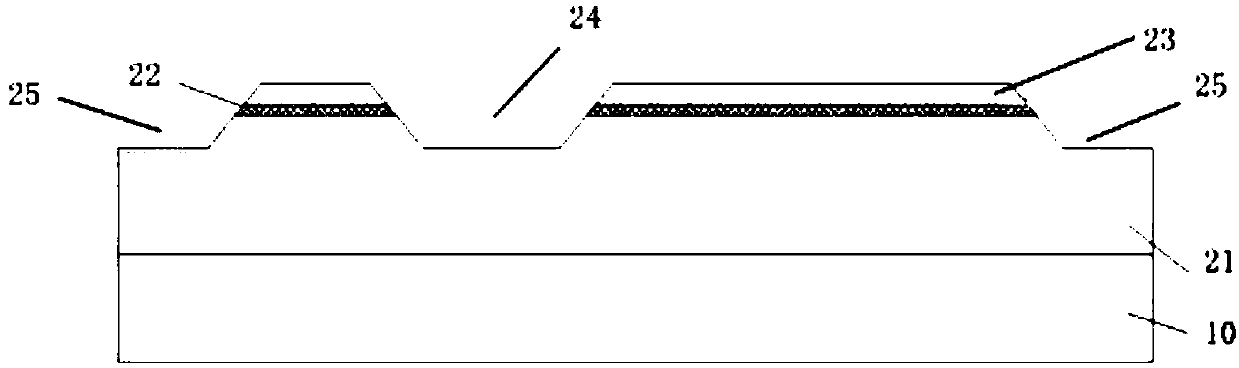

Image sensor packaging method

ActiveCN102623471AReduce packaging costsReduce lossesRadiation controlled devicesAdhesiveEngineering

The invention discloses an image sensor packaging method, which includes: a, providing a light-transmittable substrate and an auxiliary substrate which are adhered by adhesives variable in viscosity, wherein the auxiliary substrate is internally provided with perforated through holes; b, adhering wafers of an image sensor onto the auxiliary substrate, wherein photosensitive areas of the image sensor are positioned in the through holes; c, connecting pads of the image sensor onto welding materials on the backs of the wafers; d, cutting the wafers of the image sensor, the auxiliary substrate and the light-transmittable substrate so as to obtain isolated image sensor chips; and e, changing the viscosity of the adhesives variable in viscosity so as to isolate the light-transmittable substrate from the auxiliary substrate.

Owner:GALAXYCORE SHANGHAI

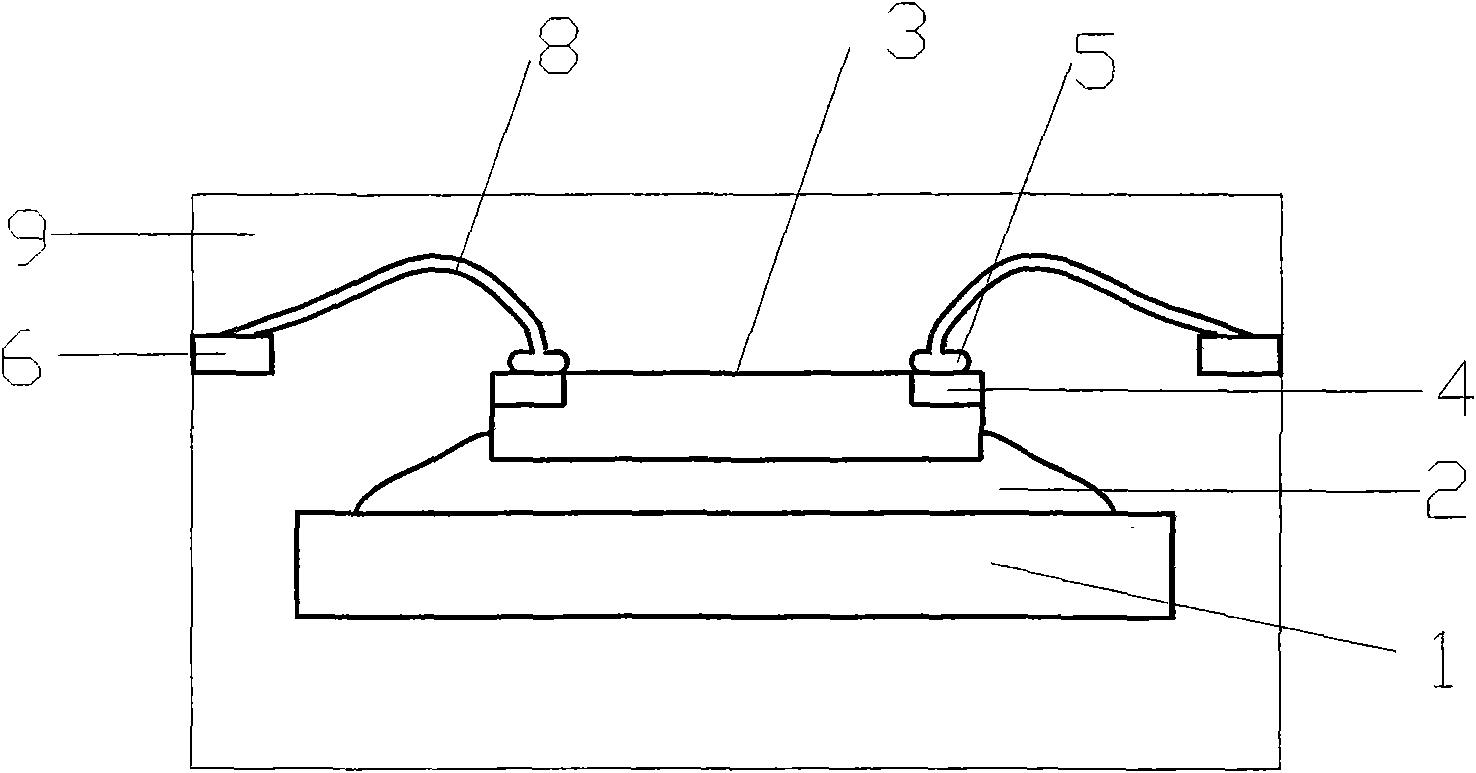

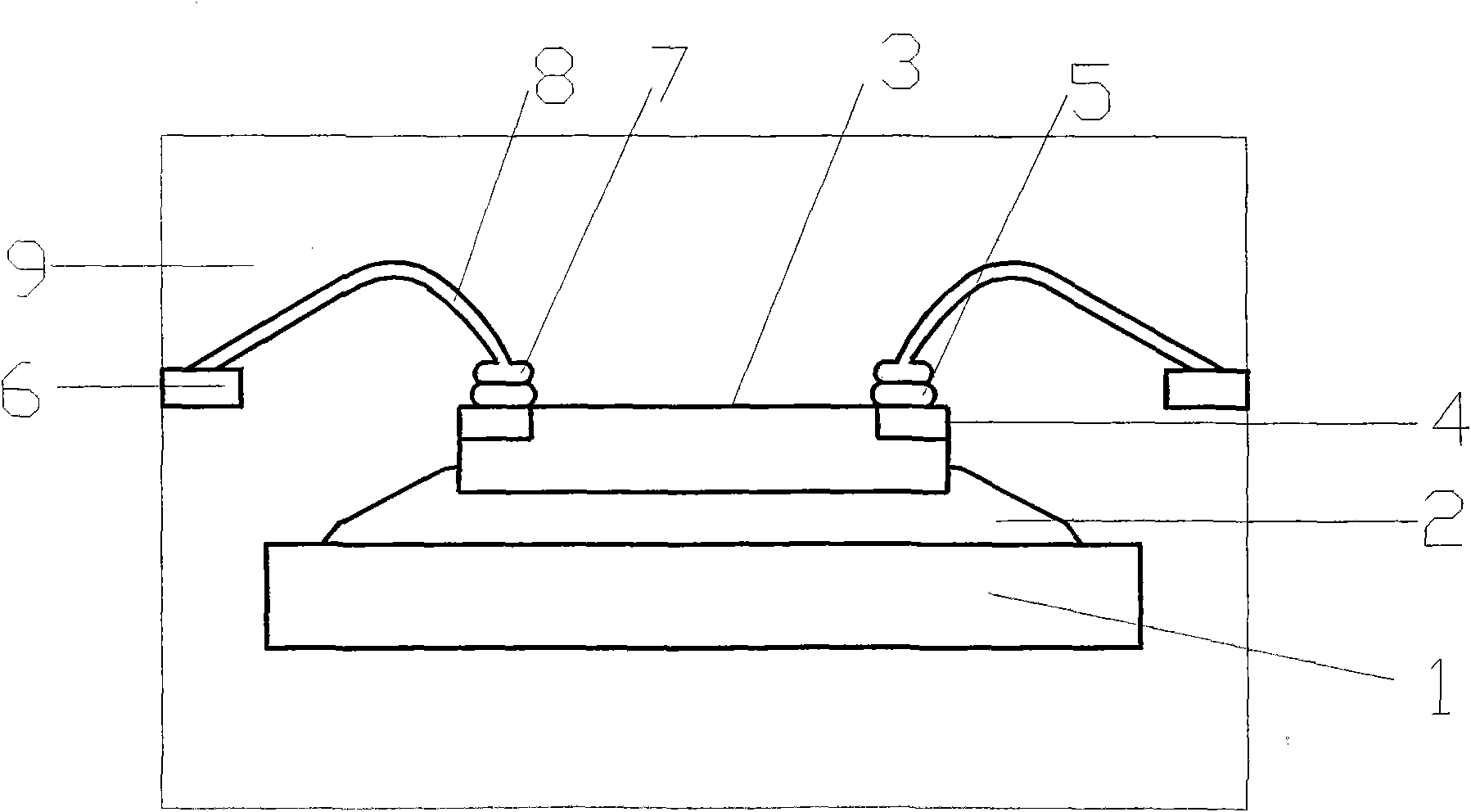

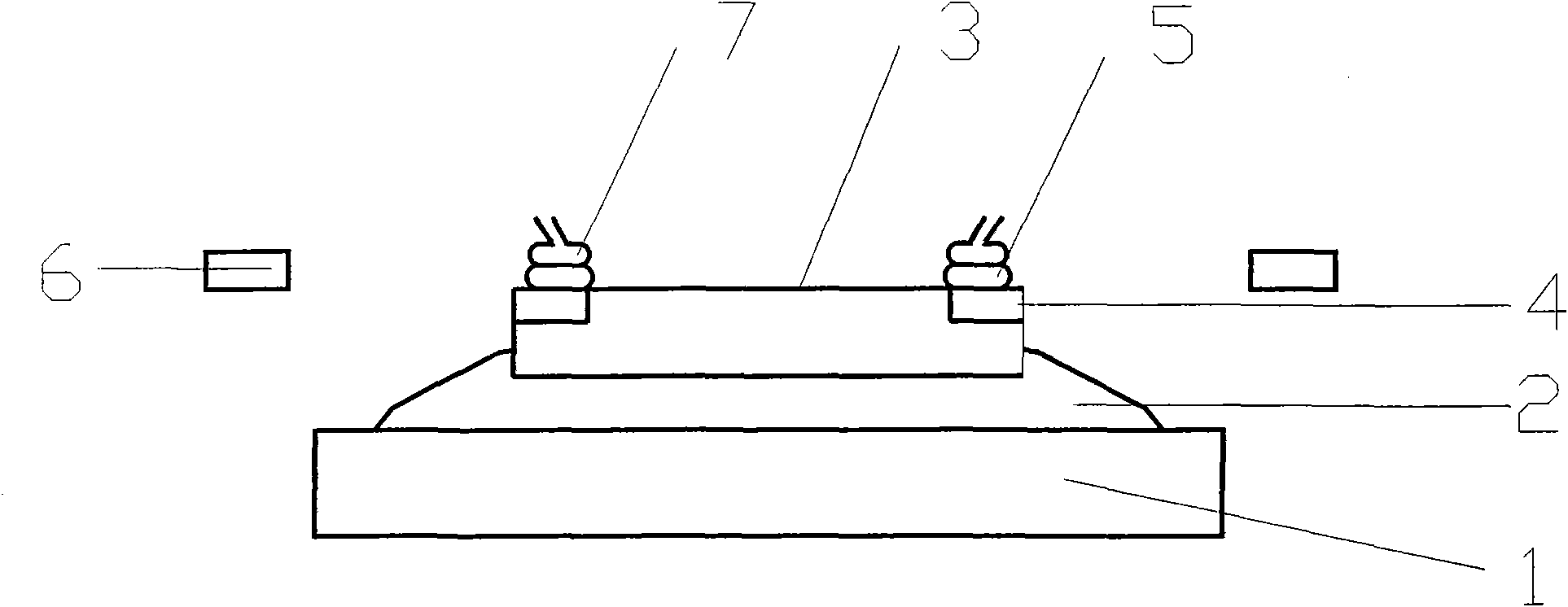

Production method of encapsulated component of copper wire bonding IC chip

InactiveCN101626008ASolving the crater puzzleSaving wire costSemiconductor/solid-state device detailsSolid-state devicesGold ballPlastic packaging

The invention relates to a production method of an encapsulated component of a copper wire bonding IC chip. A welding plate of the IC chip is provided with a golden ball on which copper bonding balls are stacked, an arch wire is provided with a copper welding point on an inner pin of a lead frame, and a welding plate of the IC chip is connected with the pin of the lead frame. A plastic packaging body is covered on the IC chip, the copper balls stacked on the packed golden ball, the copper welding point of the arch wire on the inner pin of the lead frame and partial inner pins of the lead frame to form a whole circuit. The production method comprises wafer grinding, wafer scribing, core installing, press welding, plastic package, post curing, printing, punching separation, inspection, packaging and warehousing. The invention has simple and reasonable structure, easy use and high qualified rate in encapsulation and testing as well as high reliability, avoids craters, the intensity of the welding point is improved, the pull force of copper welding wires and the shearing strength of the welding point through the production method are greater than that in a copper (golden) bonding production method through direct wire threading, and unsoldering can not happen to the inner welding point.

Owner:TIANSHUI HUATIAN TECH

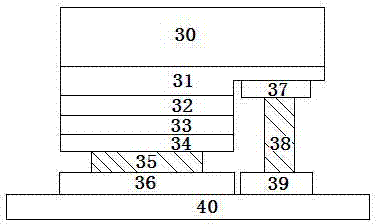

Method for manufacturing inverted LED chip

InactiveCN102403425AImprove packaging yieldAvoid WeldingSemiconductor devicesOhmic contactLight reflection

Owner:俞国宏

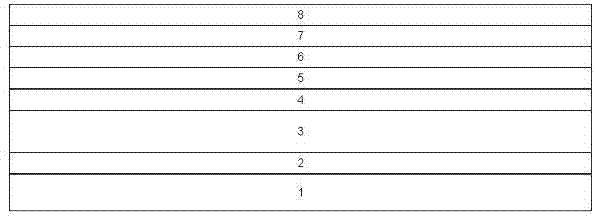

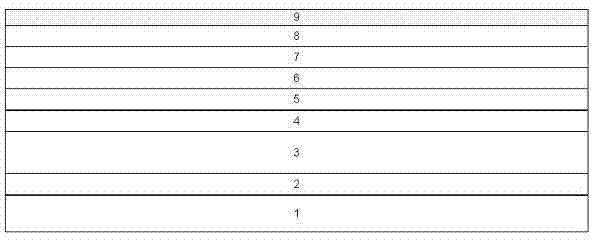

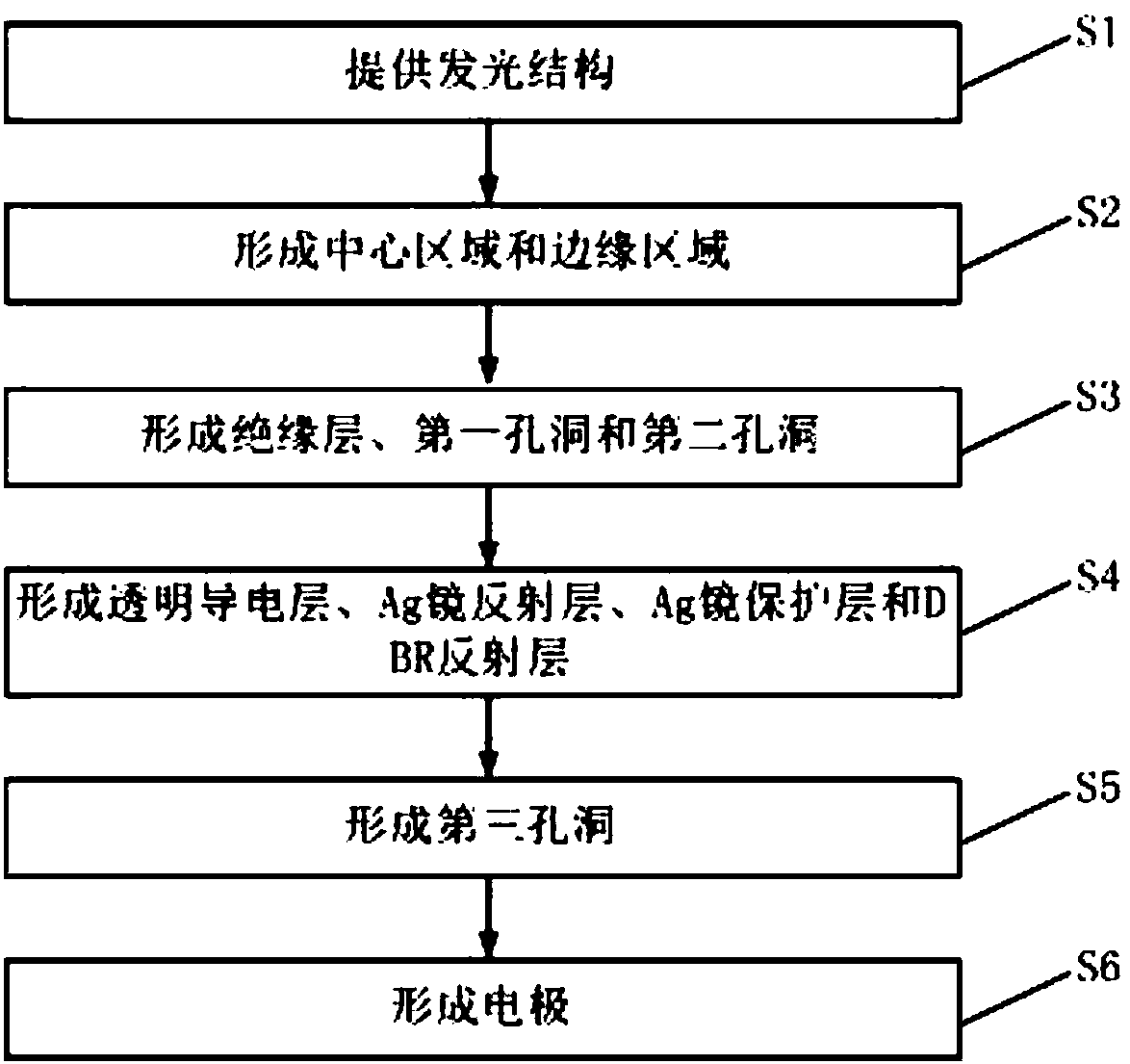

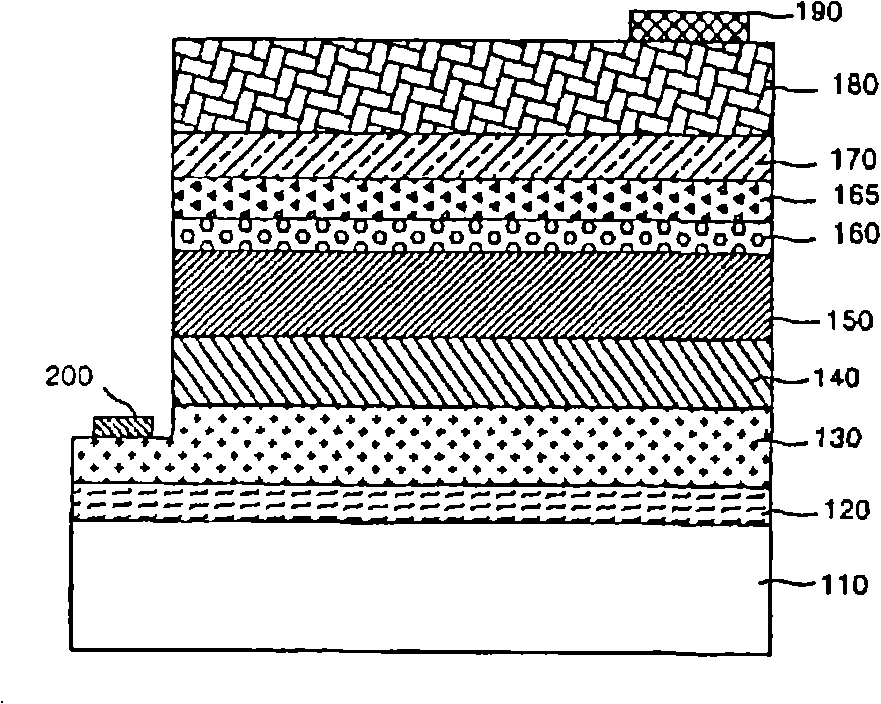

Highlight flip LED chip having insulating protection structure and manufacturing method thereof

PendingCN107863434AImprove IR yieldImprove light extraction efficiencySemiconductor devicesMirror reflectionActive layer

The invention discloses a manufacturing method of a highlight flip LED chip having an insulating layer protection structure. The manufacturing method comprises the steps that a luminous structure is provided; the luminous structure is etched; an insulating layer is deposited on the surface of the luminous structure; the insulating layer is etched so that a first hole and a second hole are formed;and a transparent conductive layer, an Ag mirror reflection layer, an Ag mirror protection layer and a DBR reflection layer are formed on the surface of the insulating layer and in the first hole andthe second hole. The insulating layer is formed on the surface or the side edge of the first semiconductor layer, the active layer and the second semiconductor layer so that the insulating layer is enabled to cover the bare part of the luminous structure, the Ag can be prevented from migrating to the bare part of the active layer under the effect of the electric field formed by the first semiconductor layer and the second semiconductor layer and the IR yield rate of the chip can be enhanced. Furthermore, the Ag mirror reflection layer covering the insulating layer can effectively reflect out the light emitted by the side edge of the luminous structure so as to enhance the luminous efficiency of the chip.

Owner:FOSHAN NATIONSTAR SEMICON

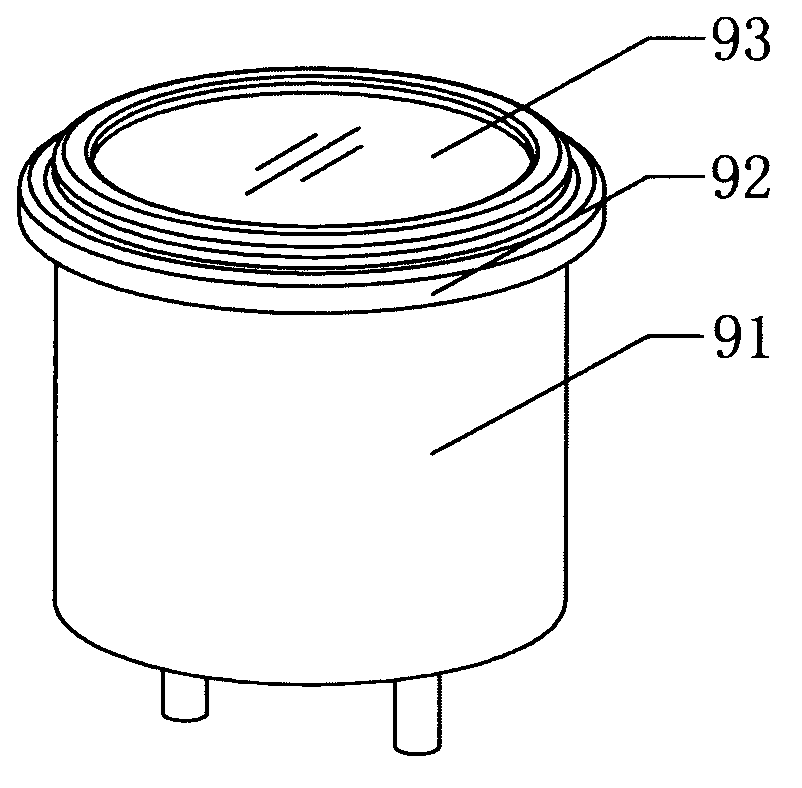

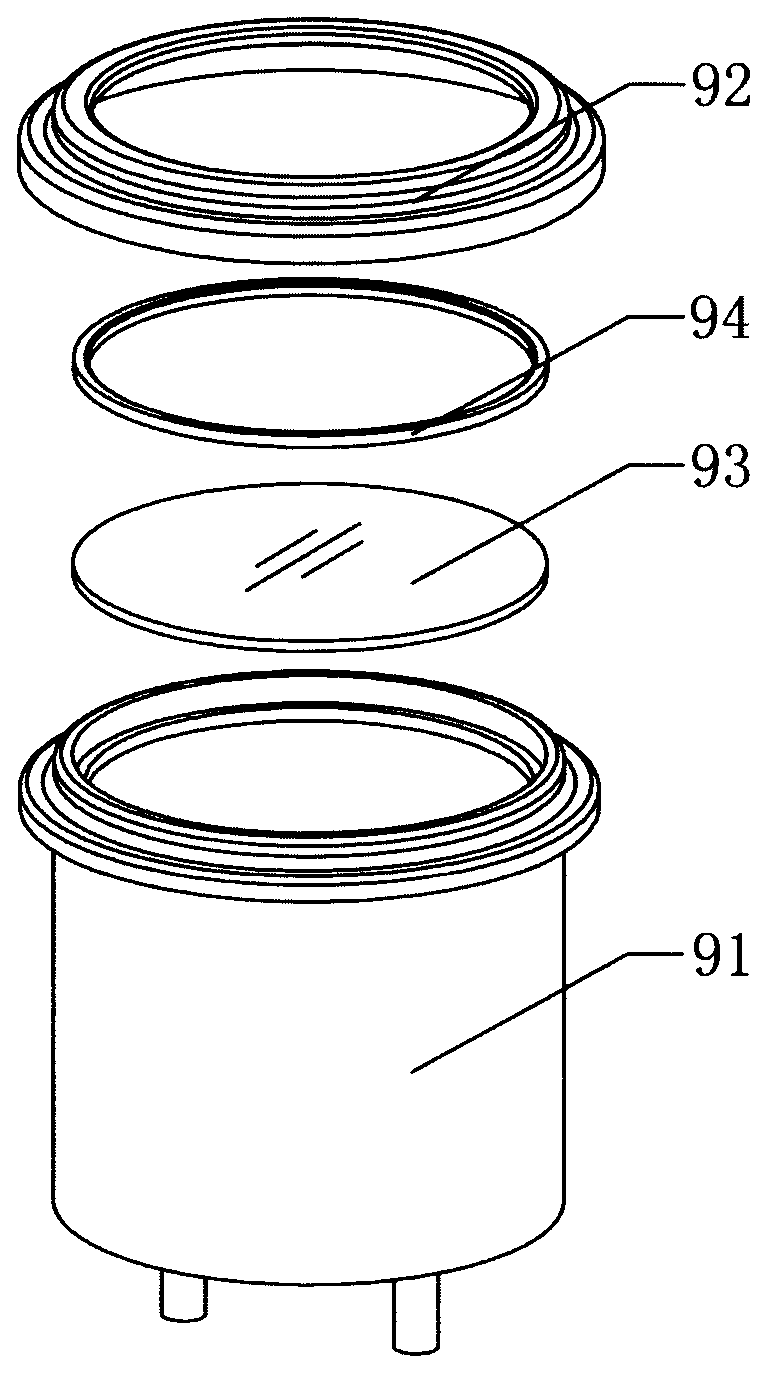

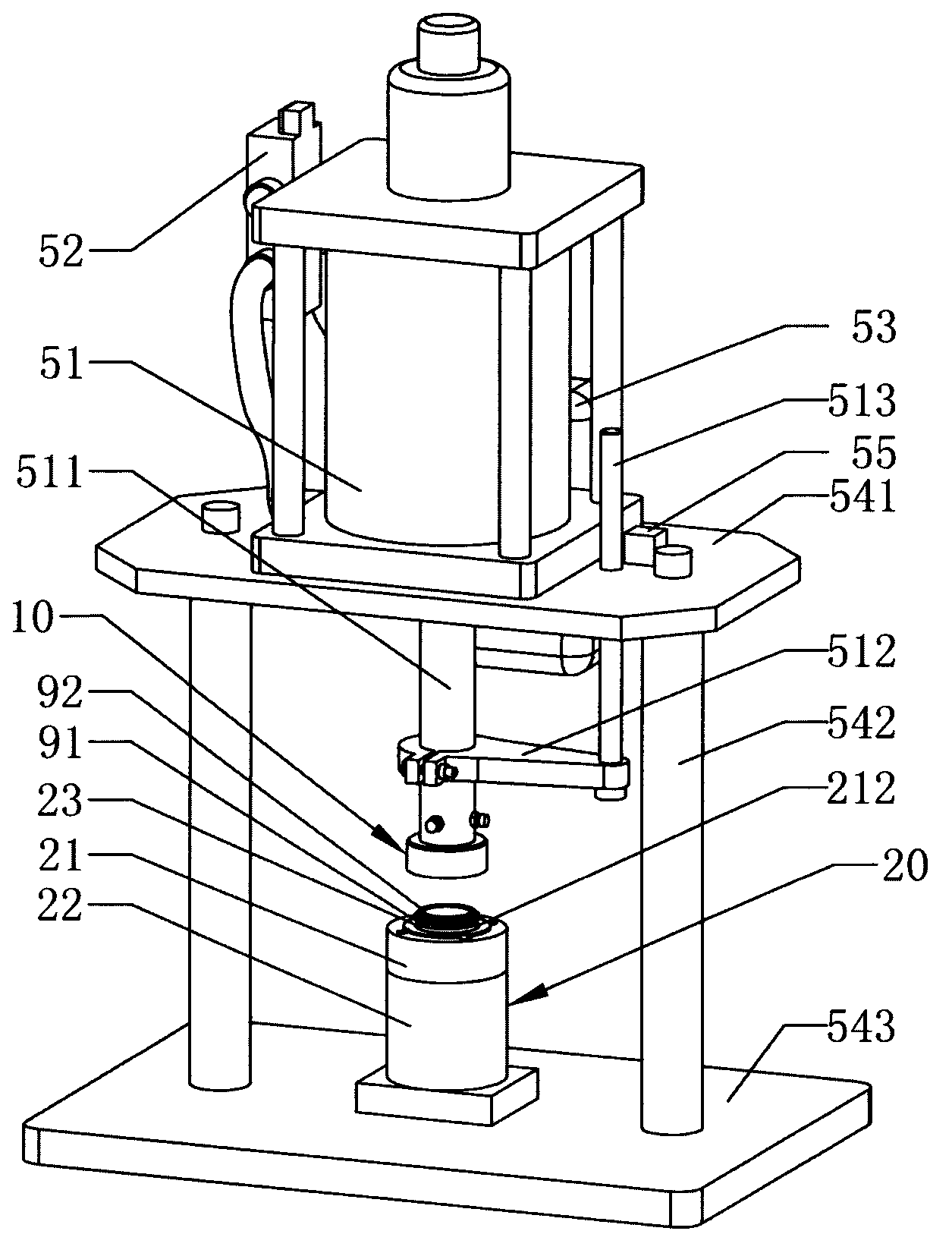

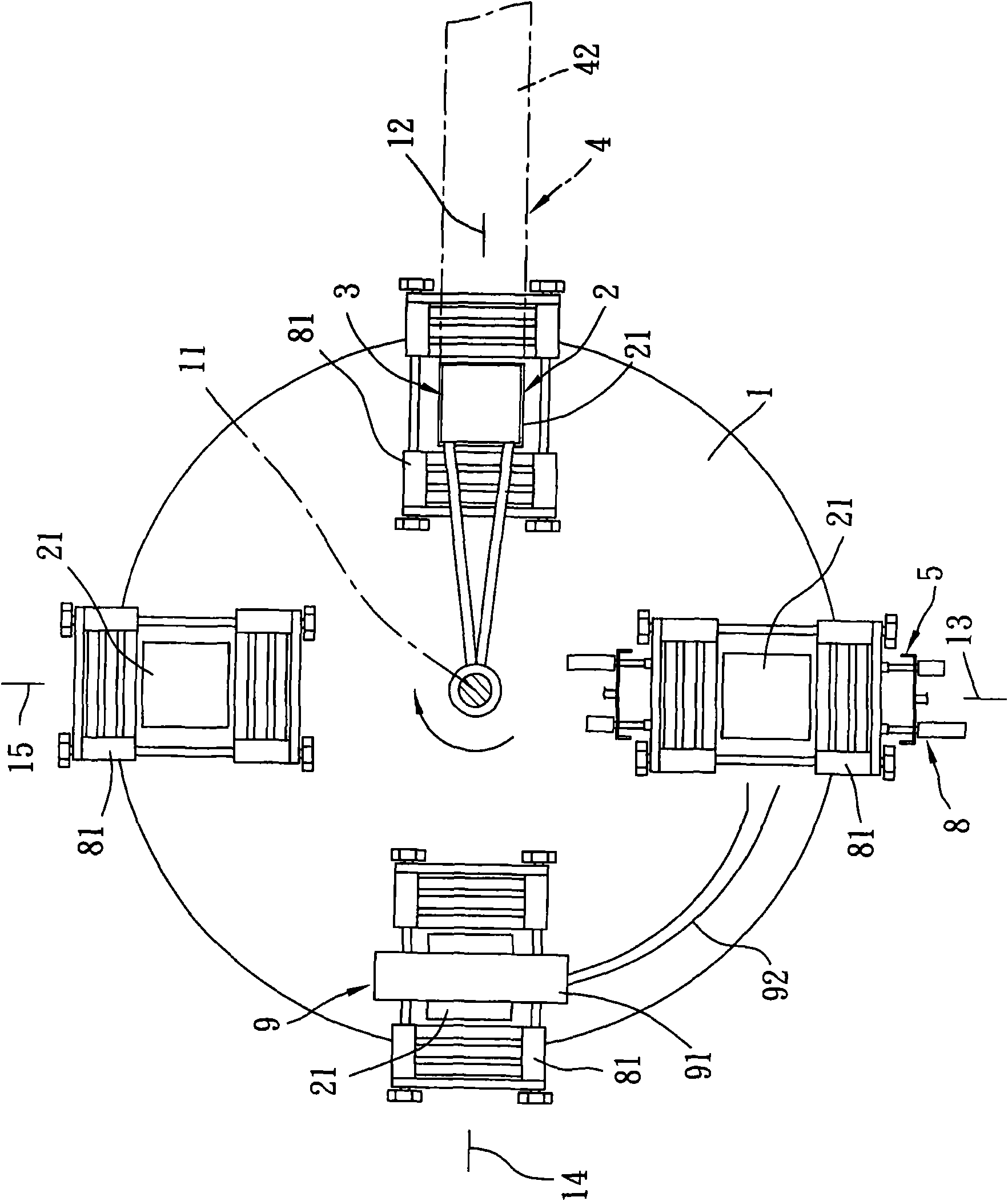

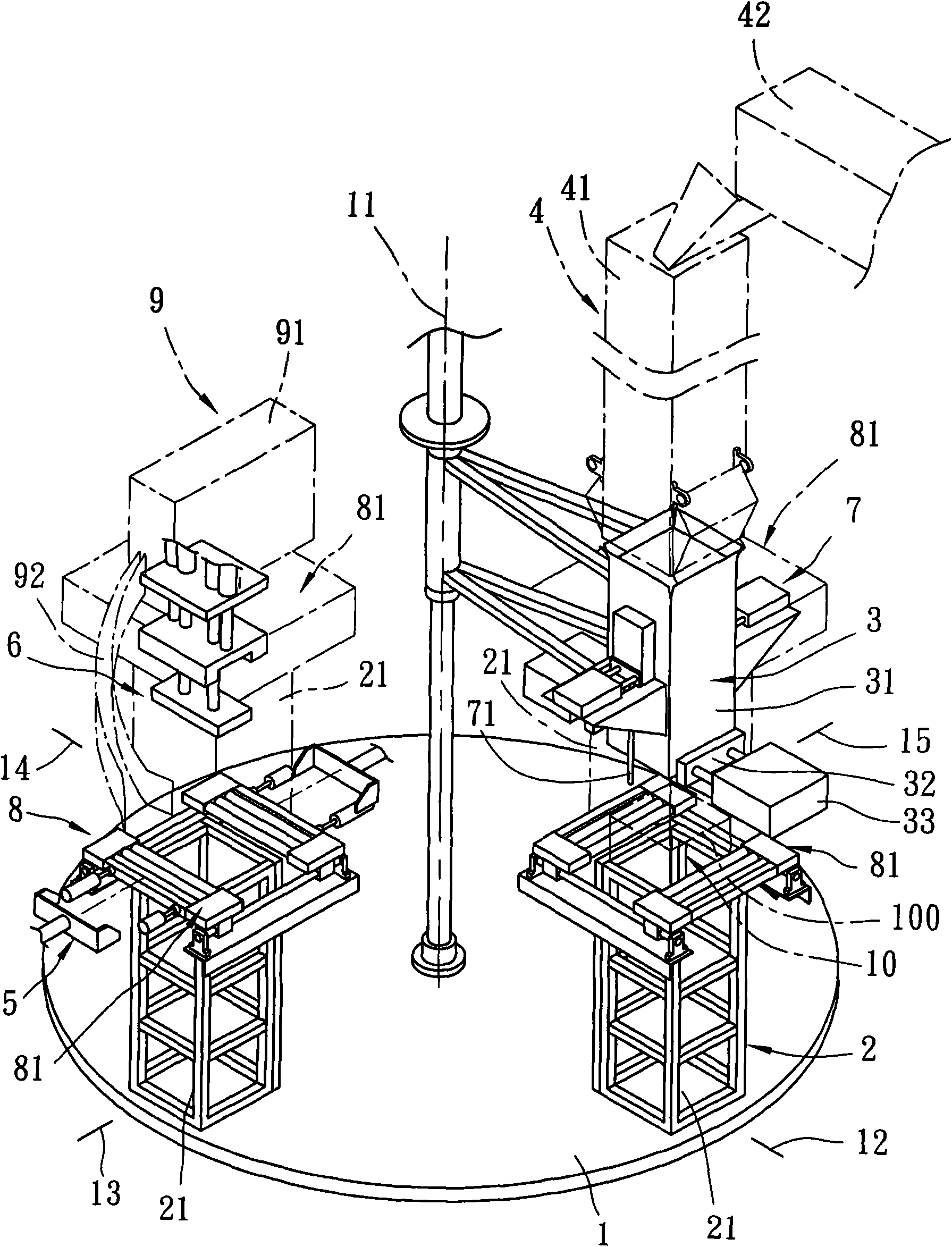

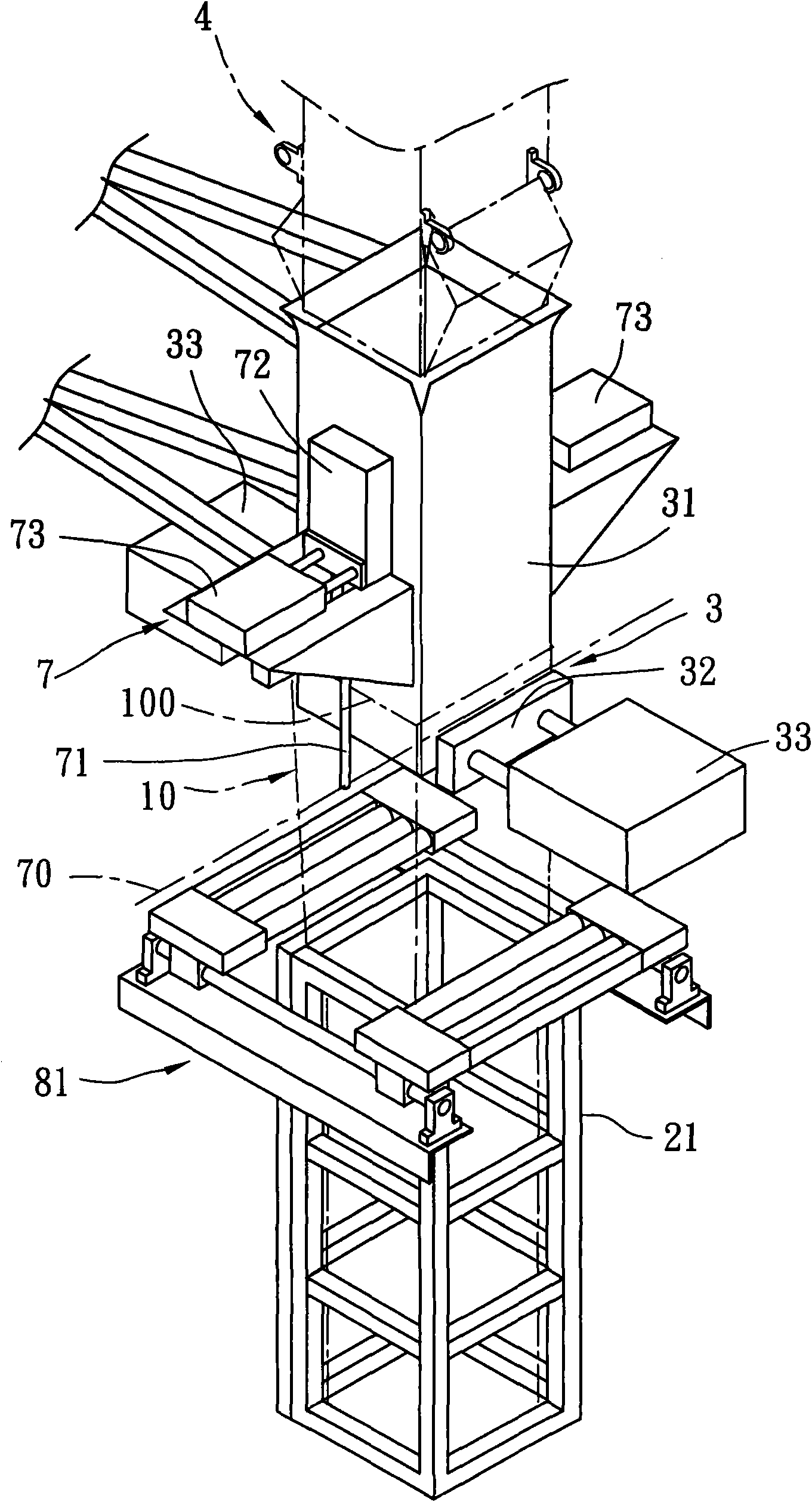

Meter packaging machine and meter packaging method thereof

InactiveCN103252631AFirmly connectedAccurate and quick axial alignmentMetal working apparatusGlass coverEngineering

The invention relates to the technical field of meter packaging machinery, in particular to a meter packaging machine and a meter packaging method thereof. The meter packaging machine comprises a frame, a drive device, a control mechanism and a die assembling module. The drive device is fixedly mounted on the upper portion of the frame. The die assembling module is disposed on the lower portion of the drive device. The control mechanism controls the drive device to operate. The die assembling module is driven by the drive device to perform die assembling. The die assembling module comprises an upper pressing die and a lower die. The upper pressing die is connected with the drive device. The lower die is fixedly mounted on the lower portion of the frame. By the meter packaging machine, meter elements can be placed in a sleeve conveniently before die assembling of the upper pressing die and the lower die, axial alignment of the meter elements can be achieved fast and accurately, and according packaging yield and efficiency can be increased. In addition, during packaging, attachment of dust or impurities to a glass cover plate can be avoided.

Owner:FENGHUA HEARTY MOTORMETERS

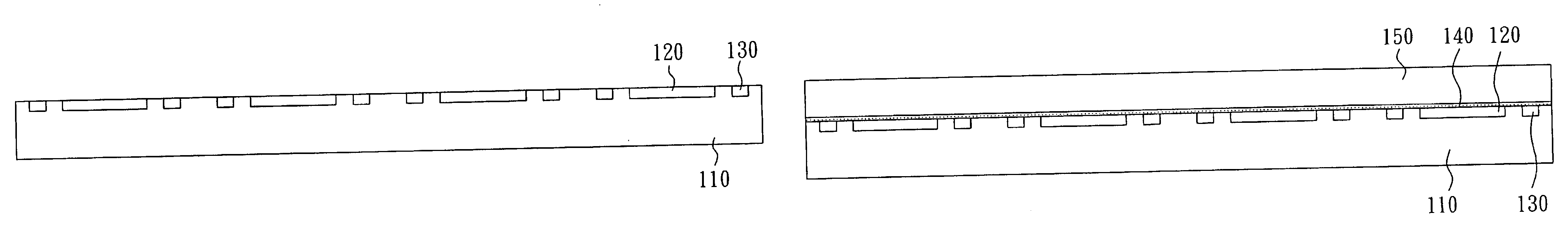

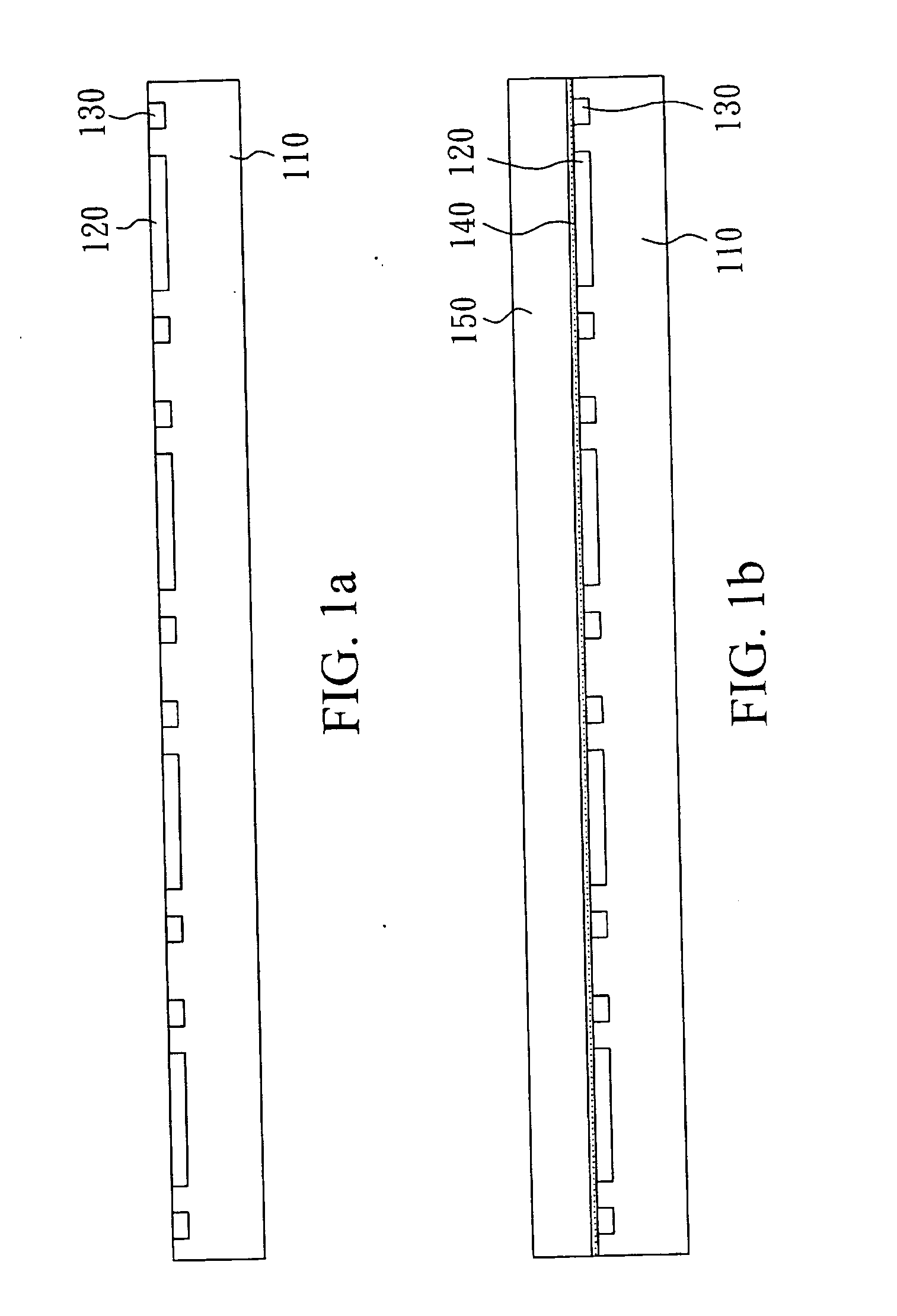

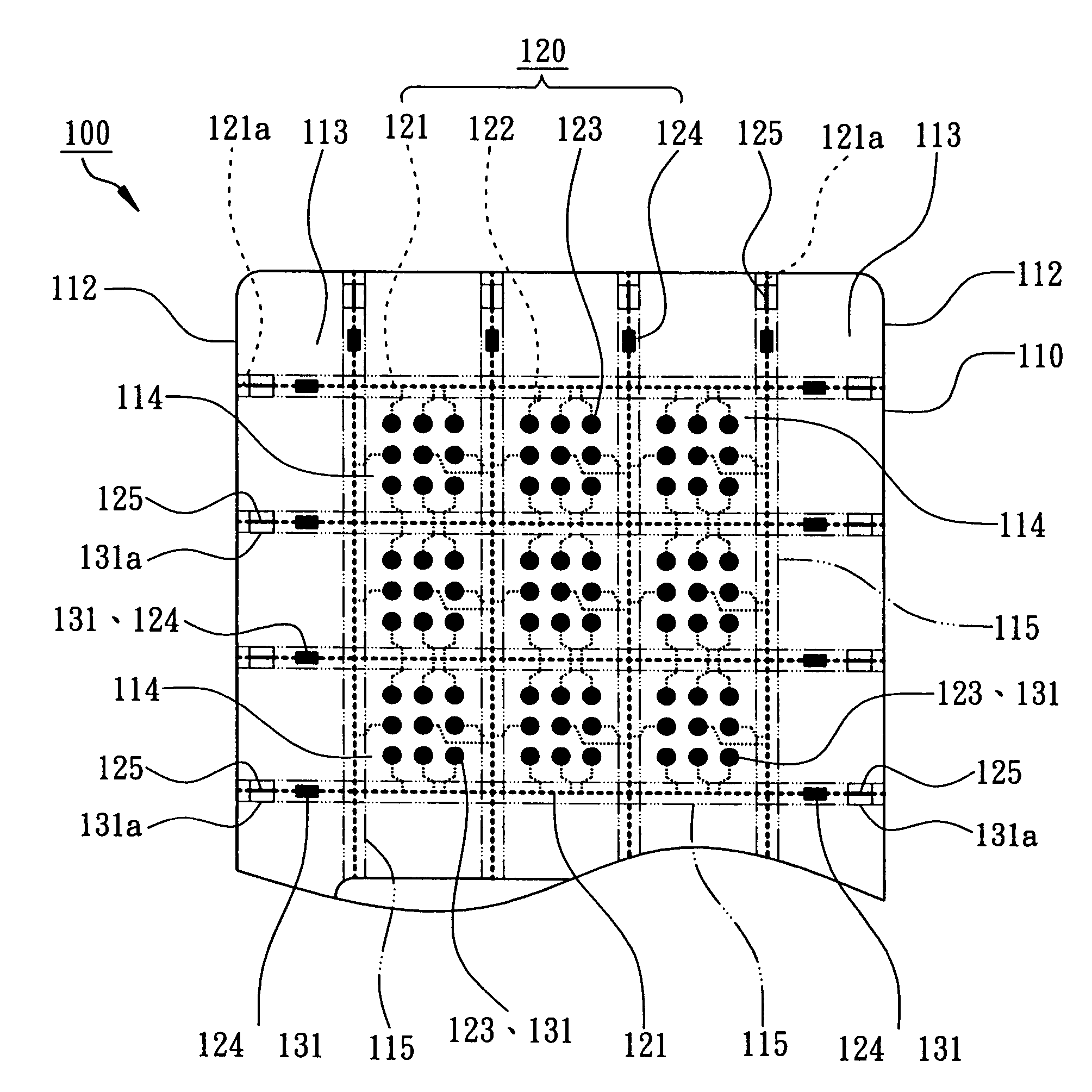

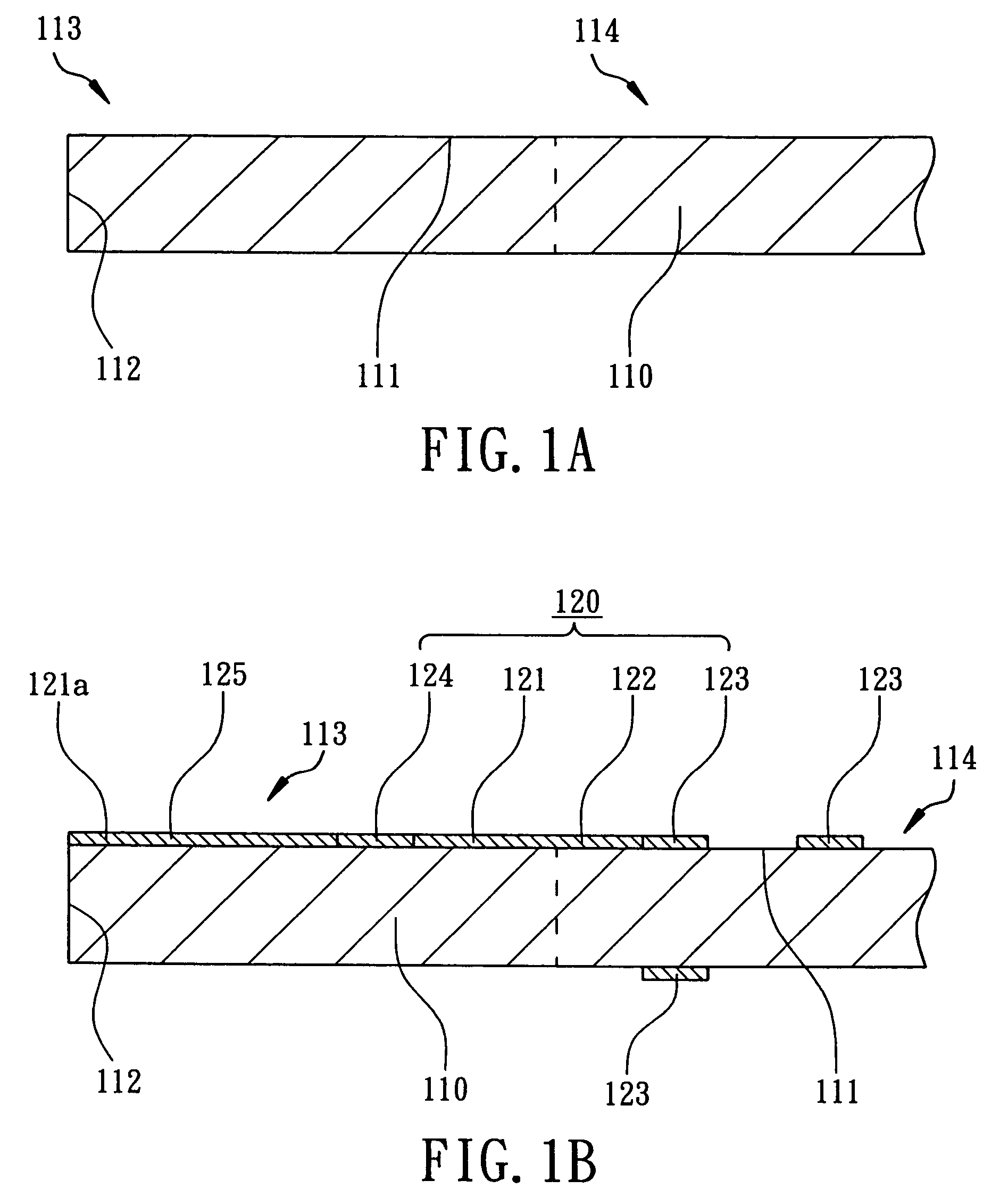

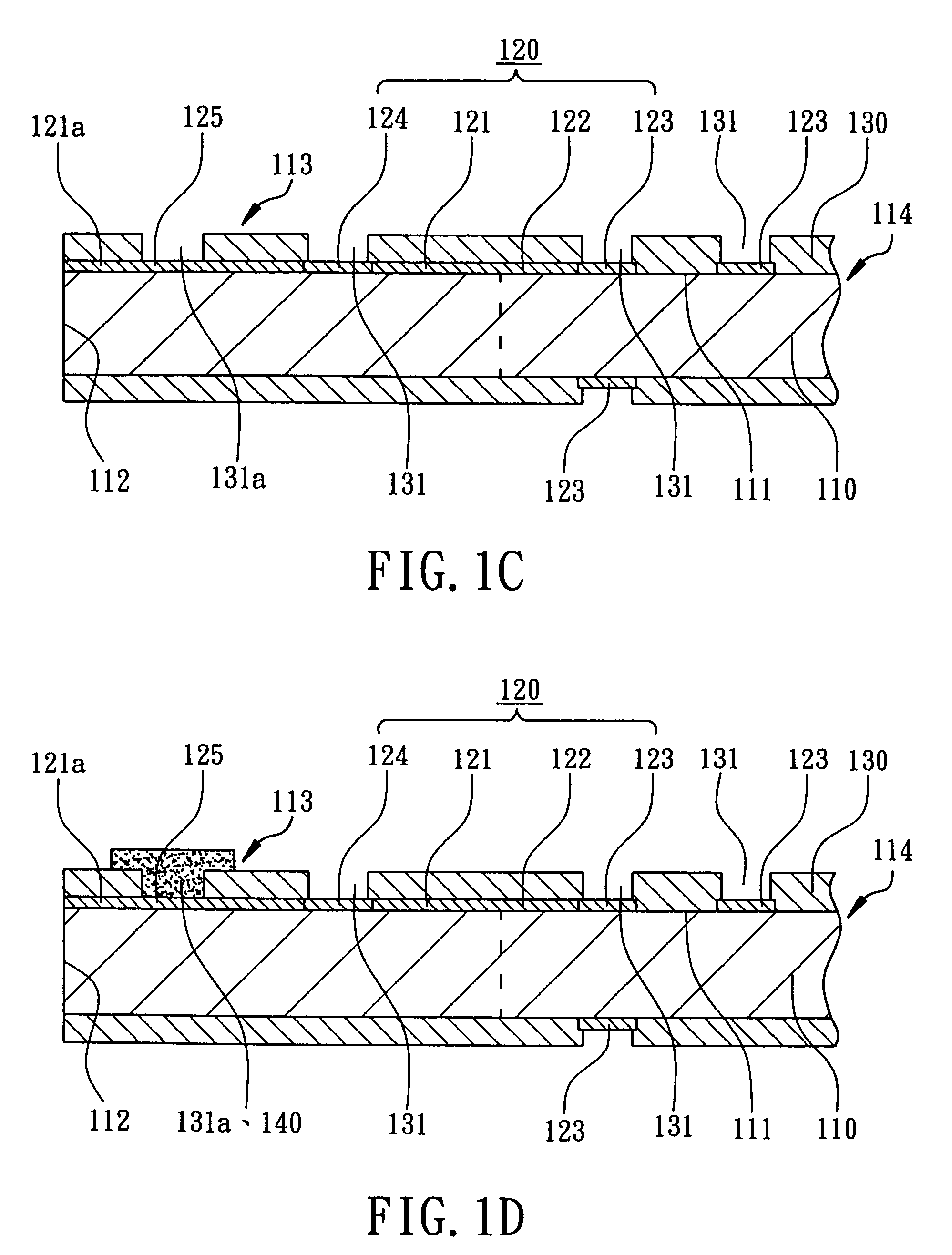

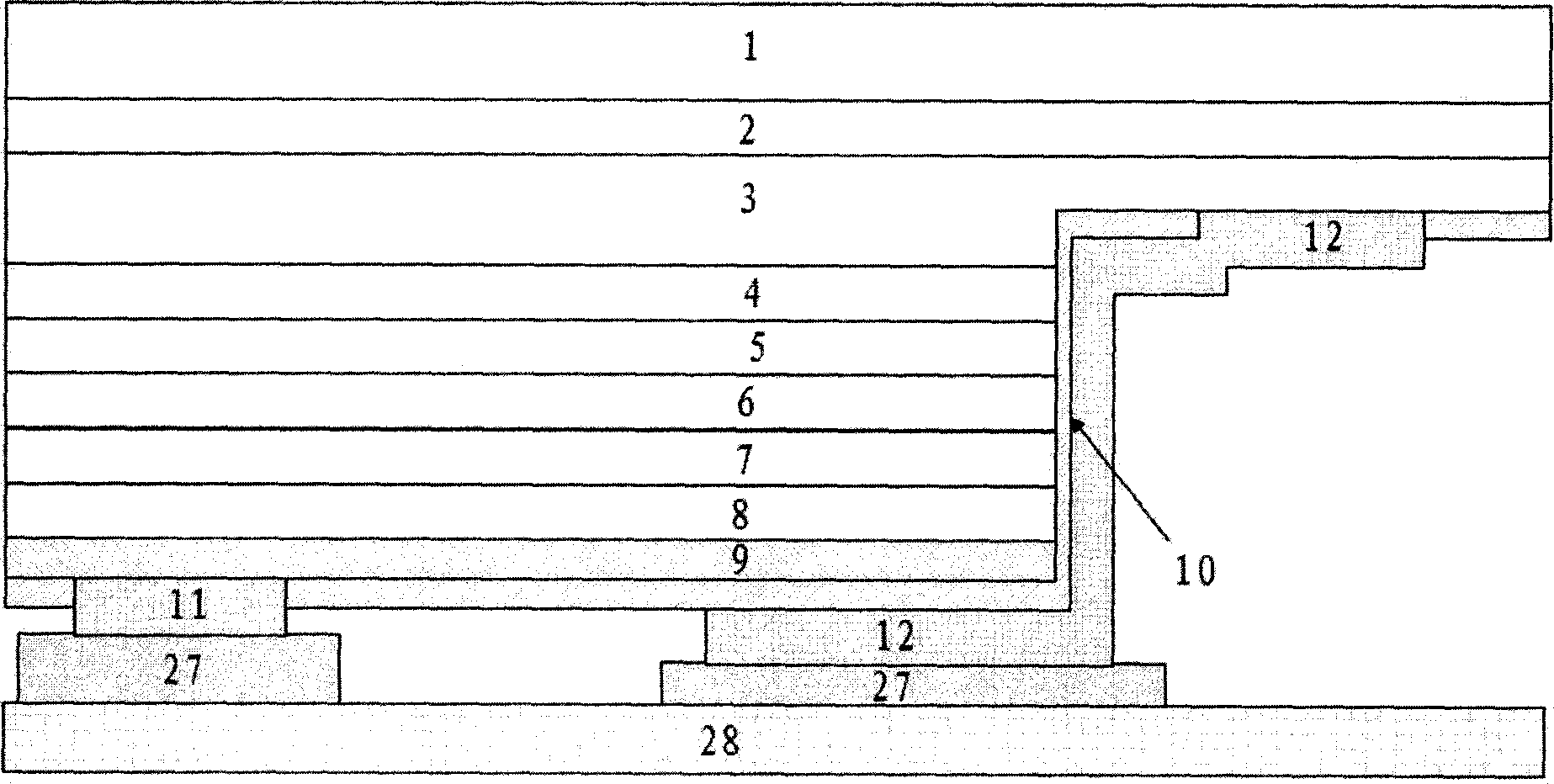

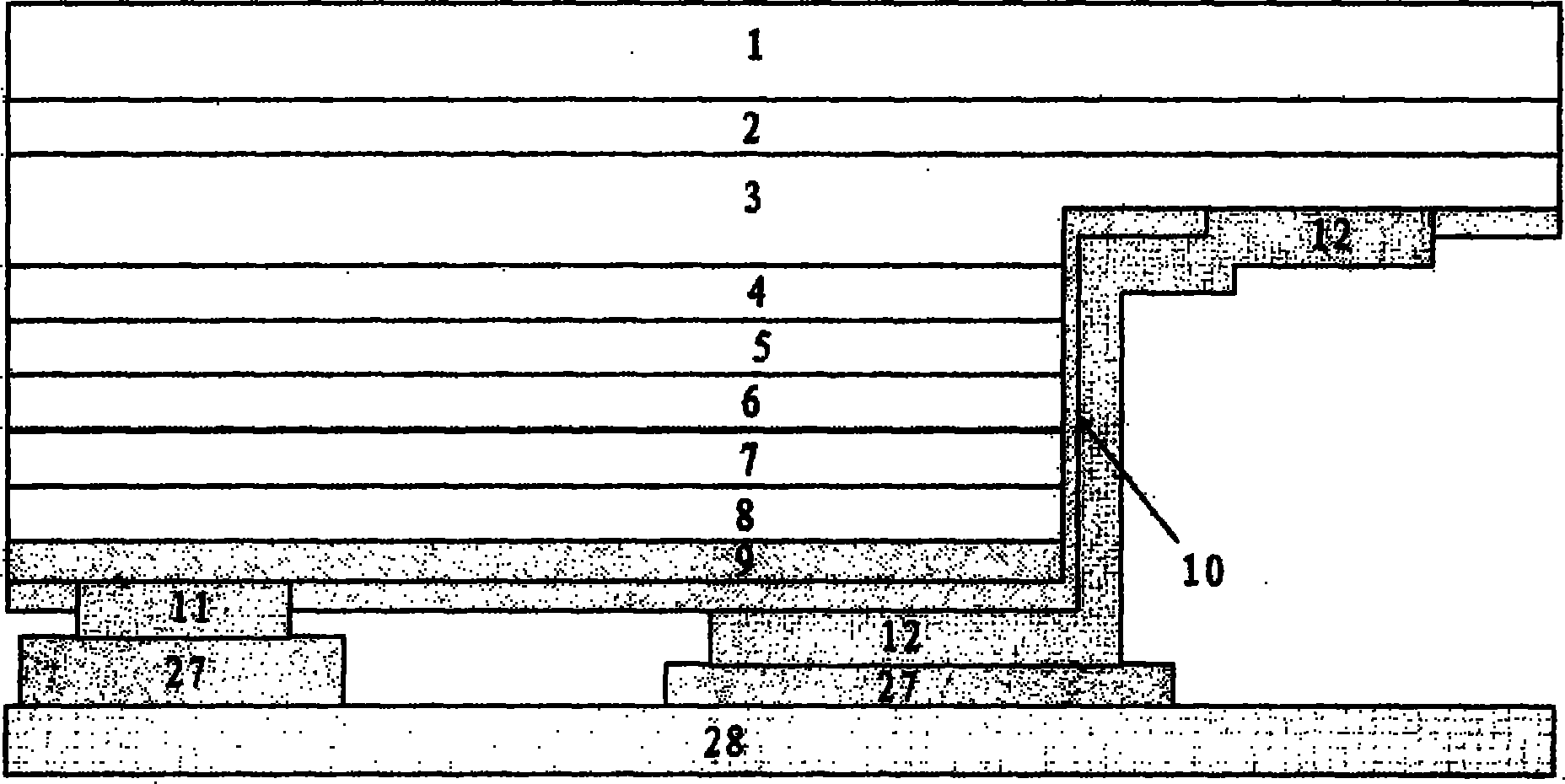

Image sensor package structure and method for fabricating the same

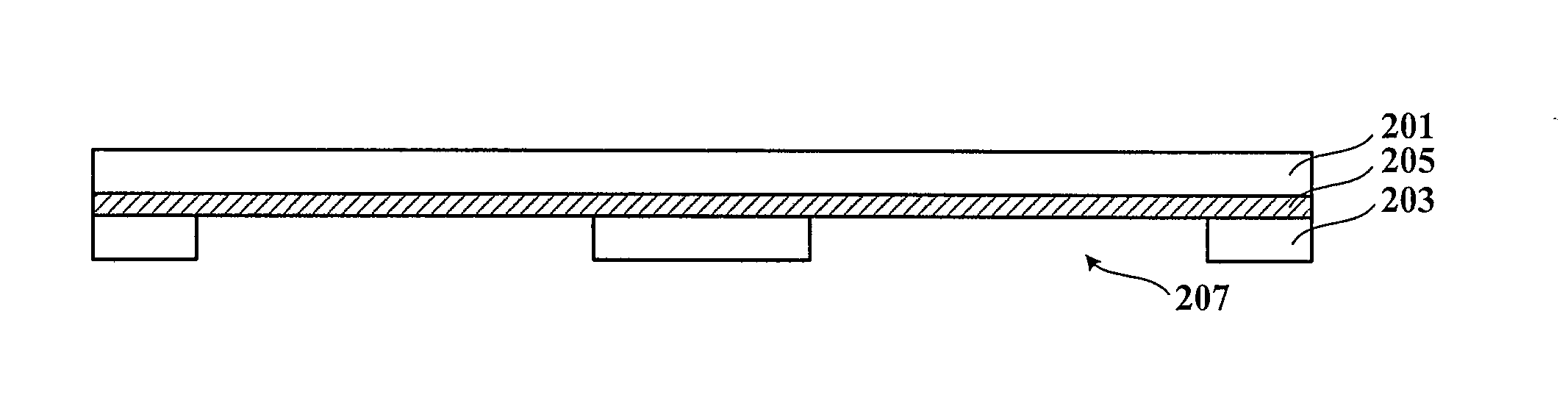

InactiveUS20060024857A1Avoid defectsImprove package yieldSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringIntegrated circuit

A method for fabricating an image sensor package is disclosed, comprising: providing a wafer having a plurality of image sensor integrated circuits, each of which has a photosensitive active region and at least one first bonding pad; joining a transparent protecting material to the wafer wherein the photosensitive active region of the image sensor integrated circuit is covered by the transparent protecting material; forming a plurality of through holes in the transparent protecting material, the through holes being correspondingly to the first bonding pad of the wafer to expose the first bonding pad; and dicing the wafer to form a plurality of image sensor integrated circuit components. The method for fabricating an image sensor package of the present invention decreases the defects of the photosensitive active region and reduces the size of the package structure.

Owner:IND TECH RES INST

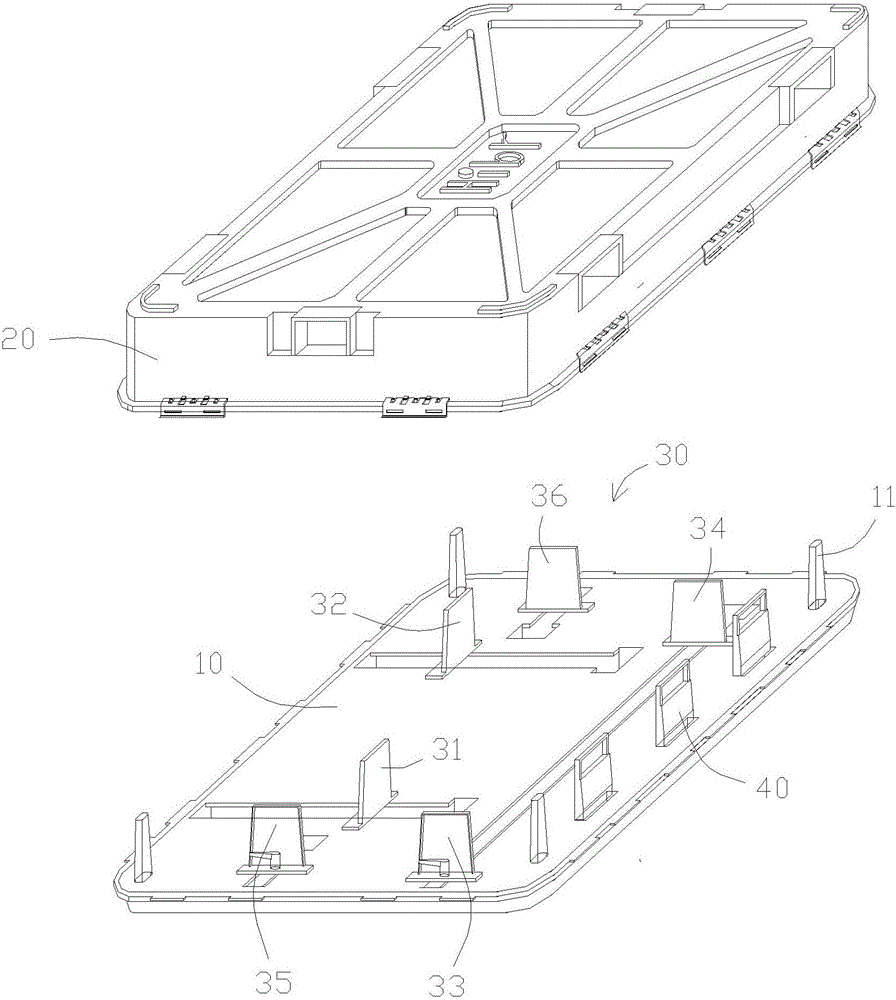

Material packaging machine

ActiveCN102464111AImprove packaging yieldWrapper twisting/gatheringSolid materialBiomedical engineeringPackaging machine

The invention discloses a material packaging machine, which is used for packaging materials in a packaging bag, and comprises a bag-holding device, a compaction device, a flattening device and a clamping device, wherein the bag-holding device is used for clamping an open edge of the packaging bag, so that materials are filled in the packaging bag; the compaction device is used for extruding the materials in the packaging bag; the flattening device is used for pulling the open edge into a flat shape; and the clamping device is used for clamping the downside part of the open edge. In the invention, the open edge of the packaging bag is flattened by using the flattening device, and the clamping device is matched to clamp the packaging bad with a flattened open edge, in such a way, the packaging bag can be sealed smoothly and perfectly, and a situation of greatly improving the packaging yield of products can be ensured.

Owner:AGRI TECH RES INST

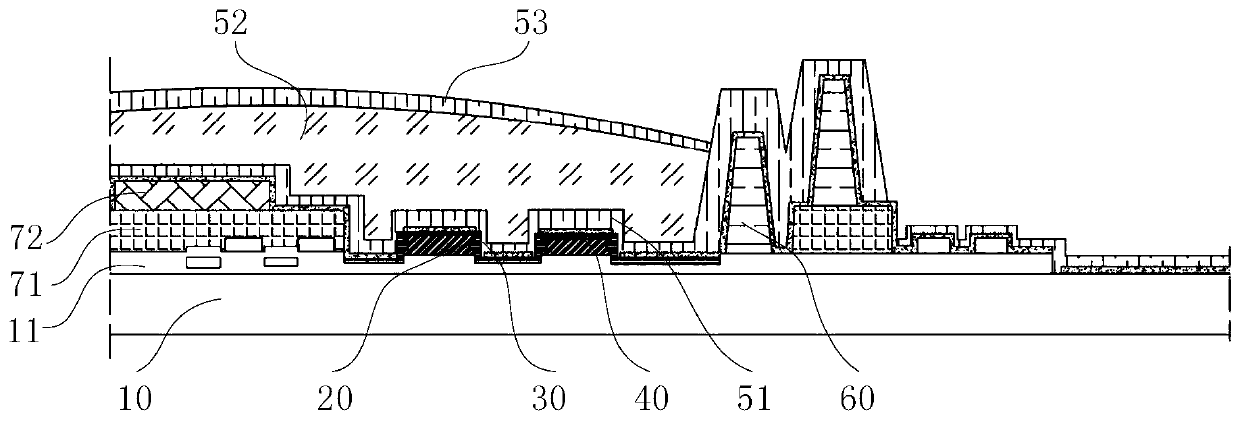

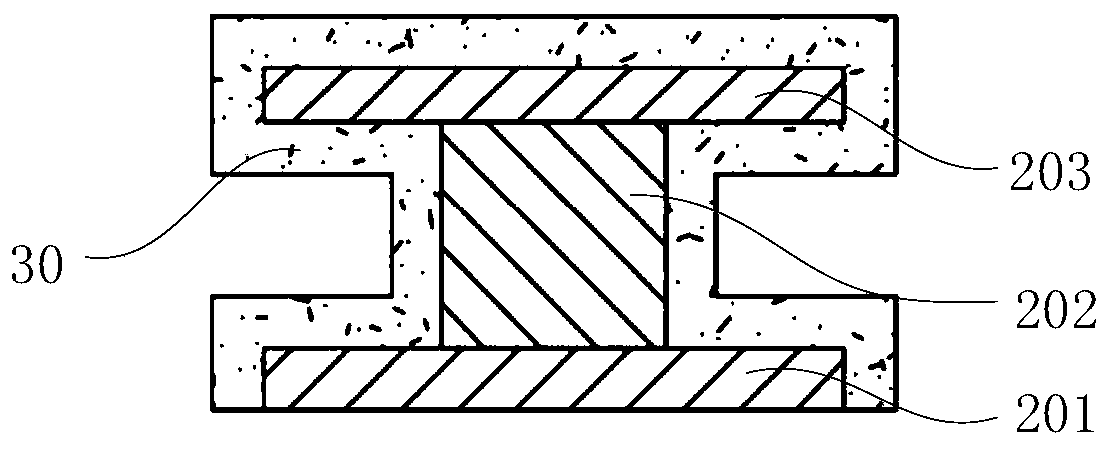

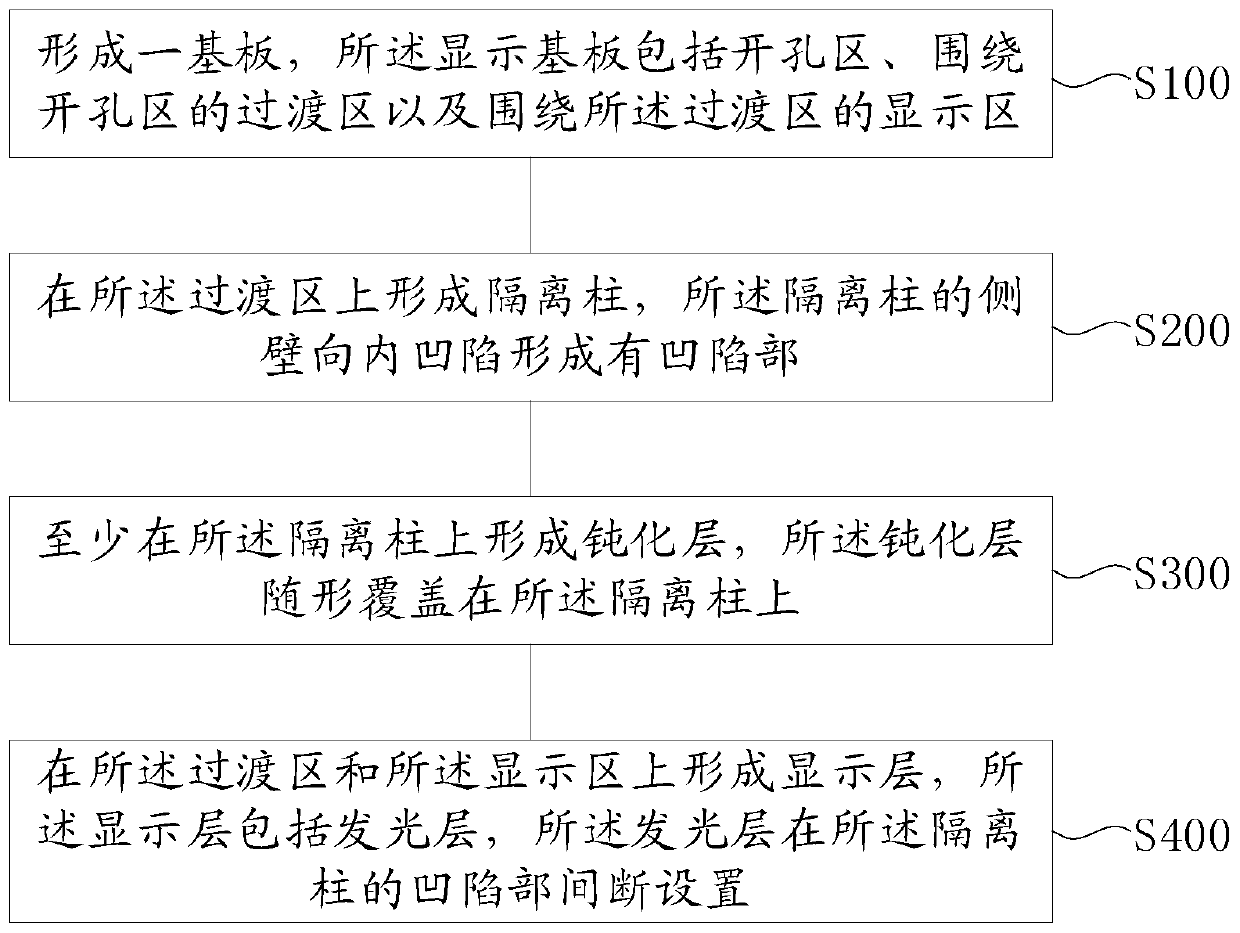

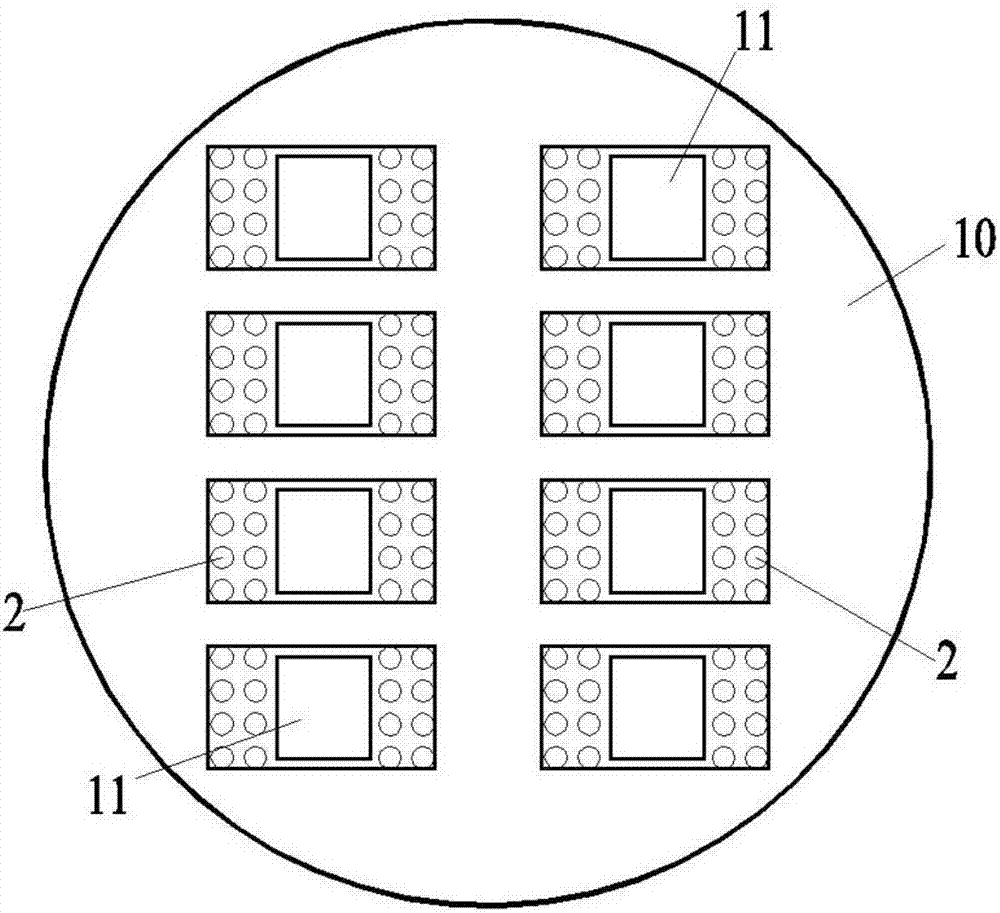

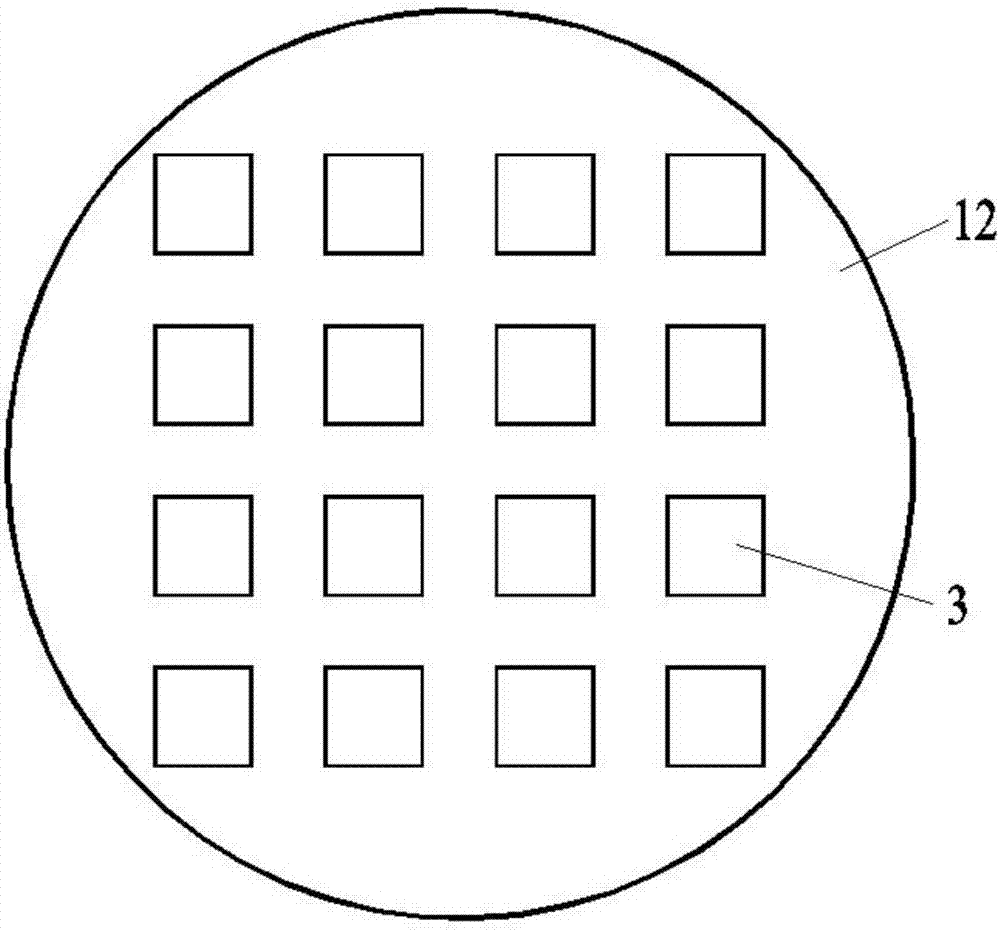

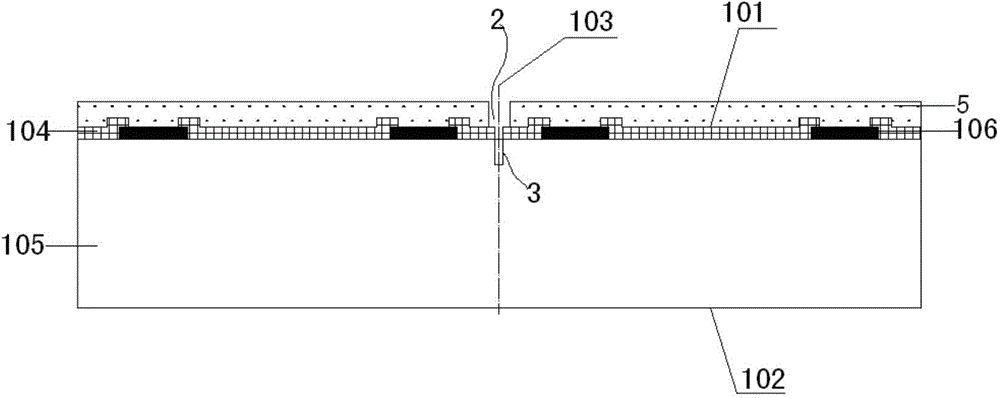

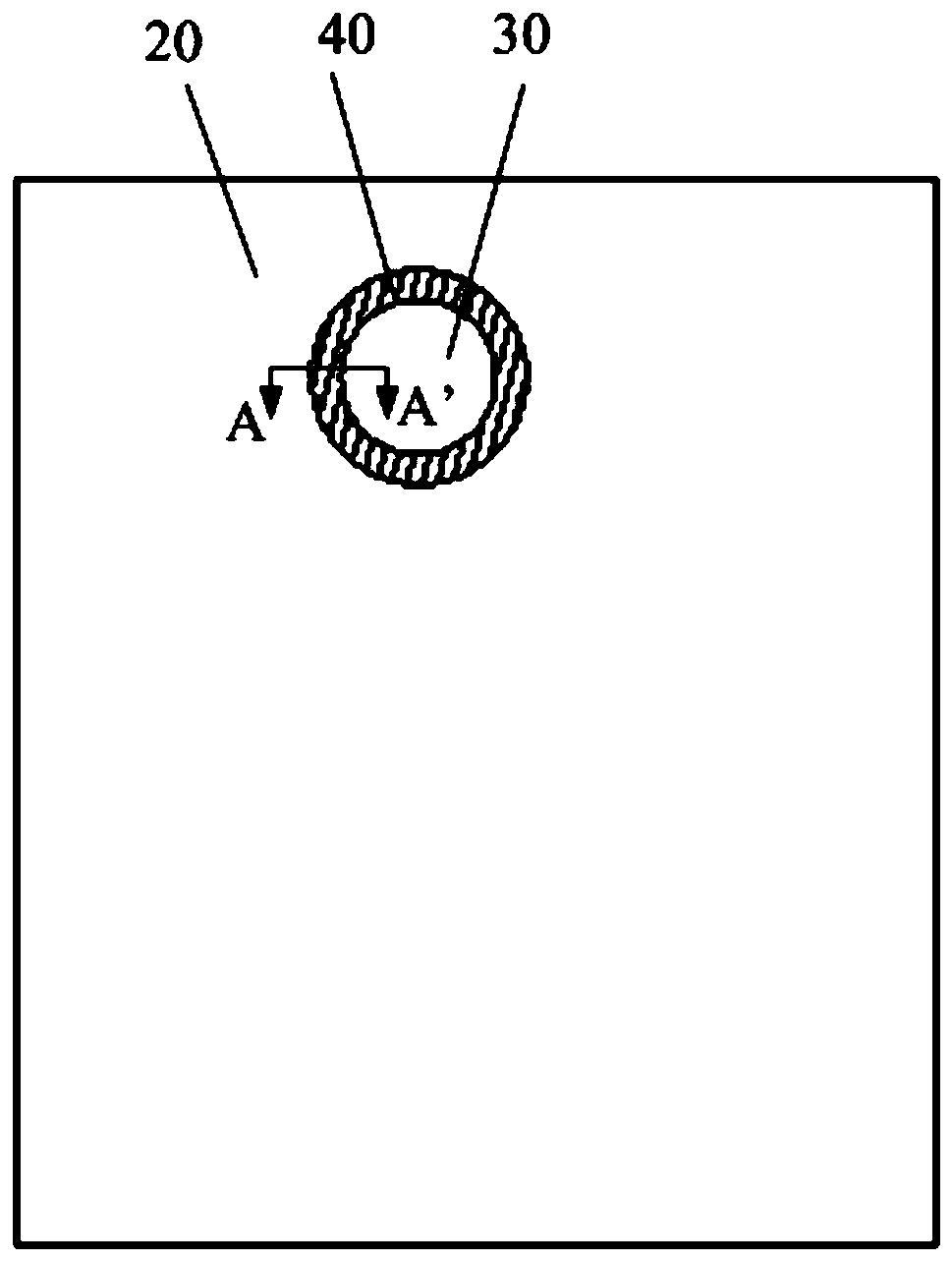

Display panel, manufacturing method thereof and display device

ActiveCN110518147AImprove packaging yieldProtective structureSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOxygen

The invention relates to a display panel, a manufacturing method thereof and a display device. The display panel comprises a substrate, an isolation column, a passivation layer and a display layer, wherein the substrate comprises an opening area, a transition area surrounding the opening area and a display area surrounding the transition area; the isolation column is arranged in the transition area, and the side wall of the isolation column is sunken inwards to form a sunken part; the passivation layer at least covers the isolation column and covers the isolation column in a conformal manner,and the passivation layer covers the sunken part; the display layer covers the transition area and the display area and comprises a light-emitting layer, and the light-emitting layer is discontinuously arranged in the sunken part of the isolation column. According to the display panel provided by the invention, the effectiveness of the isolation column for cutting off the water-oxygen invasion channel can be ensured, and the packaging yield of the display panel is improved.

Owner:BOE TECH GRP CO LTD +1

Embedded type TSV adapter plate structure for numerous-layer wiring

ActiveCN107393900AImprove packaging yieldCompact structureSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

The invention relates to an adapter plate structure, in particular to an embedded type TSV adapter plate structure for numerous-layer wiring, which belongs to the technical field of integrated circuit packaging. According to the technical scheme provided by the invention, the embedded type TSV adapter plate structure for numerous-layer wiring comprises an adapter plate body, wherein a wiring adapter plate groove is formed in the adapter plate body in a concave manner, a wiring adapter plate is arranged in the wiring adapter plate groove, numerous-layer wires are arranged on the wiring adapter plate, the wiring adapter plate is electrically connected with an adapter plate upper redistribution layer on the upper surface of the adapter plate body by means of the numerous-layer wires, the adapter plate upper redistribution layer is electrically connected with an adapter plate lower redistribution layer on the lower surface of the adapter plate body by means of filling connectors filled in through vias of the adapter plate body, a plurality of solder balls are arranged on the adapter plate lower redistribution layer, and the solder balls are electrically connected with the adapter plate lower redistribution layer. The embedded type TSV adapter plate structure can effectively increase the number of wiring layers, realizes the high-density chip scale packaging and system packaging, and is safe and reliable.

Owner:58TH RES INST OF CETC

Packaging method

ActiveCN102690044AImprove surface topographyIdeal for height non-uniformitySolid-state devicesSemiconductor/solid-state device manufacturingLaser scanningMaterials science

A packaging method comprises the following steps of: preparing a finely pulverized powder, preparing a finely pulverized powder paste by the use of the finely pulverized powder, coating a packaging wire of cover lens by with the finely pulverized powder paste and glass paste, presintering the coated cover lens in vacuum, folding the cover lens which is presented in vacuum with a glass substrate, and carrying out laser scanning and packaging on the folded combination of the cover lens and the glass substrate. By the adoption of the packaging method, height inhomogeneities of the presentered packaging wire can be controlled within an ideal range and requirements on laser power when packaging is obviously reduced.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

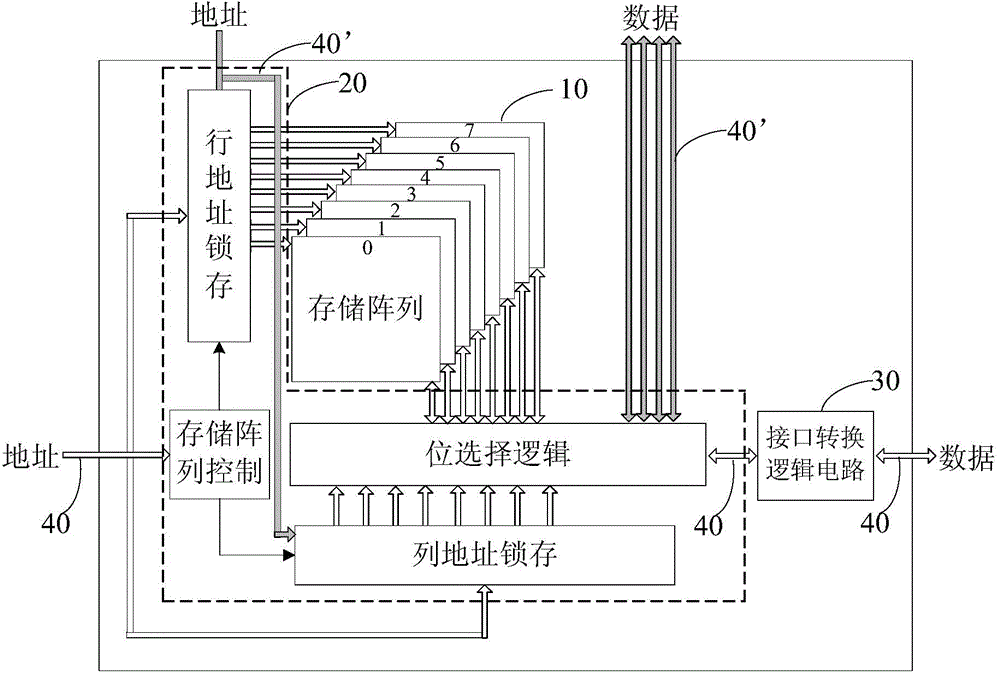

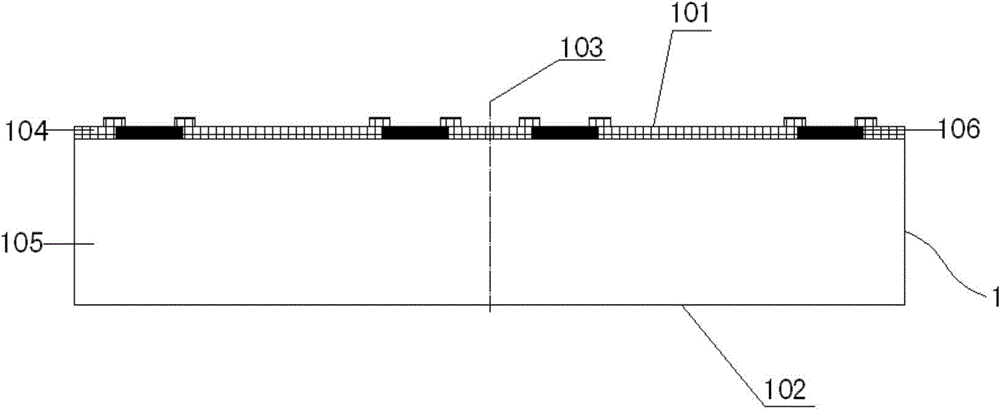

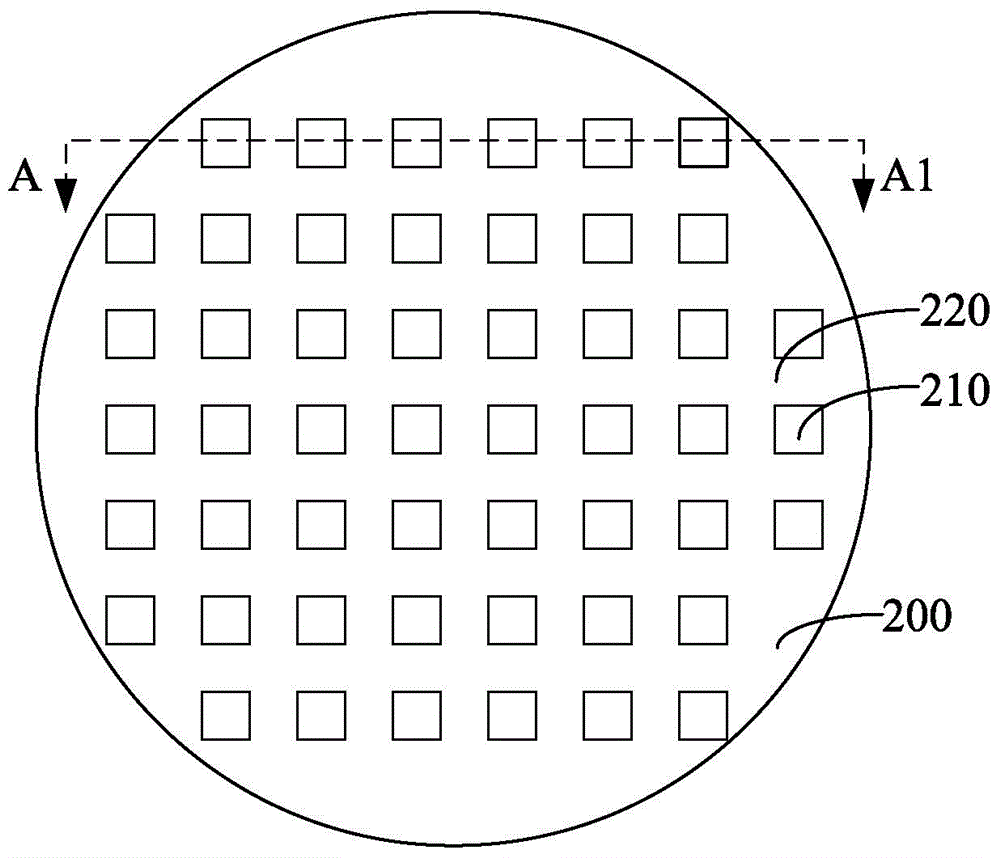

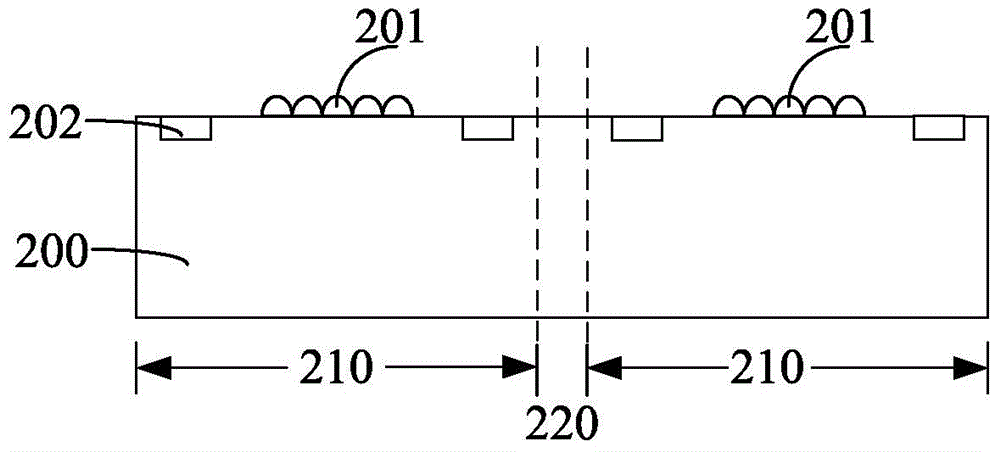

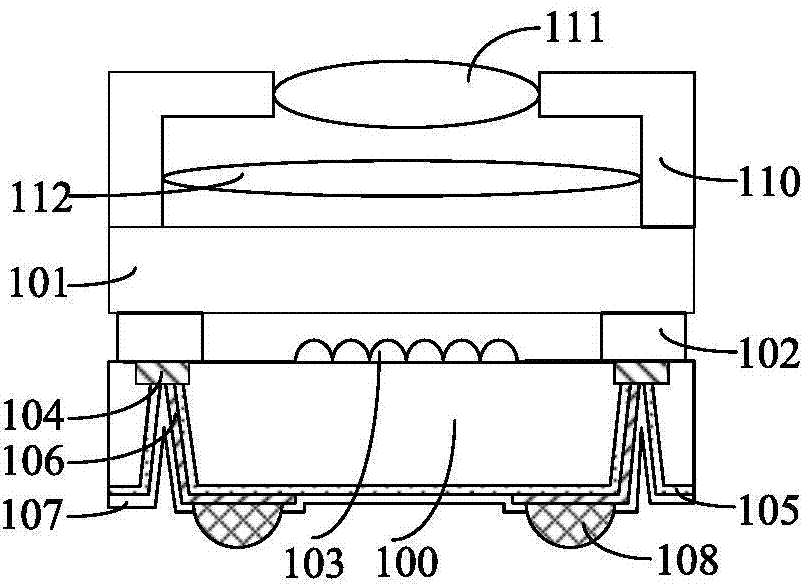

Wafer-level packaging method for semiconductor and semiconductor packaging part

ActiveCN103985648AImprove the application range of packagingReduce area wasteSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor packageWafer-level packaging

Provided are a wafer-level packaging method for a semiconductor and a semiconductor packaging part. The wafer-level packaging method for the semiconductor comprises the following steps that a first wafer with one or a plurality of storage chip units is provided, each storage chip unit is provided with a storage array circuit and a periphery circuit, and a first cut channel is arranged between the adjacent storage chip units; a second wafer provided with one or more logical chip units is provided, the area of each logical chip unit corresponds to the area of N storage chip units, wherein N is a natural number larger than or equal to 1, a second cut channel is arranged between the adjacent logical chip units, and the second cut channels are matched with the first cut channels on the peripheries of the N storage chip units; the first wafer and the second wafer are bonded, and the logical chip units are correspondingly matched with the N storage chip units. By means of the wafer-level packaging method, the packaging application range of the storage wafers is enlarged.

Owner:GALAXYCORE SHANGHAI

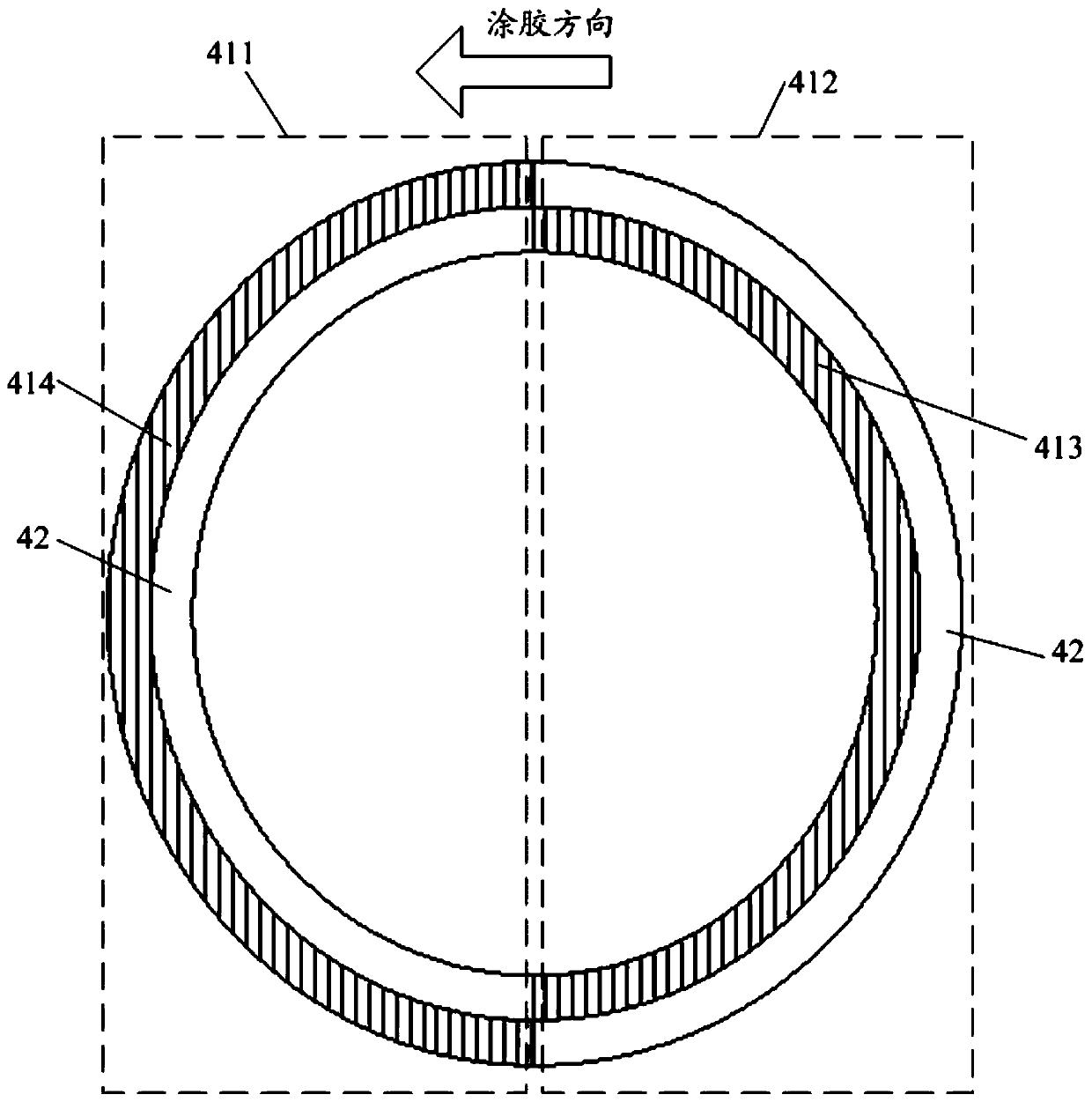

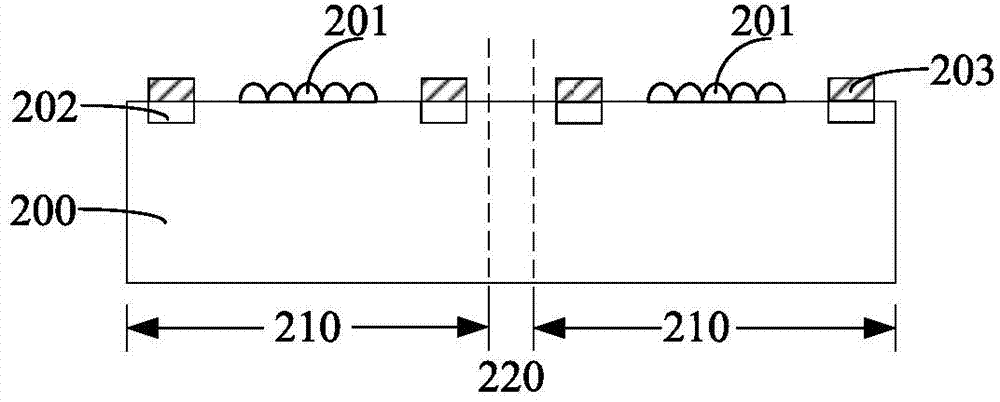

Ultra-narrow-pitch wafer level encapsulation cutting method

ActiveCN104637878ASimple processIncreased process windowSemiconductor/solid-state device manufacturingLaser cuttingEngineering

The invention discloses an ultra-narrow-pitch wafer level encapsulation cutting method. According to the method, a layer of photoresist is paved at the front side of a wafer, a first opening is formed through an exposure and development process, and a dielectric layer corresponding to a cutting path is exposed; then, a second opening is formed through an etching process or a laser cutting process, so that the second opening penetrates into a substrate at a certain depth; then, the grinding is carried out from the back surface, so that the stress is totally concentrated in a sharp corner position of the second opening formed through etching or cutting, and certain cracks are generated; if the extension resistance generated in the grinding process is great enough, the cracks can crack along a certain angle, and the wafer is further divided into single chips; if the extension resistance generated in the grinding process is not great enough, certain external force is exerted on a wafer, so that the cracks expand, and the water is further divided into the single chips. The ultra-narrow-pitch wafer level encapsulation cutting method has the advantages that the cutting of the wafer with the ultra-narrow cutting passage can be realized, in addition, the technological process is simple, and the process window is also correspondingly increased.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

Display panel, display device and manufacturing method of display panel

ActiveCN111244112AImprove packaging yieldGuaranteed validitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention discloses a display panel, a display device and a manufacturing method of the display panel. The display panel comprises a substrate, and the substrate comprises a display area, an opening area and an isolation area located between the display area and the opening area. The isolation area is internally provided with at least one isolation column, each isolation column is arranged around the hole area for a circle, and in the direction parallel to the substrate, each isolation column comprises a first part and a second part which are opposite and connected. The side face, facing the second part, of the first part and the side face, back on to the first part, of the second part are respectively provided with the grooves in a concave manner, and light-emitting layers are arranged in the display area and the isolation area and are disconnected at the grooves. Moreover, the light-emitting layer is of a continuous structure at the side, opposite to the second part, of the firstpart and the side, facing the first part, of the second part. According to the display panel provided by the invention, the packaging yield of the display panel can be effectively improved, and the effectiveness of the isolation column for cutting off a water-oxygen invasion channel is ensured.

Owner:BOE TECH GRP CO LTD +1

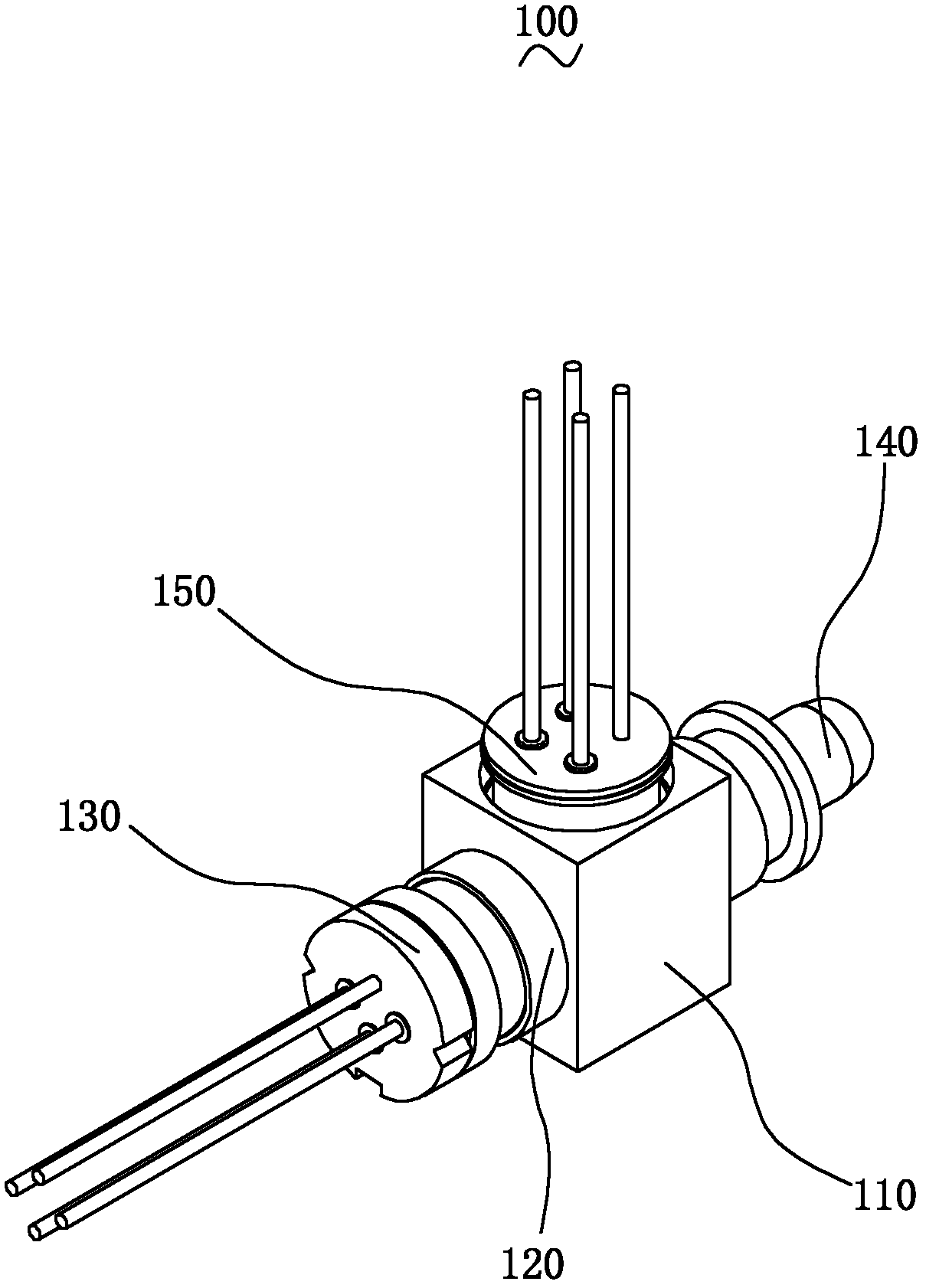

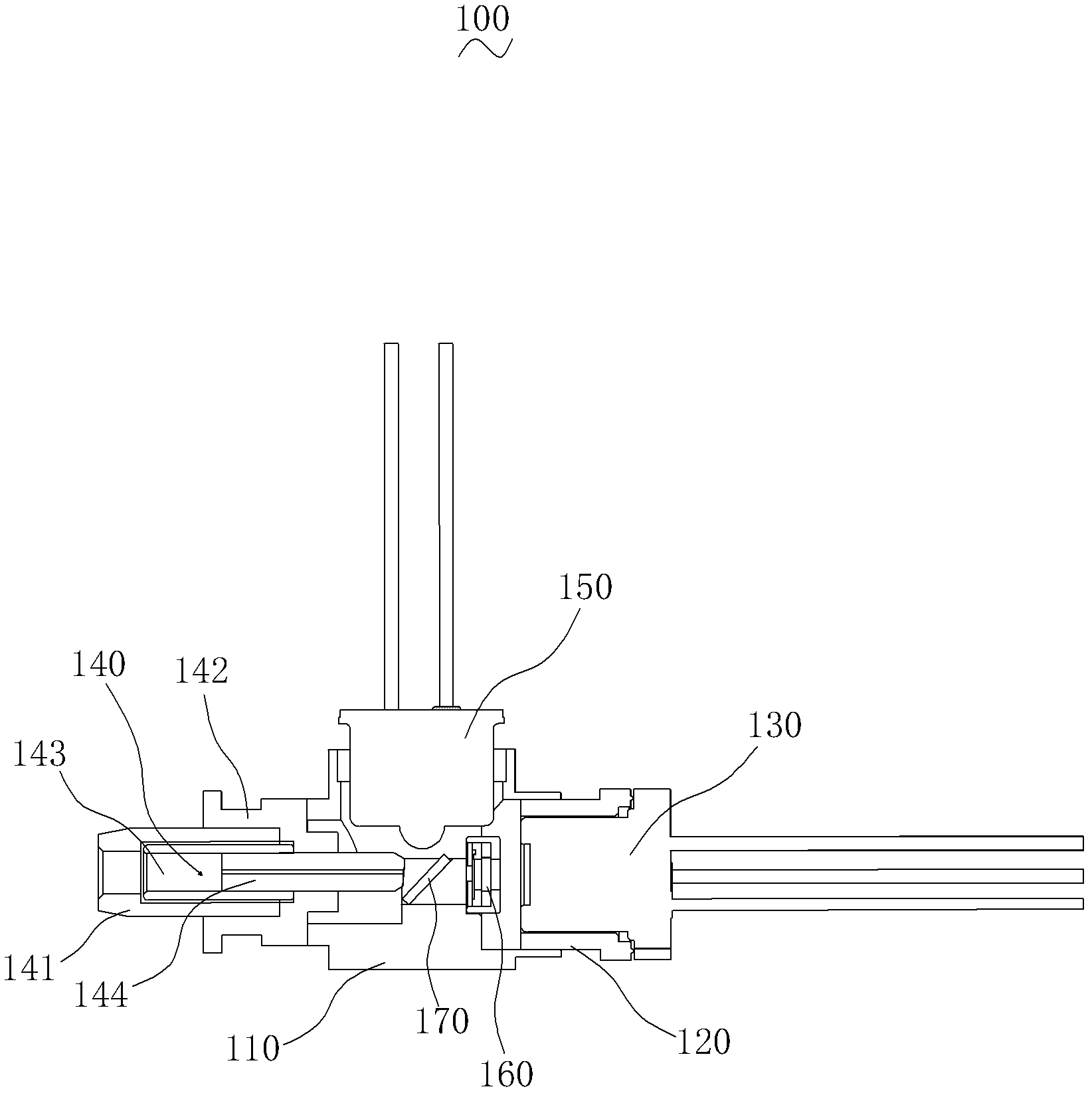

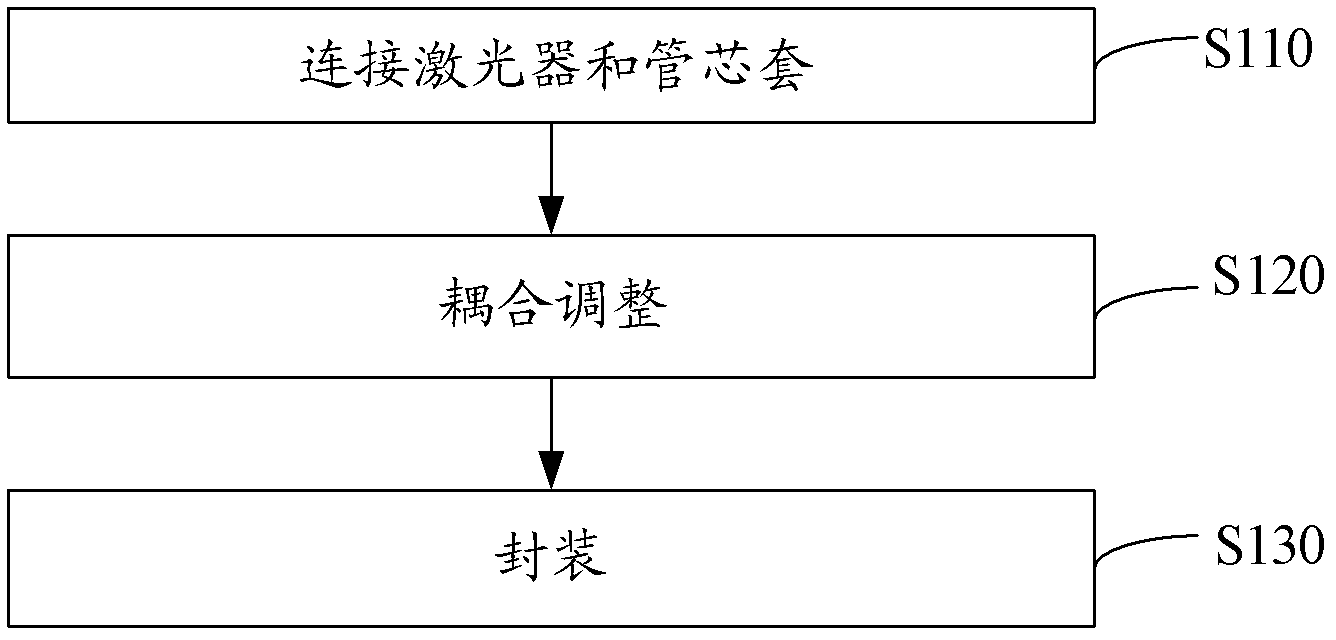

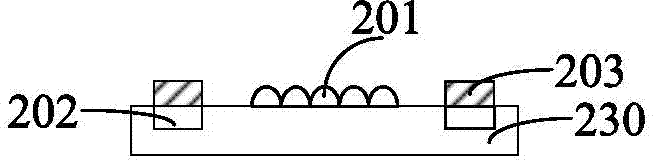

Single-fiber bidirectional component and packaging method thereof

InactiveCN102508343ACoupling does not affectImprove packaging yieldCoupling light guidesCouplingOptical power

A single-fiber bidirectional component comprises a substrate, a tube core sleeve, a receiver, an adapter, a laser device and an optical filter. The laser device is connected with the tube core sleeve, the optical filter is arranged in the substrate, a first connecting hole and a second connecting hole which are coaxial are arranged on the substrate, the tube core sleeve is inserted into the first connecting hole, the inner diameter of the first connecting hole is larger than the outer diameter of the tube core sleeve, and the adapter is inserted into the second connecting hole. Light emitted from the laser device is coupled by the optical filter and enters the adapter, and light entering the adapter is reflected by the optical filter and further enters the receiver. In a packaging process of the single-fiber bidirectional component, coupling adjustment is carried out at first so as to obtain proper optical power, and then packaging is carried out. During coupling adjustment, the laser device can be longitudinally adjusted while the adapter is transversely adjusted due to the fact that the inner diameter of the first connecting hole is larger than the outer diameter of the tube core sleeve, the adapter does not need to be longitudinally adjusted, coupling of a receiving end is unaffected, receiving coupling can be realized easily, and packaging yield is high.

Owner:SHENZHEN GIGALIGHT TECH

Packaging method and packaging structures

ActiveCN103985723AImprove packaging efficiencySave packaging timeRadiation controlled devicesBiomedical engineeringImage sensing

The invention discloses a packaging method and packaging structures. The packaging method includes the steps of providing a plurality of individual image sensing chips, wherein each image sensing chip is provided with an image sensing area and a bonding pad surrounding the image sensing area; providing a PCB substrate, wherein a metal layer is formed on the surface of the PCB substrate; reversedly arranging the image sensing chips on the PCB substrate, wherein the bonding pads are electrically connected with the metal layer; forming a plastic sealing layer which covers the surface of the metal layer and the surfaces of the image sensing chips; forming a through hole, exposed out of the surface of the metal layer, in the plastic sealing layer; forming a welding protrusion which fully fills the through hole, wherein the top of the welding protrusion is higher than the surface of the plastic sealing layer; cutting the PCB substrate along the area of cutting lines to form the multiple single packaging structures. The packaging process is simple, the packaging structures have good packaging performance and high reliability, the packaging process can be partly conducted through the PCB manufacturing technology, and packaging process difficulty and packaging cost are reduced.

Owner:CHINA WAFER LEVEL CSP

Packaging structure and packaging method of fingerprint recognition chip

ActiveCN107146779ALow costReduce thicknessSemiconductor/solid-state device detailsSolid-state devicesEngineeringSilicon

The invention provides a packaging structure and a packaging method of a fingerprint recognition chip. The packaging structure comprises a silicon substrate, a re-wiring layer formed on the silicon substrate, metal leading wires welded on the re-wiring layer through a wire-welding process, the fingerprint recognition chip arranged above the re-wiring layer through metal welding points, and a packaging material covering the fingerprint recognition chip, wherein the front surface of the fingerprint recognition chip is arranged towards the re-wiring layer, and the metal leading wires are exposed out of the packaging material. According to the packaging structure and the packaging method, the fingerprint recognition chip is packaged in a fan-out manner, compared with conventional packaging of other fingerprint recognition chips, the cost is low, the thickness is small, and the yield is high; and by employing the wire-welding process, the process temperature can be greatly reduced, and the application range of the process is extended.

Owner:SJ SEMICON JIANGYIN CORP

Image sensor module and formation method thereof

ActiveCN103943645AThe overall thickness is thinMeet different needsSemiconductor/solid-state device manufacturingRadiation controlled devicesOptoelectronicsImage sensing

The invention provides an image sensor module and a formation method thereof, wherein the image sensor module comprises a substrate which is provided with a frontage and a back opposite to the frontage, a buffer layer located on the frontage of the substrate and a metal layer located on the surface of the buffer layer, a die inverted above the substrate, a welding projection located on the surface of the metal layer, and a formed lens assembly, wherein the die is provided with an image sensing region and a bonding pad surrounding the image sensing region, and the bonding pad is electrically connected with the metal layer; the lens assembly comprises a mirror base and a lens, and the lens is connected with the back of the substrate by virtue of the mirror base. The performance and the reliability of the image sensor module are improved.

Owner:苏州晶方光电科技有限公司

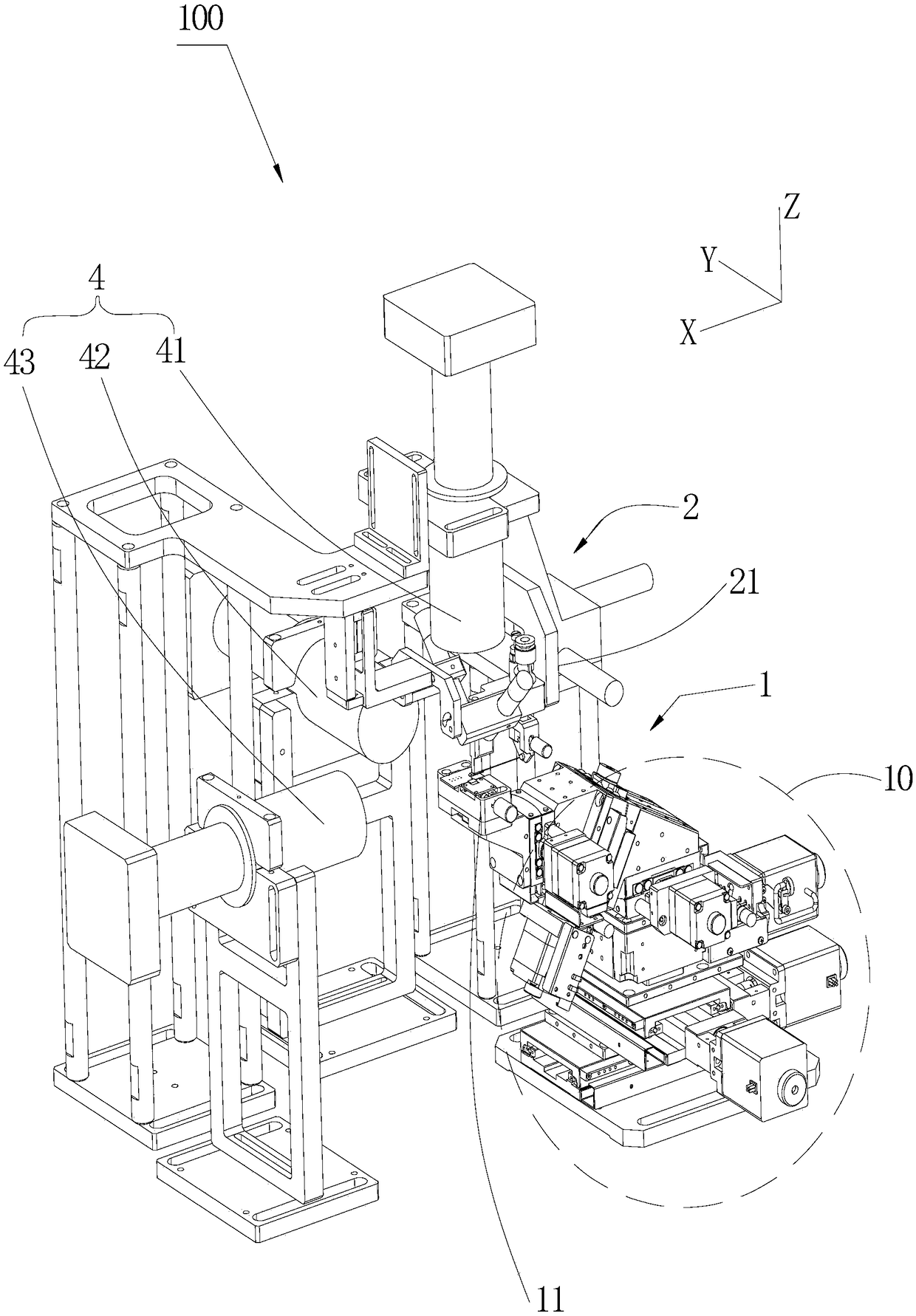

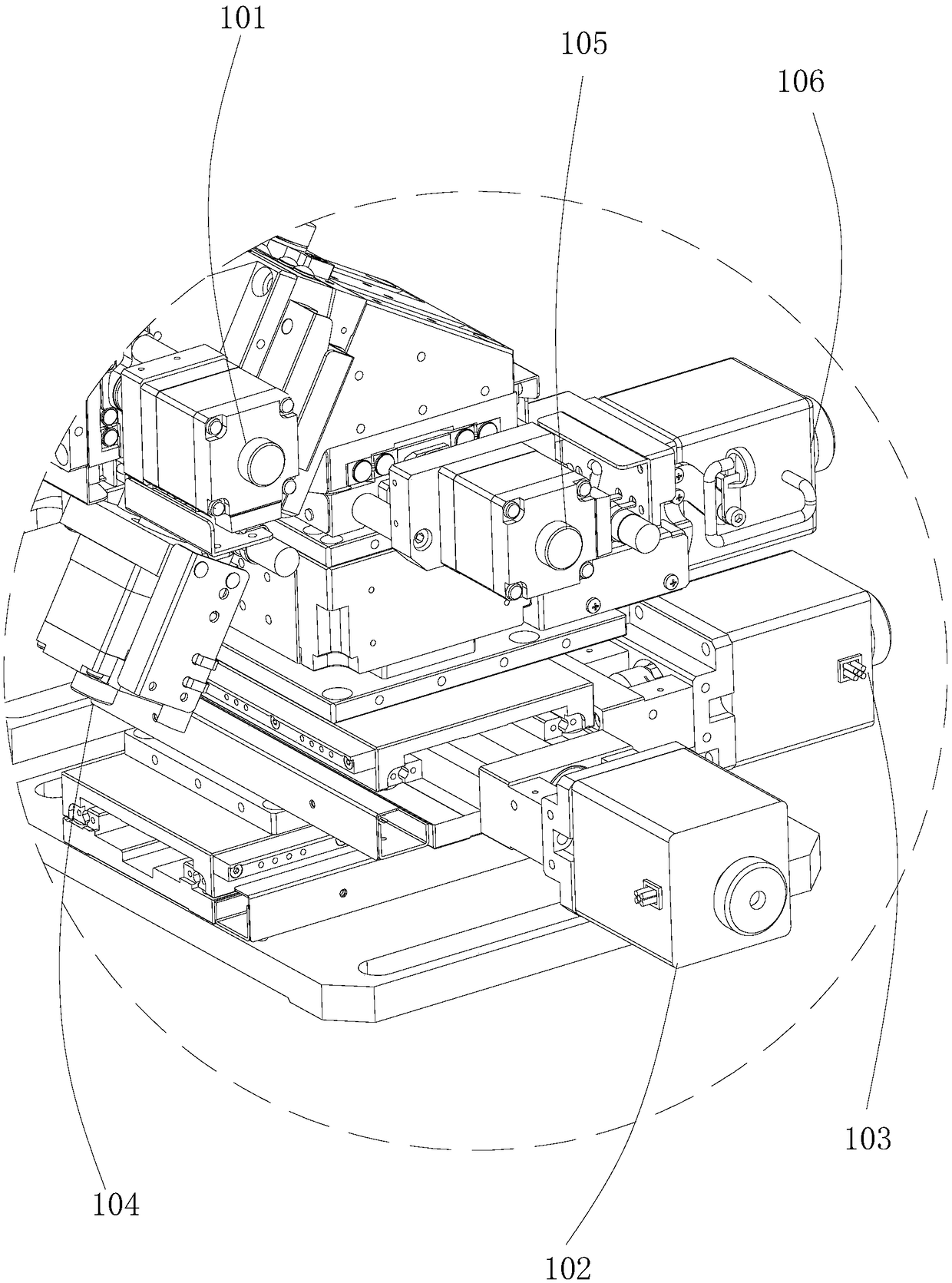

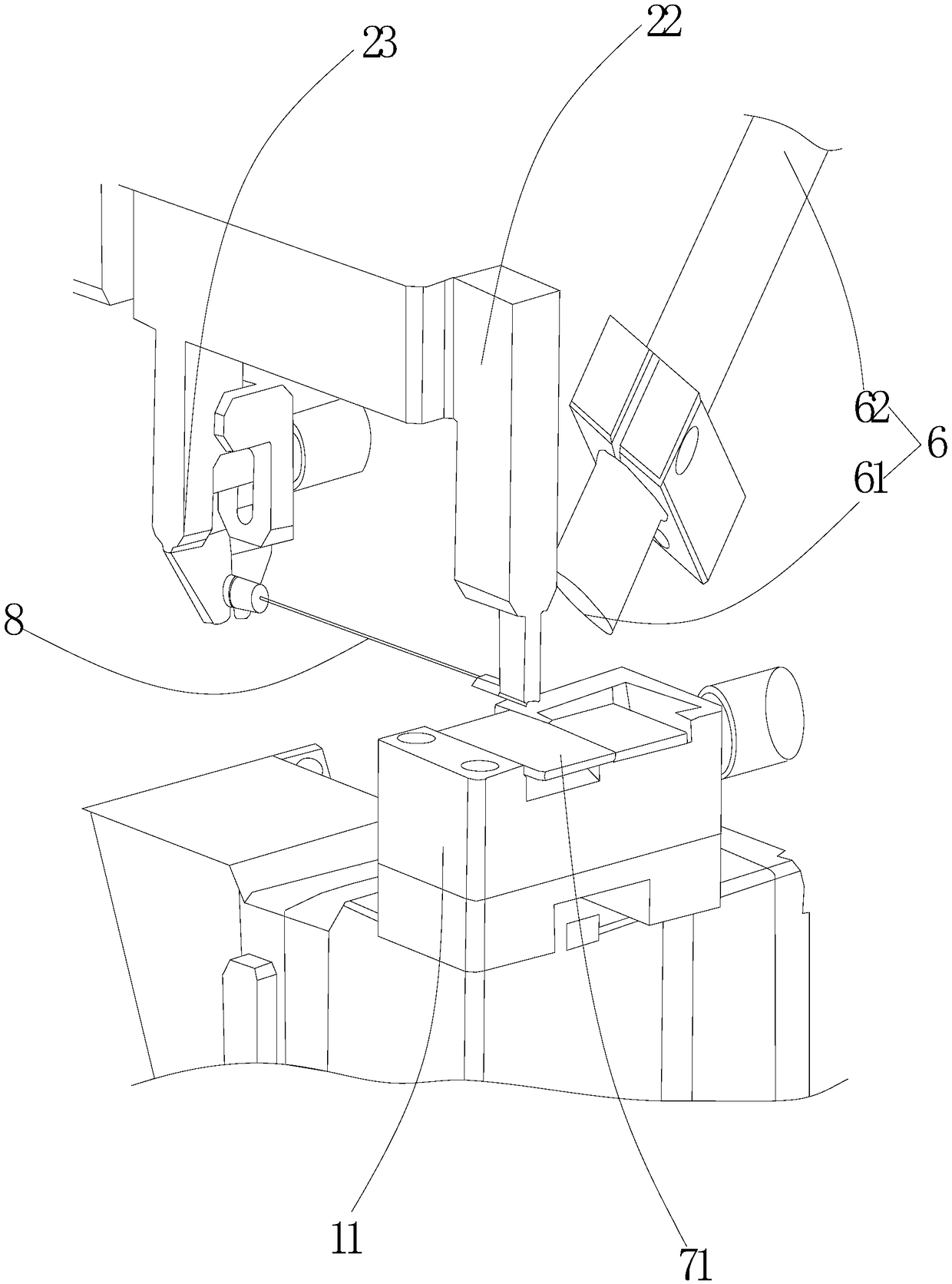

Coupled system of optical device and coupled method of optical device

PendingCN108873200AImprove coupling efficiencyAvoid collisionCoupling light guidesGratingCoupling system

The present invention is suitable for the technical field of optical device package, and provides a coupled system of an optical device and a coupled method of an optical device. The system comprisesa six-axis coupled device, a three-dimensional mobile device, a current detection device and a camera monitoring device. The six-axis coupled device is configured to drive a PD array to move and perform coupling of an arrayed waveguide grating, and the camera monitoring device is configured to perform monitoring of a relative position and a relative distance between the PD array and the arrayed waveguide grating in the coupled process. The coupled system of the optical device and the coupled method of the optical device are provided with the camera monitoring device to perform shooting and monitoring of the relative position and the relative distance between the PD array and the arrayed waveguide grating to avoid the problem that the PD array and the arrayed waveguide grating are collideddue to manual determination faults when a distance between the PD array and the arrayed waveguide grating is too small and prevent the PD array and the arrayed waveguide grating from being extruded and damaged compared to a mode of eye observation of operators so as to improve the coupled efficiency between the PD array and the arrayed waveguide grating on this basis and improve the package yield.

Owner:APAT OPTOELECTRONICS COMPONENTS

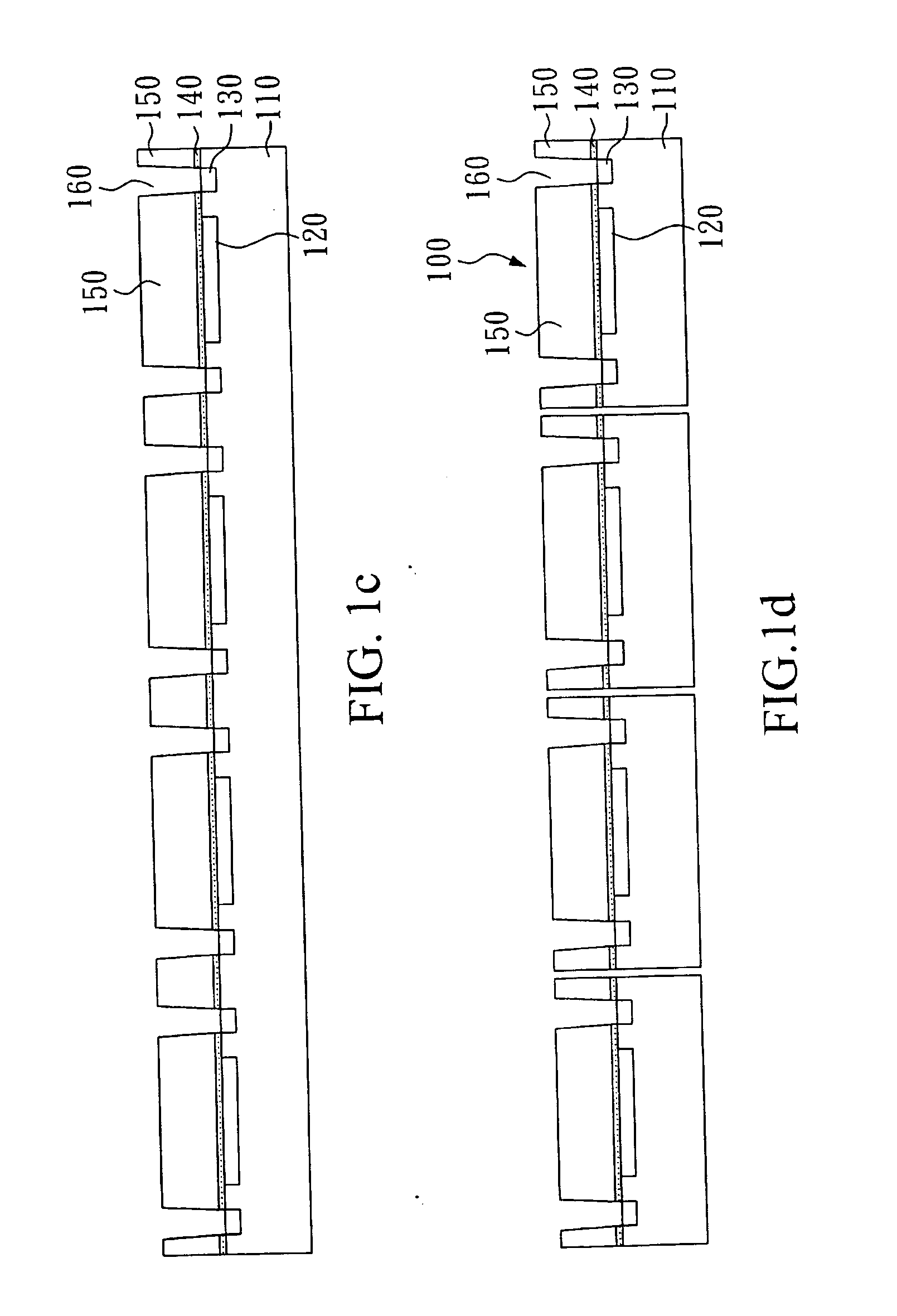

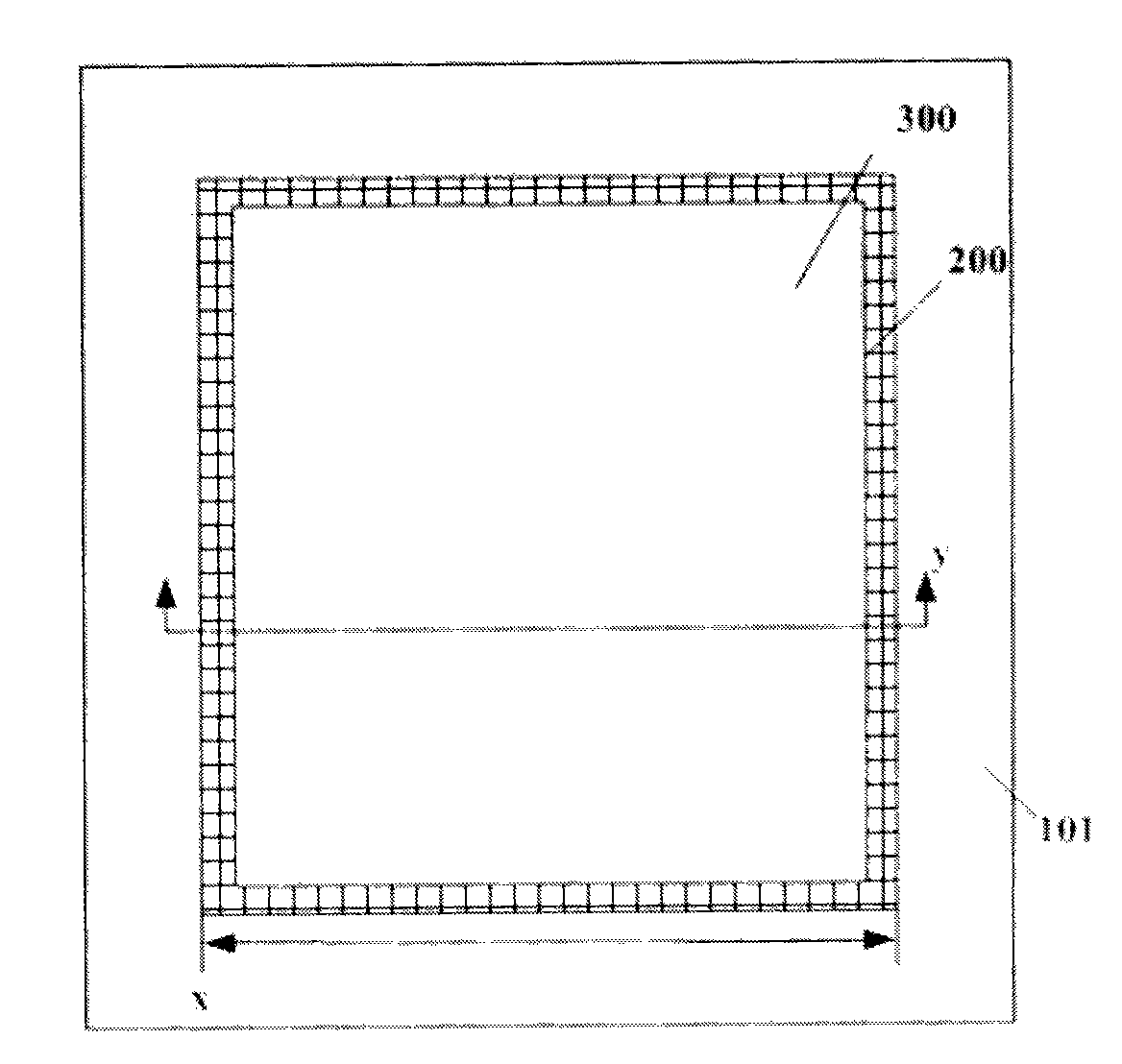

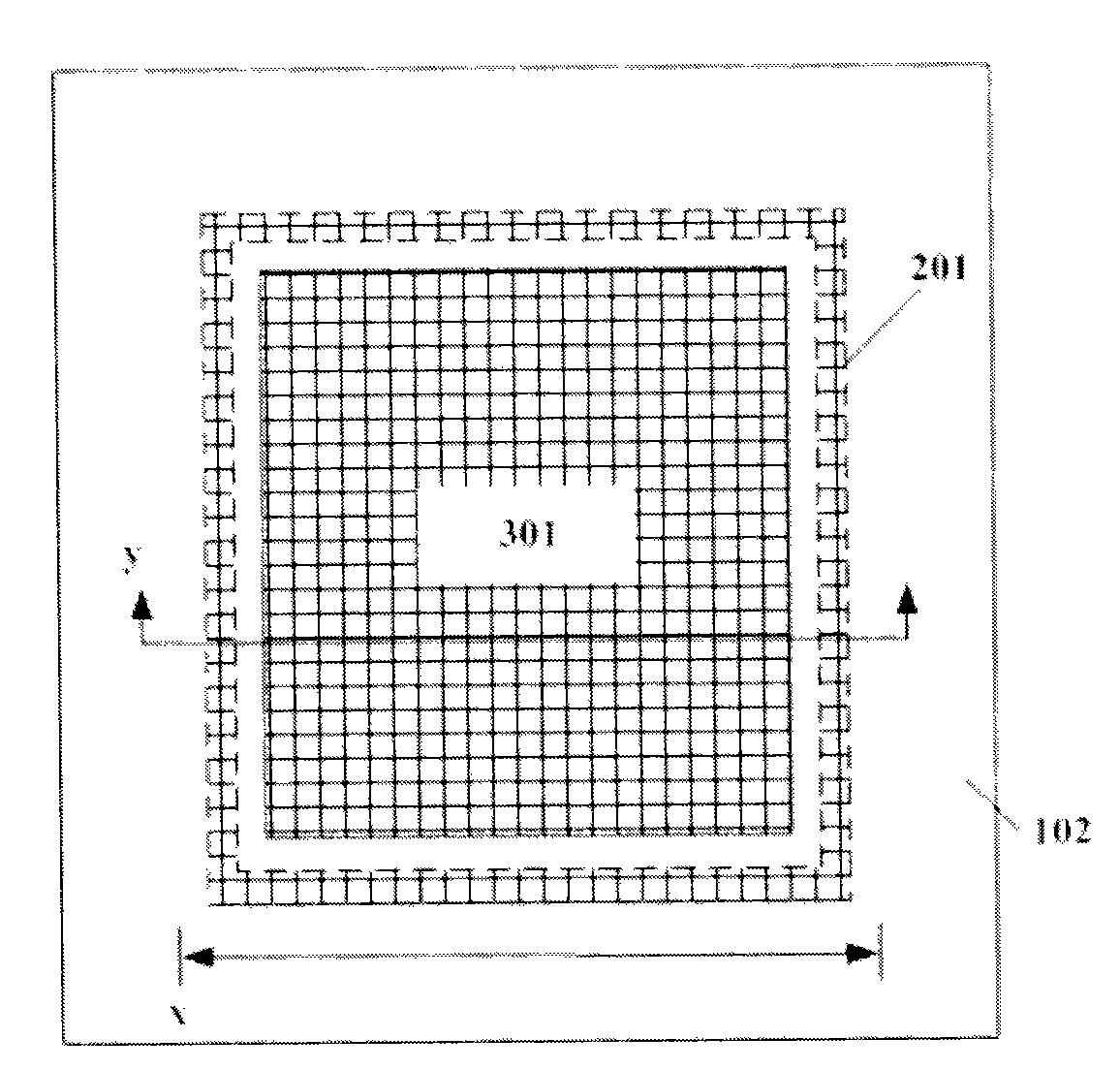

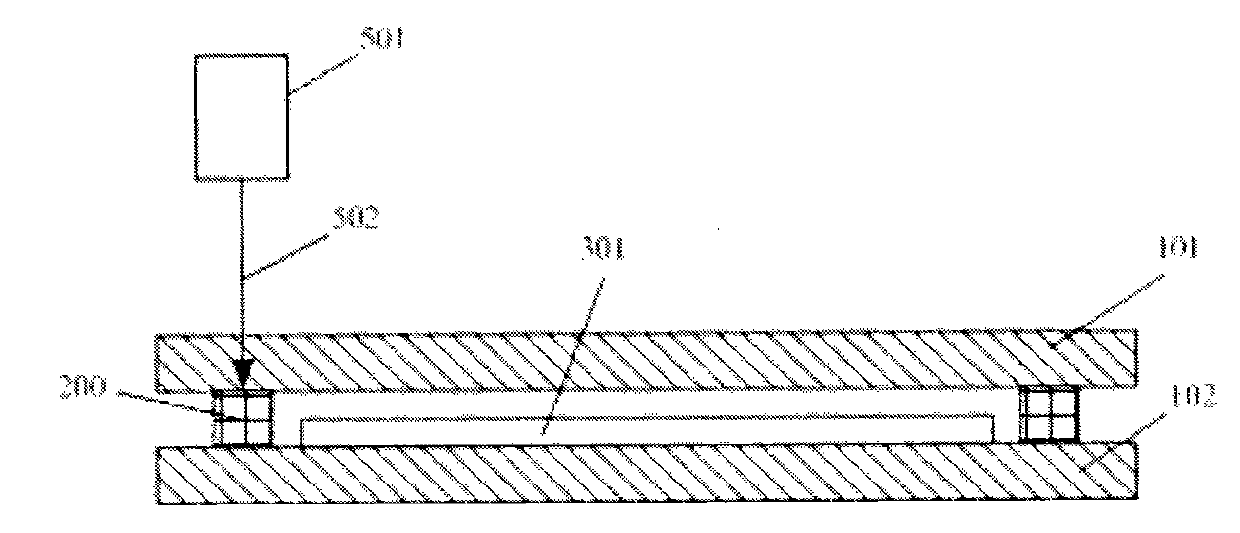

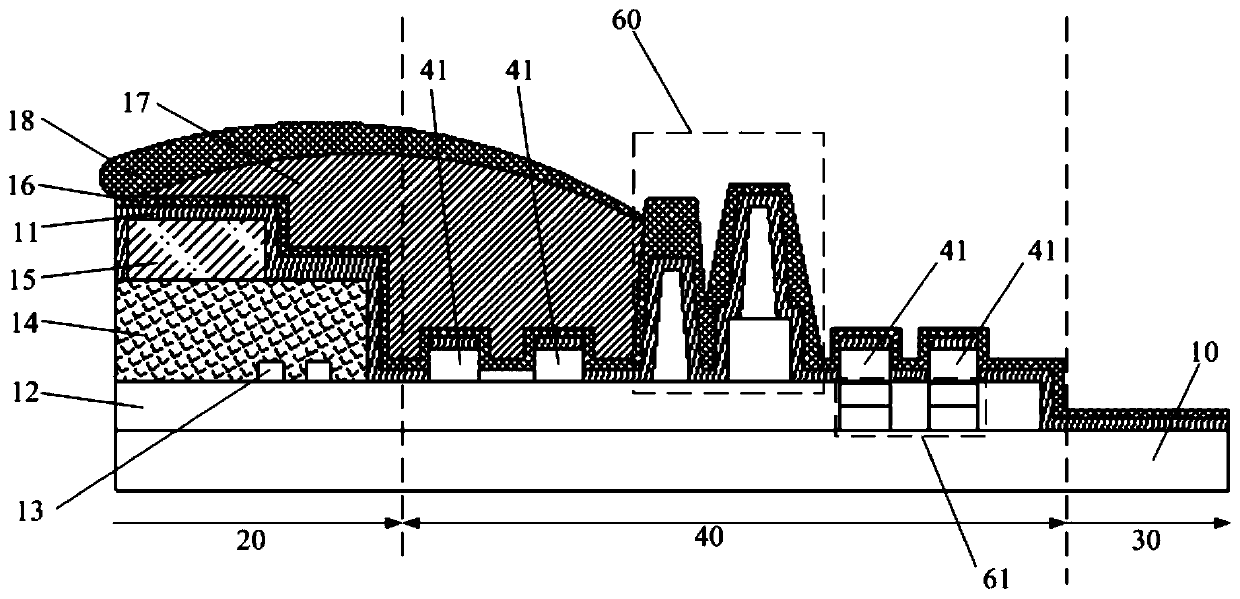

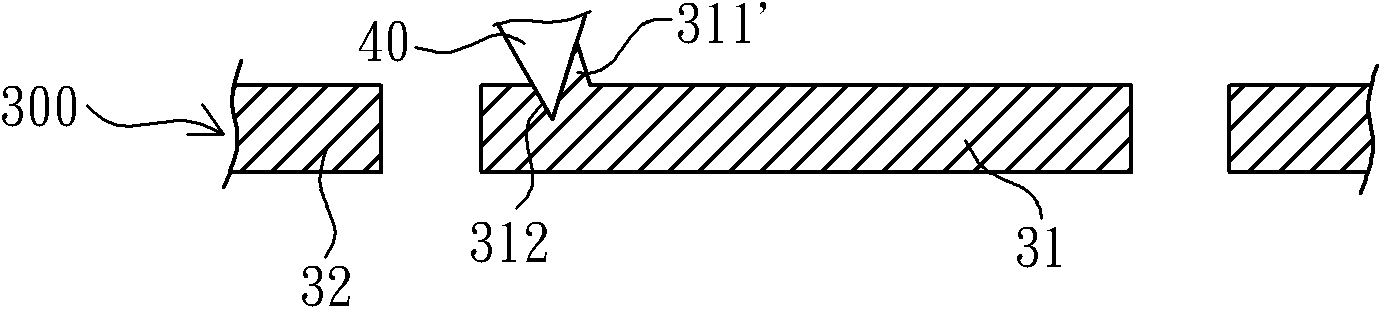

Method and structure for prevention leakage of substrate strip

InactiveUS7091583B2Improve package yieldSimple formatSemiconductor/solid-state device detailsPrinted circuit aspectsSolder maskSurface layer

The present invention provides a structure and a method for prevention leakage of a substrate strip. The substrate strip includes an edge portion and a plurality of units. A patterned metal layer on a surface of the substrate strip includes at least one plating bus extended to the edge portion, a plurality of plating lines at the units, a plurality of contact pads at the units and a plurality of fiducial marks at the edge portion. The plating bus has an extended trail having one end exposed out of the sidewall of the substrate strip. The fiducial marks and the contact pads are exposed out of a plurality of first openings of a solder mask. The solder mask also has a second opening at the edge portion exposing a portion of the plating bus to define a breaking hole. After forming a surface layer on the fiducial marks and the contact pads, the exposed portion of the plating bus is void of the surface layer. By removing the exposed portion of the plating bus, the breaking hole is formed to electrically isolate the extended trail from the contact pads in order to prevent a chip on the substrate strip from being damaged by ESD (Electrostatic Discharge) during packaging processes.

Owner:ADVANCED SEMICON ENG INC

Wafer level package method

InactiveCN102194985AImprove packaging yieldSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorEngineering

The invention discloses a wafer level package method. A semiconductor component and an encapsulation substrate are combined tightly by using a secondary encapsulation manufacture procedure, so gaps between the wafer and the encapsulation substrate can be reduced, and the combining degree between the wafer and the encapsulation substrate can be improved.

Owner:ZHANJING TECH SHENZHEN +1

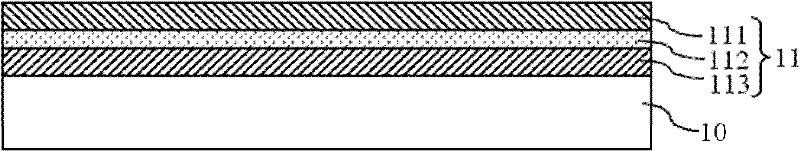

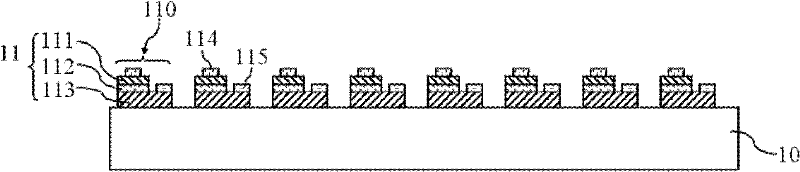

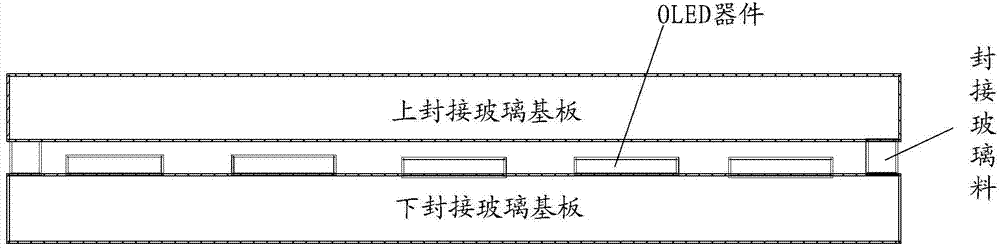

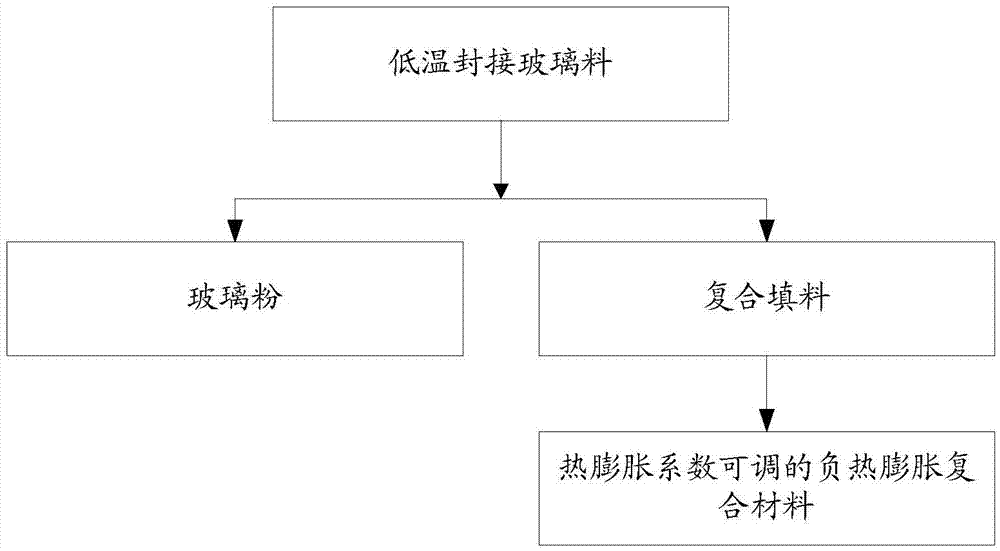

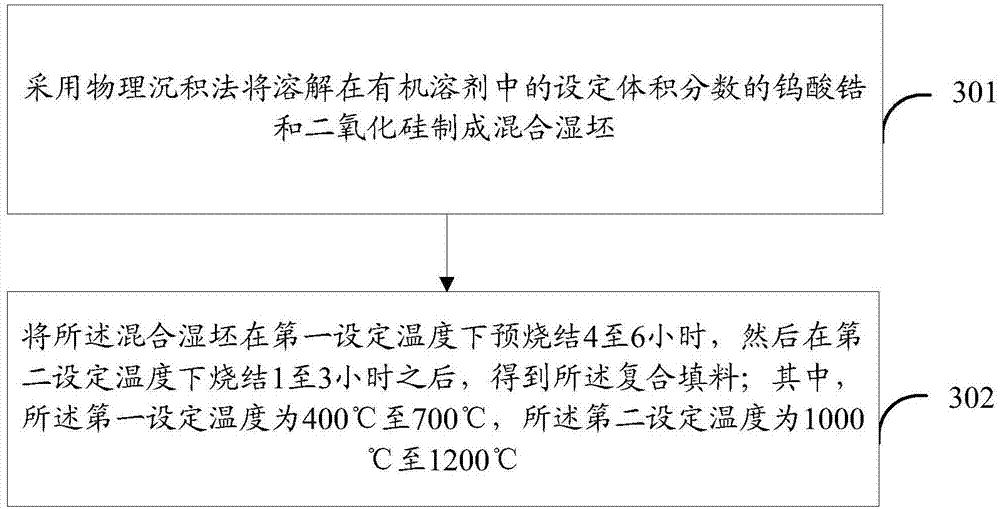

Low-temperature seal glass material and preparation method of composite filler

The invention discloses a low-temperature seal glass material and a preparation method of a composite filler in the glass material. The low-temperature seal glass material comprises glass powder and filler, wherein the filler at least comprises composite filler which is a negative thermal expansion composite material with adjustable coefficient of thermal expansion. The coefficient of thermal expansion of the low-temperature seal glass material mixed by the composite filler and the glass powder can be adjusted, so that the coefficient of thermal expansion of the low-temperature seal glass material can be matched with that of an OLED apparatus packaging glass substrate, thereby improving the packaging yield of OLED apparatuses. The problem in the prior art that the seal glass substrate and the seal glass material sealed are distorted and cracked or the OLED seal glass substrate has cracks when the packaged OLED apparatus is under high-light exposure as the difference of coefficient of thermal expansion of the seal glass material and that of the seal glass substrate is great is solved.

Owner:SHANGHAI TIANMA AM OLED +1

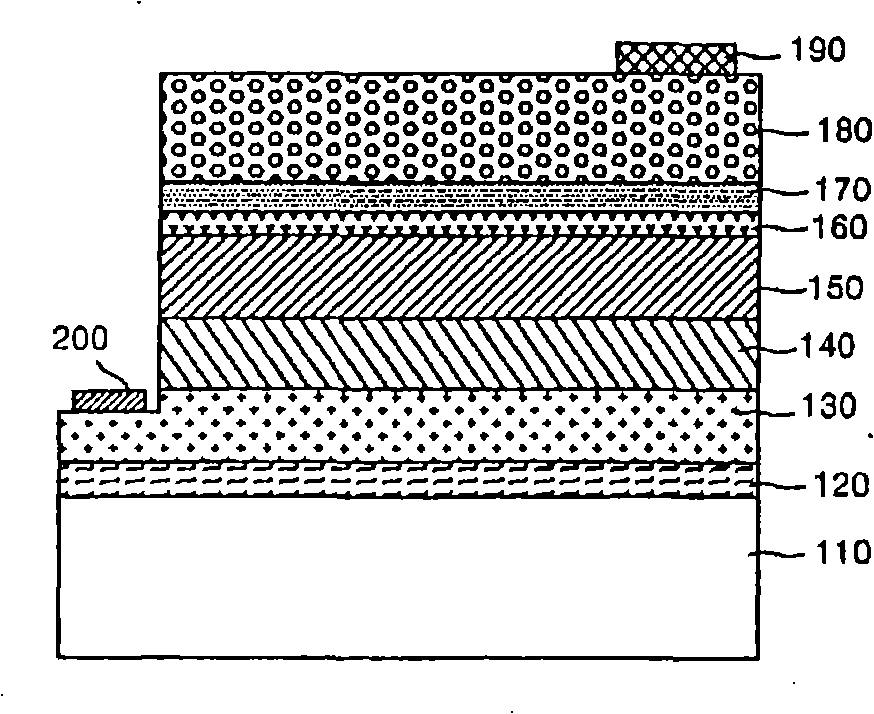

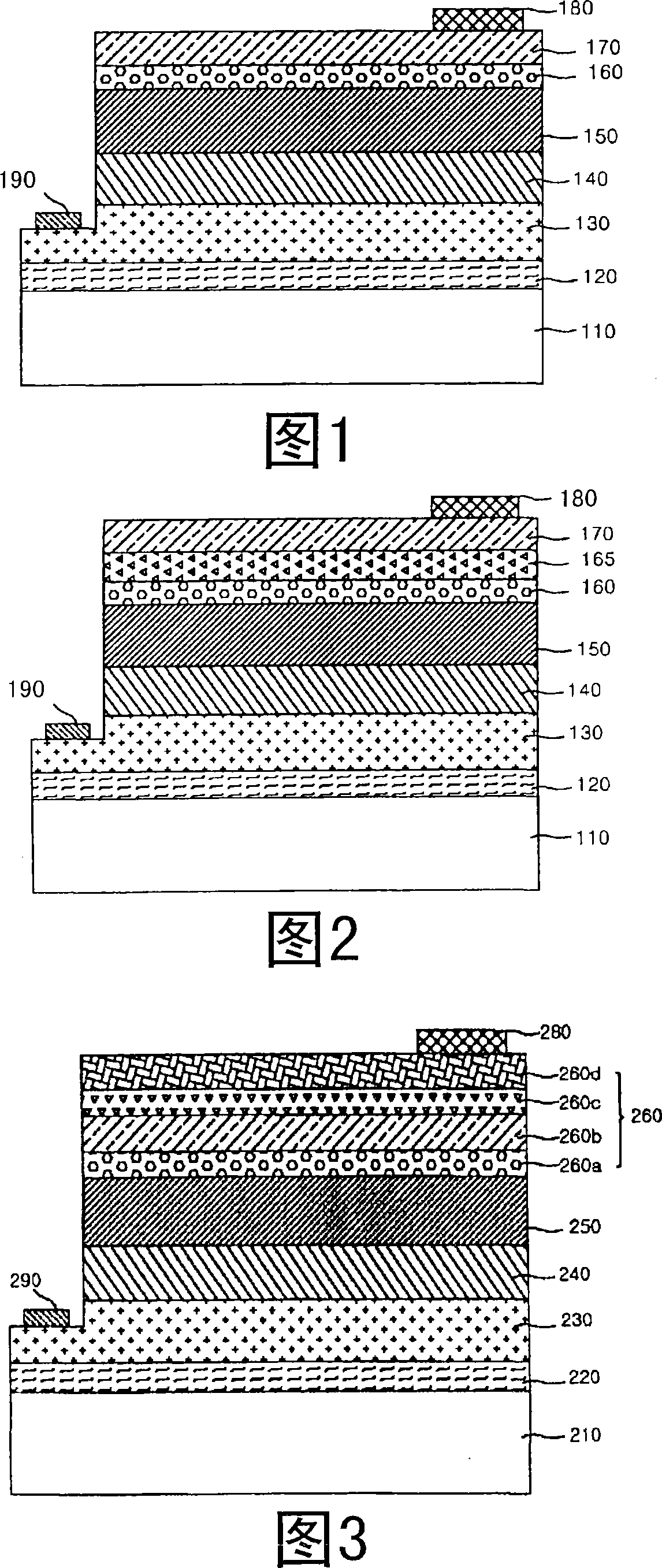

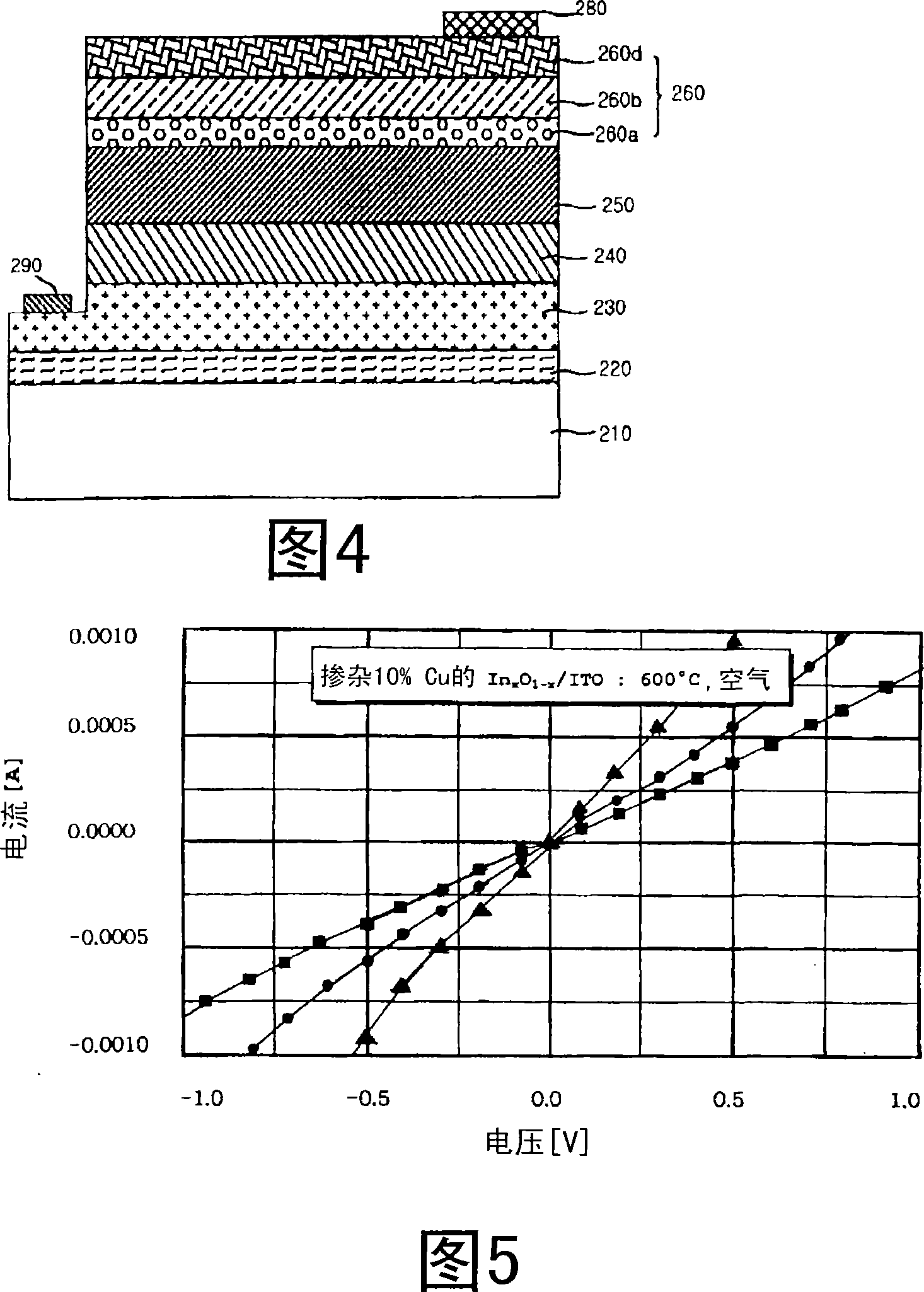

Flip-chip light emitting diodes and method of manufacturing thereof

ActiveCN101278409AImproved ohmic contact characteristicsImprove packaging yieldSemiconductor devicesOhmic contactWire bonding

Provided are a flip-chip nitride-based light emitting device having an n-type clad layer, an active layer and a p-type clad layer sequentially stacked thereon, comprising a reflective layer formed on the p-type clad layer and at least one transparent conductive thin film layer made up of transparent conductive materials capable of inhibiting diffusion of materials constituting the reflective layer, interposed between the p-type clad layer and reflective layer; and a process for preparing the same. In accordance with the flip-chip nitride-based light emitting device of the present invention and a process for preparing the same, there are provided advantages such as improved ohmic contact properties with the p-type clad layer, leading to increased wire bonding efficiency and yield upon packaging the light emitting device, capability to improve luminous efficiency and life span of the device due to low specific contact resistance and excellent current-voltage properties.

Owner:SAMSUNG ELECTRONICS CO LTD

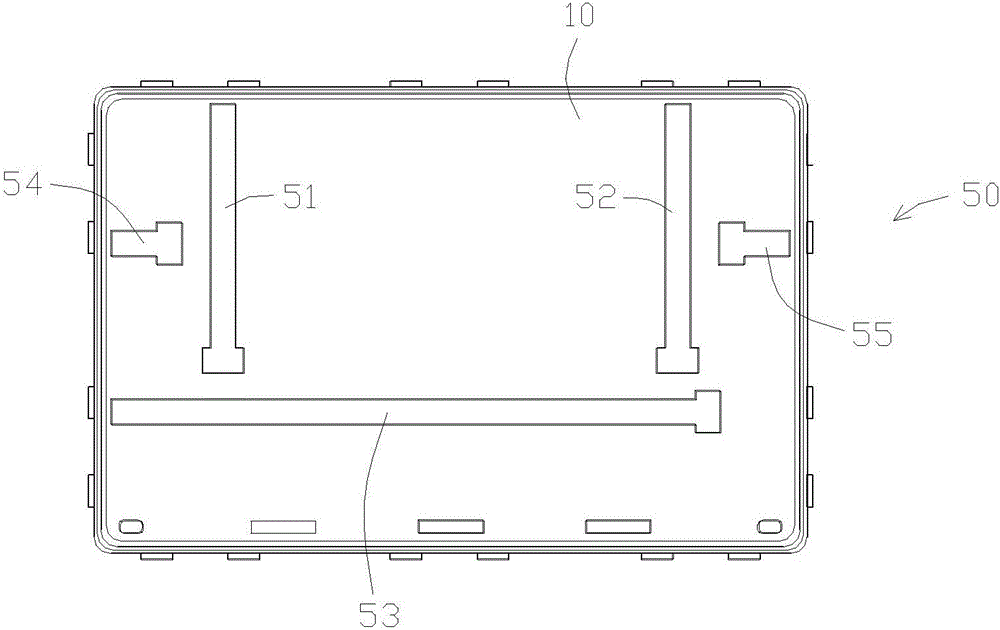

Polaroid packaging and fixing device

InactiveCN105691812AImprove work efficiencyLow costRigid containersDamagable goods packagingVacuum pumpingCarton

The invention provides a polaroid packaging and fixing device. The polaroid packaging and fixing device comprises a base and an upper cover used for covering the base. Pluggable fixed blocking pillars used for being connected with the upper cover are arranged at the four corners of the base. Sliding baffles used for fixing a polaroid and fixed baffles used for fixing the polaroid are arranged in the base. By means of the polaroid packaging and fixing device, the links of cleaning end faces, putting the polaroid into an aluminum foil bag for vacuum pumping, then putting the polaroid into a tray, putting the tray into a carton and the like are removed, the polaroid packaging working efficiency is improved, and the packaging yield can also be increased; and meanwhile the device can be directly put on a machine table to be subjected to wire feeding for use at a client end, the trouble of demounting the carton, demounting the aluminum foil bag and the tray by putting the carton, the demounting aluminum foil bag and the tray on the machine table pack by pack is saved, the wire feeding working efficiency of the client end is improved, the packaging cost is reduced, and the packaging yield is increased.

Owner:HANBO HIGH TECH MATERIALS HEFEI CO LTD

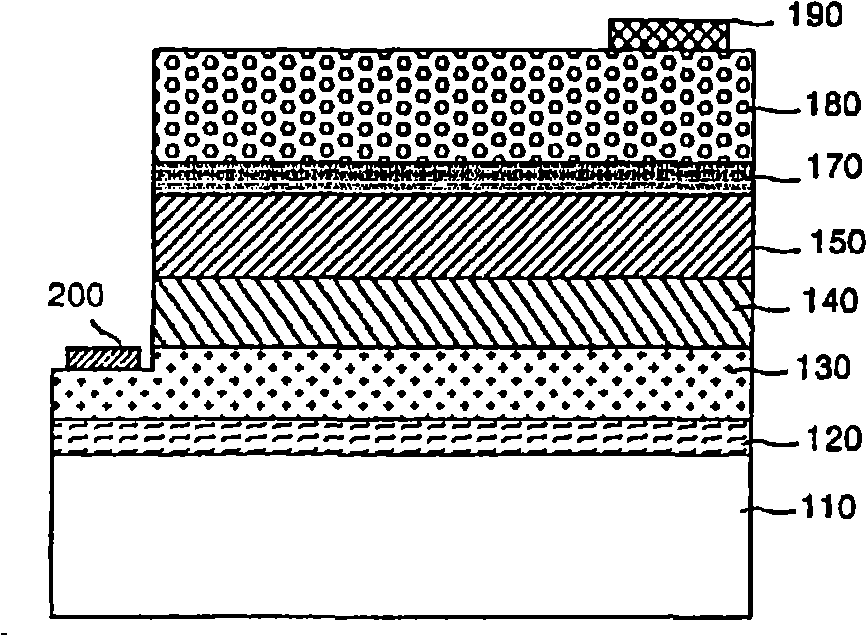

Top-emitting light emitting diodes and method of manufacturing thereof

InactiveCN101027790AImprove packaging yieldImproved ohmic contact characteristicsSemiconductor devicesOhmic contactConductive materials

Provided are a top-emitting nitride-based light emitting device having an n-type clad layer, an active layer and a p-type clad layer sequentially stacked thereon, comprising an interface modification layer formed on the p-type clad layer and a transparent conductive thin film layer made up of a transparent conductive material formed on the interface modification layer; and a process for preparing the same. In accordance with the top-emitting nitride-based light emitting device of the present invention and a process for preparing the same, there are provided advantages such as improved ohmic contact with the p-type clad layer, leading to increased wire bonding efficiency and yield upon packaging the light emitting device, capability to improve luminous efficiency and life span of the device due to low specific contact resistance and excellent current- voltage properties.

Owner:GWANGJU INST OF SCI & TECH

LED chip

The invention relates to an LED chip. The LED chip adopts the structure that an N-type electrode (22) adopts a staircase structure; the lower end of the N-type electrode (22) penetrates an insulating dielectric film (13) to be connected with an N-type layer (3); the middle part of the N-type electrode (22) is attached to the insulating dielectric film (13) at a vertical part; the upper end of the N-type electrode (22) is positioned above the insulating dielectric film (13) at the top, and extends towards the position of a P-type electrode (21); and the upper end of the N-type electrode (22) is connected with a second PCB board (23), and the N-type electrode (22) at the upper end and the P-type electrode (21) are provided with common soldering surfaces of which heights are equal or approximately equal. As the N-type electrode and the P-type electrode of the flip LED chip are provided with the common soldering surfaces of which heights are equal or approximately equal, the yield of packaging in the inverted-chip process of the LED chip is increased, and the phenomenon of inveracious soldering or desoldering of the electrode is avoided.

Owner:启东市天汾电动工具技术创新中心

Manufacturing method of LED (light-emitting diode) chip with inverted structure

The invention relates to a manufacturing method of an LED (light-emitting diode) chip with an inverted structure. The LED chip comprises an N-type electrode formation region and a P-type electrode formation region, wherein the N-type electrode formation region comprises a substrate, a buffer layer, an N-type layer, an N-type respective limiting layer, an active region layer, a P-type respective limiting layer, a P-type layer, a P-type ohmic contact layer, a light reflecting layer and an insulating film; one end face of an N-type electrode passes through the insulating film so as to be connected with the light reflecting layer, and the other end face of the N-type electrode is connected with a heating panel through a PCB (printed circuit board); the P-type electrode formation region comprise a substrate, a buffer layer, an N-type layer and the insulating film, one end of a P-type electrode passes through the insulating film so as to be connected with the N-type layer, and the other end of the P-type electrode is connected with the heating panel by virtue of the PCB; and the two end faces, respectively connected with the PCB, of the N-type electrode and the P-type electrode are positioned at a same horizontal plane. The manufacturing method provided by the invention has the advantages that the N-type electrode and P-type electrode of the LED chip are manufactured in the same surface, the package yield of a chip inversion process is increased, thereby avoiding the occurrence of the electrode rosin joint or sealed-off state.

Owner:祝进田

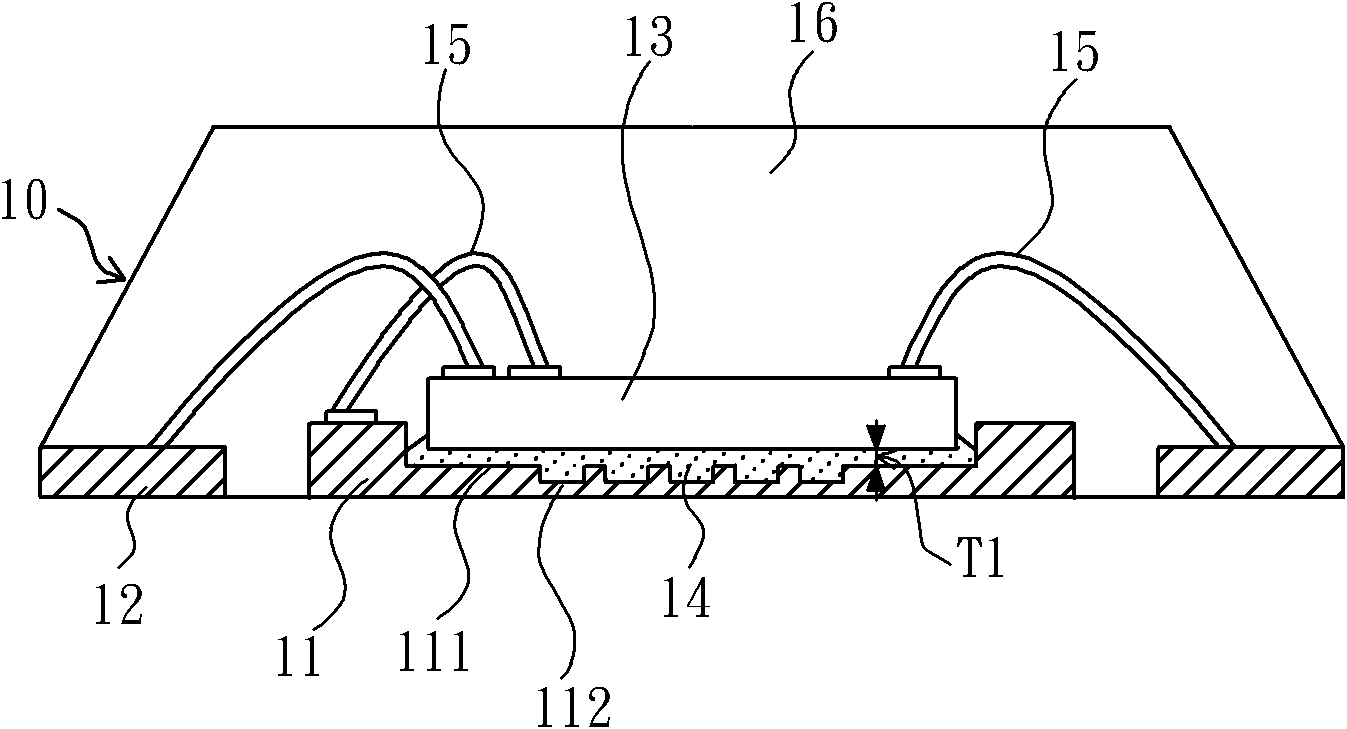

Packaging method for image sensor chip and packaging structure

ActiveCN105244339AAvoid Disengagement SituationsImprove packaging yieldSemiconductor/solid-state device detailsSolid-state devicesComputer scienceImage sensor

The invention provides a packaging method for an image sensor chip and a packaging structure. The packaging method comprises the steps as follows: a wafer is provided; the wafer comprises a first surface and a second surface opposite to the first surface, and comprises the image sensor chip which is formed by arranging a plurality of grids; the image sensor chip comprises an image sensor region and a boning pad; the image sensor region and the boning pad are located on the first surface of the wafer; an opening which extends towards the first surface is formed in the second surface of the wafer, and exposes the bonding pad; a V-shaped cutting groove which extends towards the first surface is formed in the second surface of the wafer; a photosensitive ink coats the second surface of the wafer, so that the V-shaped cutting groove is fully filled with the photosensitive ink; the photosensitive ink covers the opening; and a hollow cavity is formed in the opening. The hollow cavity is formed in the opening, so that the condition that a re-wiring layer is separated from the bonding pad is effectively avoided; the packaging yield of the image sensor chip is improved; and the reliability of the packaging structure of the image sensor chip is improved.

Owner:CHINA WAFER LEVEL CSP

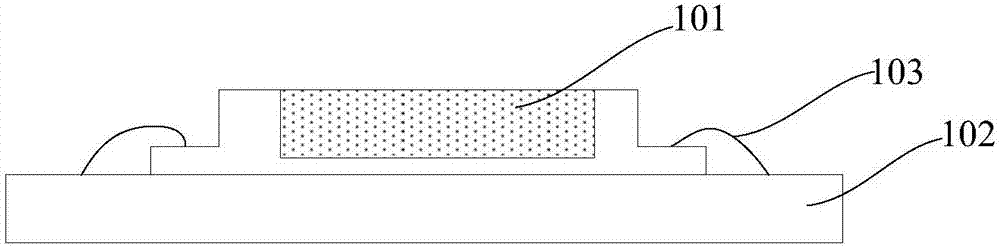

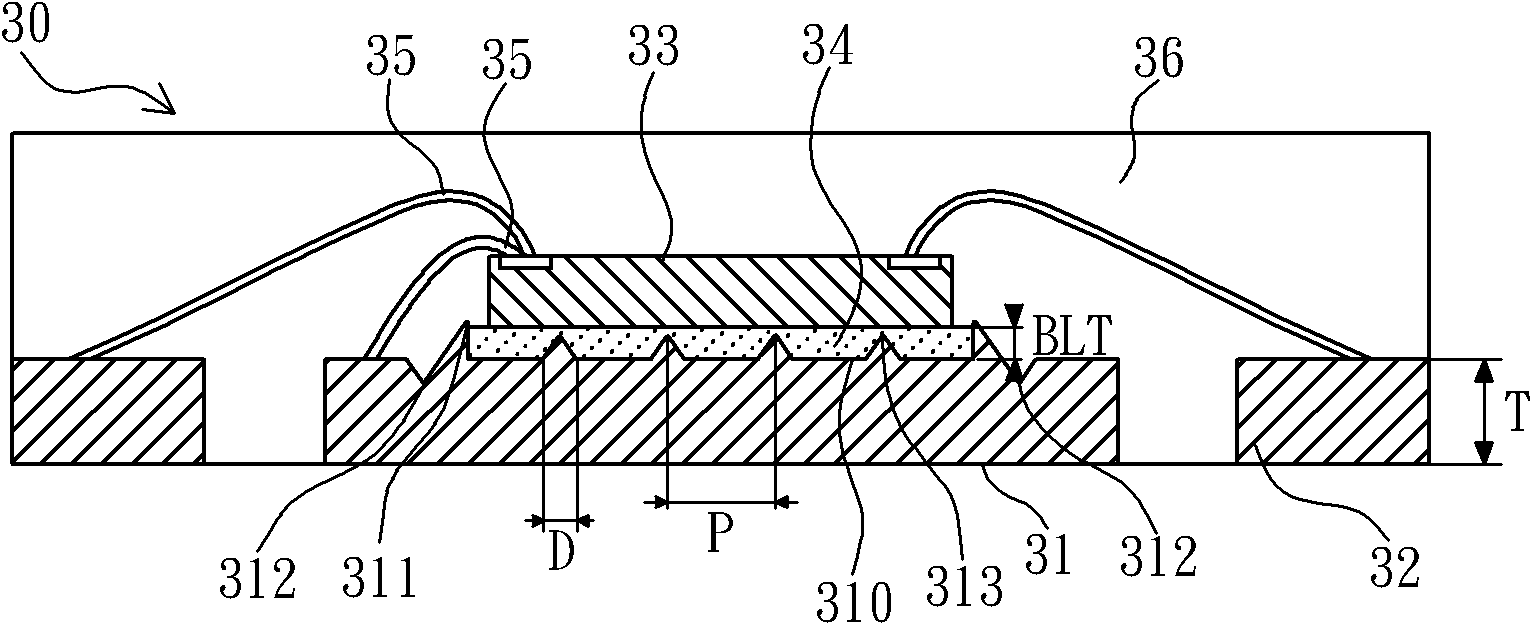

Lead frame of high-power chip package structure and manufacturing method thereof

ActiveCN102148213AIncreased processing optionsAvoid affecting the wiring operationSemiconductor/solid-state device detailsSolid-state devicesLead frameAdhesive materials

The invention discloses a lead frame of a high-power chip package structure and a manufacturing method thereof. A chip holder of the lead frame has a thickness of at least 0.5mm, so that sufficient heat absorbing efficiency and heat dissipation efficiency can be provided. The chip holder is also provided with an accommodating space for accommodating an adhesive layer, and a plurality of bumps are arranged at the inner bottom of the accommodating space, so that the lower surface of a high-power chip is prevented from tilting and an adhesive material in the accommodating space is prevented from overflowing, the levelness of the high-power chip is maintained, and the adhesion thickness of the adhesive layer is effectively and uniformly controlled. Therefore, the uniformity of heat energy conduction of the adhesive layer is favorably kept, furthermore, the reliability of the high-power chip package structure is relatively improved, and the service life is relatively prolonged.

Owner:ADVANCED SEMICONDUCT ENG (WEIHAI) INC