Ultra-narrow-pitch wafer level encapsulation cutting method

A wafer-level packaging and cutting method technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems affecting the number of packaged products, cutting process restrictions, and affecting the packaging yield, so as to improve the packaging yield , the process window is enlarged, and the process is simple

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

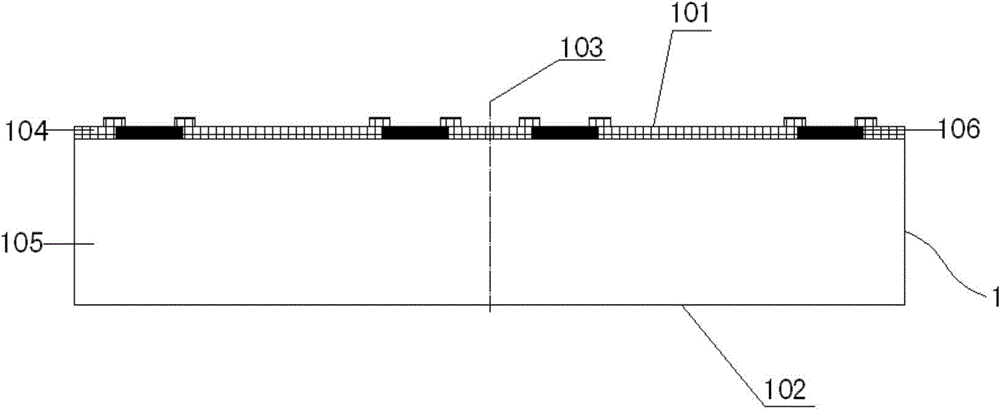

[0044] Figure 1 to Figure 8 A cross-sectional view of the manufacturing process of the ultra-narrow-pitch wafer-level packaging cutting method of the present invention is shown. Such as figure 1 As shown, a bare wafer 1 is provided, the functional surface thereof is the front side 101 , and the opposite side thereof is the back side 102 . The wafer includes a substrate 105 , a dielectric layer 104 on the functional surface of the substrate, and pads 106 partially disposed in the dielectric layer.

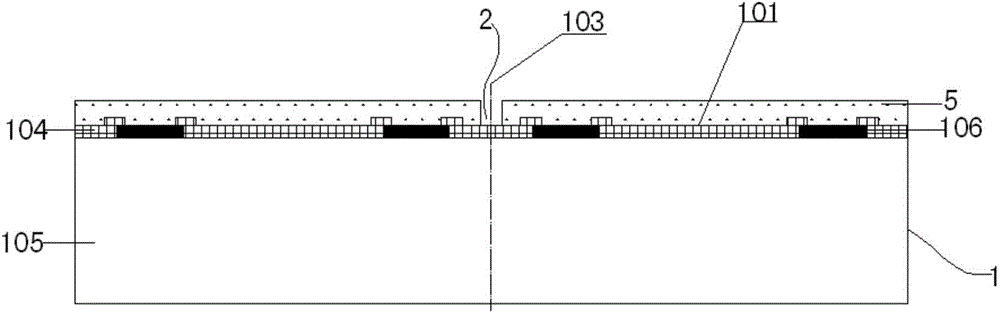

[0045] Next, if figure 2 As shown, a layer of photoresist 5 is coated on the front side of the wafer 1, and a first layer extending from the front side to the back side is formed on the front side of the wafer at a position facing the scribe line 103 through exposure and development processes. Opening 2, the first opening exposes the dielectric layer 104 facing the wafer dicing line;

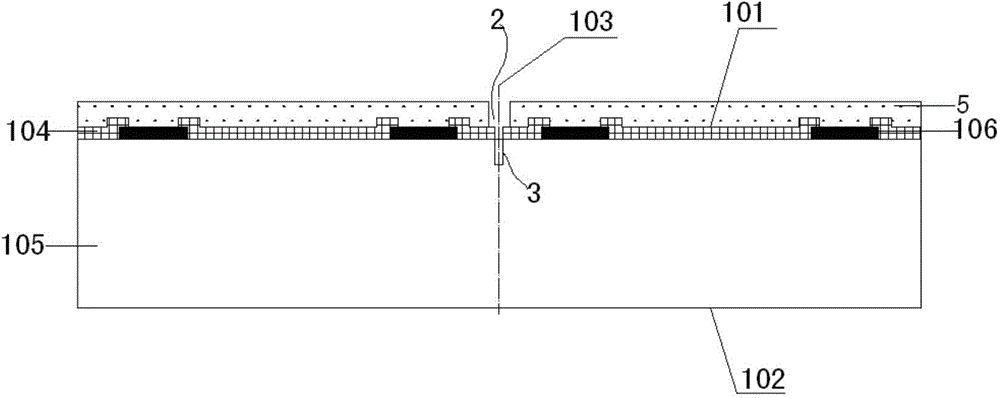

[0046] Next, if image 3 As shown, a second opening 3 extending from the front side to the ...

Embodiment 2

[0050] Figures 9 to 17 A cross-sectional view of a wafer-level packaging cutting process according to an embodiment of the present invention is shown. Such as Figure 9As shown, a half-encapsulated wafer 1 is provided, the functional surface of the wafer is a front surface 101, and the opposite side is a back surface 102, and the wafer includes a substrate 105, a dielectric layer 104 and a part of the functional surface of the substrate. The welding pad 106 arranged in the dielectric layer, the front side of the wafer is formed with a metal wiring layer 6 electrically leading out the welding pad 106 in the wafer dielectric layer, and a protective layer 7 is arranged above the metal wiring layer, A solder ball 8 serving as a connection window between the metal wiring layer and the outside world is formed on the protection layer, and the material of the protection layer is photoresist;

[0051] Next, if Figure 10 As shown, through the exposure and development process, the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More