Wafer-level packaging method for semiconductor and semiconductor packaging part

A wafer-level packaging and semiconductor technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problem of the narrow application range of wafer-to-wafer packaging, and improve the scope of packaging and reduce the area. wasteful effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

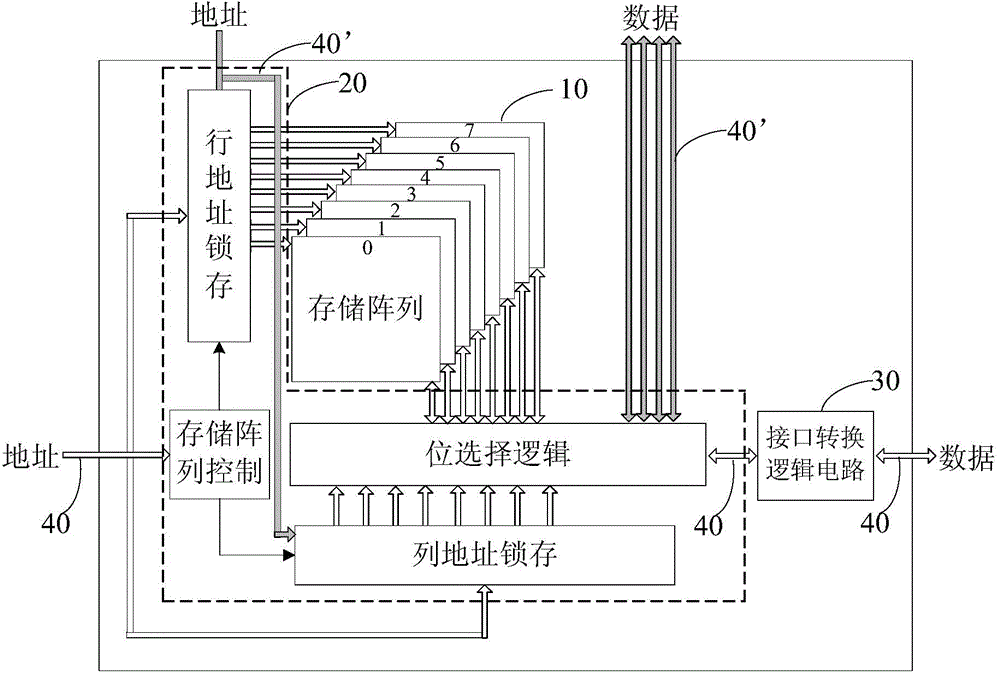

[0045] As mentioned in the background art, the current wafer-to-wafer packaging is still very narrow in application. One type of memory wafer cannot adapt to logic wafers of different sizes, and generally can only be used for one type of logic wafer.

[0046] To this end, the present invention provides a new semiconductor wafer-level packaging method, which improves the application range of wafer-to-wafer packaging by matching one logic chip unit with more than one memory chip unit, and Reduce the waste of chip area.

[0047] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0048] An embodiment of the present invention provides a semiconductor wafer-level packaging method, please refer to Figure 1 to Figure 4 .

[0049] Please refer to figure 1 , providing a first wafer 100 having one or mo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More