Device with through-silicon via (tsv) and method of forming the same

A device, silicon substrate technology, used in semiconductor devices, electric solid state devices, semiconductor/solid state device manufacturing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

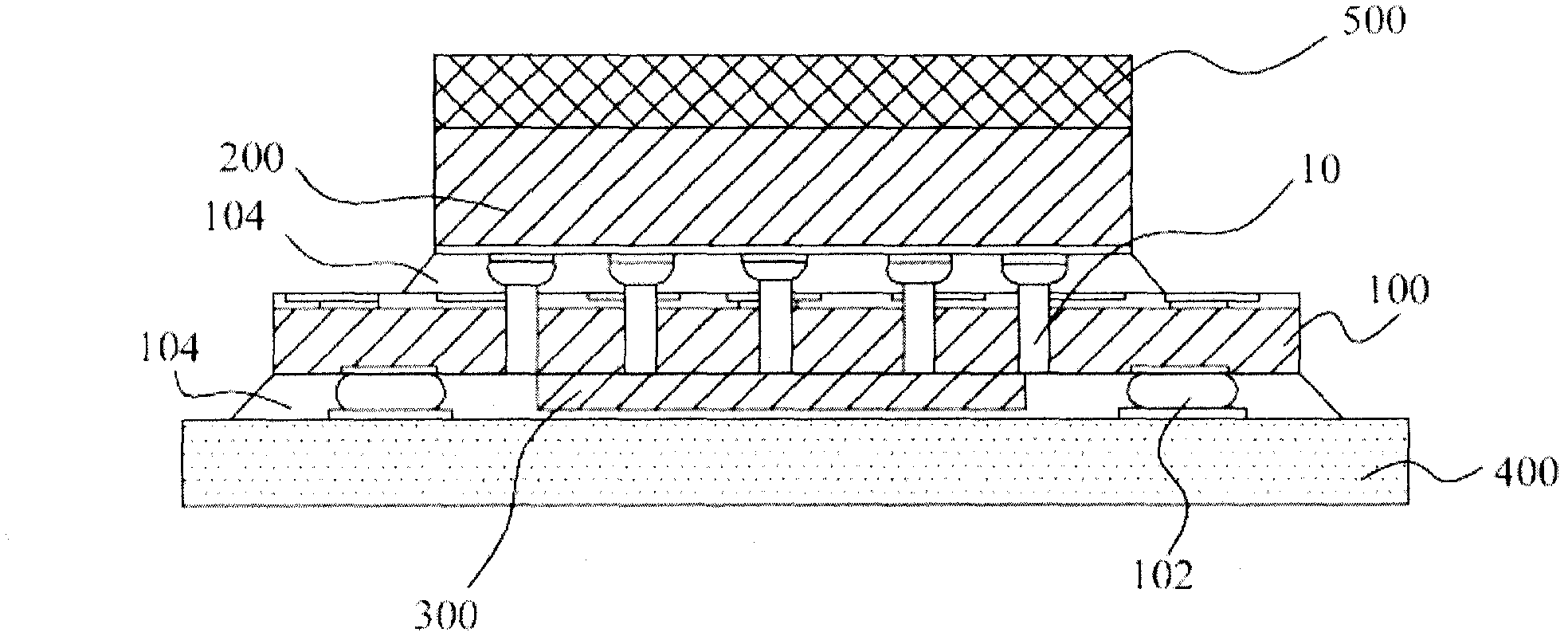

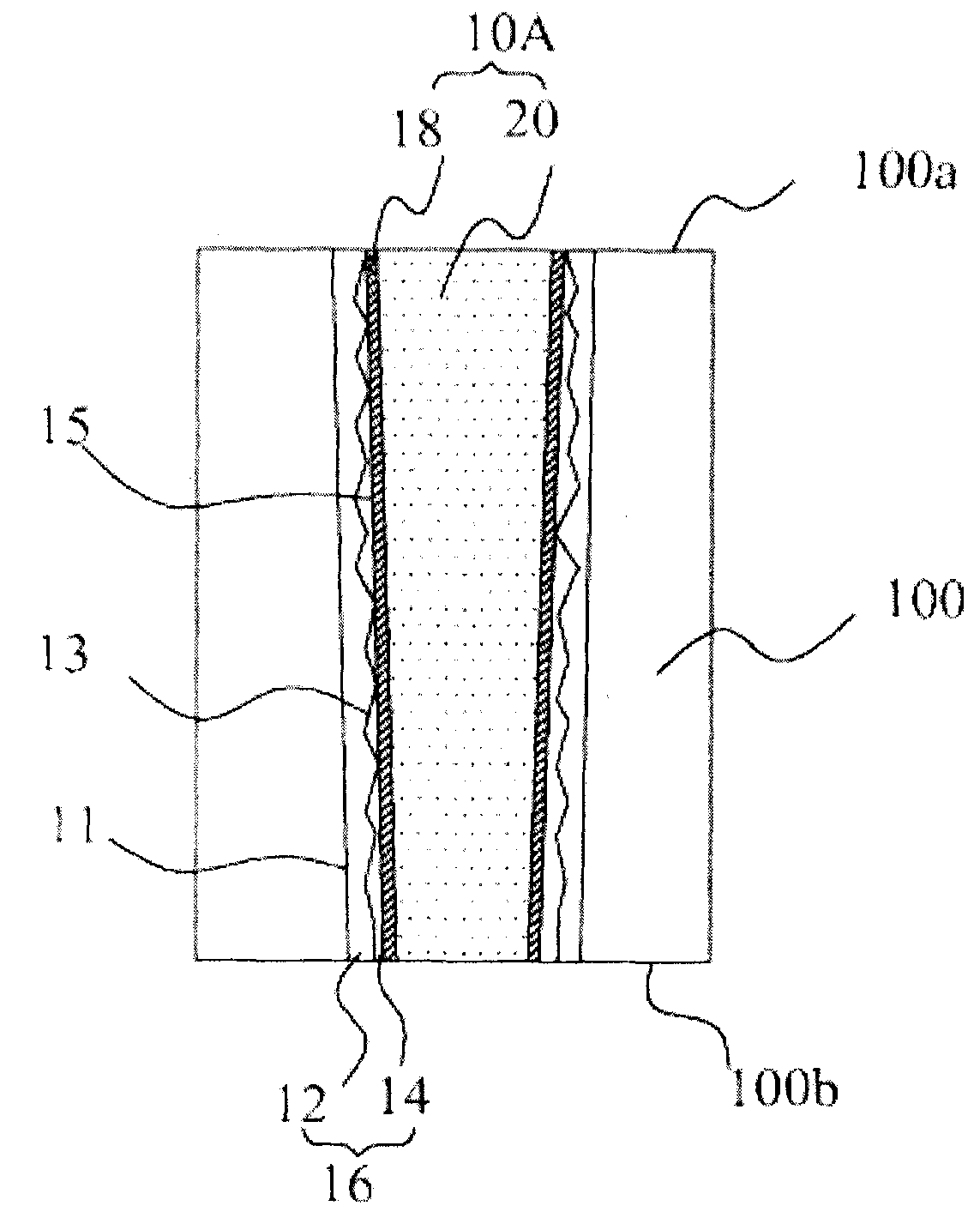

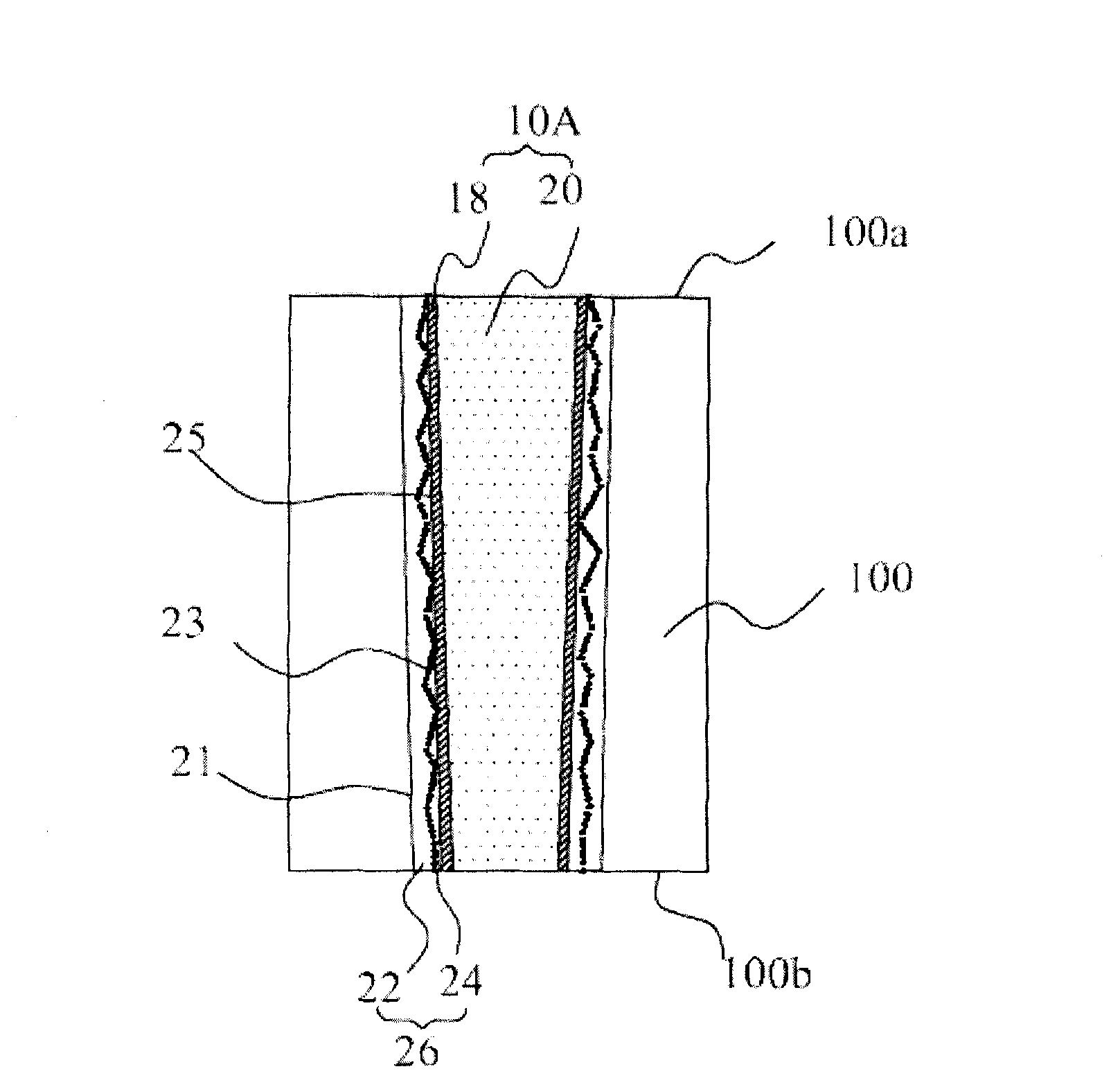

[0029] The present disclosure provides embodiments of TSVs with sidewall insulation and processes for forming the same. TSVs with sidewall insulation can be fabricated on wafers, IC dies, interposers, or substrates for flip-chip assembly, wafer-level chip-scale packaging (WLCSP), three-dimensional integrated circuit (3D-IC) stacking, and / or Or any advanced packaging technology field. Exemplary embodiments shown in the drawings will now be described in detail. Wherever possible, the same reference numbers are used in the drawings and description to refer to the same or like parts. In the drawings, shapes and thicknesses may be exaggerated for clarity and convenience. The description is particularly directed to elements forming part of, or cooperating directly with, an apparatus according to the present disclosure. It is to be understood that elements not specifically shown or described may take any form known in the art. Also, when a layer is referred to as being on another...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More