Patents

Literature

76 results about "Interfacial roughness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

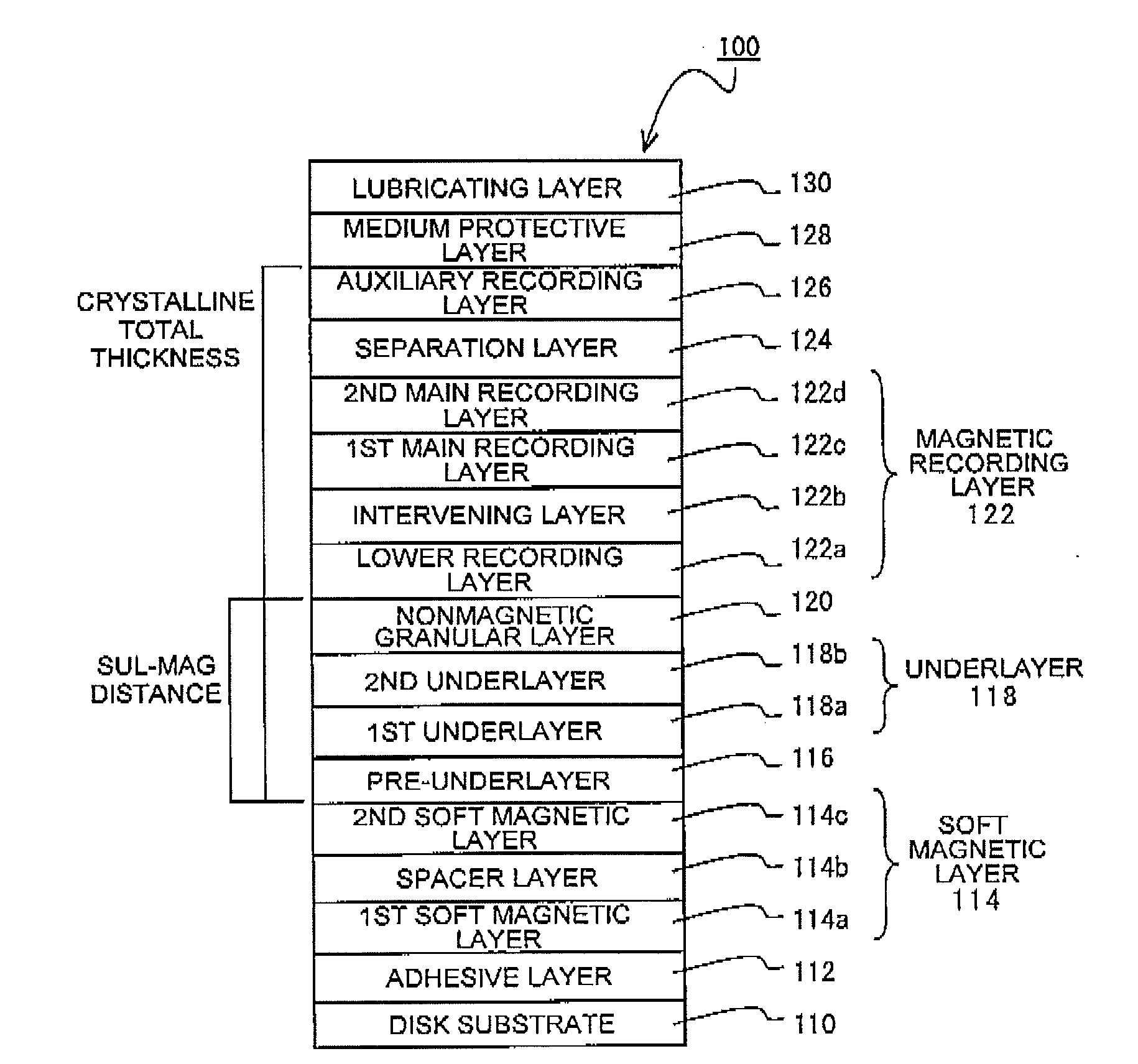

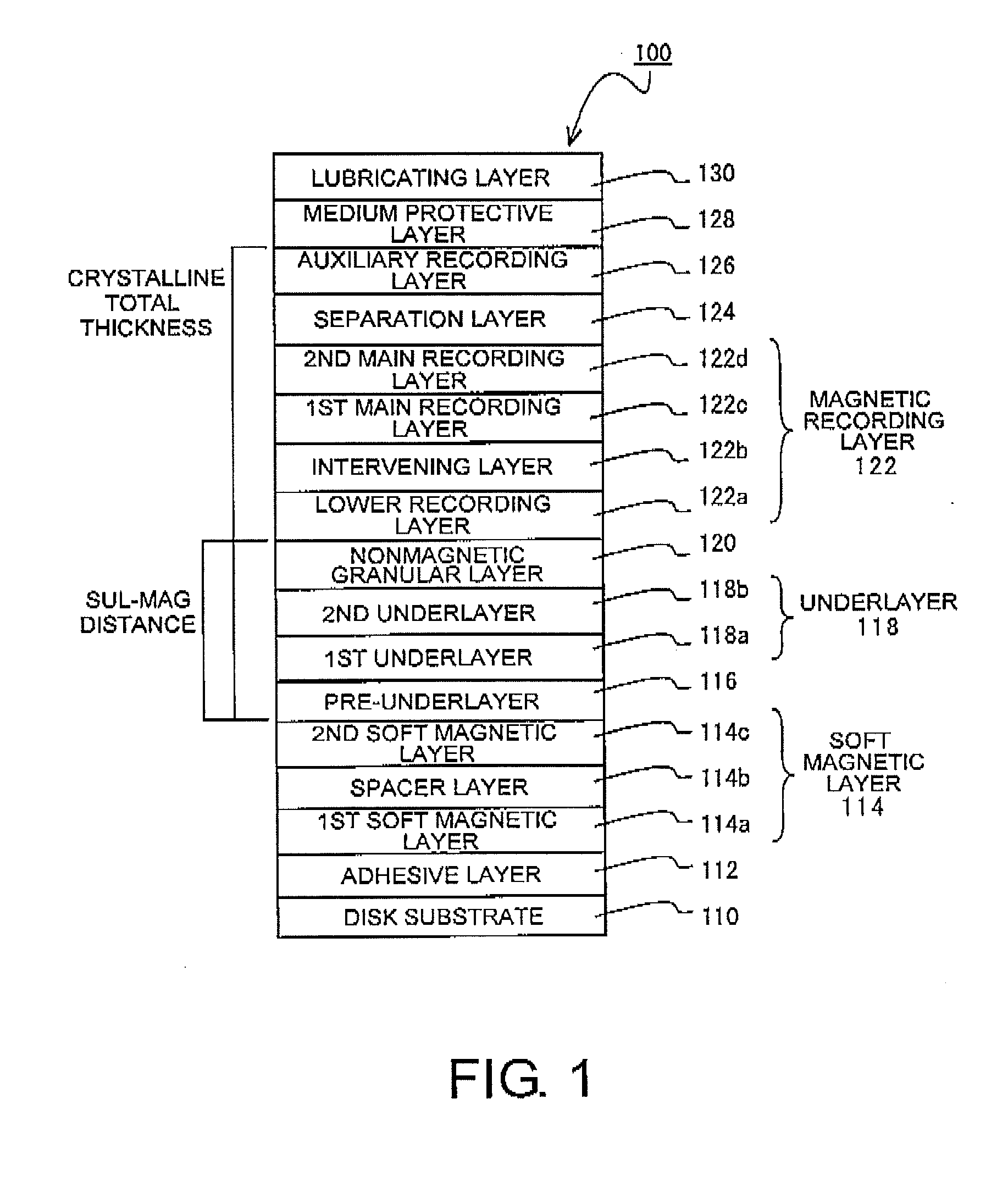

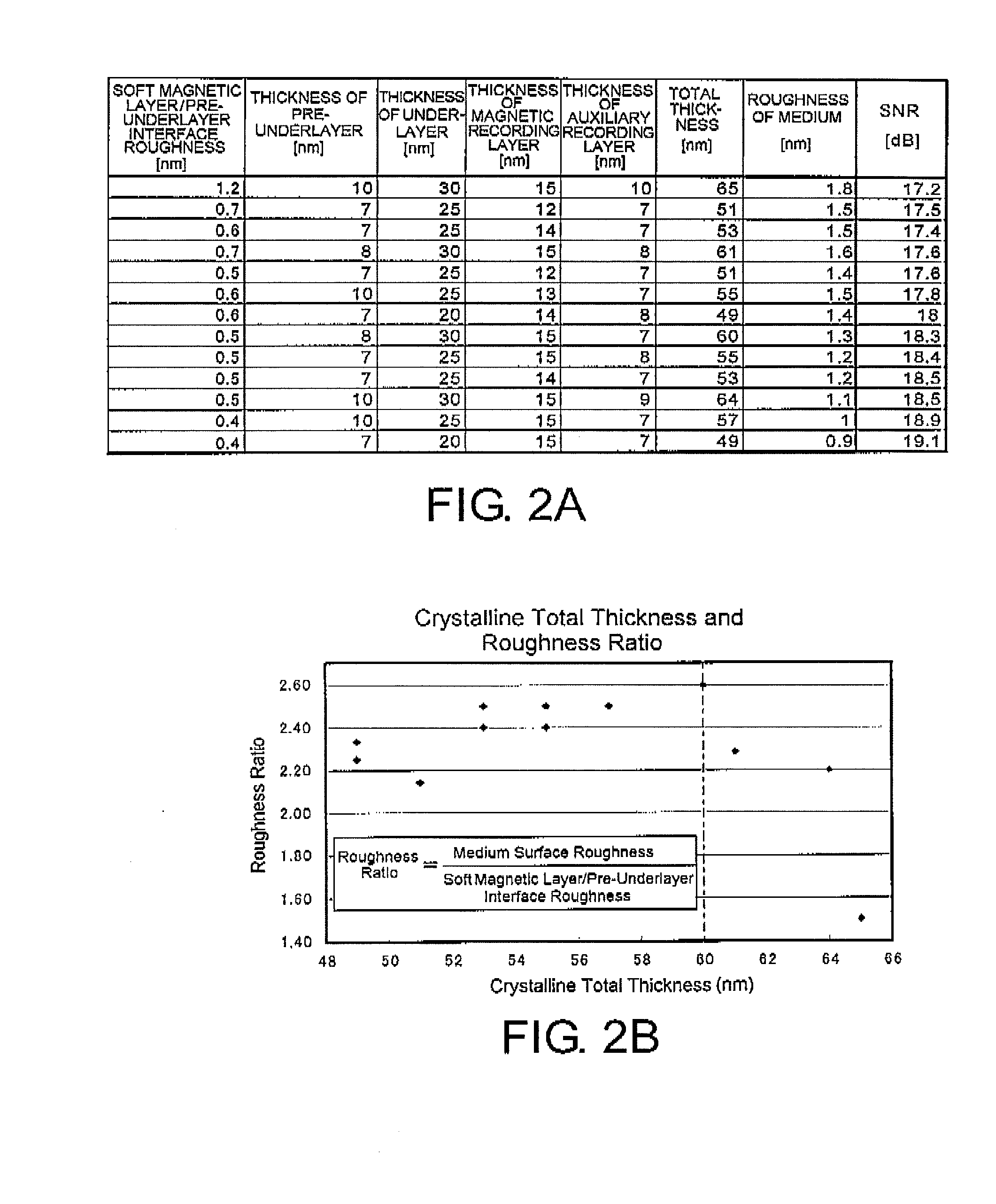

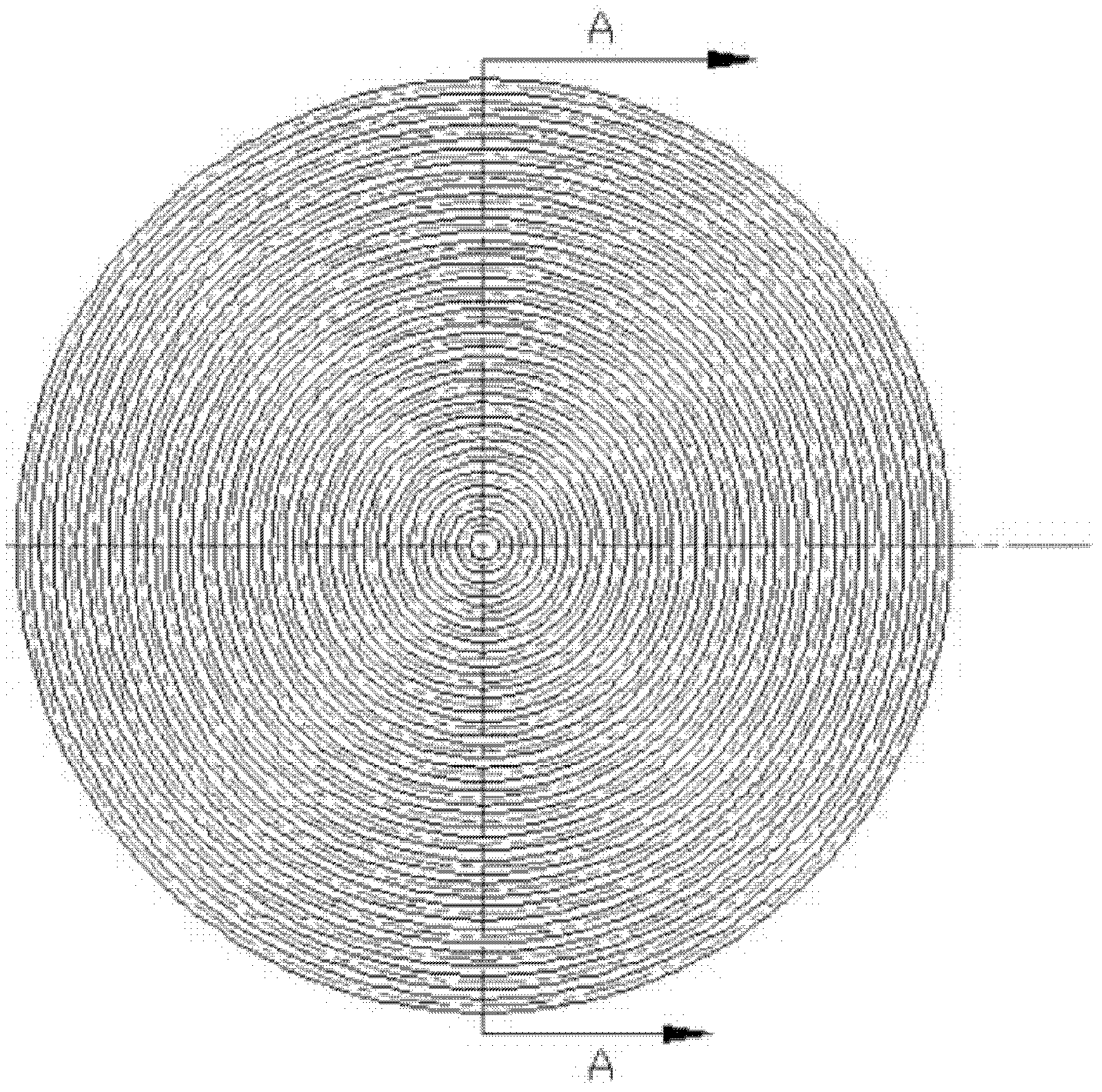

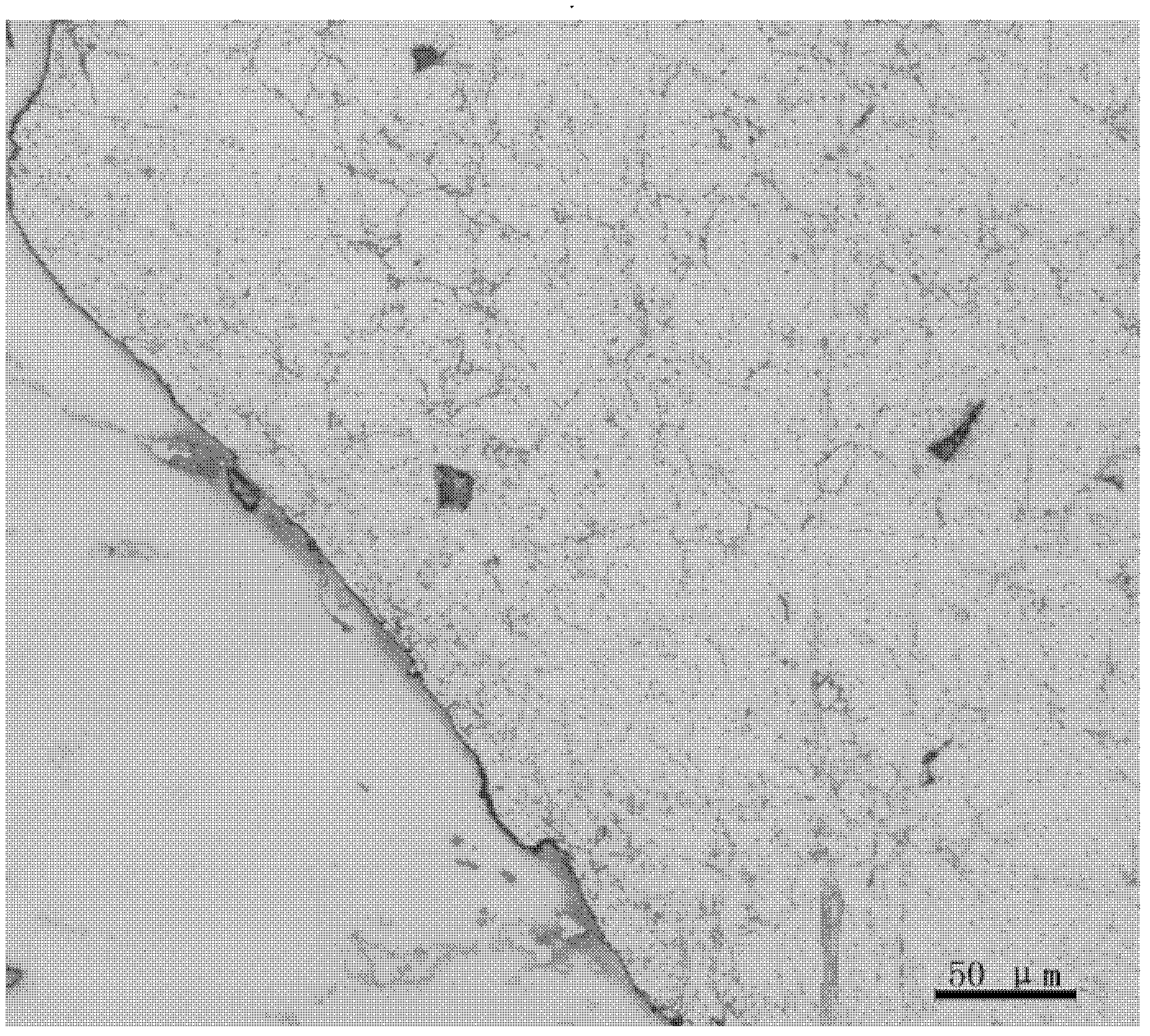

Perpendicular magnetic recording medium

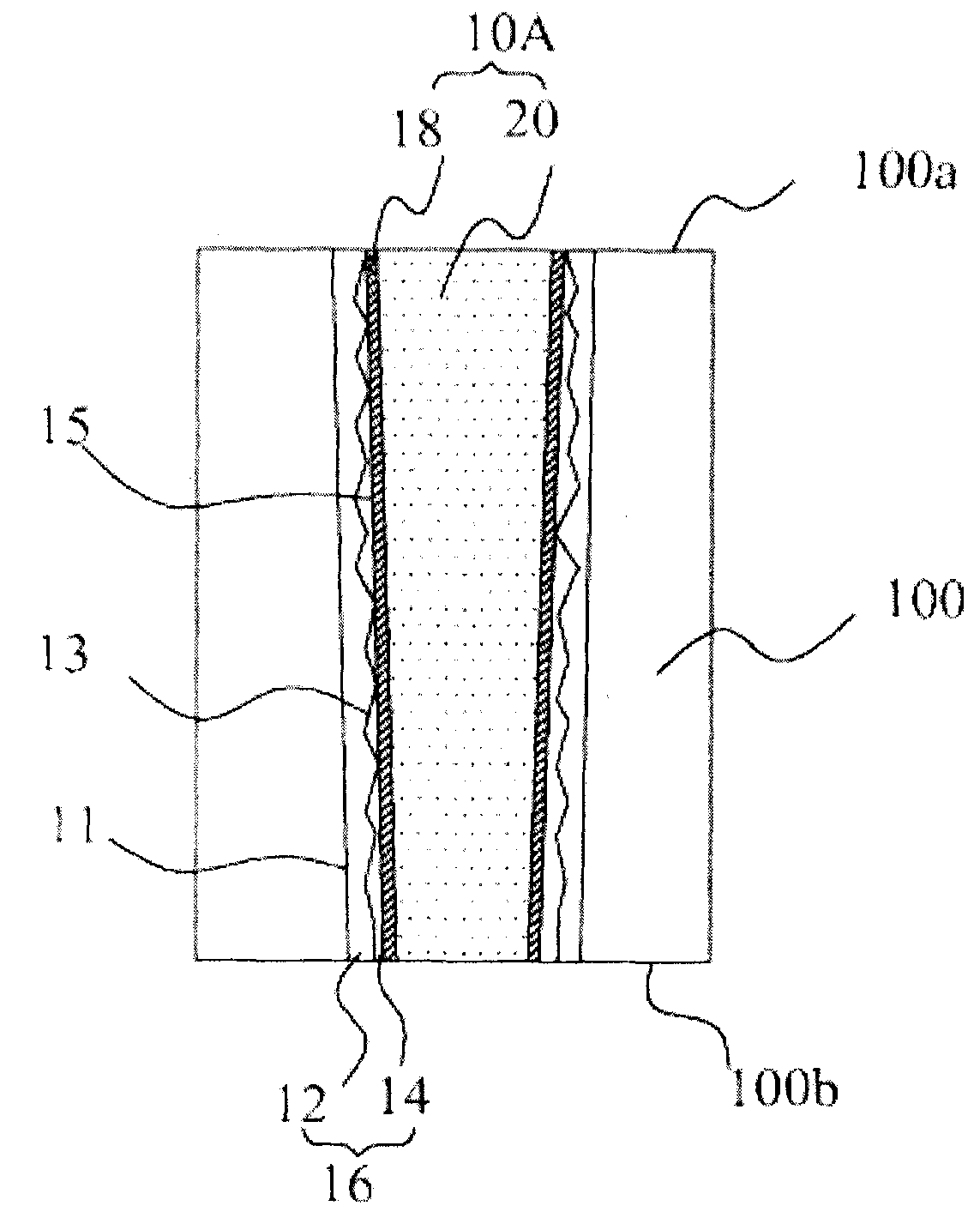

ActiveUS20100247965A1Reduce surface roughnessImprove recording densityRecord information storageManufacture of flux-sensitive headsCrystalline materialsNon magnetic

In a perpendicular magnetic recording medium having, over a substrate, a magnetic recording layer, an underlayer made of Ru or a Ru compound and provided below the magnetic recording layer, a pre-underlayer made of a nonmagnetic crystalline material, and a soft magnetic layer provided below the pre-underlayer, when the difference between the highest point and the lowest point of unevenness of the interface between the soft magnetic layer and the pre-underlayer, derived by a cross-sectional TEM image, is given as an interface roughness (nm) and the distance between the soft magnetic layer and the magnetic recording layer, excluding the soft magnetic layer and the magnetic recording layer, is given as a SUL-MAG distance (nm), interface roughness (nm)≦0.4 (nm) and interface roughness×SUL-MAG distance (nm)≦12 (nm) are satisfied.

Owner:WESTERN DIGITAL TECH INC

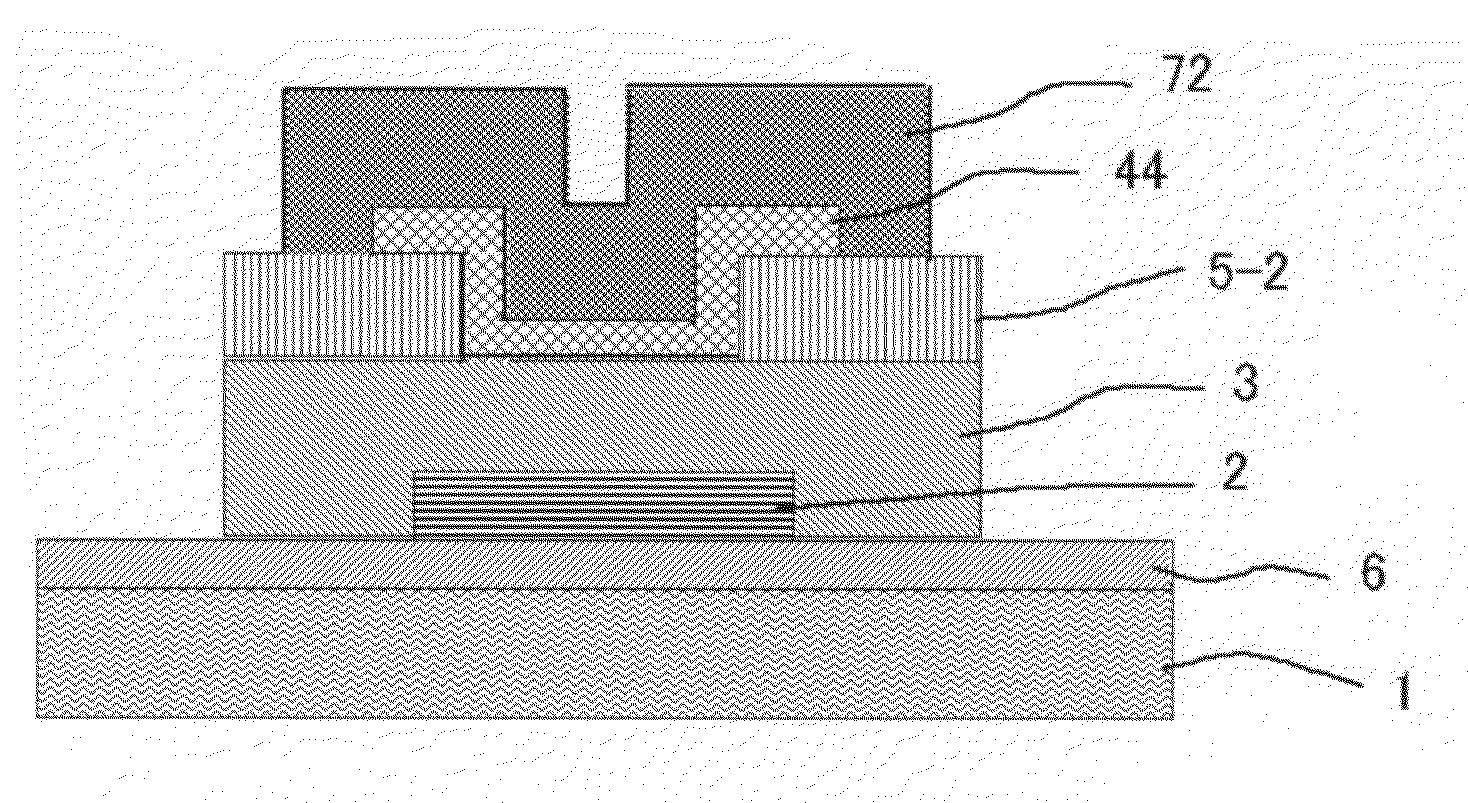

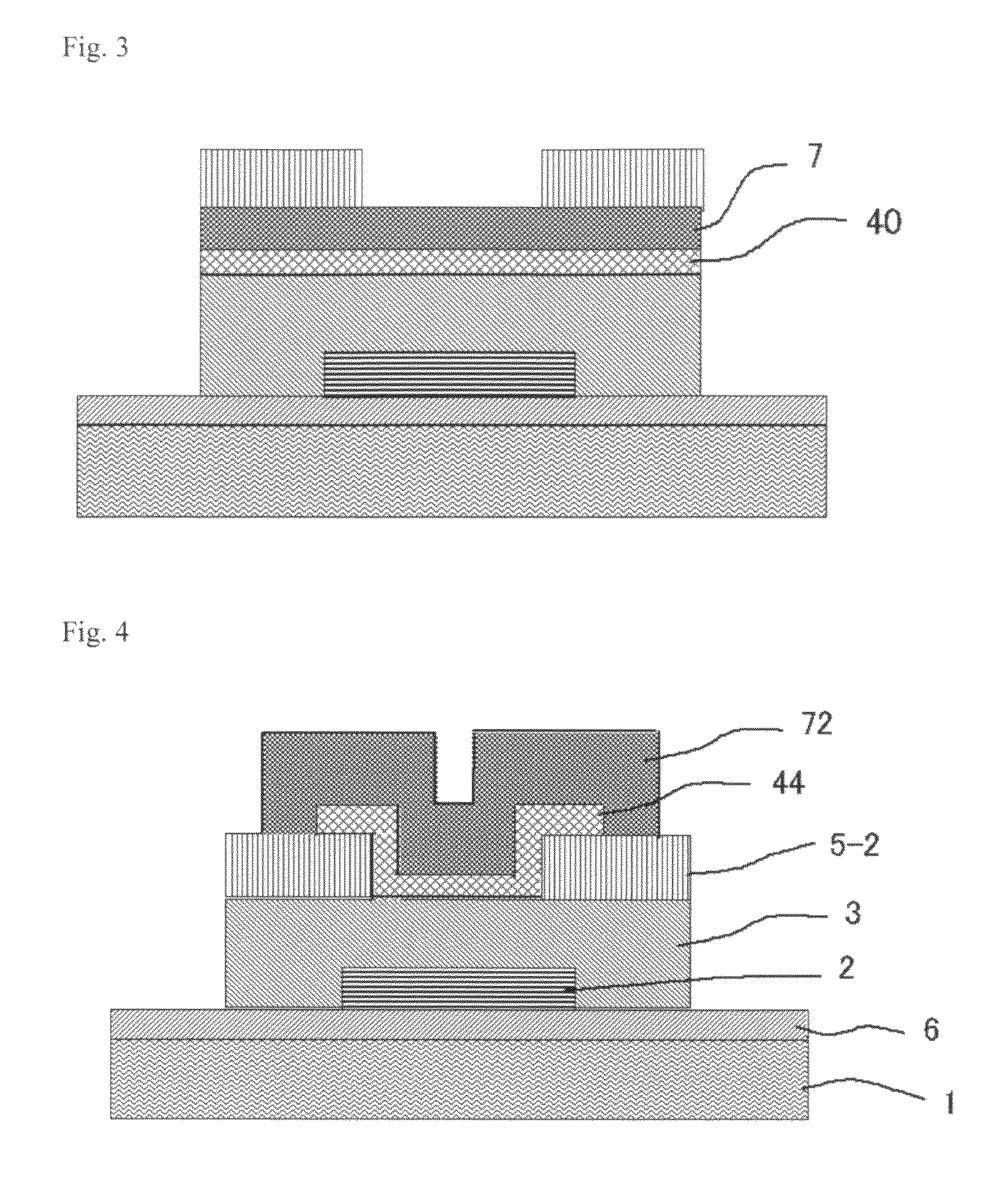

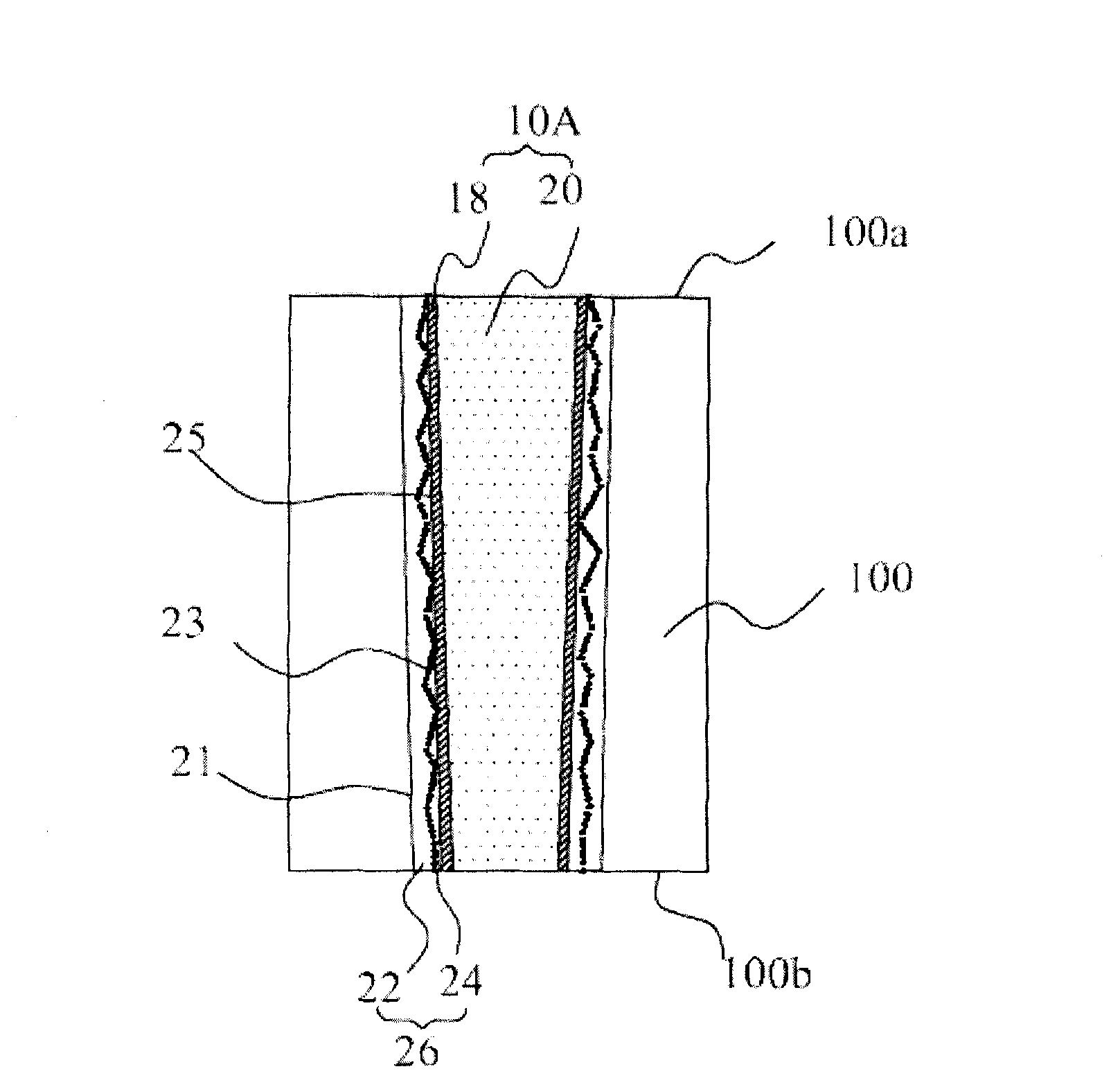

Thin film field effect transistor and display using the same

A TFT is provided which includes on a substrate, at least a gate electrode, a gate insulating layer, an active layer containing an amorphous oxide semiconductor, a source electrode, and a drain electrode, wherein a mean square interface roughness between the gate insulating layer and the active layer is less than 2 nm, a carrier concentration of the active layer is 1×1015 cm−3 or more, and a film thickness of the active layer is 0.5 nm or more and less than 20 nm. A TFT is provided which has high field effect mobility and a high ON-OFF ratio, and is improved in environmental temperature dependency. Also, a display using the TFT is provided.

Owner:SAMSUNG DISPLAY CO LTD

Thin film field effect transistor with amorphous oxide active layer and display using the same

A TFT is provided which includes on a substrate, at least a gate electrode, a gate insulating layer, an active layer containing an amorphous oxide semiconductor, a source electrode, and a drain electrode, wherein a mean square interface roughness between the gate insulating layer and the active layer is less than 2 nm, a carrier concentration of the active layer is 1×1015 cm−3 or more, and a film thickness of the active layer is 0.5 nm or more and less than 20 nm. A TFT is provided which has high field effect mobility and a high ON-OFF ratio, and is improved in environmental temperature dependency. Also, a display using the TFT is provided.

Owner:SAMSUNG DISPLAY CO LTD

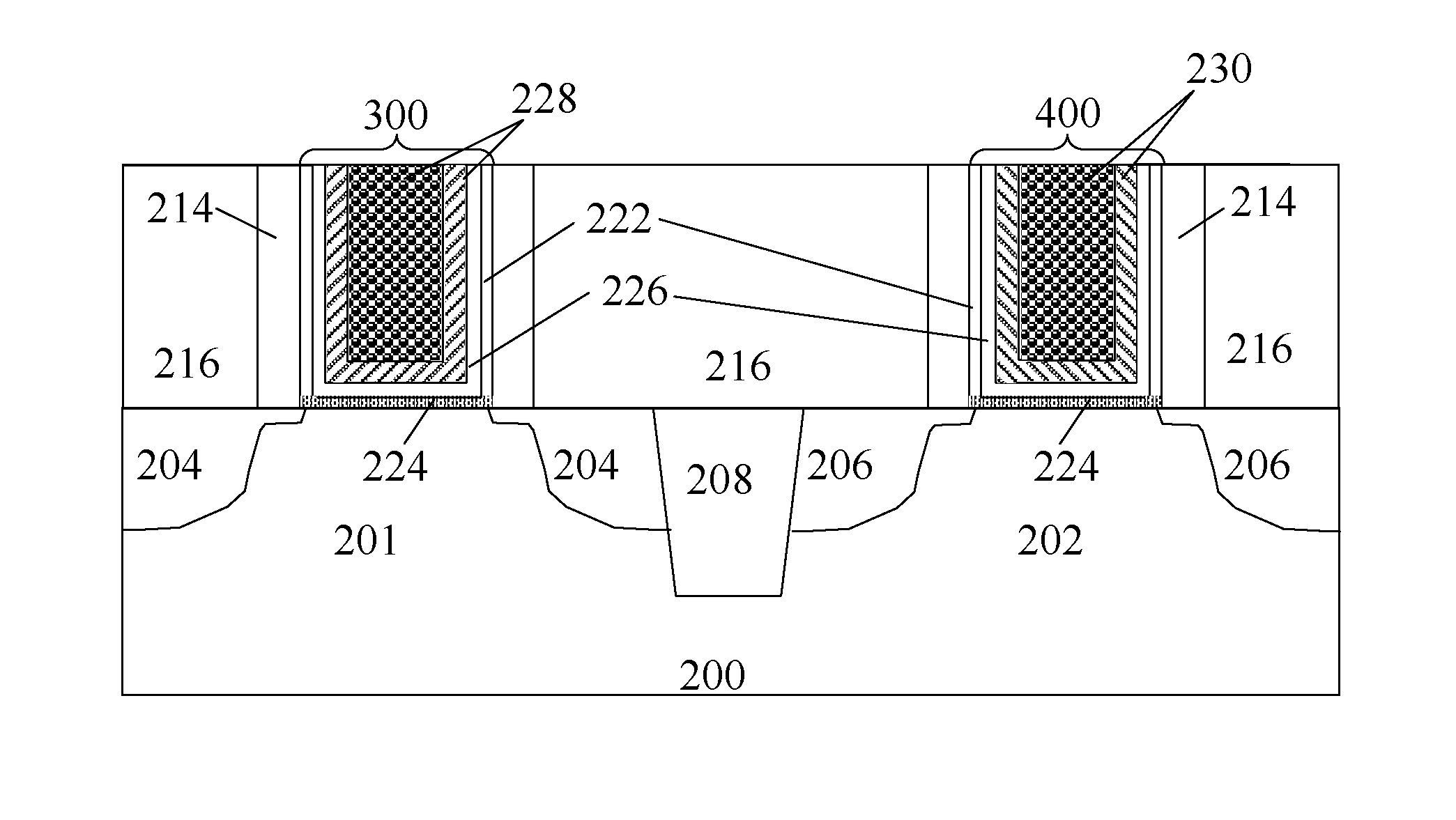

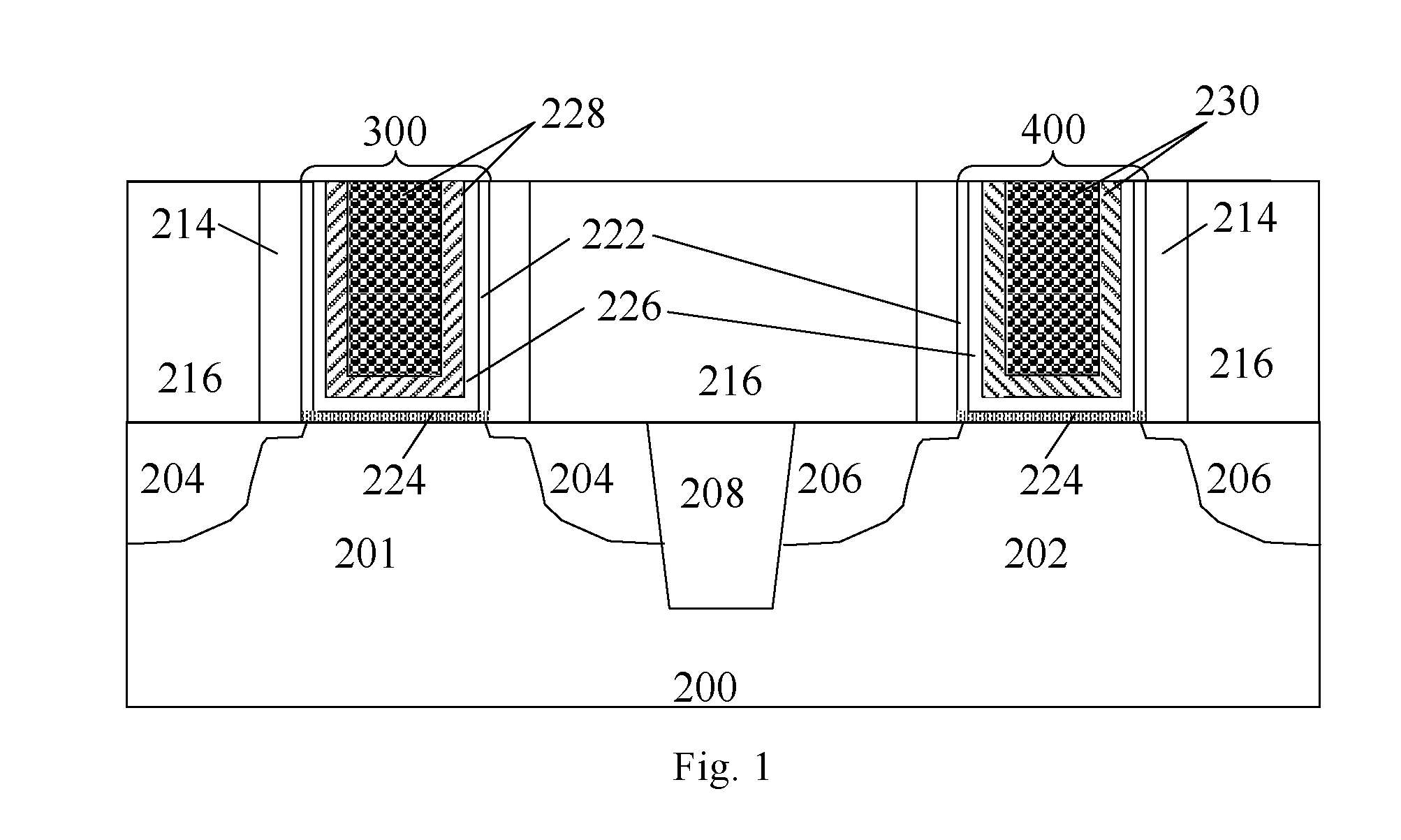

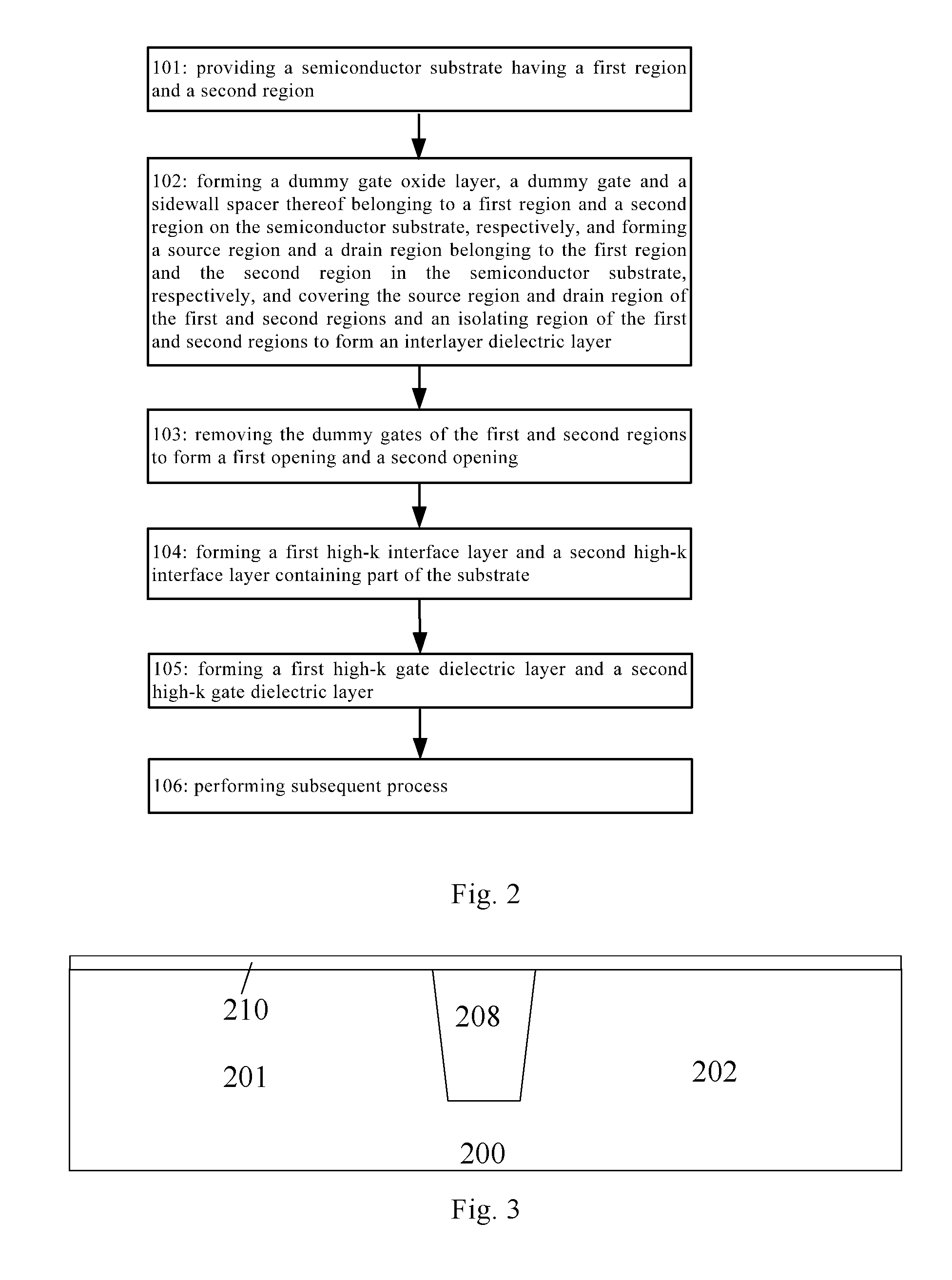

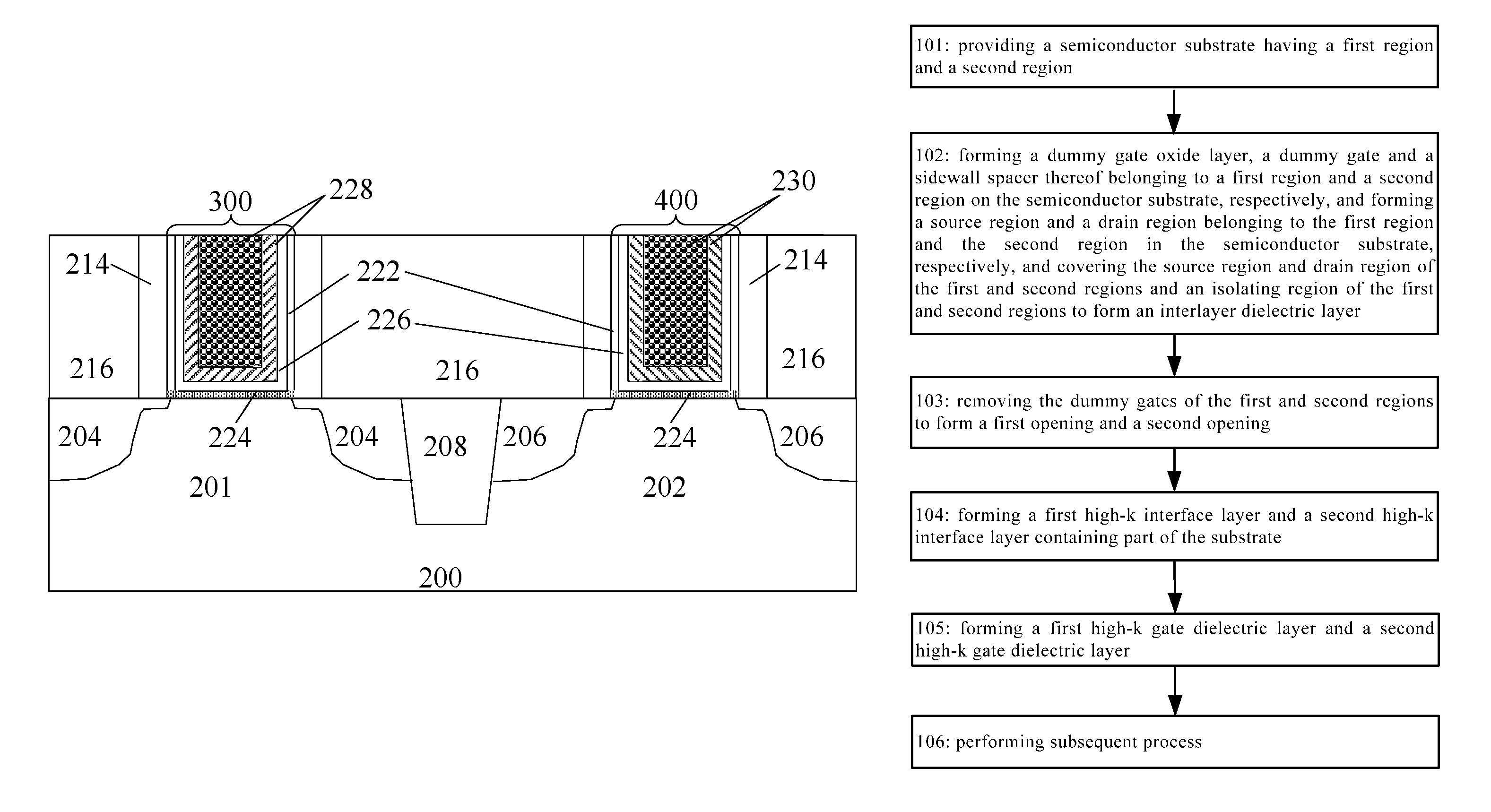

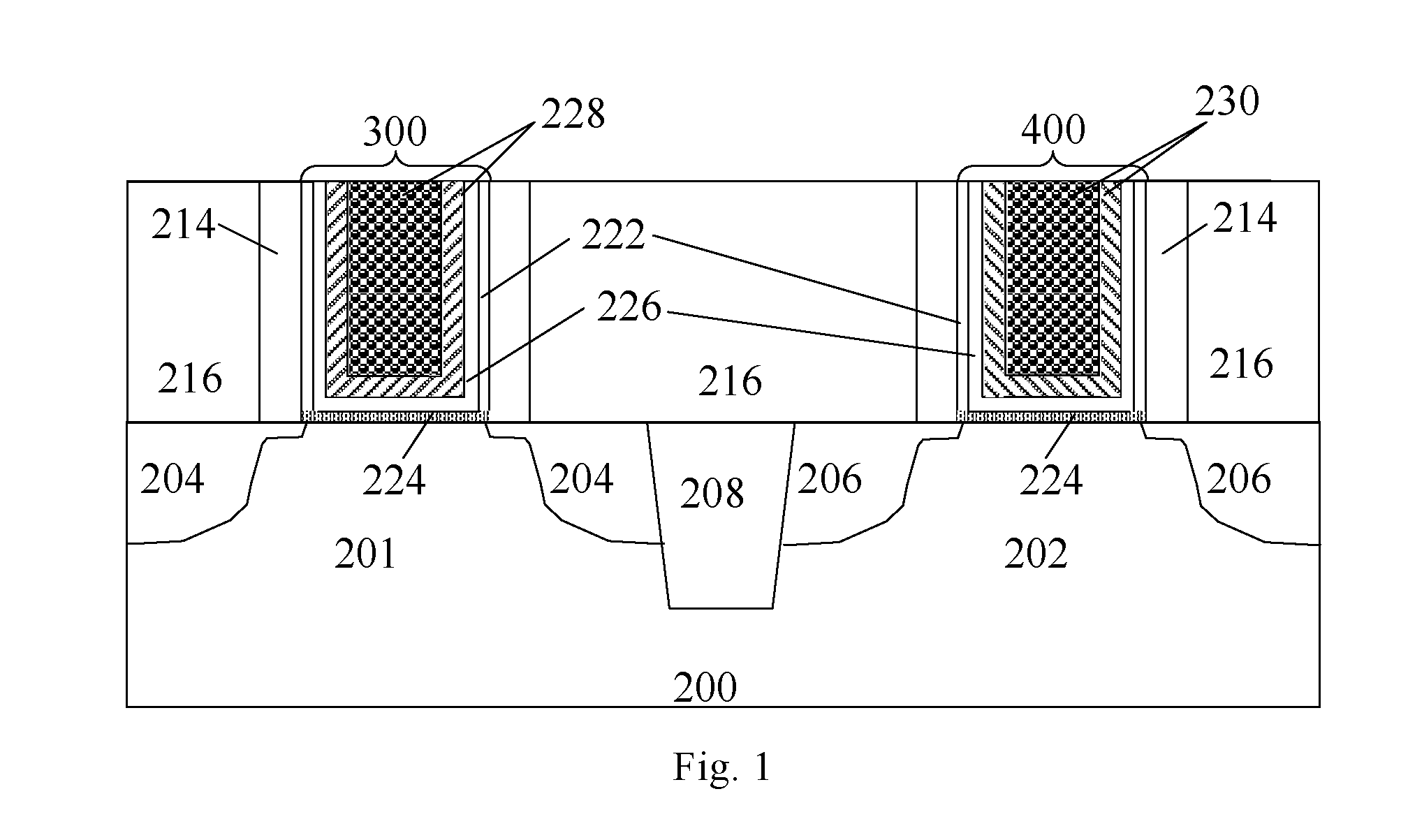

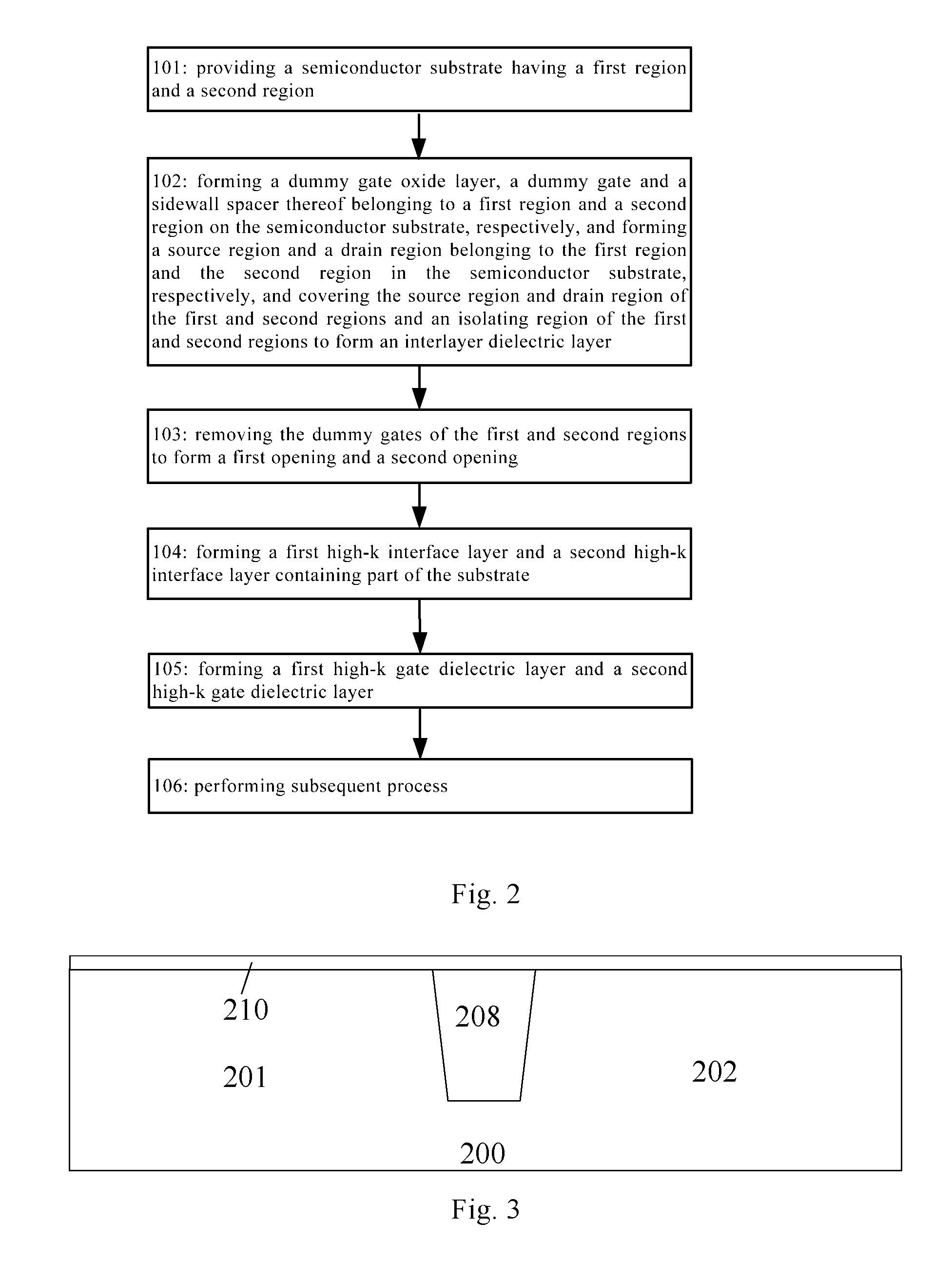

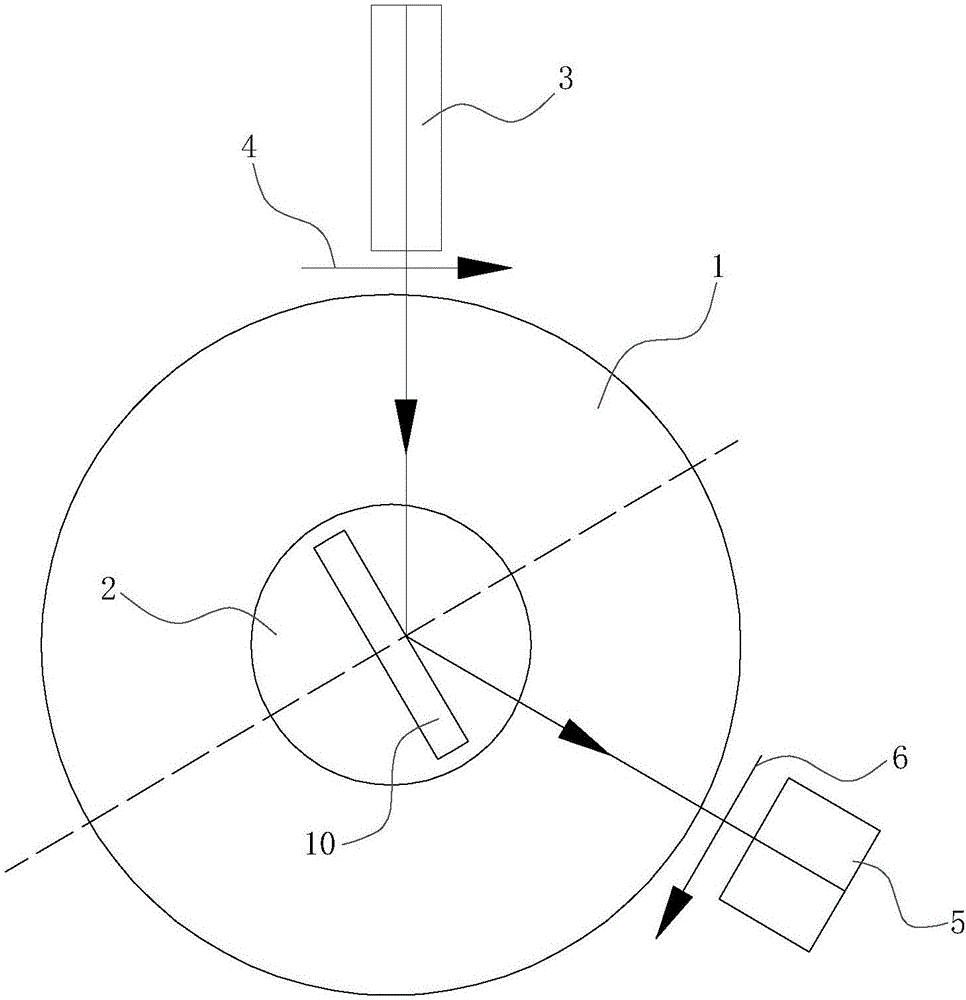

Semiconductor device and method of manufacturing the same

ActiveUS20110254093A1Reduce EOTAvoid degradationTransistorSolid-state devicesDielectricGate dielectric

A semiconductor device and a method of manufacturing the same are provided. A multi-component high-k interface layer containing elements of the substrate is formed from a ultra-thin high-k dielectric material in a single-layer structure of atoms by rapid annealing in the manufacturing of a CMOS transistor by the replacement gate process, and a high-k gate dielectric layer with a higher dielectric constant and a metal gate layer are formed thereon. The EOT of the device is effectively decreased, and the diffusion of atoms in the high-k gate dielectric layer from an upper level thereof is effectively prevented by the optimized high-k interface layer at high-temperature treatment. Thus, the present invention may also avoid the growth of the interface layers and the degradation of carrier mobility. Furthermore, the present invention may further alleviate the problem of high interface state and interface roughness caused by direct contact of the high-k gate dielectric layer with high dielectric constant and the substrate, and thus the overall performance of the device is effectively enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

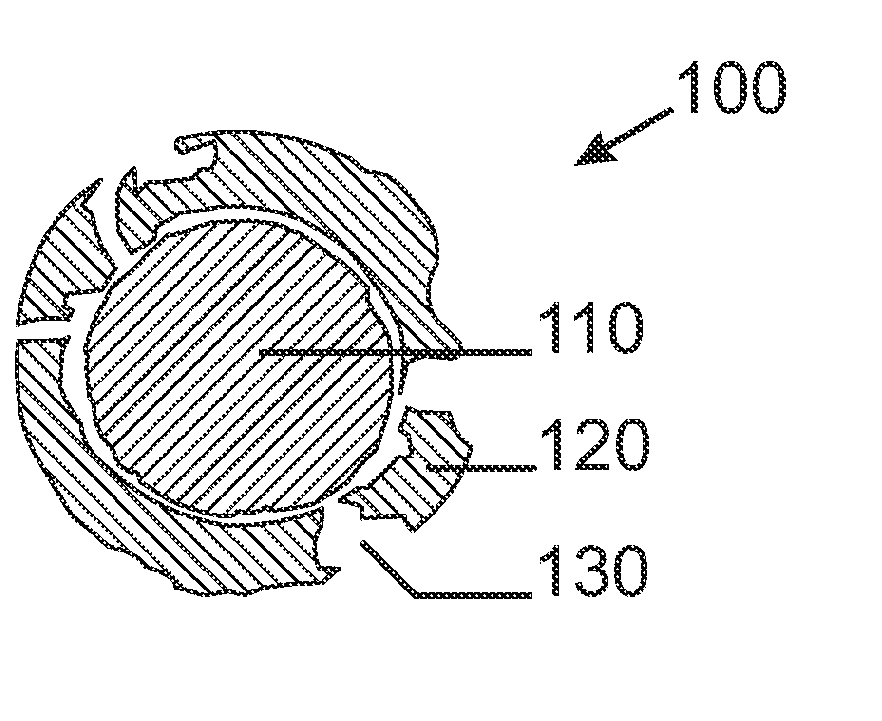

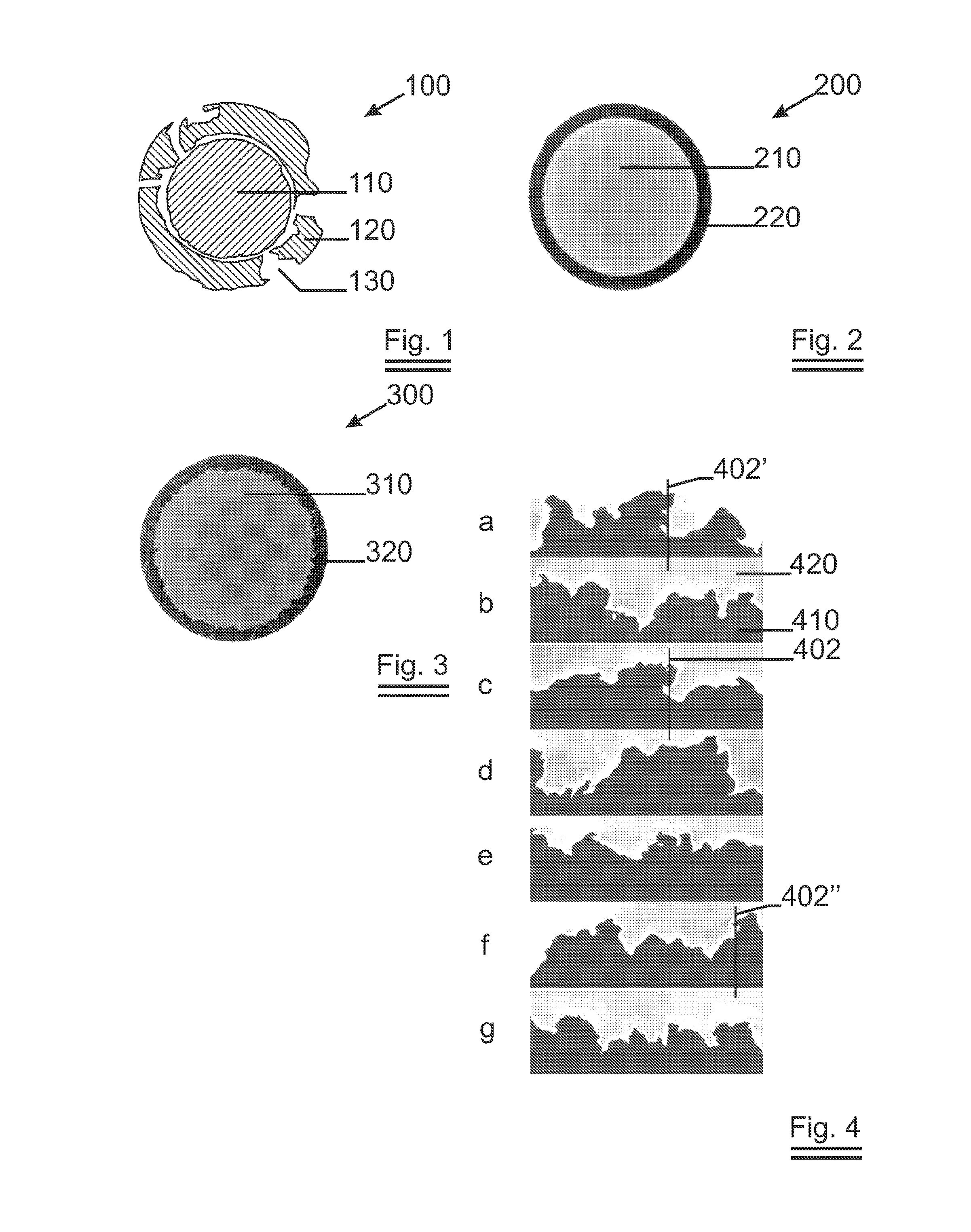

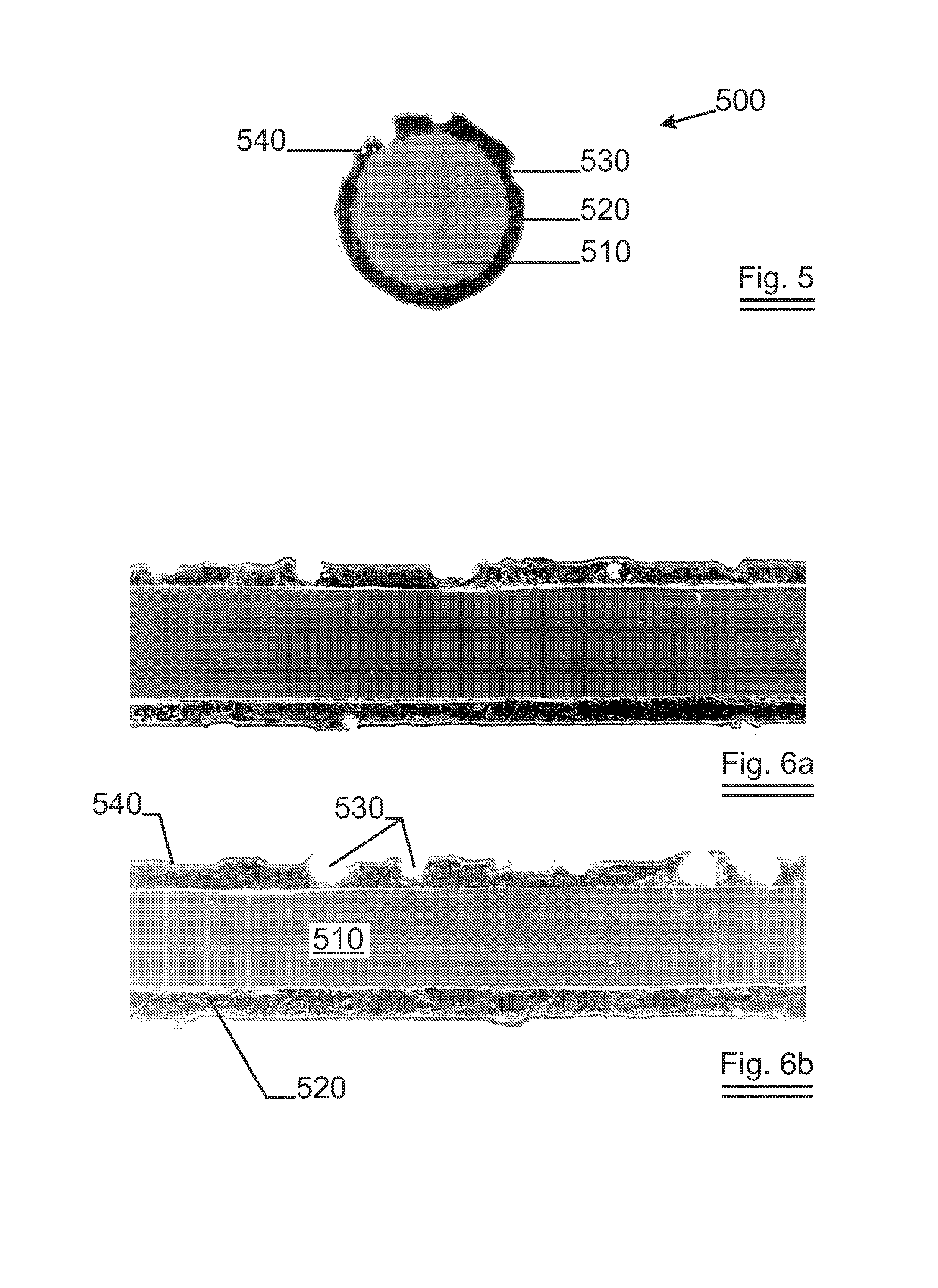

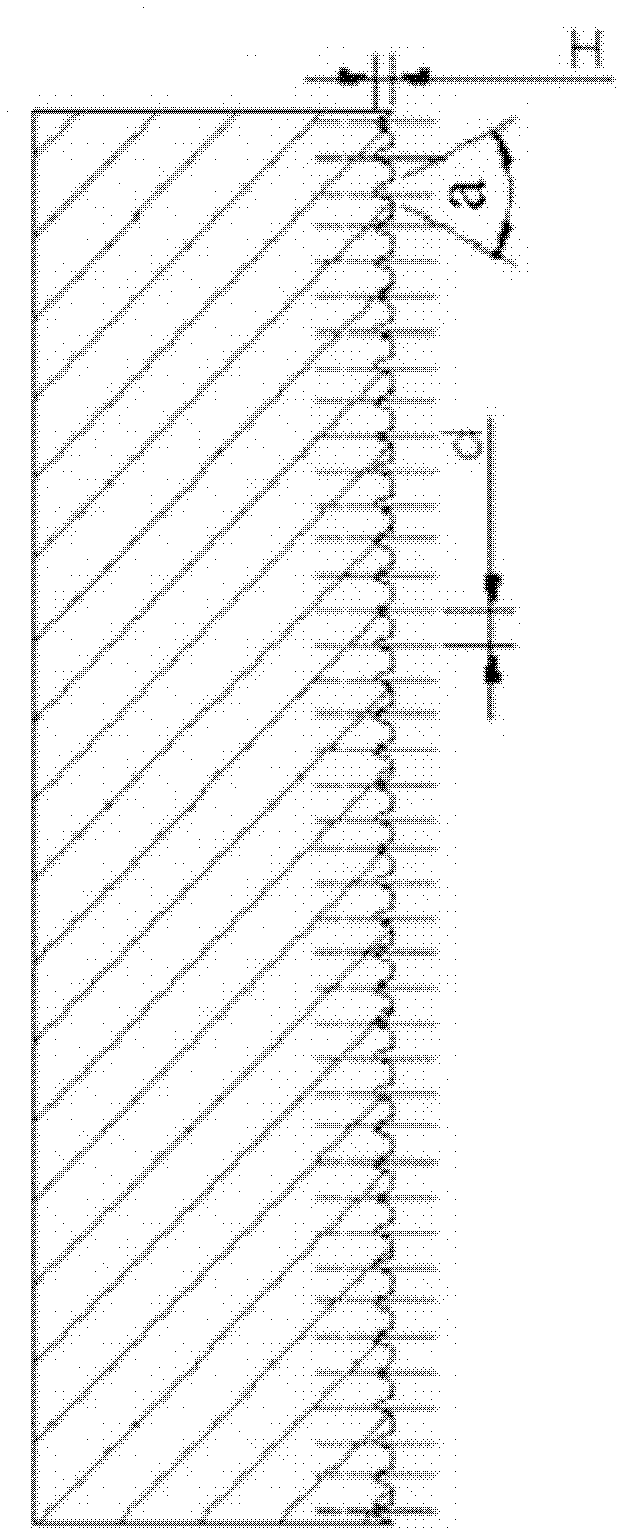

Fixed abrasive sawing wire with a rough interface between core and outer sheath

InactiveUS20120037140A1Extended service lifeMinimise kerf lossAbrasion apparatusMetal sawing toolsMetalMaterials science

A fixed abrasive sawing wire is presented that comprises a core (310) and an outer sheath layer (320) that is softer than the core. In the sheath abrasive particles are embedded that are held by a binding layer. The bond between core and sheath is enhanced by making it rough. The arithmetical mean deviating roughness must at least be higher than 0.50 micron. Particularly preferred is when interlocking between the core and the sheath is introduced. Such interface roughness can be obtained by subjecting the wire to sufficient cold forming by wire drawing. Interlocking will occur at even higher degrees of cold forming. The binding layer can be a metallic binding layer or an organic binding layer.

Owner:NV BEKAERT SA

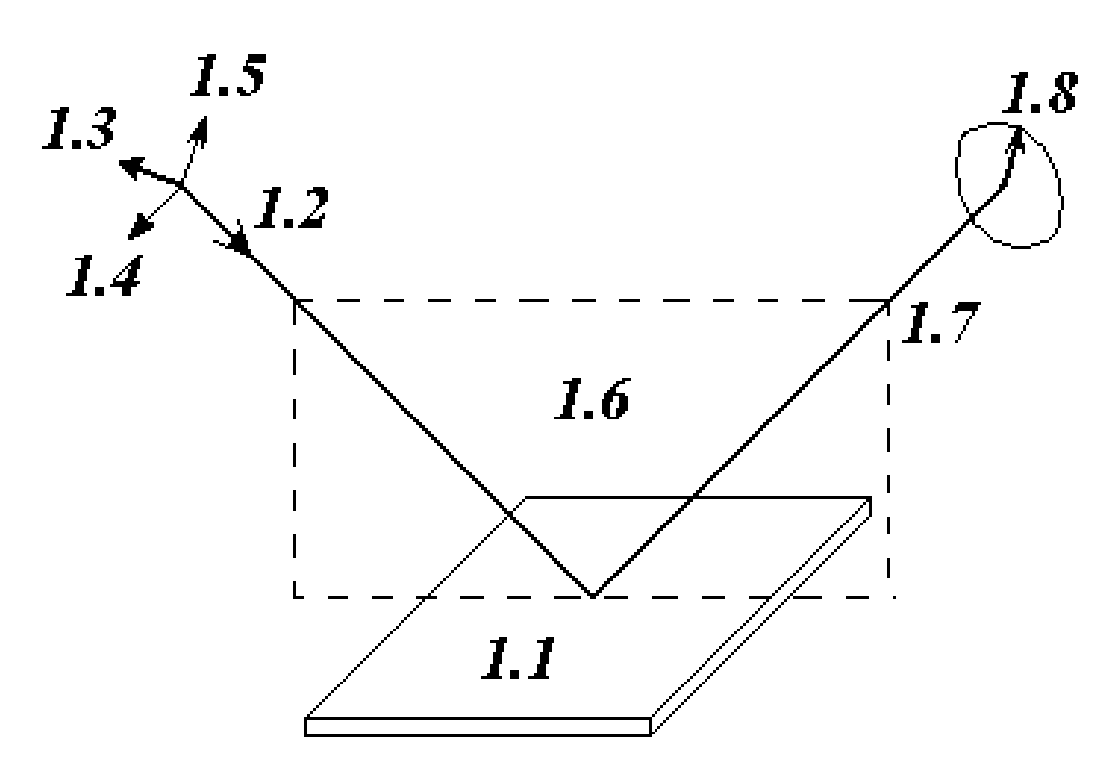

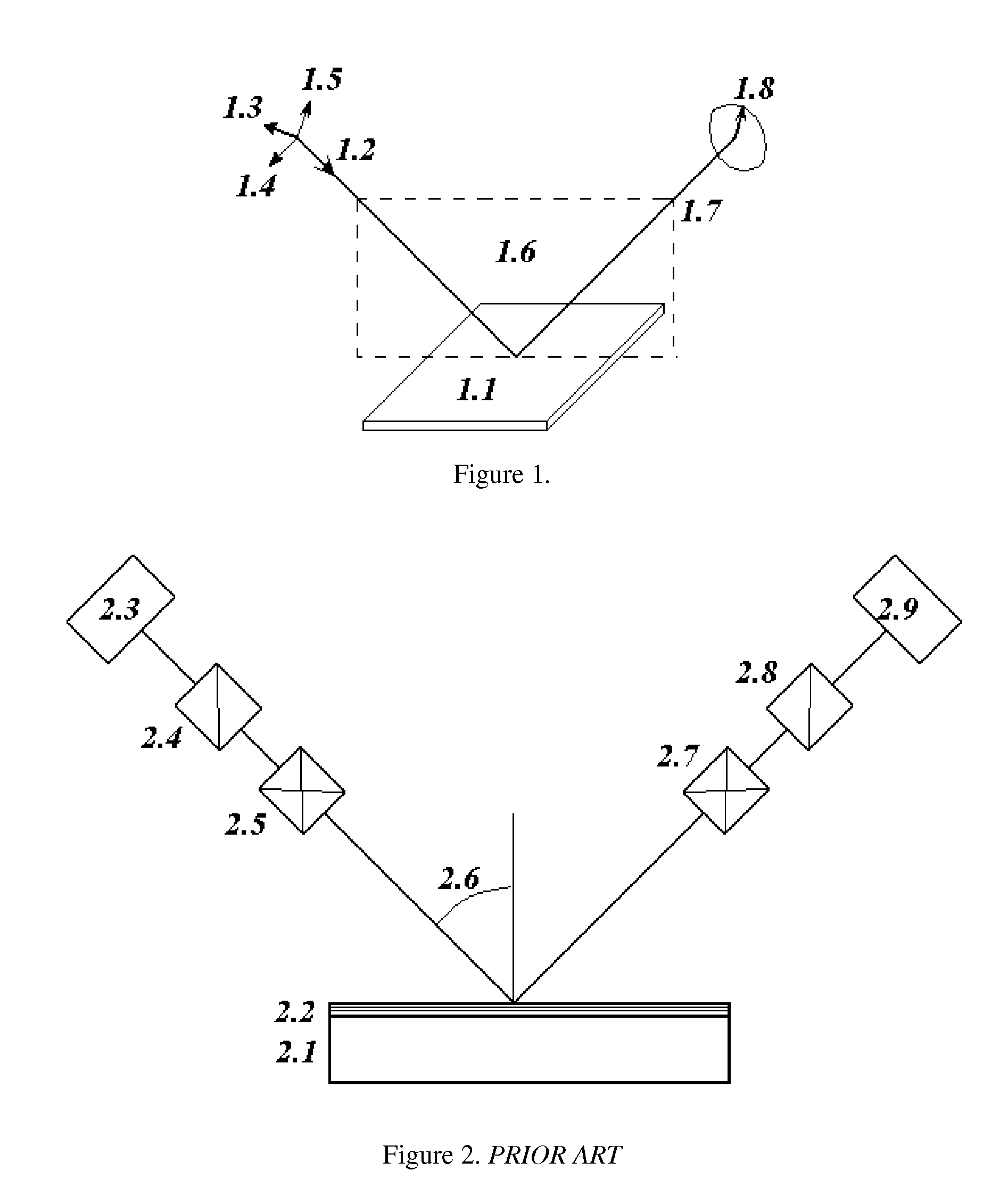

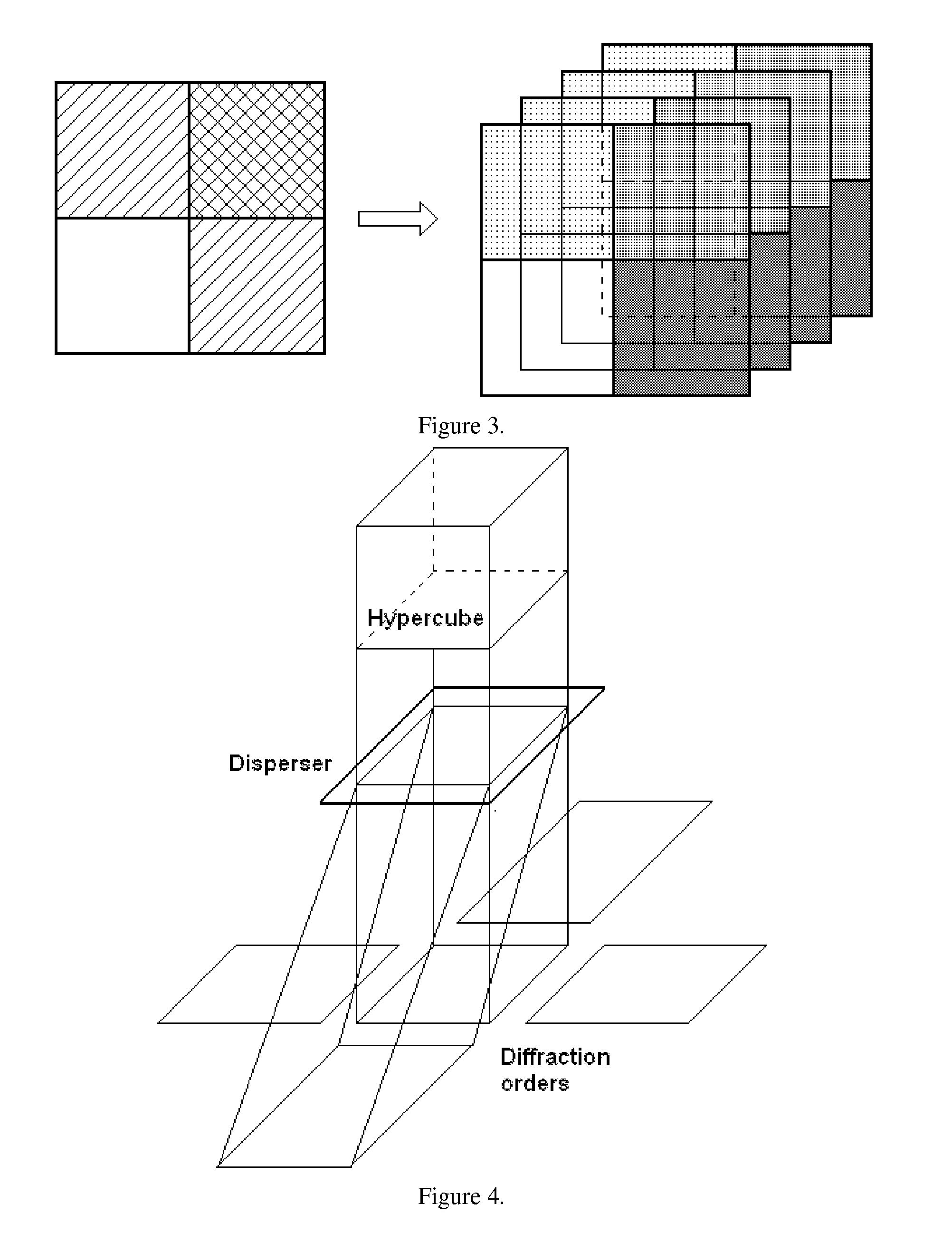

Apparatus for characterization of thin film properties and method of using the same

InactiveUS20100004773A1Increase speedVariation is detectedRadiation pyrometryPolarisation spectroscopySemiconductor structureDisplay device

This invention provides an apparatus and method for characterization of thin film structures. More particularly, the present invention provides methods and devices for fast and accurate identification of optical constants, thickness, interface roughness and stresses of a sensing film structures by spectropolarimetric imaging technique. This invention also provides the method for active in-line manufacturing diagnostics and process control. The invention is broadly applicable with most important applications being manufacturing diagnostics, process control, quality control and characterization of solar cells, flat panel displays and semiconductor structures.

Owner:PHYSTECH

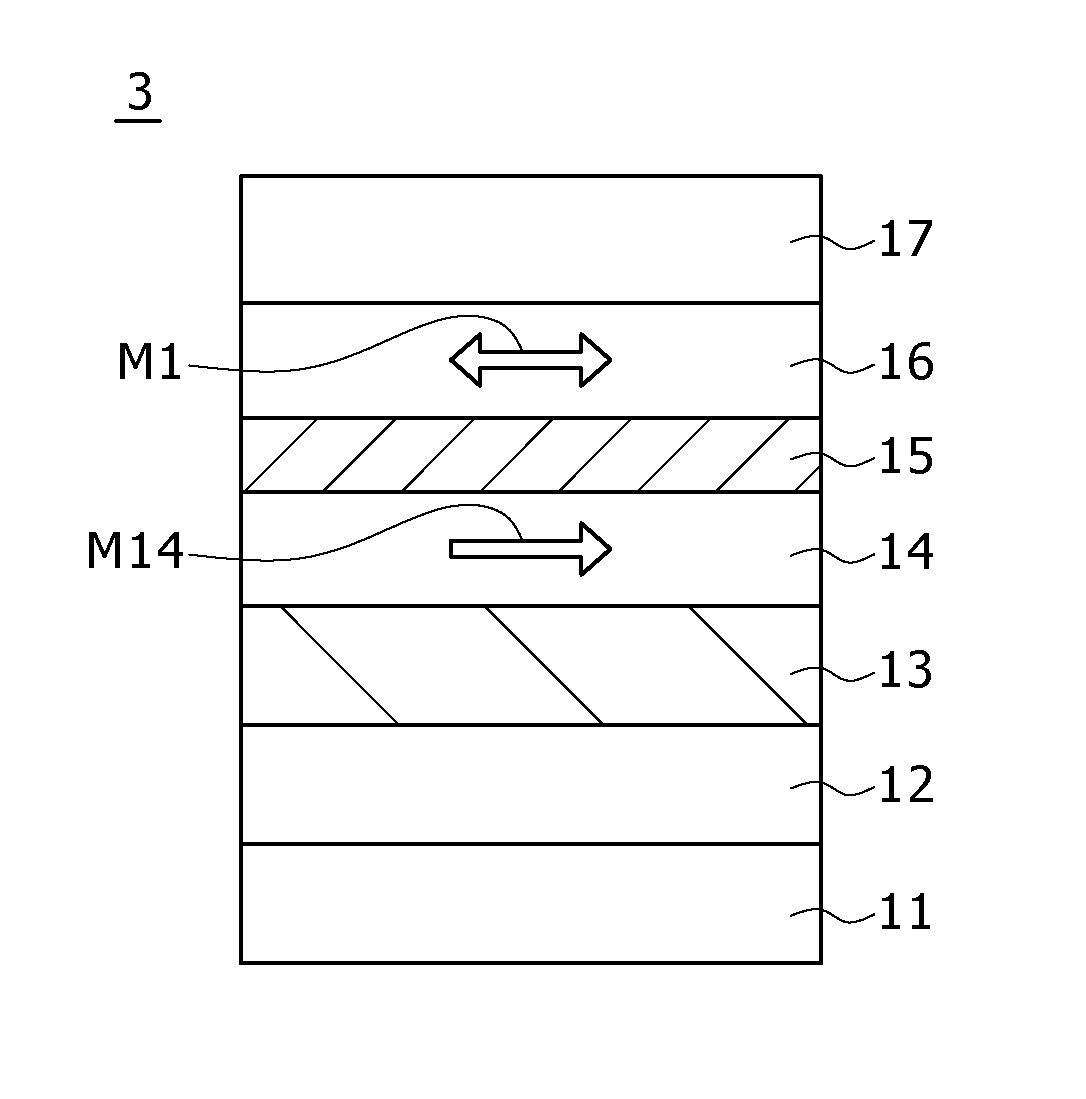

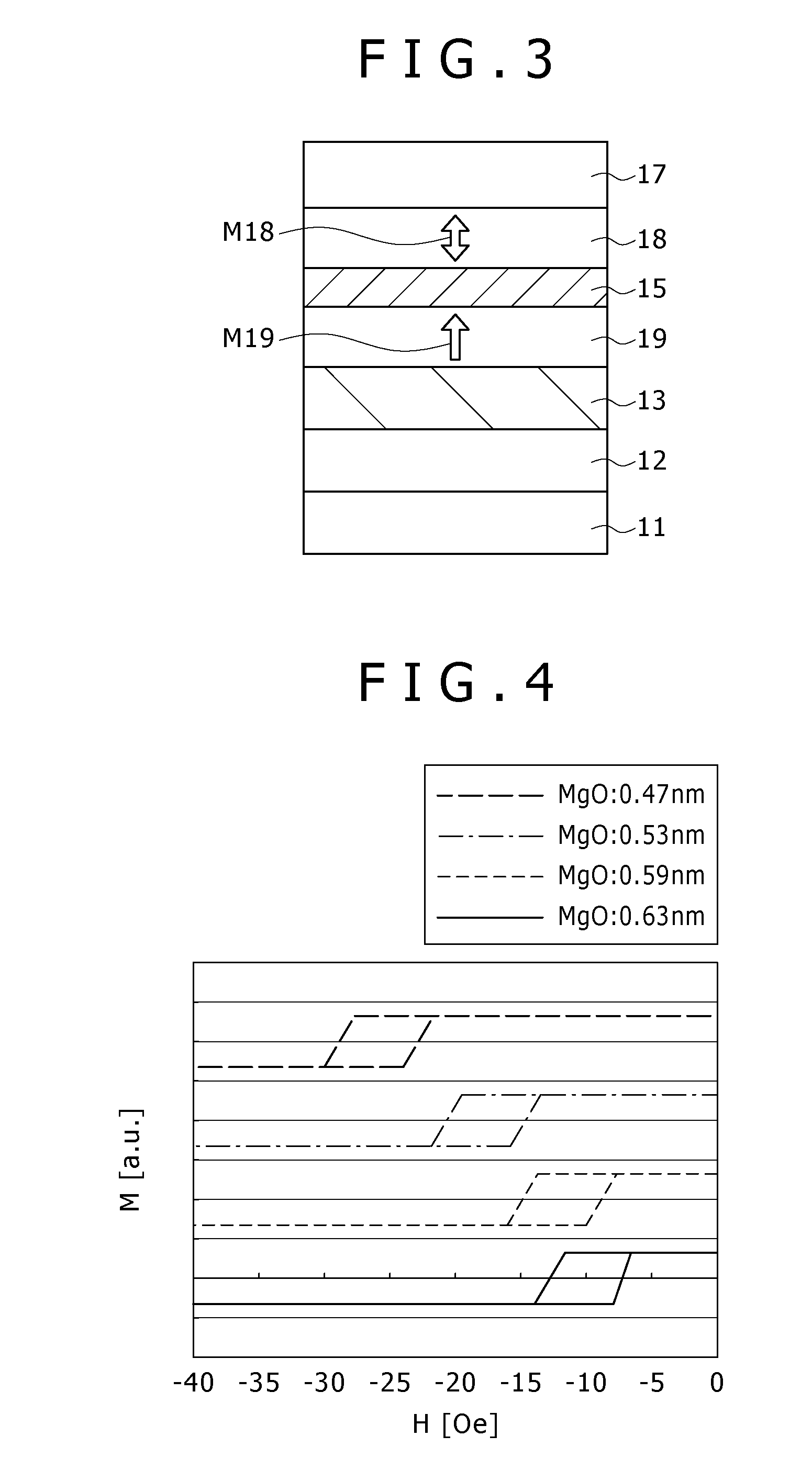

Storage element, method for manufacturing storage element, and memory

ActiveUS20110316103A1Sufficient flatnessIncrease roughnessNanomagnetismMagnetic-field-controlled resistorsPower flowSpins

Disclosed herein is a storage element, including: a storage layer configured to retain information based on a magnetization state of a magnetic material; and a magnetization pinned layer configured to be provided for the storage layer with intermediary of a tunnel barrier layer, wherein the tunnel barrier layer has a thickness not less than or equal to 0.1 nm to not more than or equal to 0.6 nm and interface roughness less than 0.5 nm, and information is stored in the storage layer through change in direction of magnetization of the storage layer by applying a current in a stacking direction and injecting a spin-polarized electron.

Owner:SONY CORP

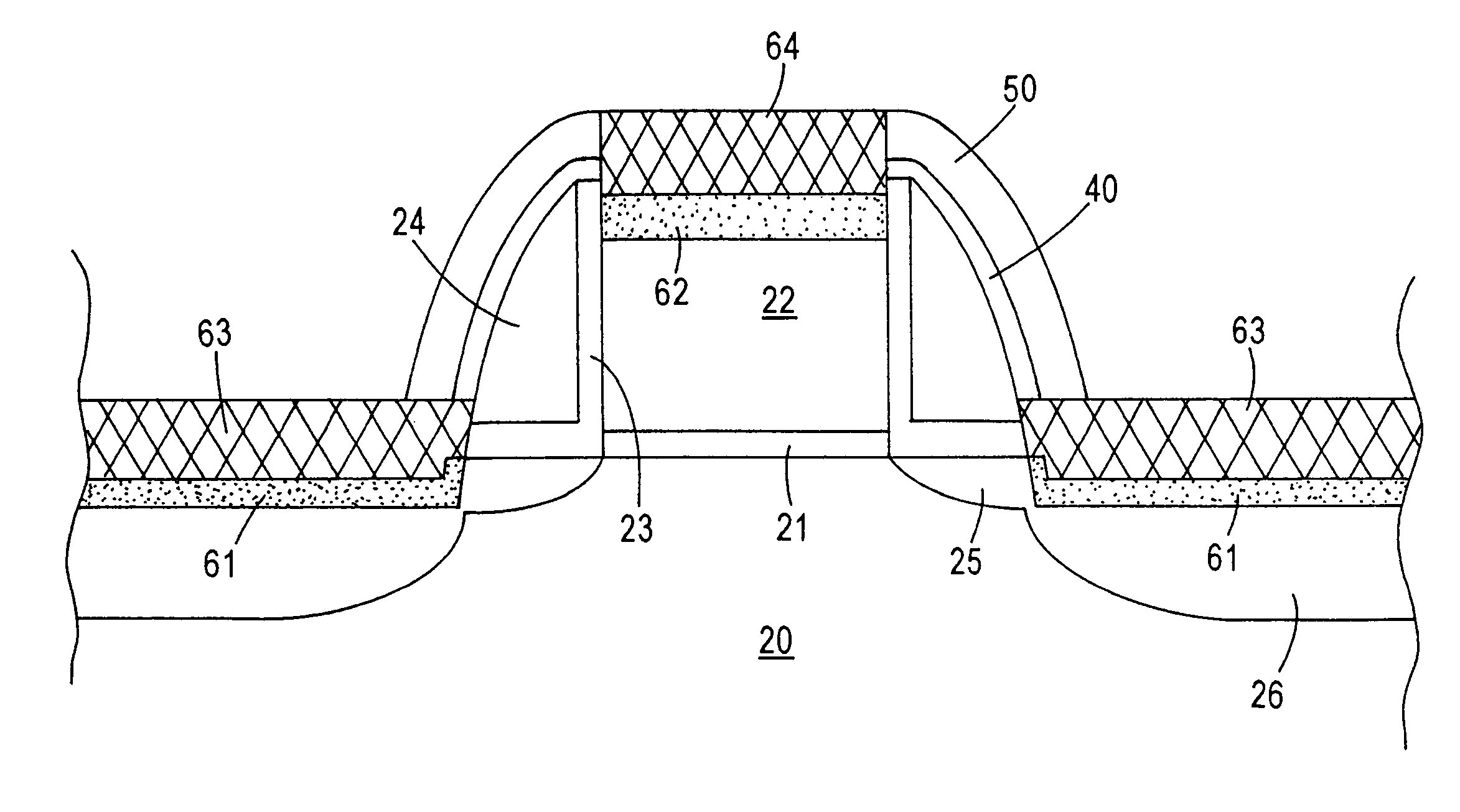

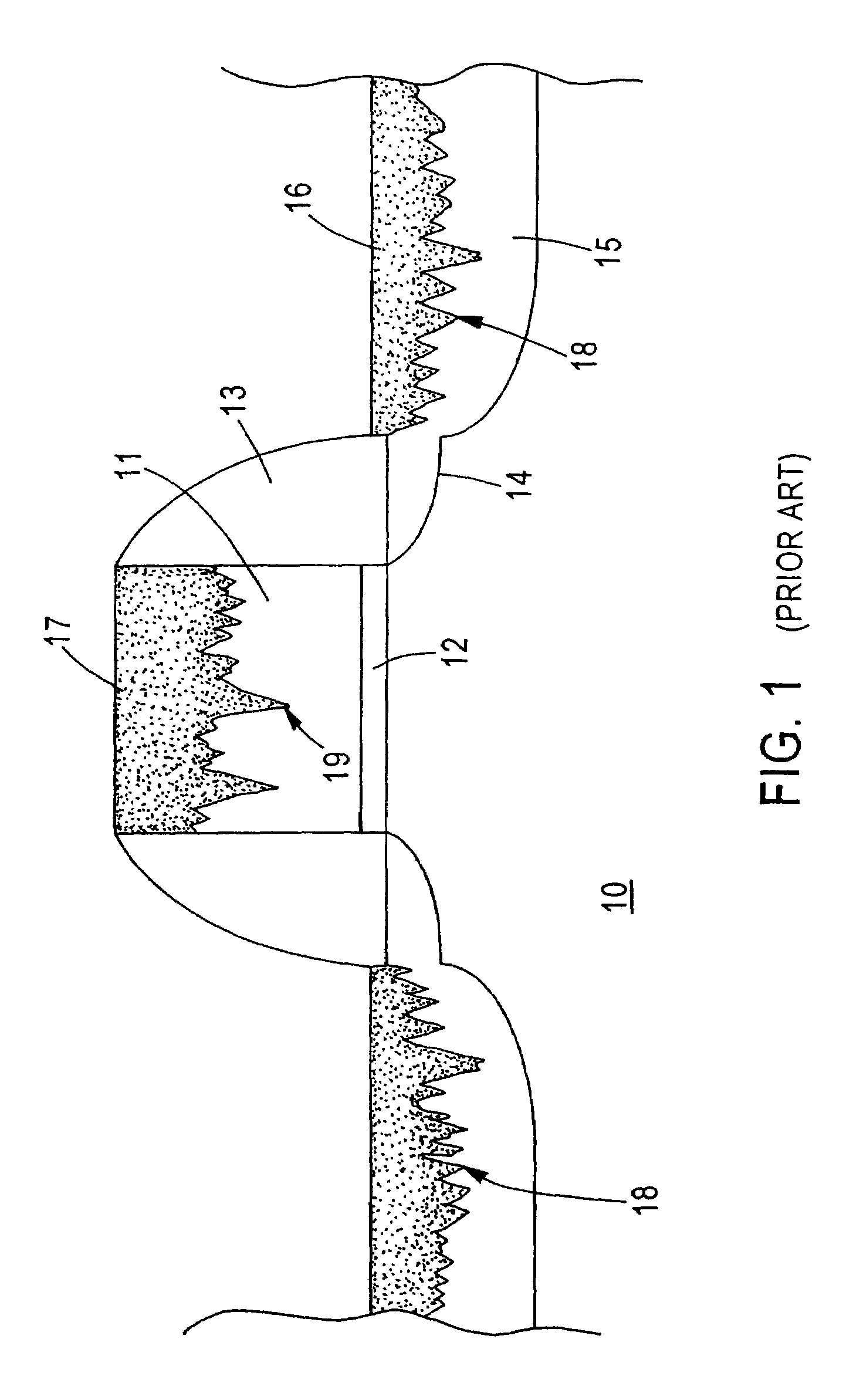

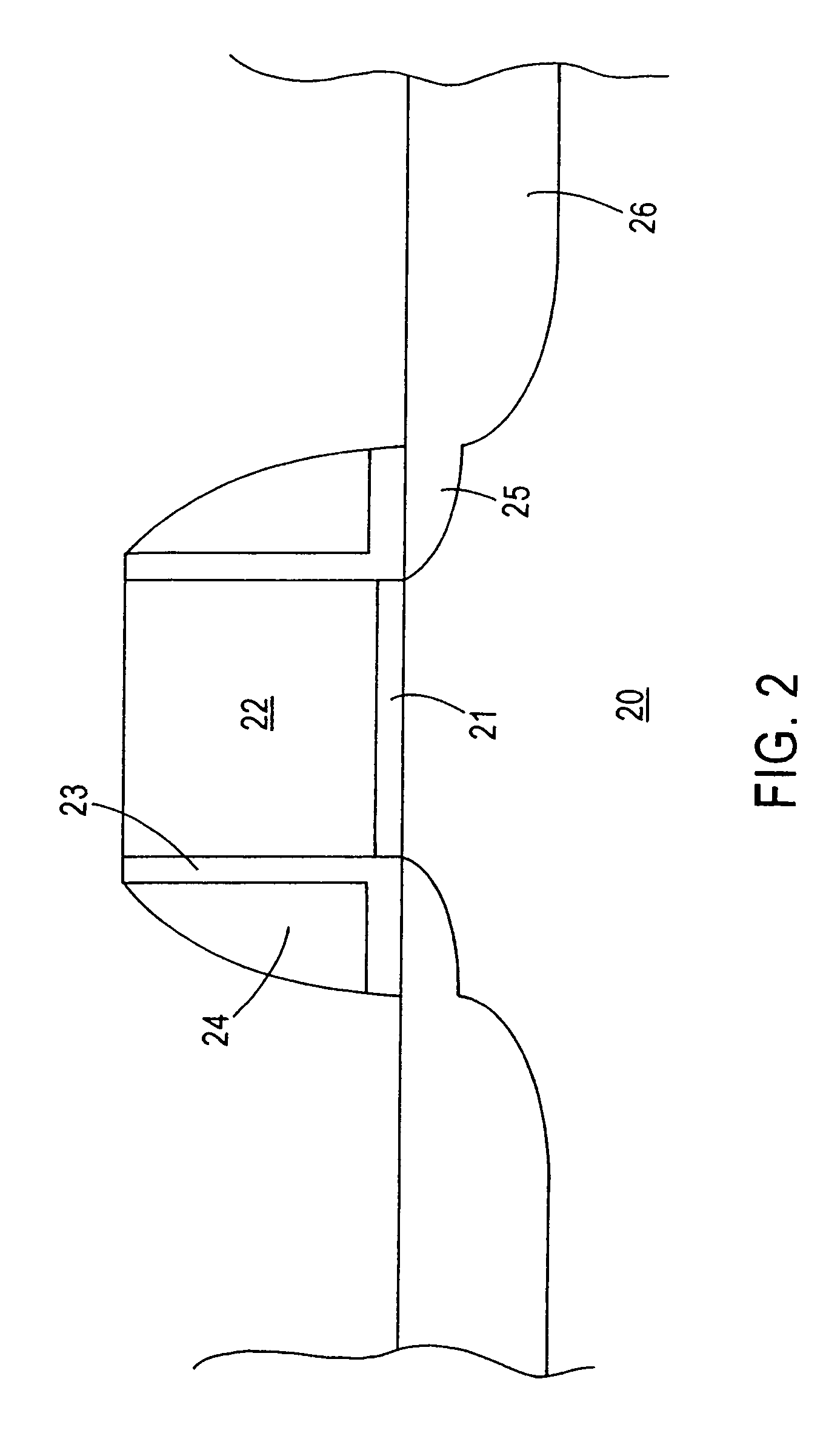

Method of manufacturing semiconductor device having nickel silicide with reduced interface roughness

InactiveUS6967160B1Reduce roughnessTransistorSemiconductor/solid-state device detailsMaterials scienceNickel silicide

Nickel silicide formation with significantly reduced interface roughness is achieved by forming a diffusion modulating layer between the underlying silicon and nickel silicide layers. Embodiments include ion implanting nitrogen into the substrate and gate electrode, depositing a thin layer of titanium or tantalum, depositing a layer of nickel, and then heating to form a diffusion modulating layer containing nitrogen at the interface between the underlying silicon and nickel silicide layers.

Owner:ADVANCED MICRO DEVICES INC

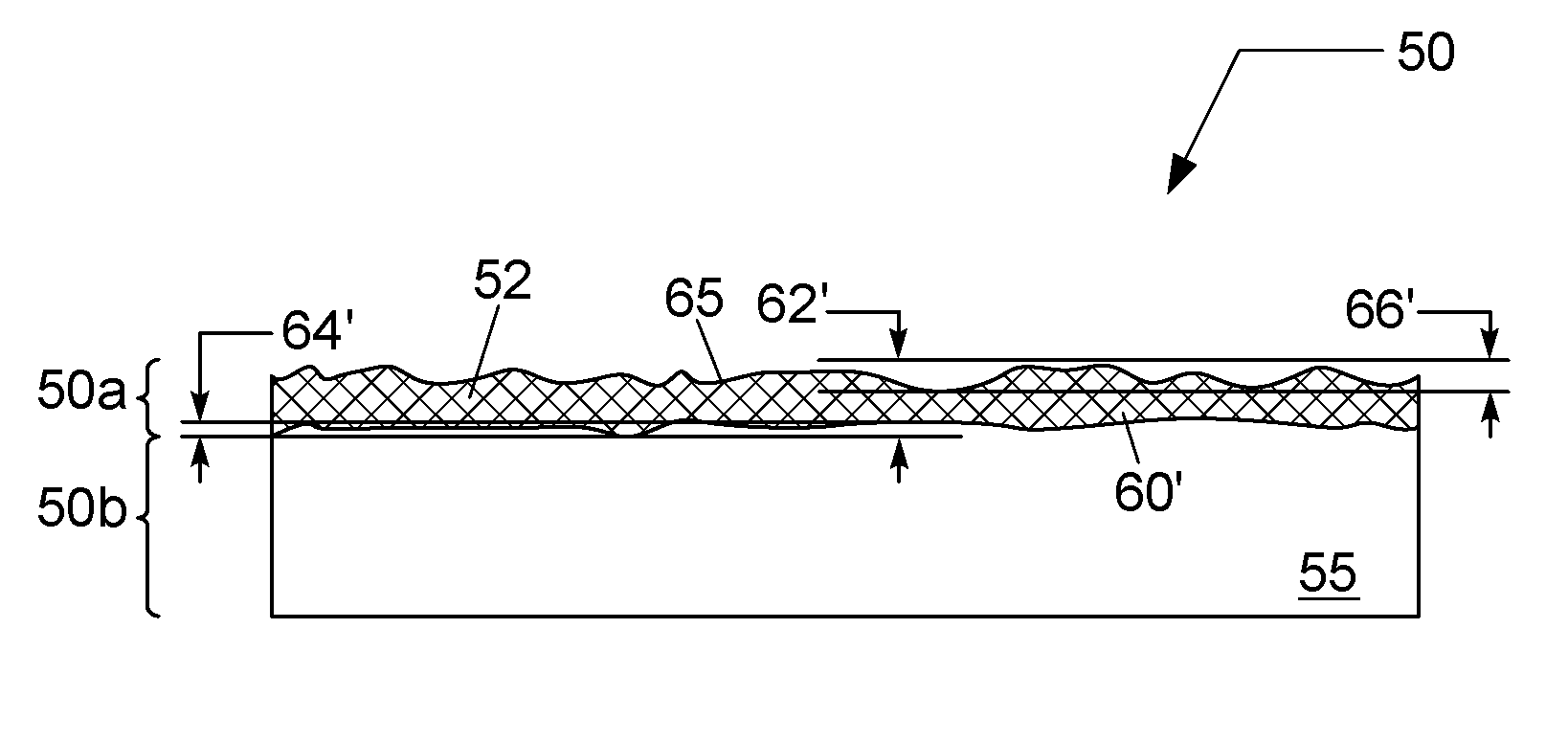

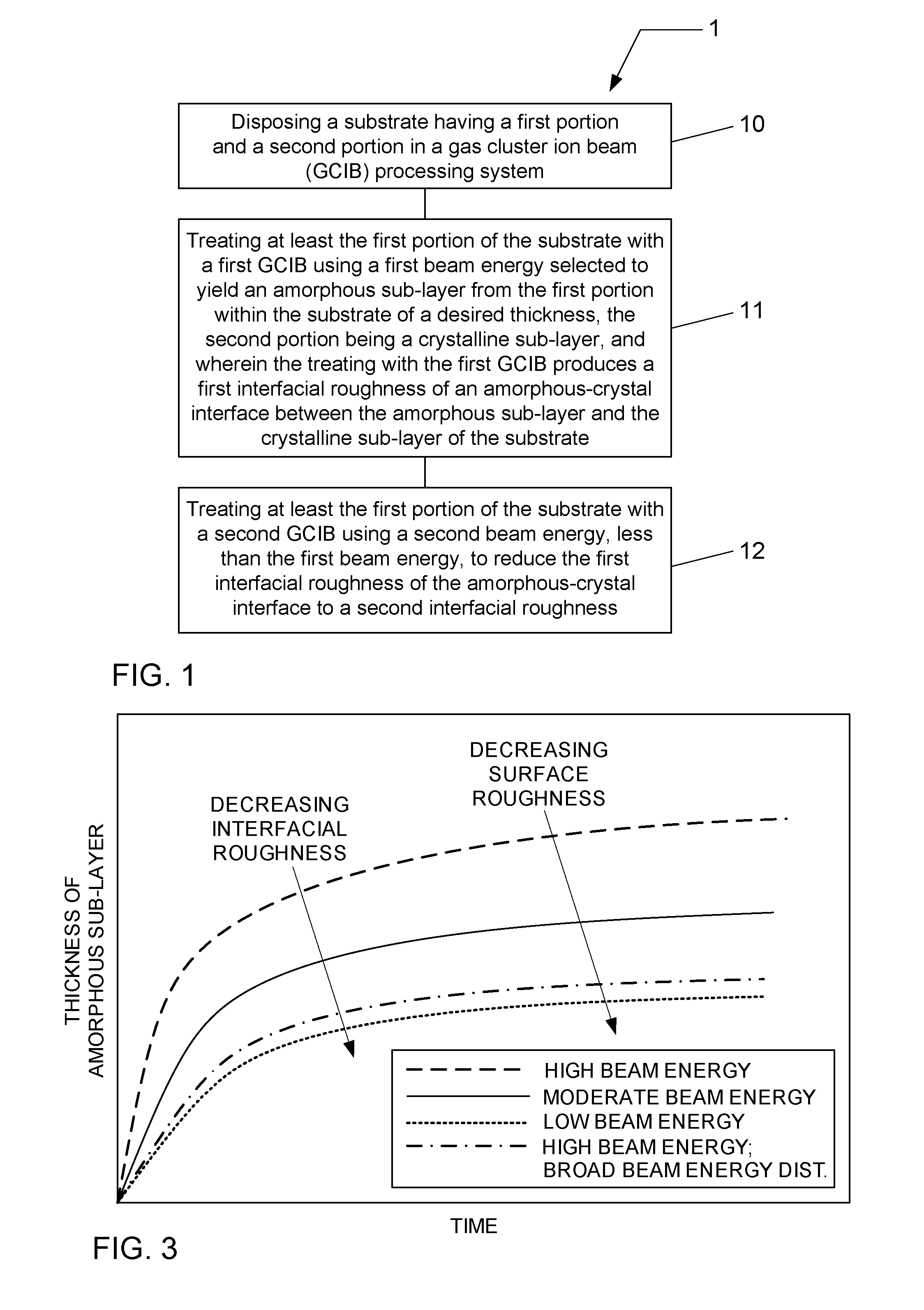

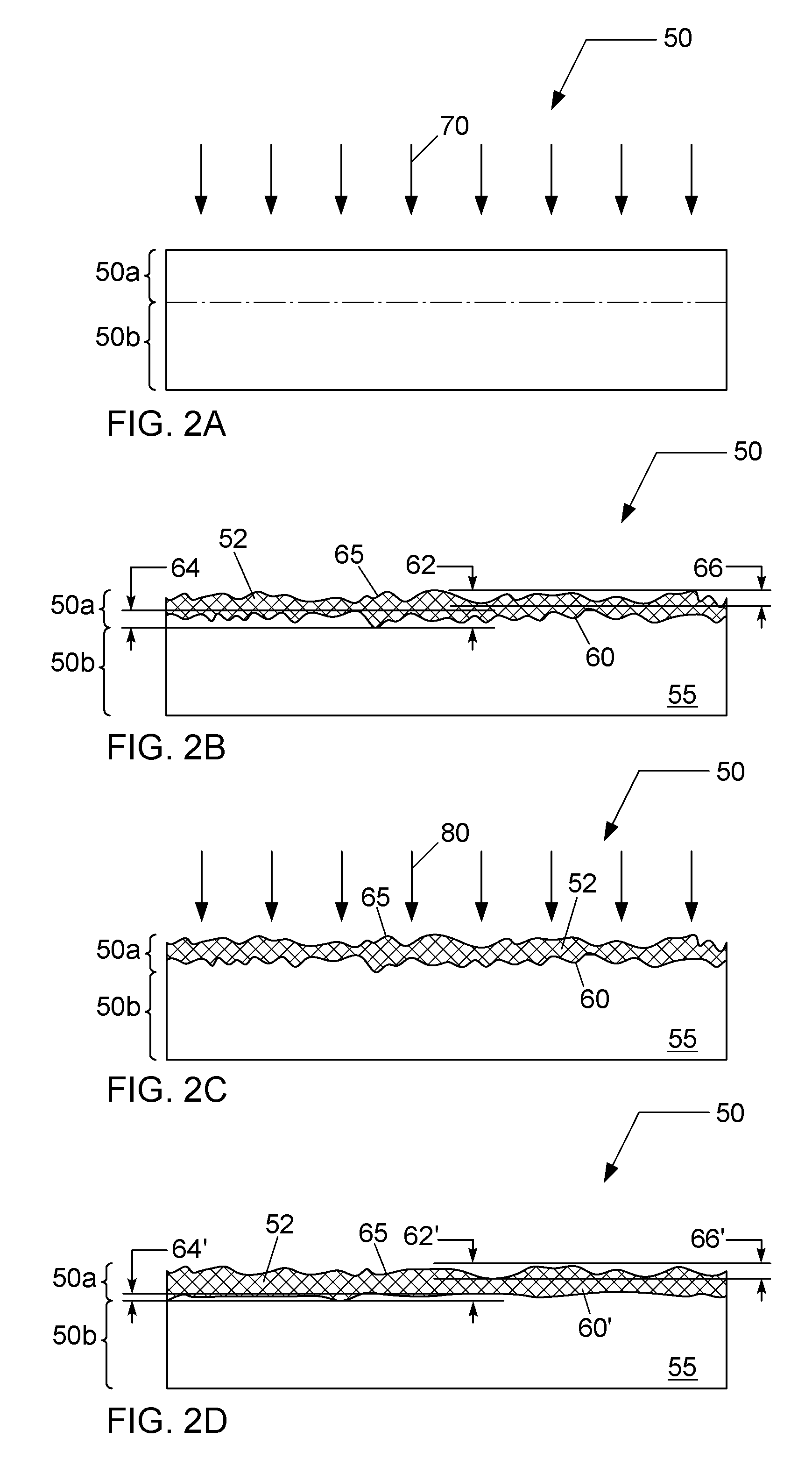

Gcib process for reducing interfacial roughness following pre-amorphization

InactiveUS20120252222A1Reduce interfacial roughnessReduce roughnessSemiconductor/solid-state device manufacturingBeam energyGas cluster ion beam

A method for amorphizing a layer on a substrate is described. In one embodiment, the method includes treating the substrate with a first gas cluster ion beam (GCIB) using a first beam energy selected to yield an amorphous sub-layer within the substrate of a desired thickness, which produces a first interfacial roughness of an amorphous-crystal interface between the amorphous sub-layer and a crystalline sub-layer of the substrate. The method further includes treating the substrate with a second GCIB using a second beam energy, less than the first beam energy, to reduce the first interfacial roughness of the amorphous-crystal interface to a second interfacial roughness.

Owner:TEL EPION

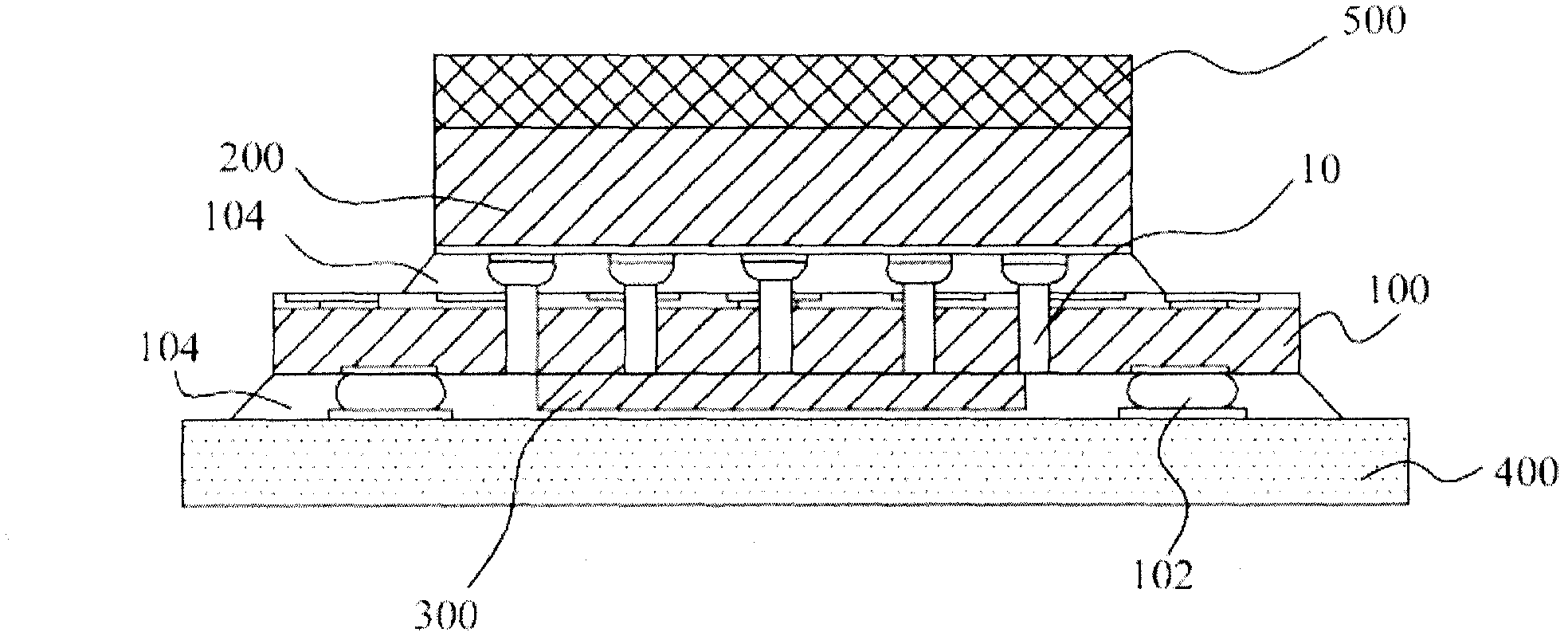

Device with through-silicon via (tsv) and method of forming the same

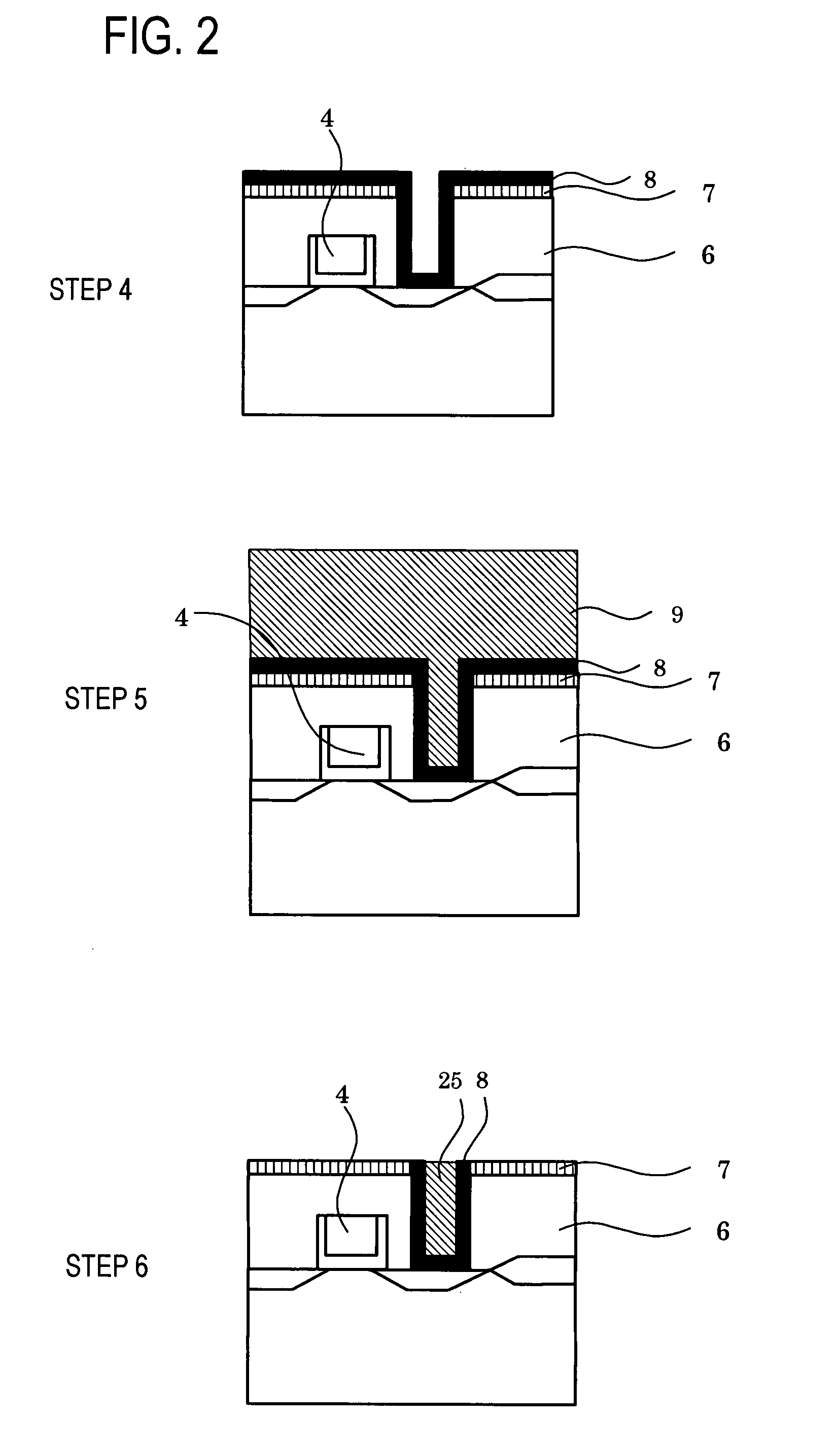

ActiveCN102420210AWith interface roughnessSemiconductor/solid-state device detailsSolid-state devicesInsulation layerThrough-silicon via

A device with through-silicon via (TSV) and a method of forming the same includes the formation of an opening in a silicon substrate, the formation of a first insulation layer on the sidewalls and bottom of the opening, the formation of a second insulation layer on the sidewalls and bottom of the opening. A first interface between the first insulation layer and the silicon substrate has an interface roughness with a peak-to-valley height less than 5 nm. A second interface between the second insulation layer and the conductive layer has an interface roughness with a peak-to-valley height less than 5 nm.

Owner:TAIWAN SEMICON MFG CO LTD

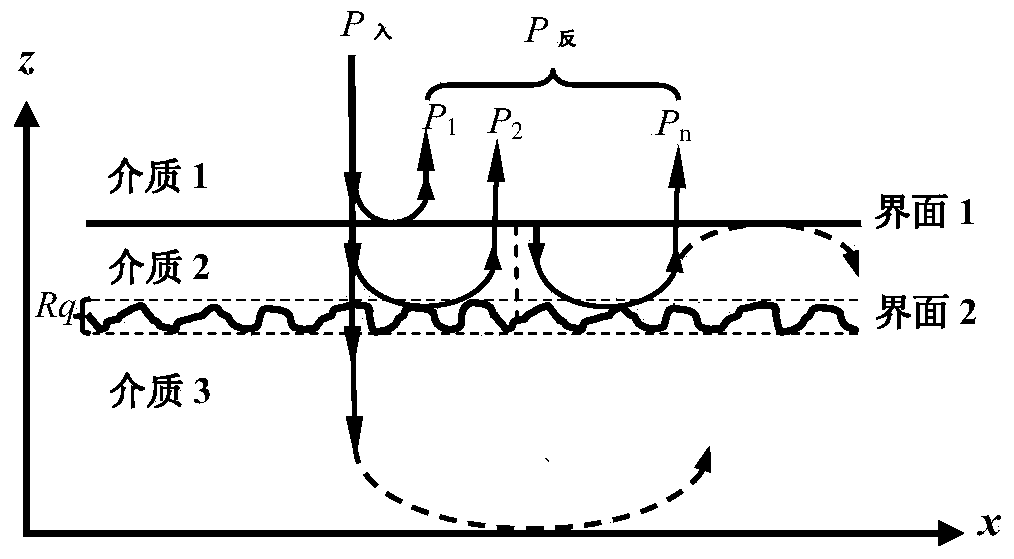

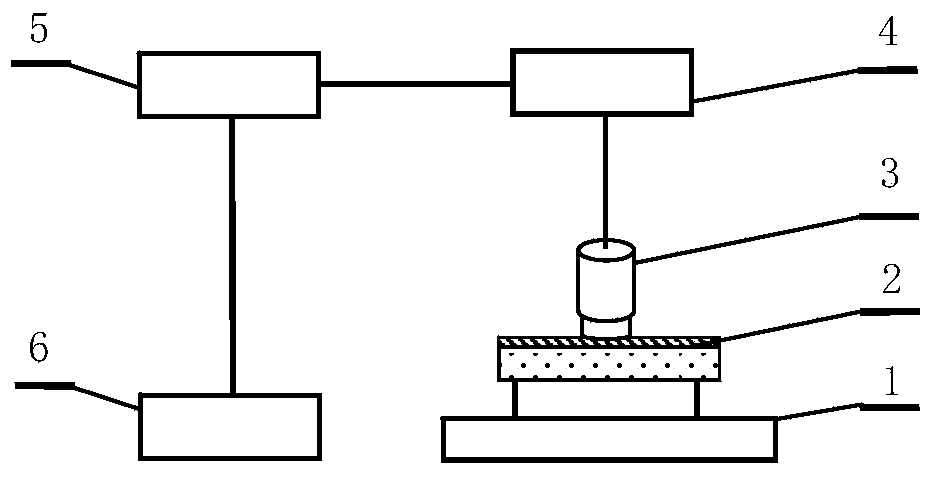

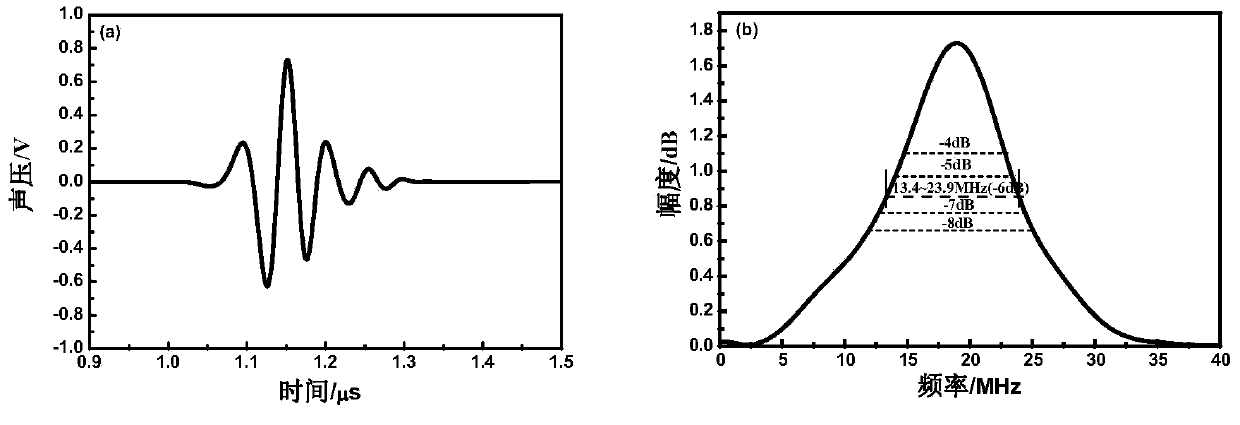

Method for measuring coating thickness and interfacial roughness simultaneously by ultrasonic

ActiveCN104197872AAccurate measurementEasy and flexible measurementUsing subsonic/sonic/ultrasonic vibration meansSound pressureNondestructive testing

The invention discloses a method for measuring coating thickness and interfacial roughness simultaneously by ultrasonic and belongs to the technical field of ultrasonic nondestructive test and evaluation for materials. The method adopts an ultrasonic pulse echo detection system which comprises a sample table, an interfacial roughened coating sample, a delay block probe, a flow detector, a digital oscilloscope and a computer. Aiming to solve the difficult problem about measuring thickness and roughness of the nondestructive characterization interfacial roughened coating, the method includes deriving a sound pressure reflection coefficient amplitude spectrum / r(f;rq,d) / of the interfacial roughened coating structure, performing correlation operation to theoretical and experimental sound pressure reflection coefficient amplitude spectrums of different frequency bandwidth to obtain thickness di and roughness Rqi of the coating corresponding to the maximum correlation coefficient eta<max>(Rq,d) of each bandwidth, averaging thickness and roughness measured within different frequency windows to obtain mean d and mean Rq which are respectively the coating thickness and the interfacial roughness needed to solve. The method fills a gap in the coating thickness and roughness nondestructive characterization methods.

Owner:DALIAN UNIV OF TECH

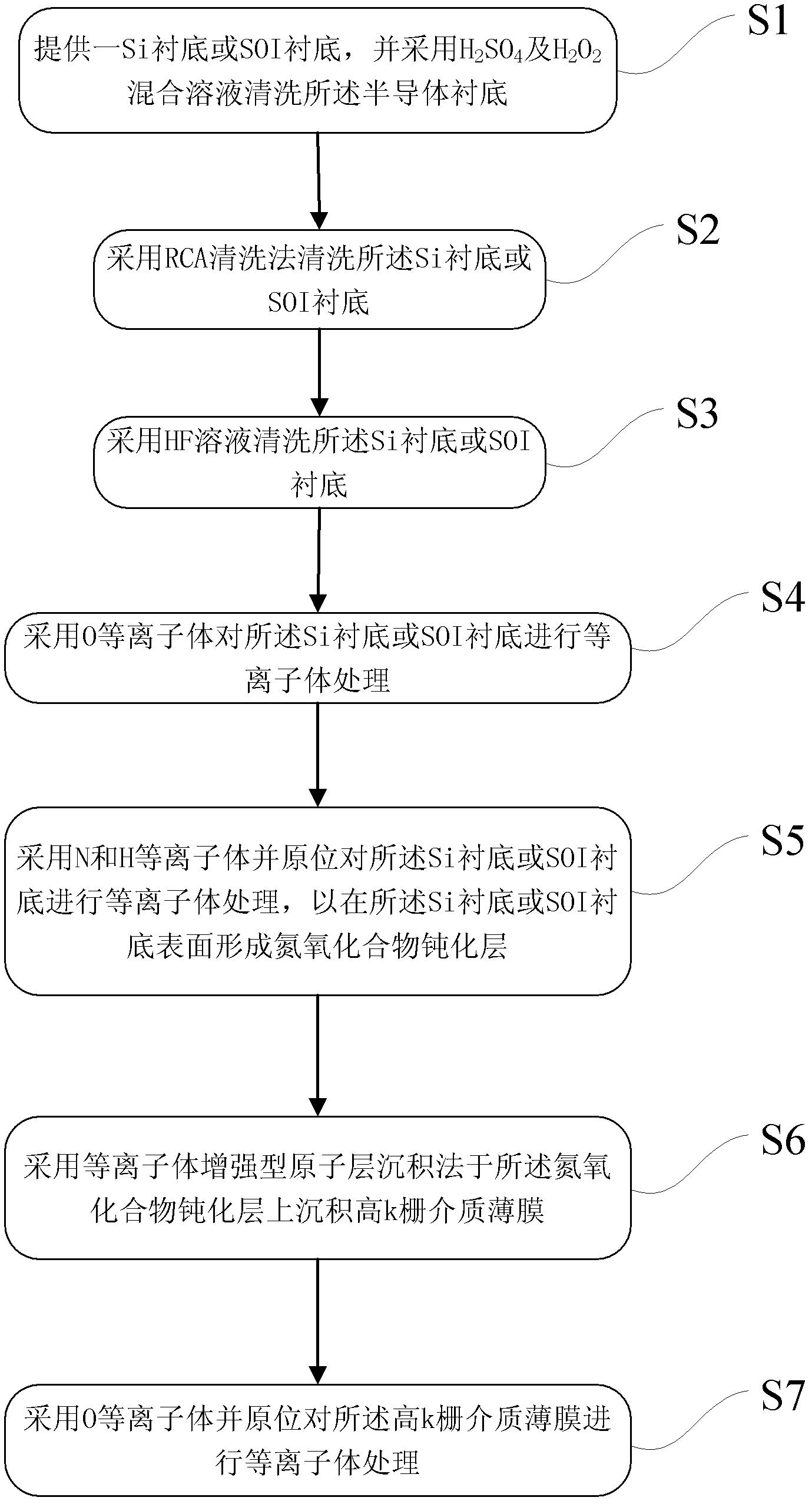

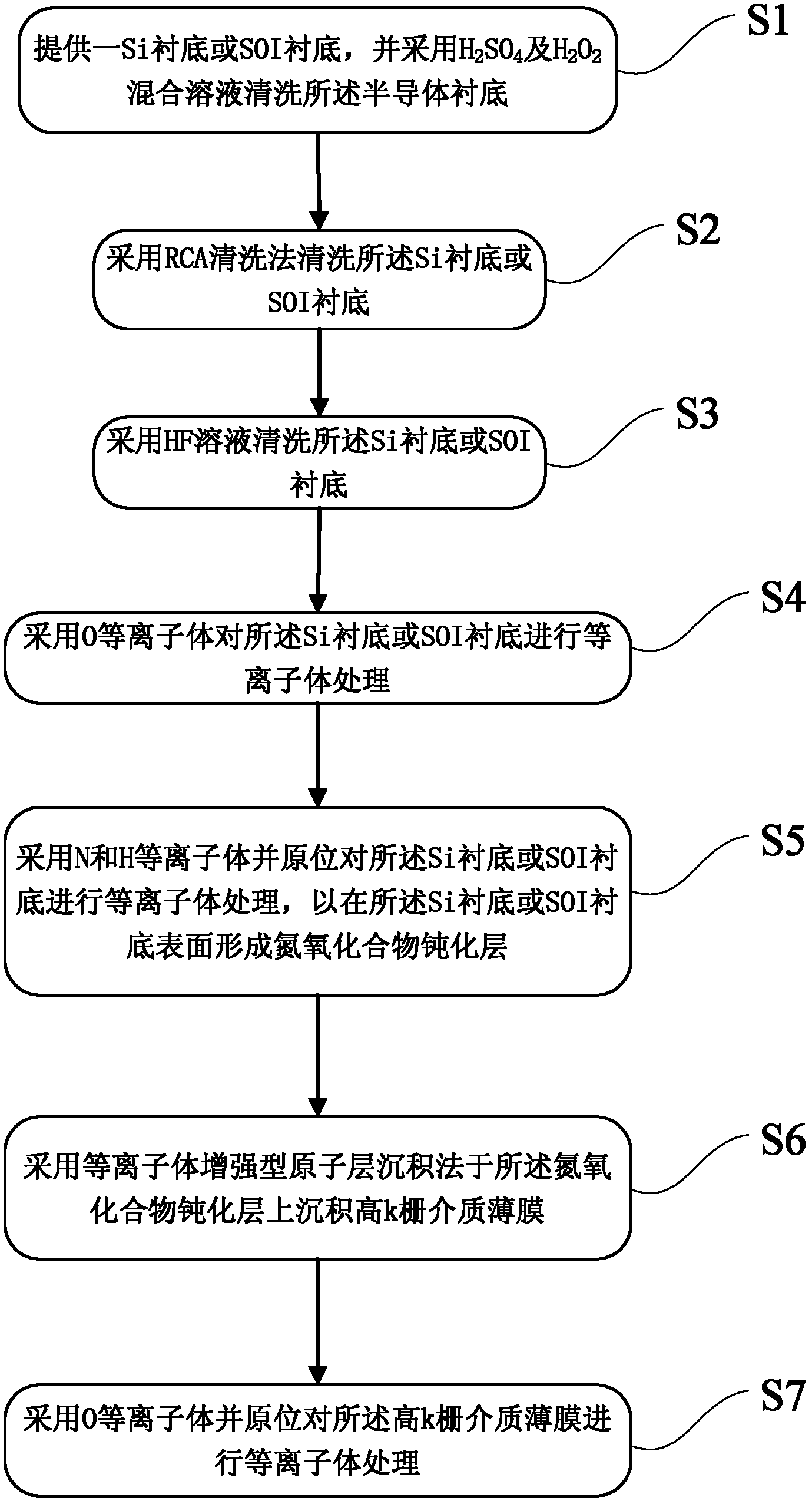

Preparation method for high-K medium film

InactiveCN102592974AReduced oxygen vacanciesImprove puritySemiconductor/solid-state device manufacturingHydrogen fluorideOxygen vacancy

The invention provides a preparation method for a high-K medium film. Organics on the surface of a sample can be removed and the purity of the surface of a substrate can be improved by adding the step of washing with H2SO4 and H2O2 before adopting a standard RCA washing method. The thickness of an interface layer of the film can be effectively reduced by removing a surface oxide layer by using hydrogen fluoride (HF) again after adopting the standard RCA washing method. A layer of very thin oxynitride passivation layer grows between the high-K medium film and Si by a plasma atomic layer deposition method and the technology of treating the surface of the Si through in-situ O2 and NH3 plasmas. The high-K medium film passivation layer can inhibit the growth of the interface layer. The high-K medium film is grown in a plasma growing way and oxygen plasma post treatment is performed on the high-K medium film in situ so as to reduce oxygen vacancy in the film. The thickness of an interface buffering layer and the roughness of the interface are reduced by the method, element diffusion between the substrate and the film is inhibited, and equivalent grid oxygen thickness is reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Semiconductor substrate and field-effect transistor, and manufacturing method for same

InactiveUS7405142B2Reduce threading dislocation densityReduce surface roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesSurface roughnessCritical thickness

Owner:SUMCO CORP

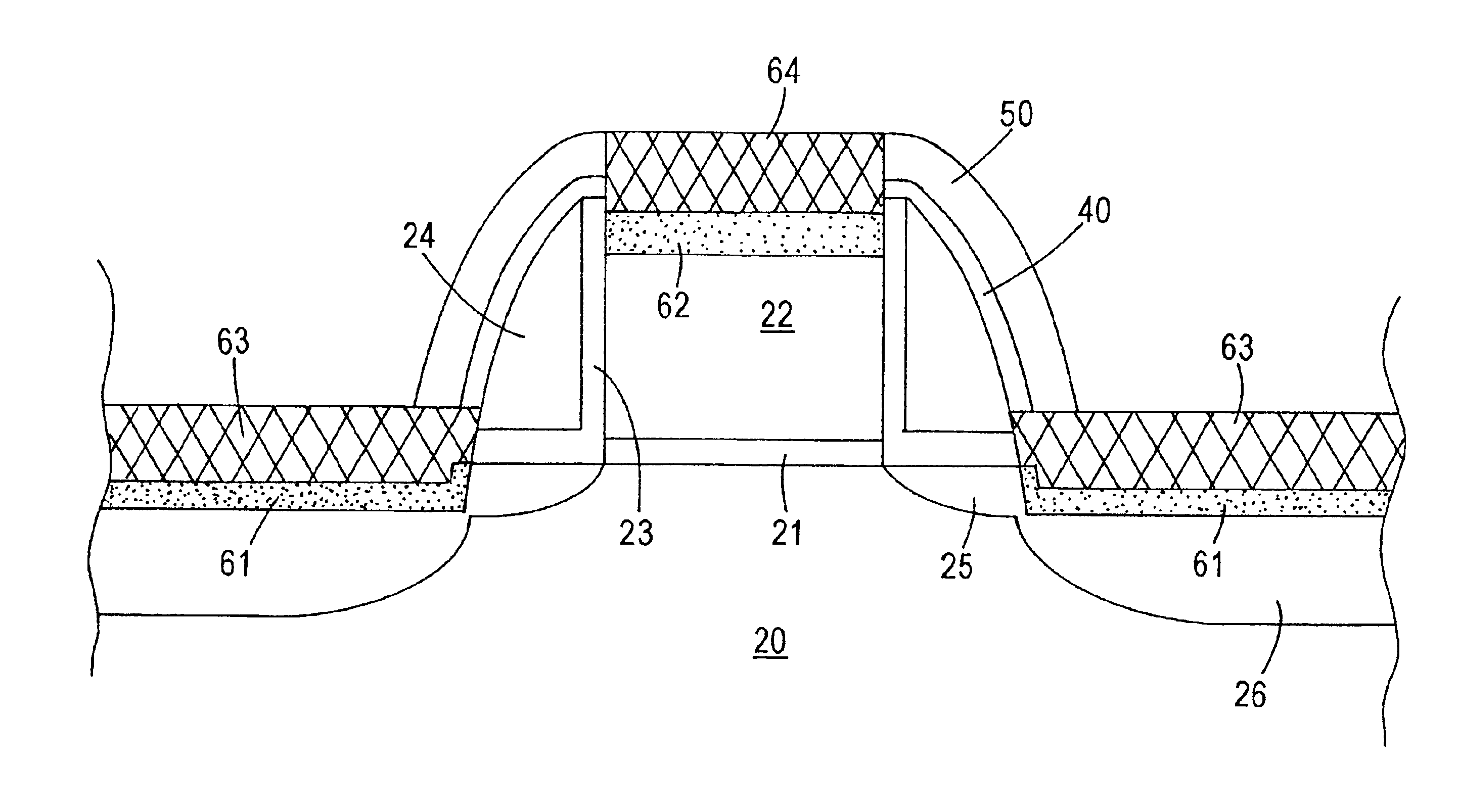

Roughness reducing film at interface, materials for forming roughness reducing film at interface, wiring layer and semiconductor device using the same, and method for manufacturing semiconductor device

ActiveUS20070232075A1Small electric power consumptionHigh TDDB resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductorElectric power

Techniques for obtaining a wiring layer with a high TDDB resistance and little leakage current, and accordingly, for manufacturing a highly reliable semiconductor device with a small electric power consumption are provided, in which an interfacial roughness reducing film is formed which is in contact with an insulator film and also in contact with a wiring line on the other side surface thereof, and has an interfacial roughness between the wiring line and the interfacial roughness reducing film smaller than that between the insulator film and the interfacial roughness reducing film.

Owner:FUJITSU LTD

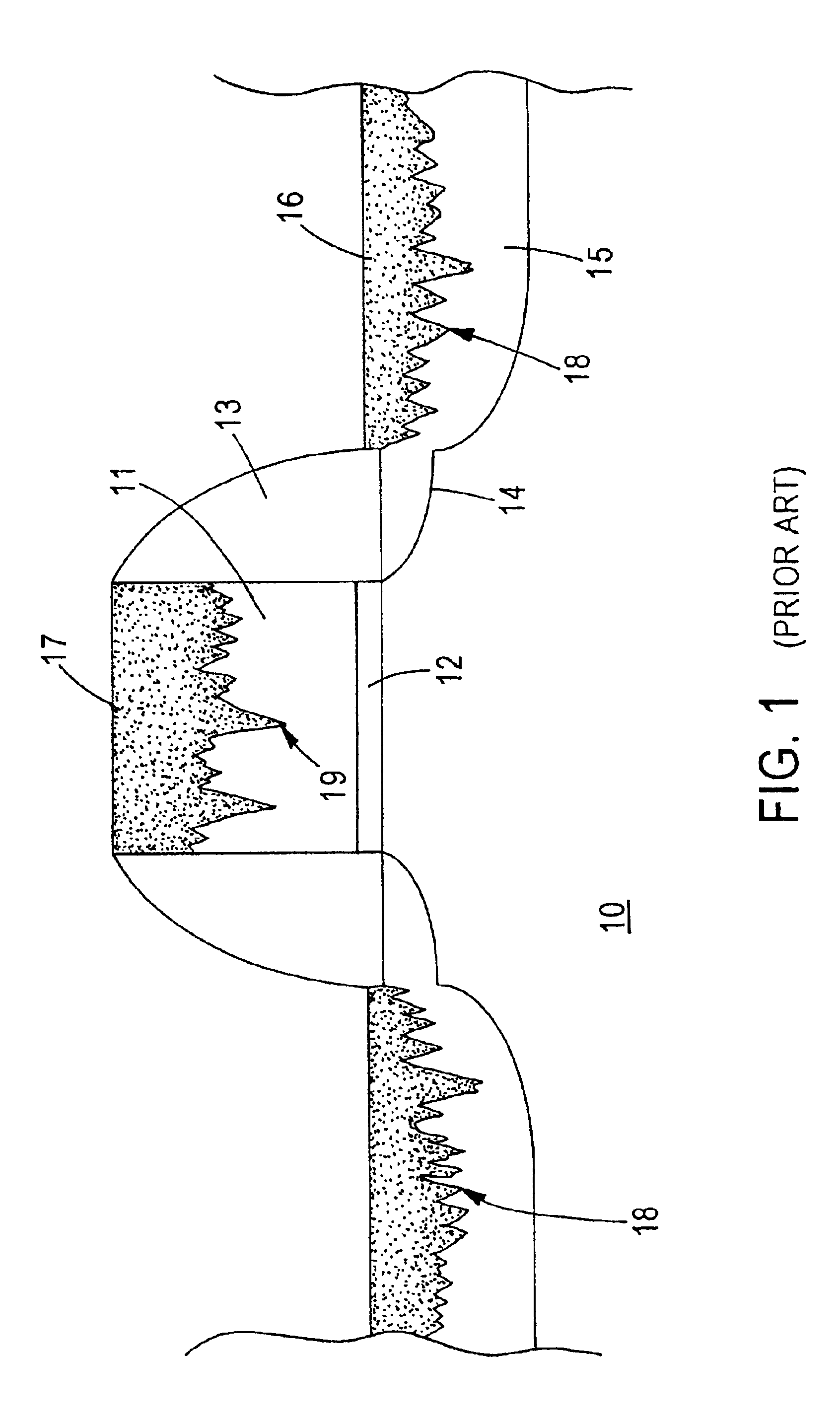

Nickel silicide with reduced interface roughness

InactiveUS6873051B1Reduce roughnessTransistorSemiconductor/solid-state device detailsThin layerNitrogen

Nickel silicide formation with significantly reduced interface roughness is achieved by forming a diffusion modulating layer between the underlying silicon and nickel silicide layers. Embodiments include ion implanting nitrogen into the substrate and gate electrode, depositing a thin layer of titanium or tantalum, depositing a layer of nickel, and then heating to form a diffusion modulating layer containing nitrogen at the interface between the underlying silicon and nickel silicide layers.

Owner:ADVANCED MICRO DEVICES INC

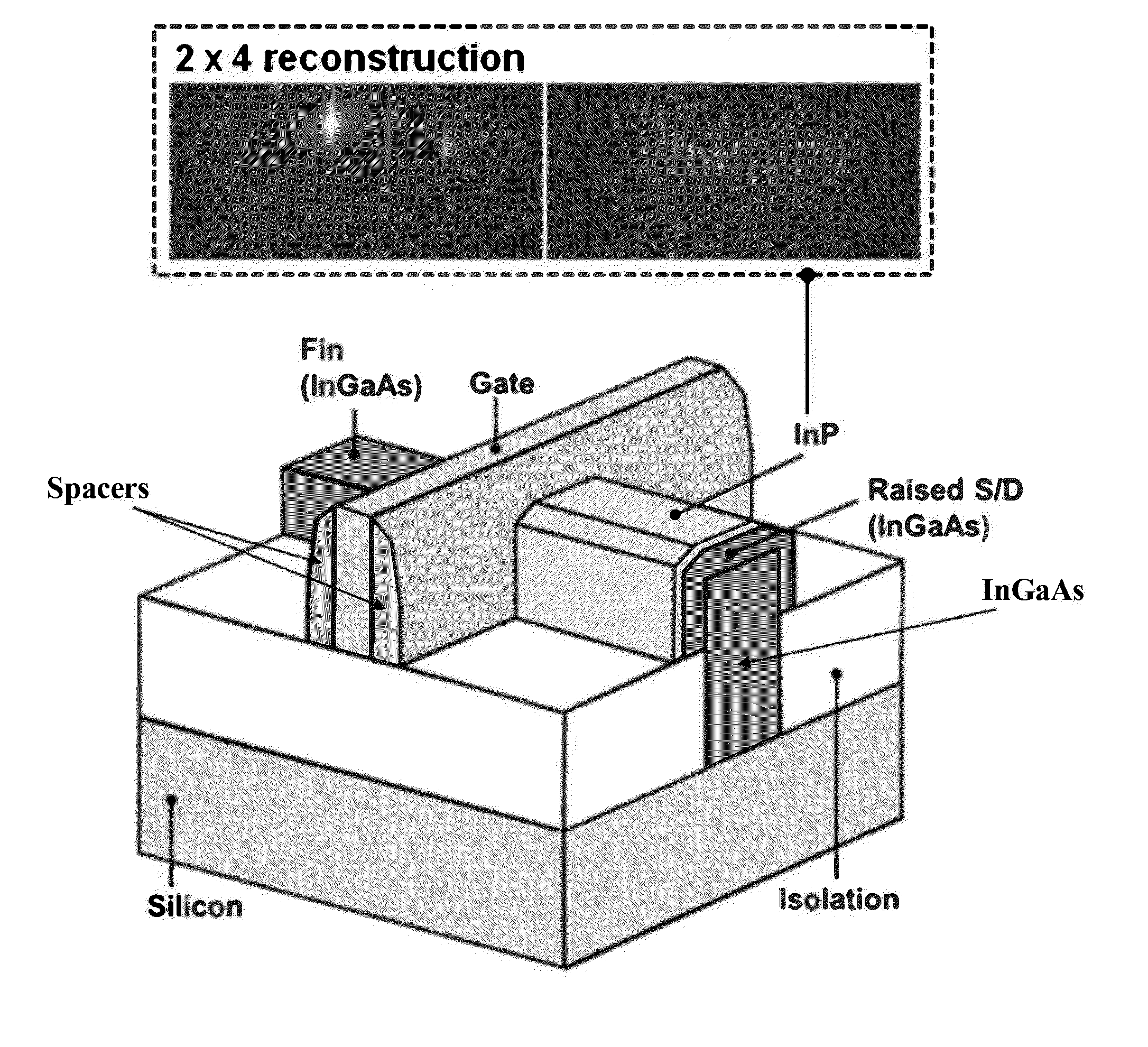

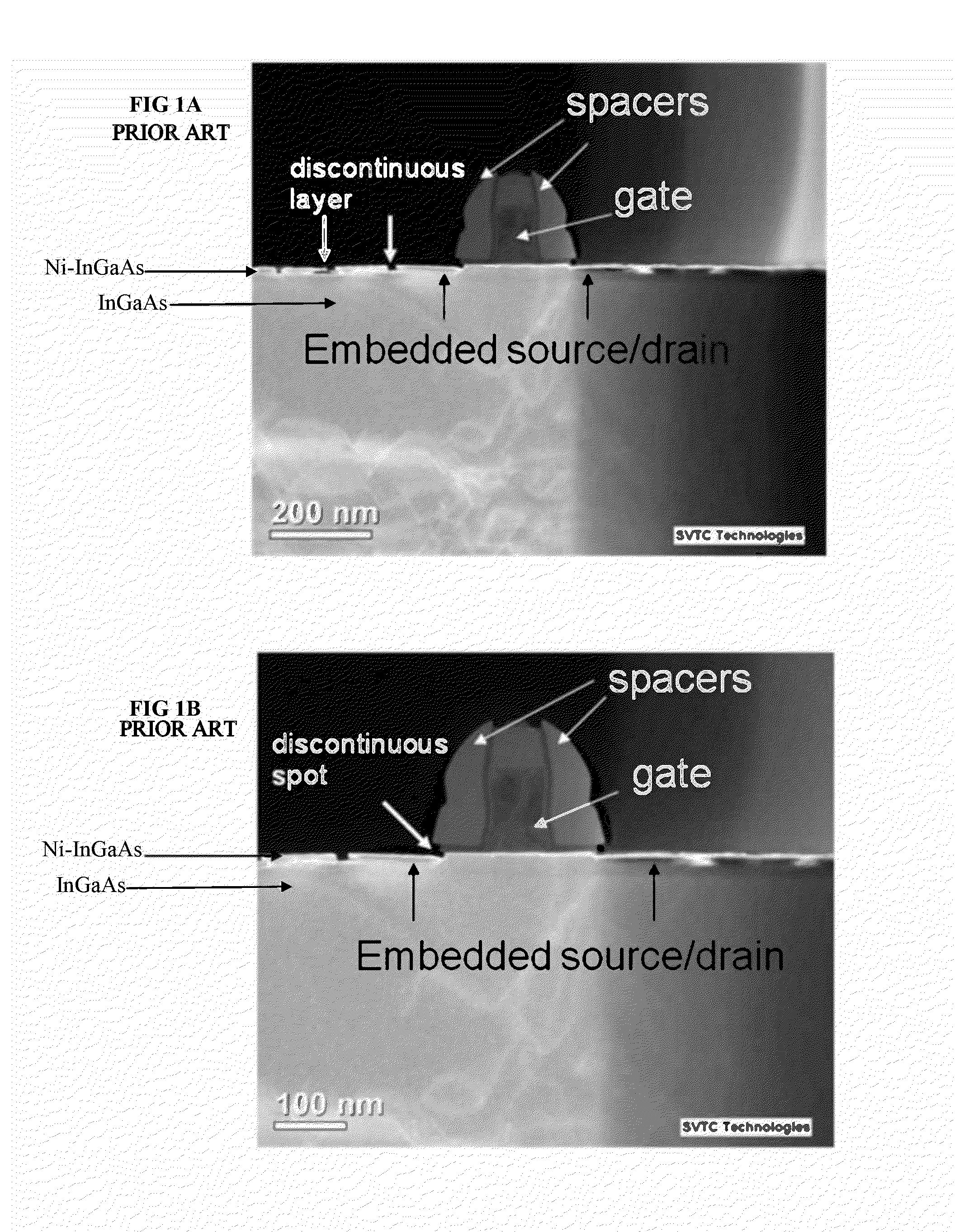

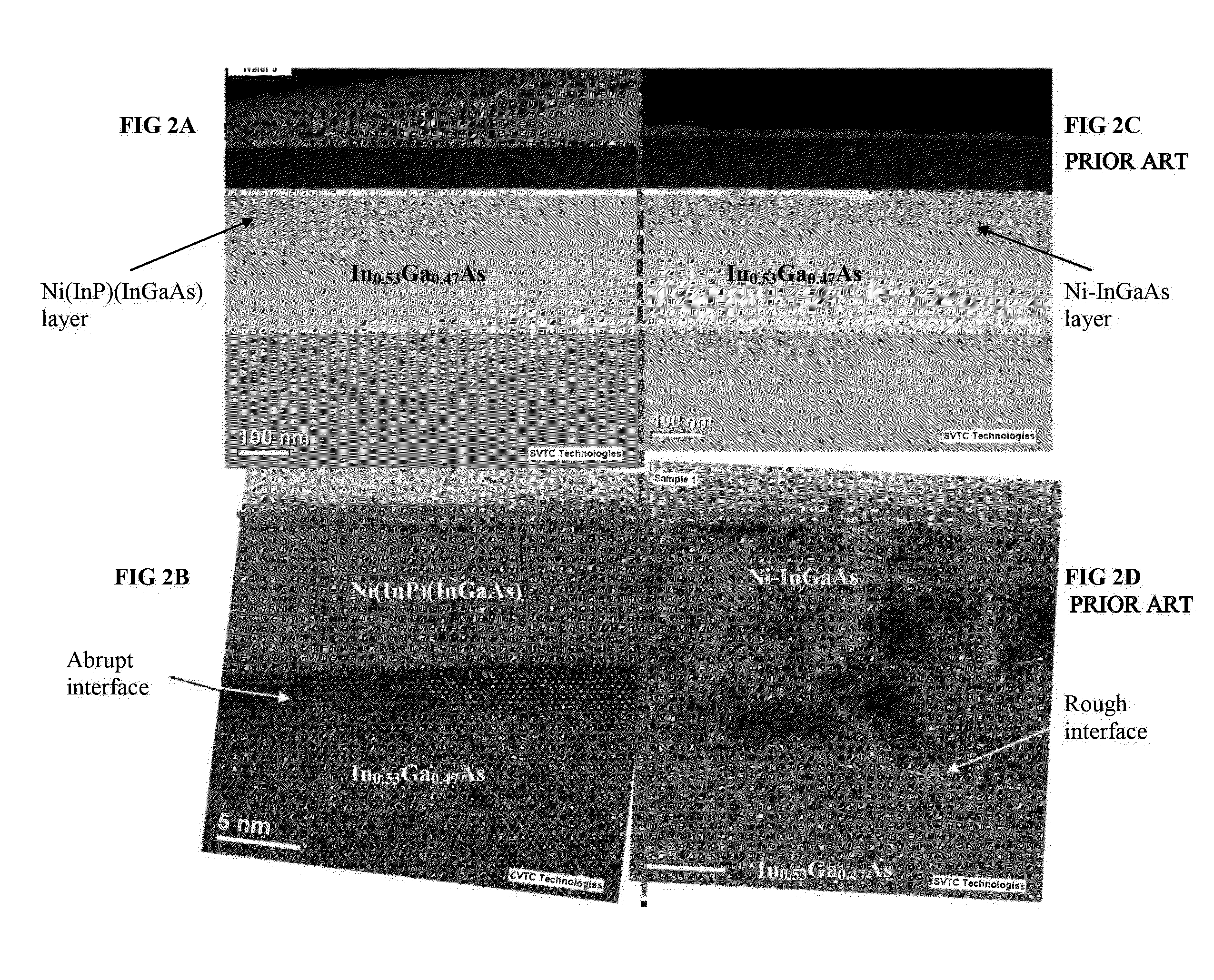

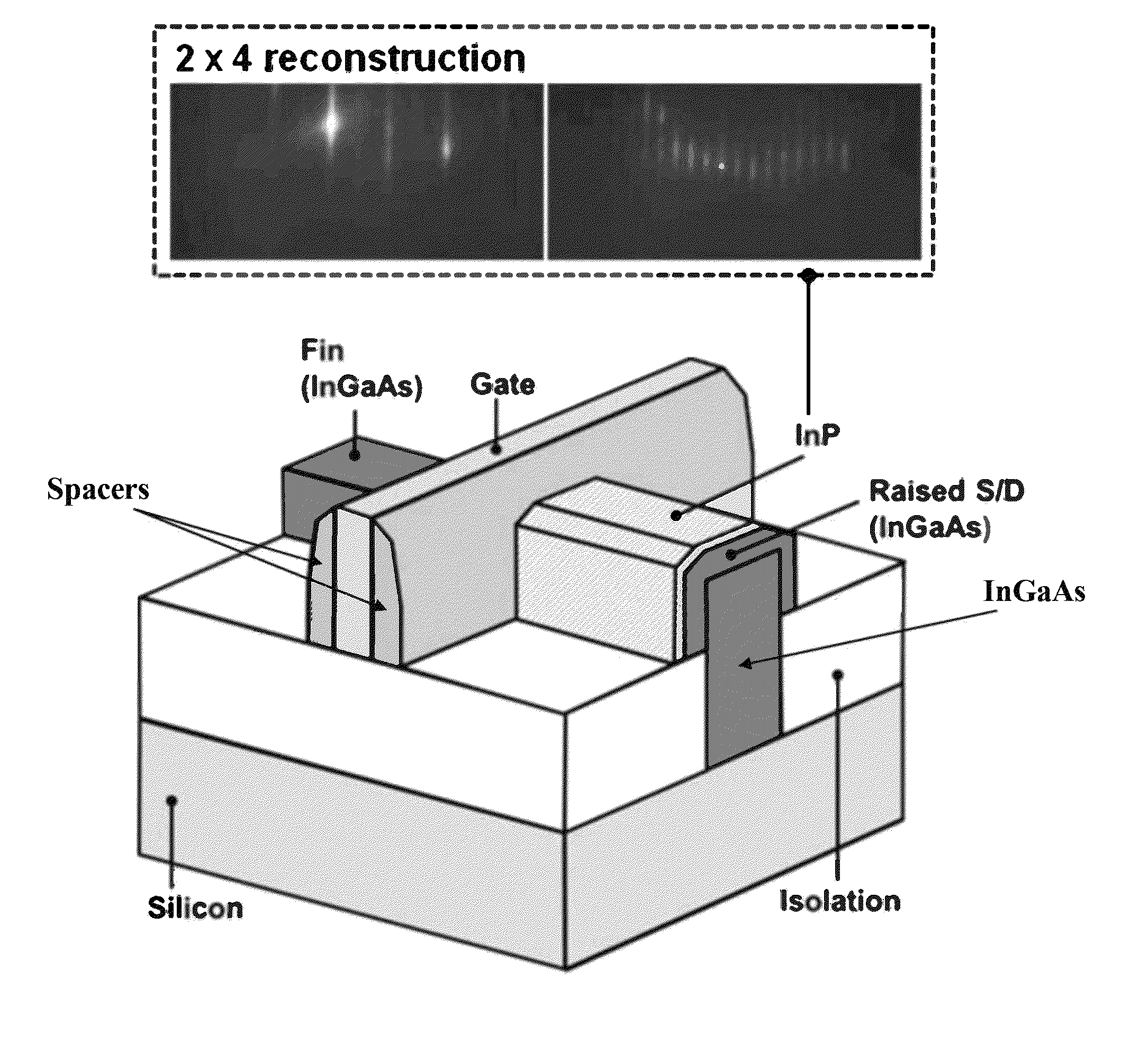

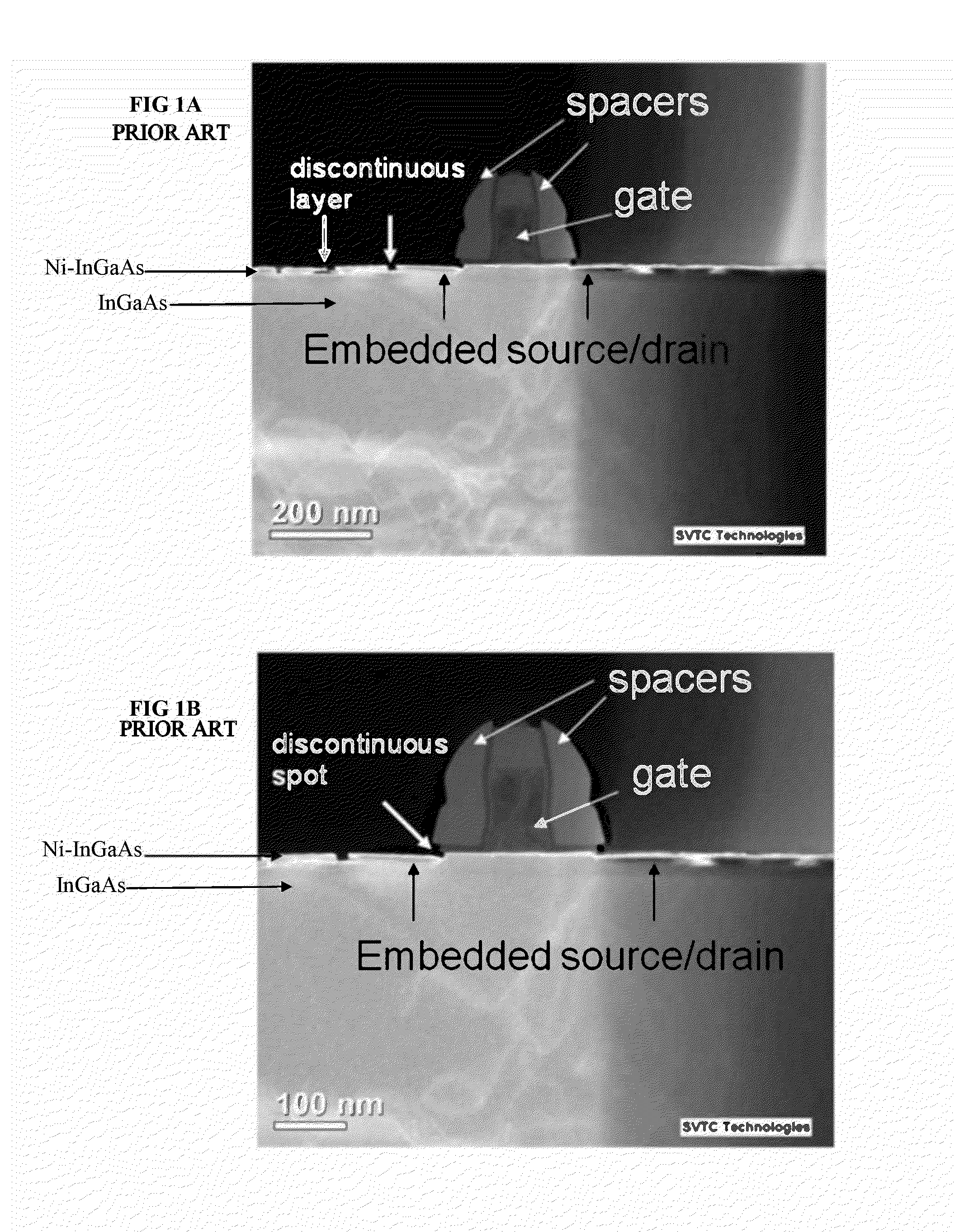

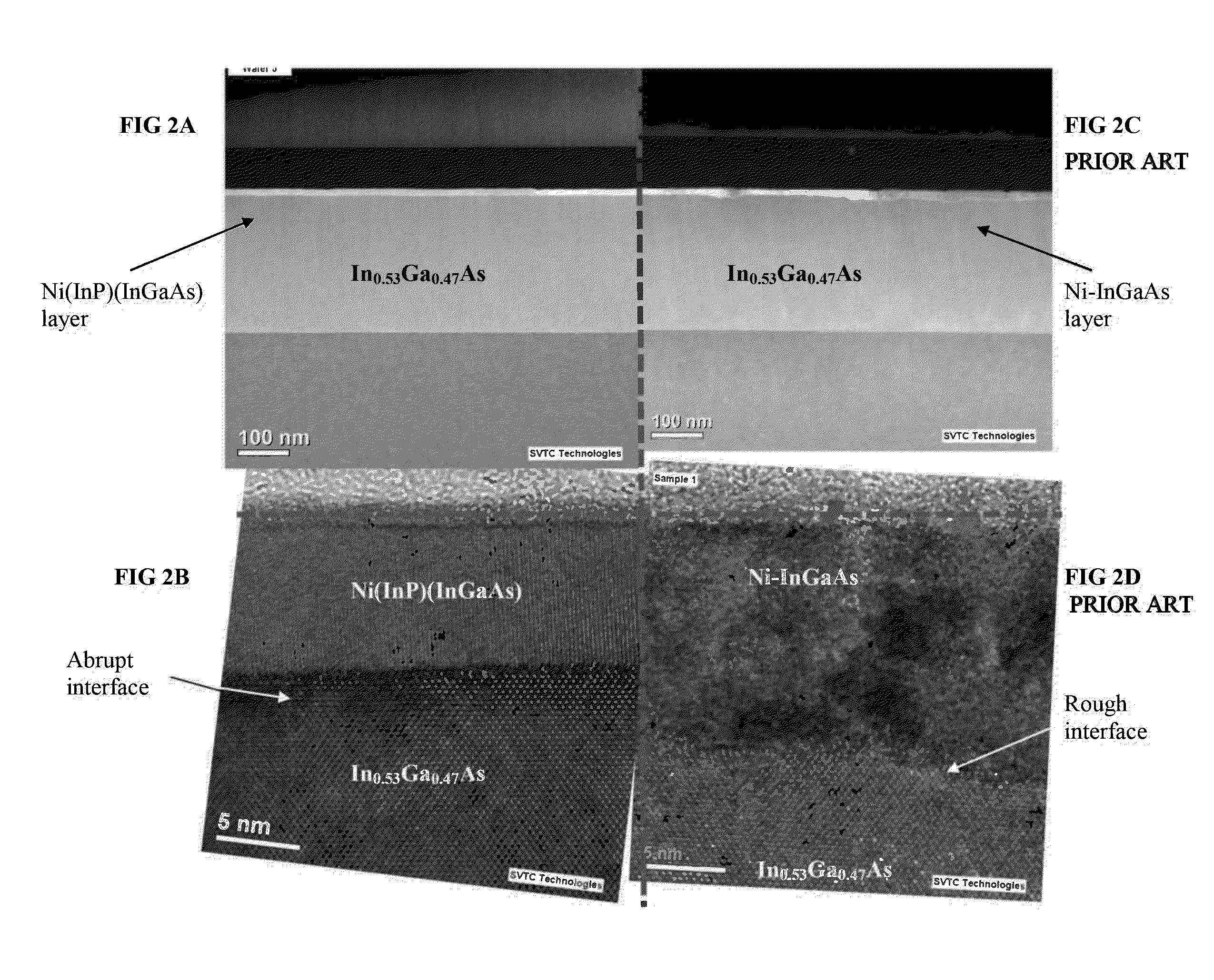

Metal alloy with an abrupt interface to iii-v semiconductor

InactiveUS20140183597A1Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSemiconductor structure

Semiconductor structures having a first layer including an n-type III-V semiconductor material and a second layer including an M(InP)(InGaAs) alloy, wherein M is selected from Ni, Pt, Pd, Co, Ti, Zr, Y, Mo, Ru, Ir, Sb, In, Dy, Tb, Er, Yb, and Te, and combinations thereof, are disclosed. The semiconductor structures have a substantially planar interface between the first and second layers. Methods of fabricating semiconductor structures, and methods of reducing interface roughness and / or sheet resistance of a contact are also disclosed.

Owner:SEMATECH

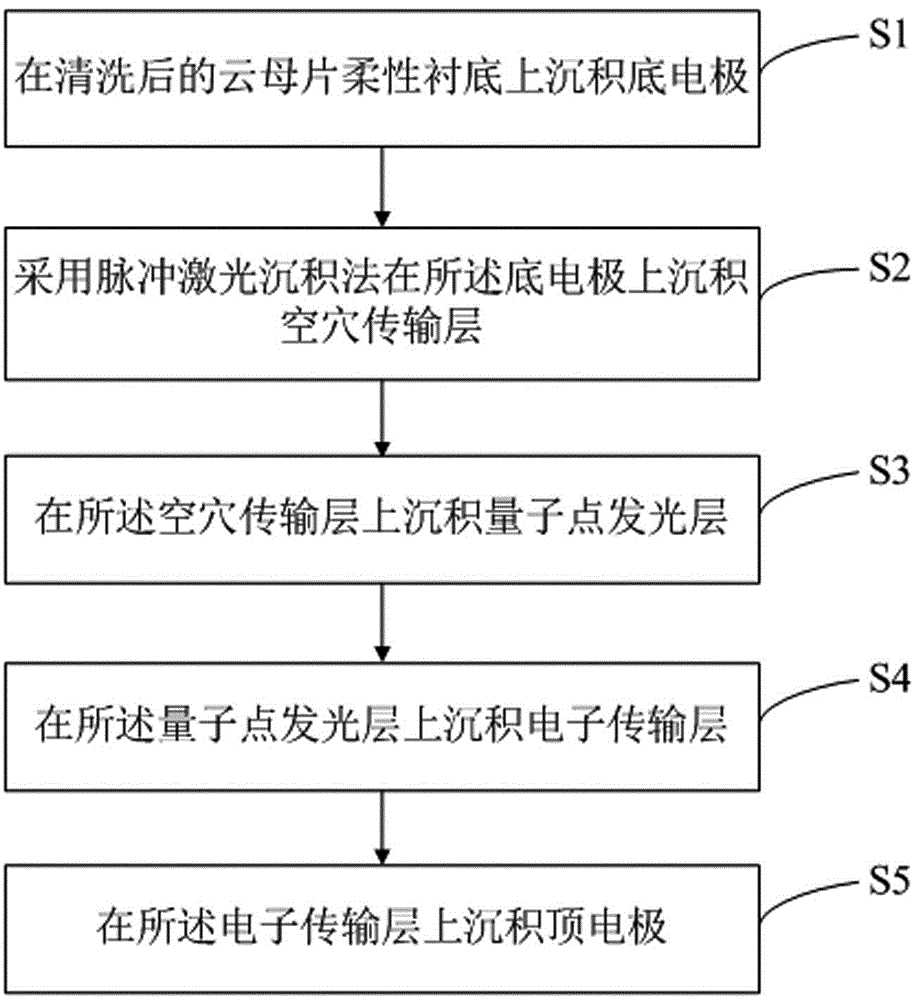

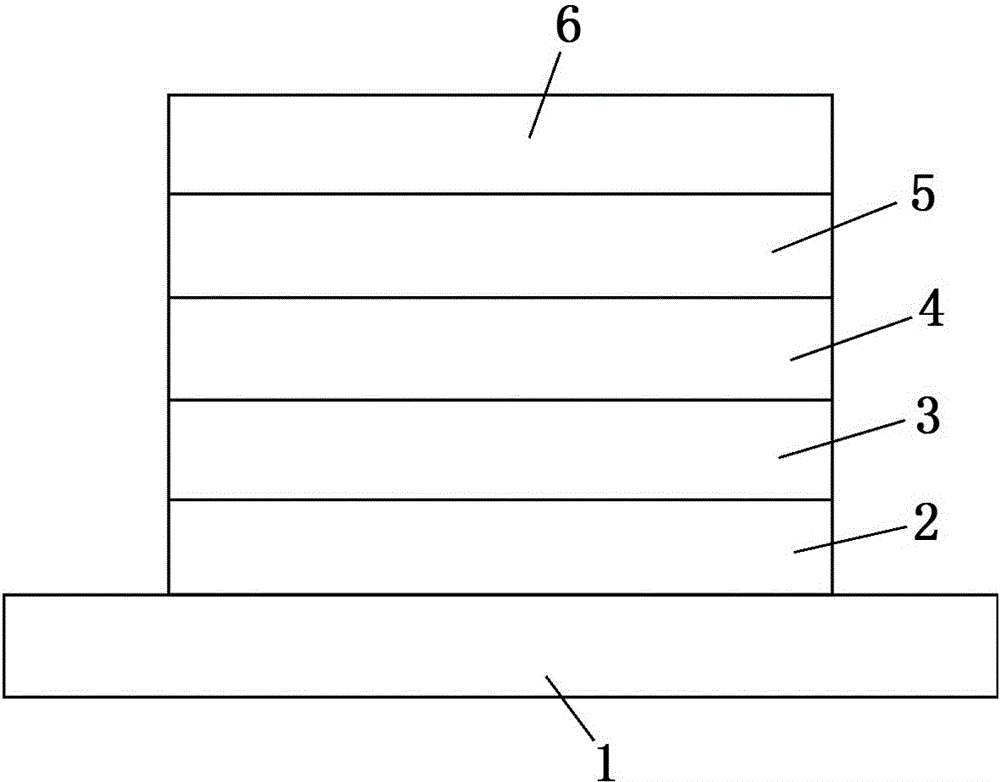

Flexible fully-inorganic QLED device and preparation method thereof

ActiveCN106711309AHigh crystallinityReduce crystal defectsSemiconductor devicesQuantum dotCrystallographic defect

The invention discloses a flexible fully-inorganic QLED device and a preparation method thereof. The preparation method comprises the steps that a bottom electrode is deposited on a cleaned mica sheet flexible substrate; a hole transmission layer is deposited on the bottom electrode by using a pulse laser deposition method; a quantum dot luminescent layer is deposited on the hole transmission layer; an electron transmission layer is deposited on the quantum dot luminescent layer; and a top electrode is deposited on the electron transmission layer. The fully-inorganic QLED device having the hole transmission layer of high crystallinity, less crystal defect, low interface roughness and high quality is acquired on the high-temperature-resistant mica sheet flexible substrate by using the laser pulse deposition method; and the carrier transmission efficiency of the hole transmission layer can be effectively enhanced by the high-quality hole transmission layer so as to enhance the luminescent efficiency of the QLED device.

Owner:TCL CORPORATION

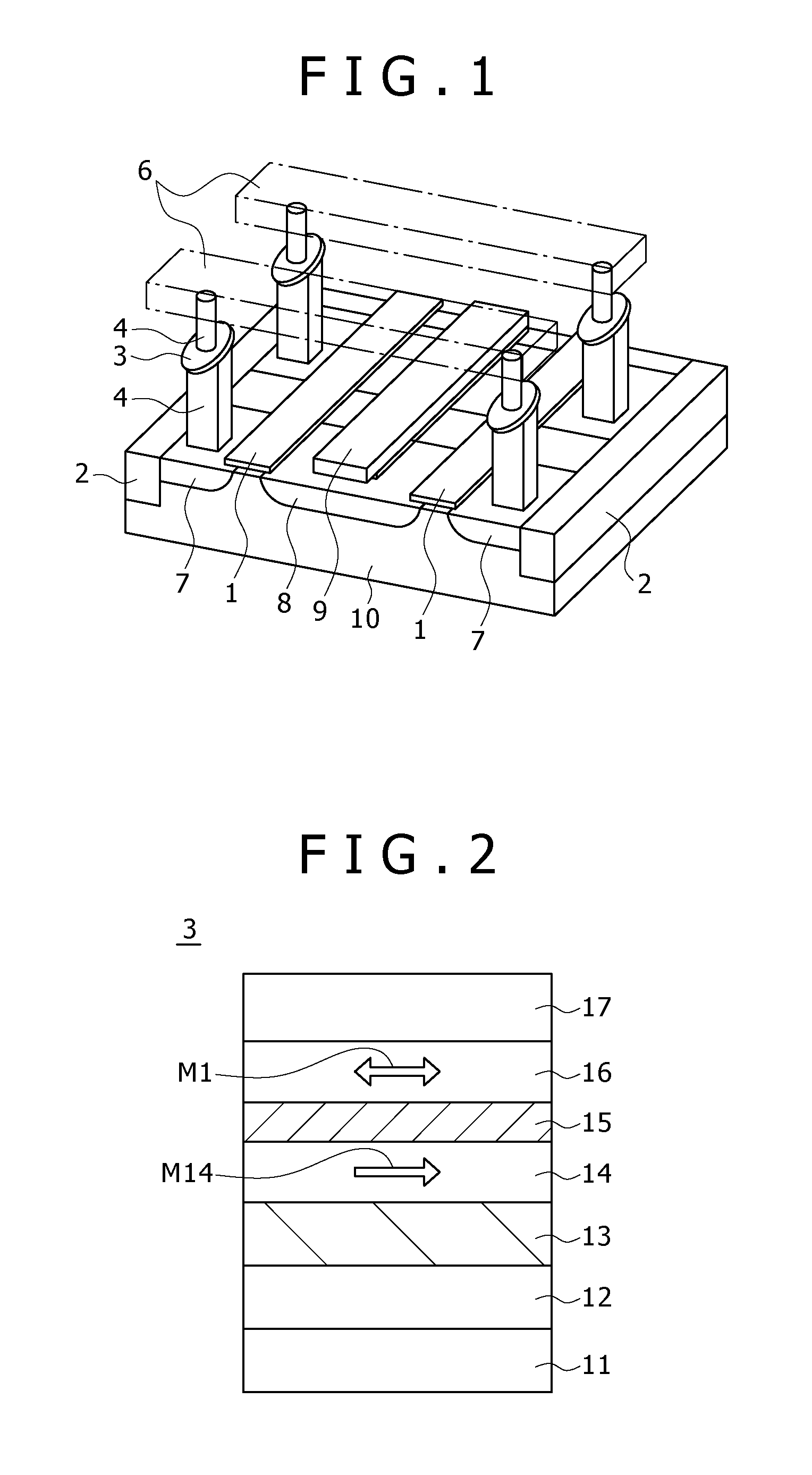

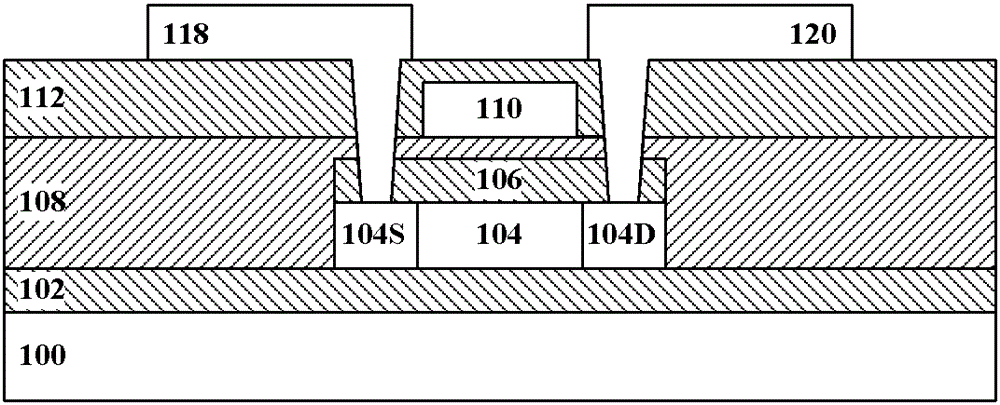

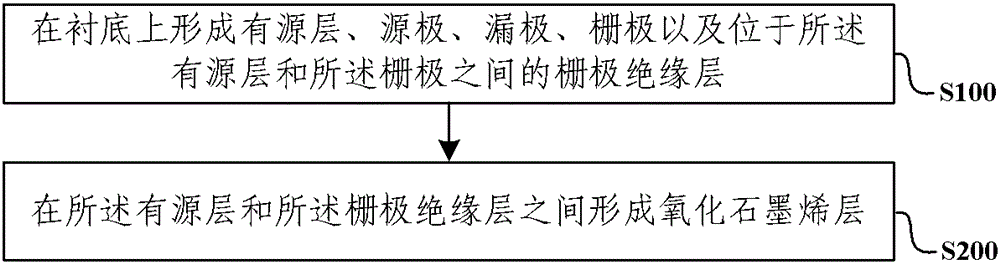

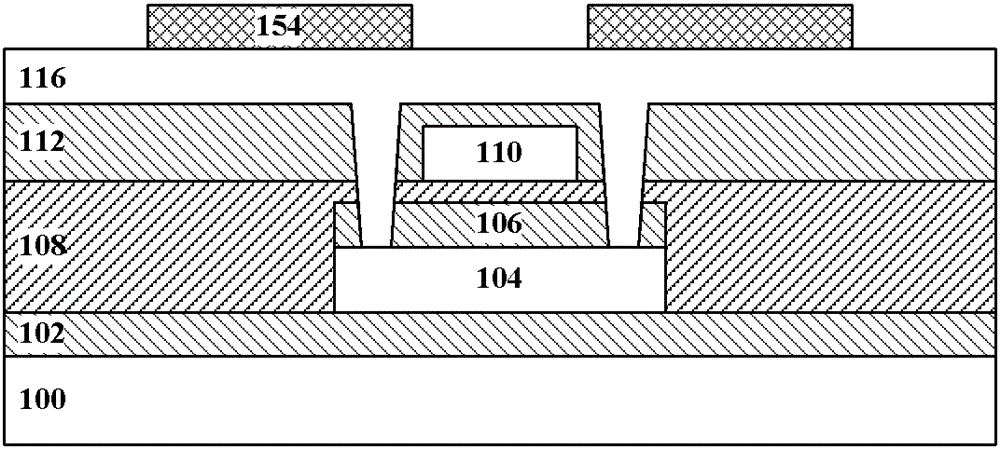

Low-temperature polycrystalline silicon thin film transistor, manufacturing method, array substrate, and display panel

ActiveCN105261654ASmall molecular structureIncreased ion mobilityTransistorSolid-state devicesOptoelectronicsGraphene

The invention relates to the technical field of display, and discloses a low-temperature polycrystalline silicon thin film transistor, a manufacturing method, an array substrate, and a display panel. The transistor comprises an active layer, a source electrode, a drain electrode, a grid electrode, a grid insulating layer disposed between the active layer and the grid electrode, and an oxidized graphene layer disposed between the active layer and the grid insulating layer, wherein the active layer, the source electrode, the drain electrode and the grid electrode are disposed on a substrate. The oxidized graphene layer is disposed between the active layer and the grid insulating layer, thereby reducing the interface roughness and the interface defect mode density between the active layer and the grid insulating layer. Moreover, there is no need to carry out pre-cleaning of the grid insulating layer. The invention also discloses the manufacturing method for the transistor, the array substrate, and the display panel.

Owner:BOE TECH GRP CO LTD

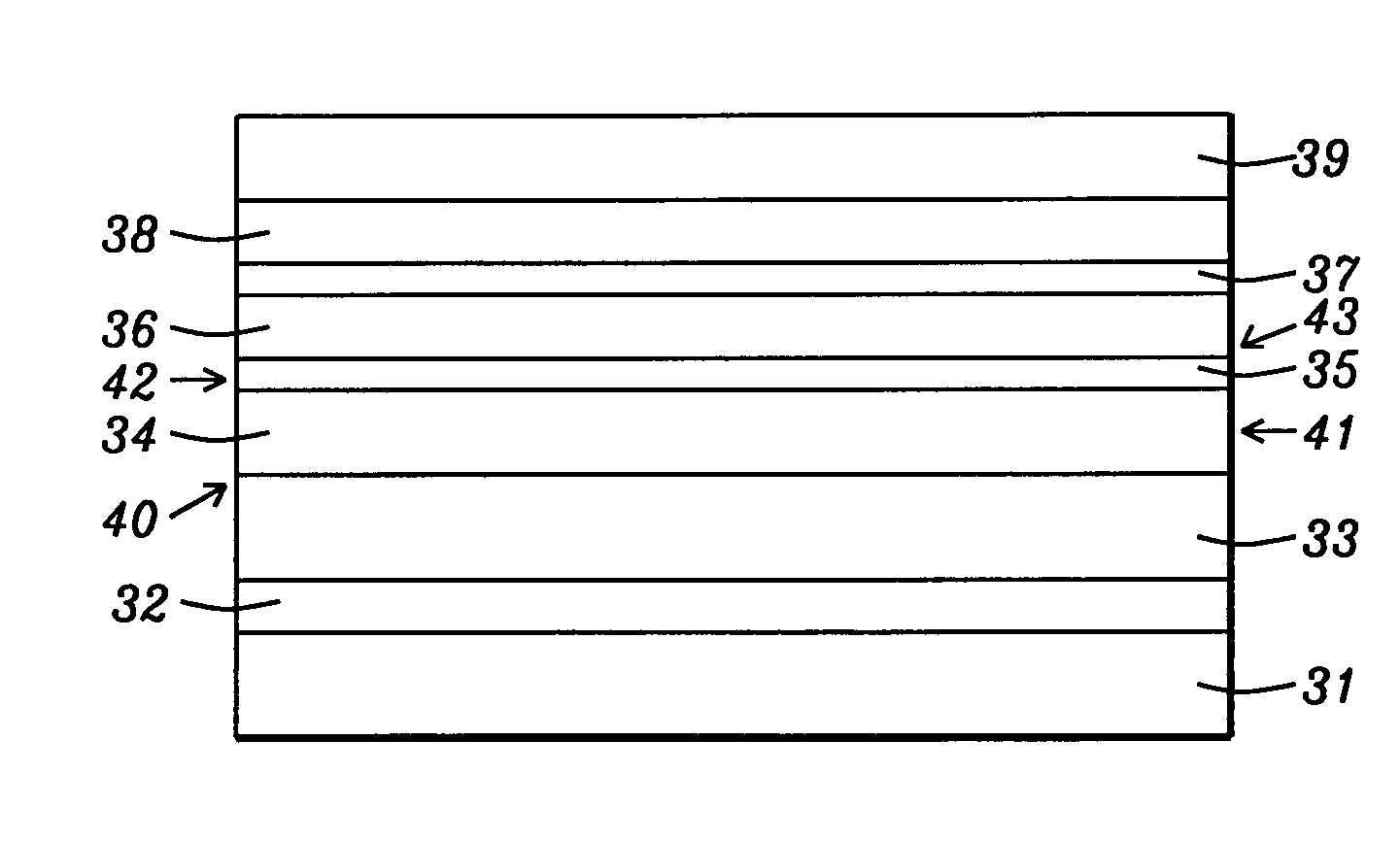

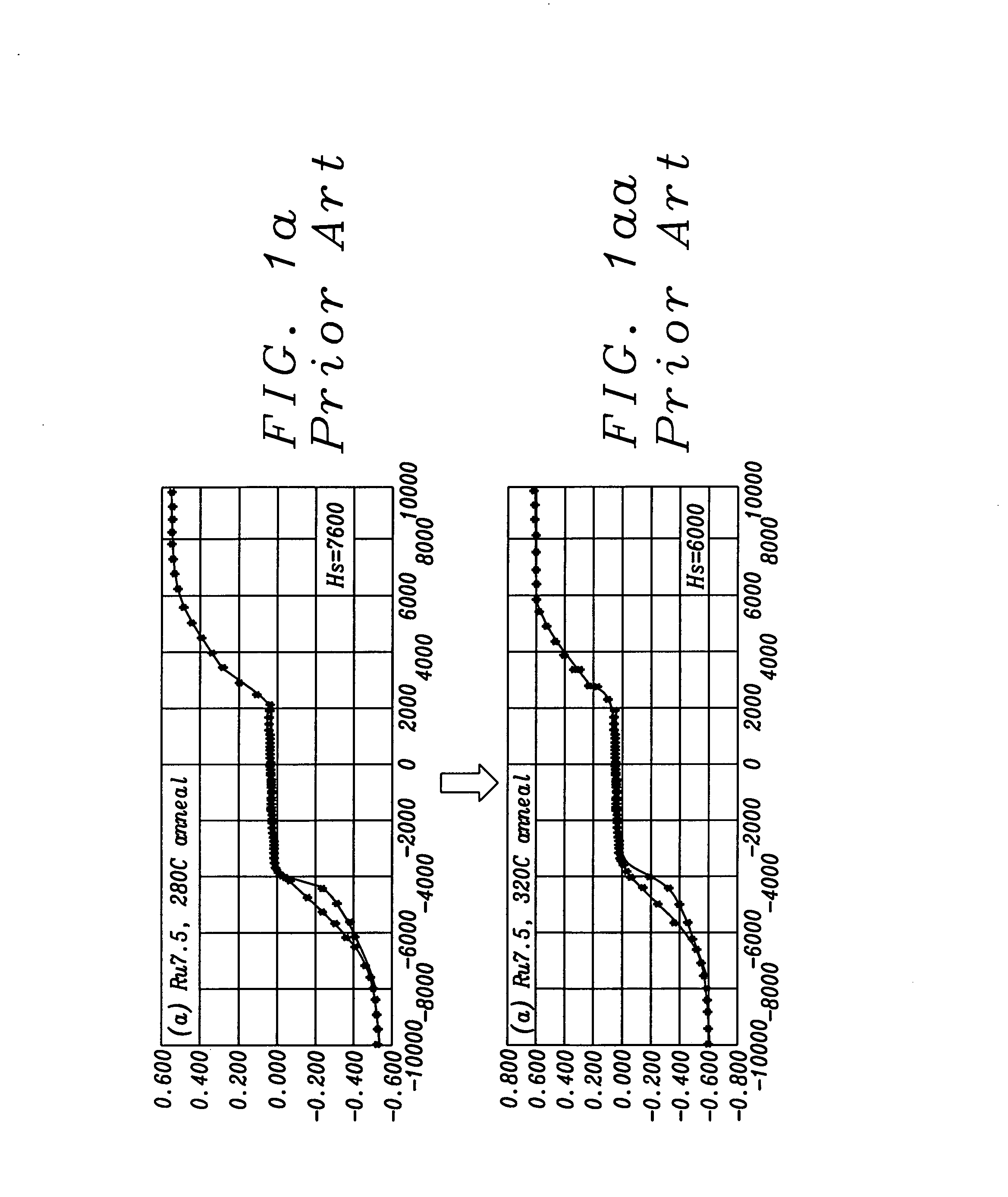

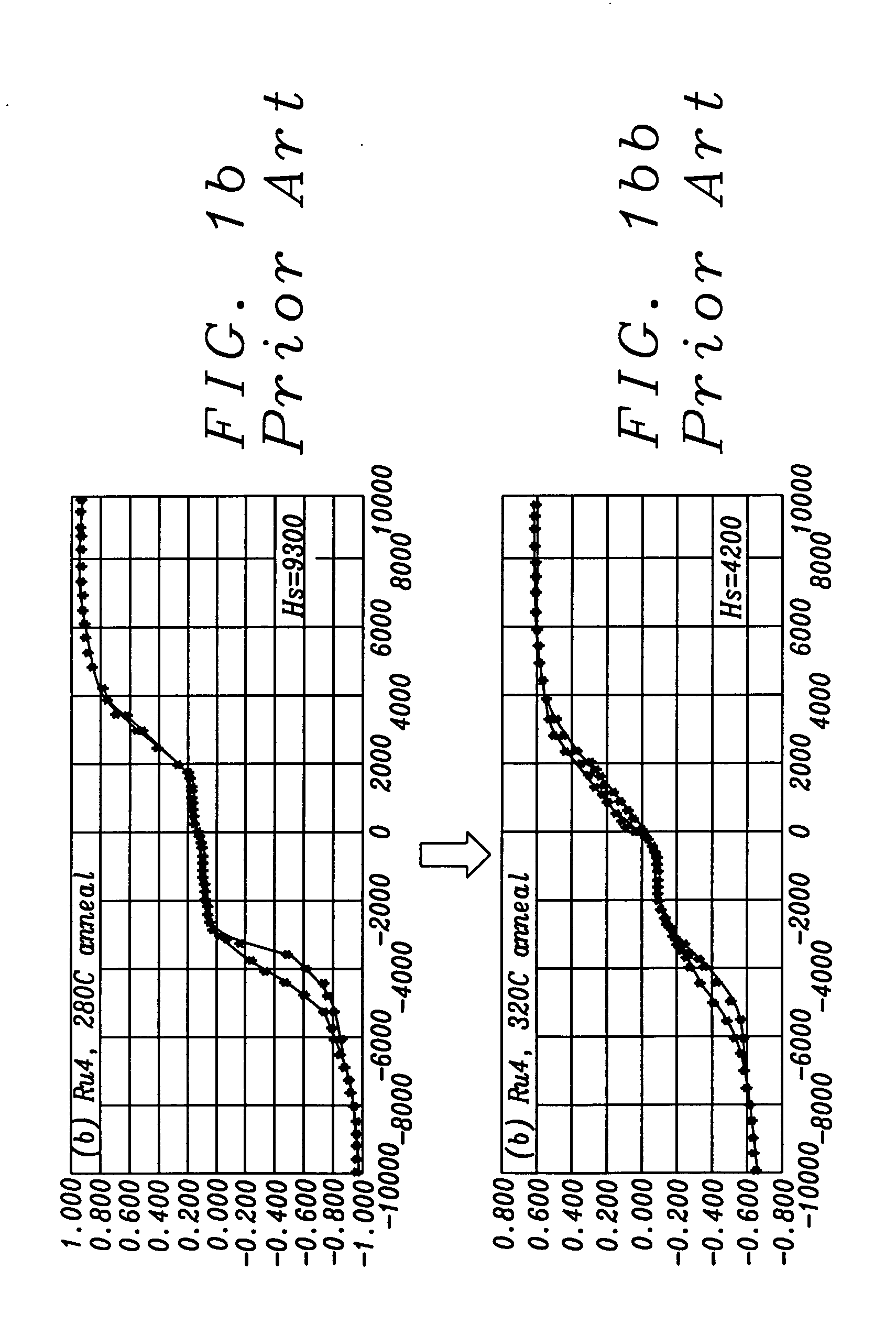

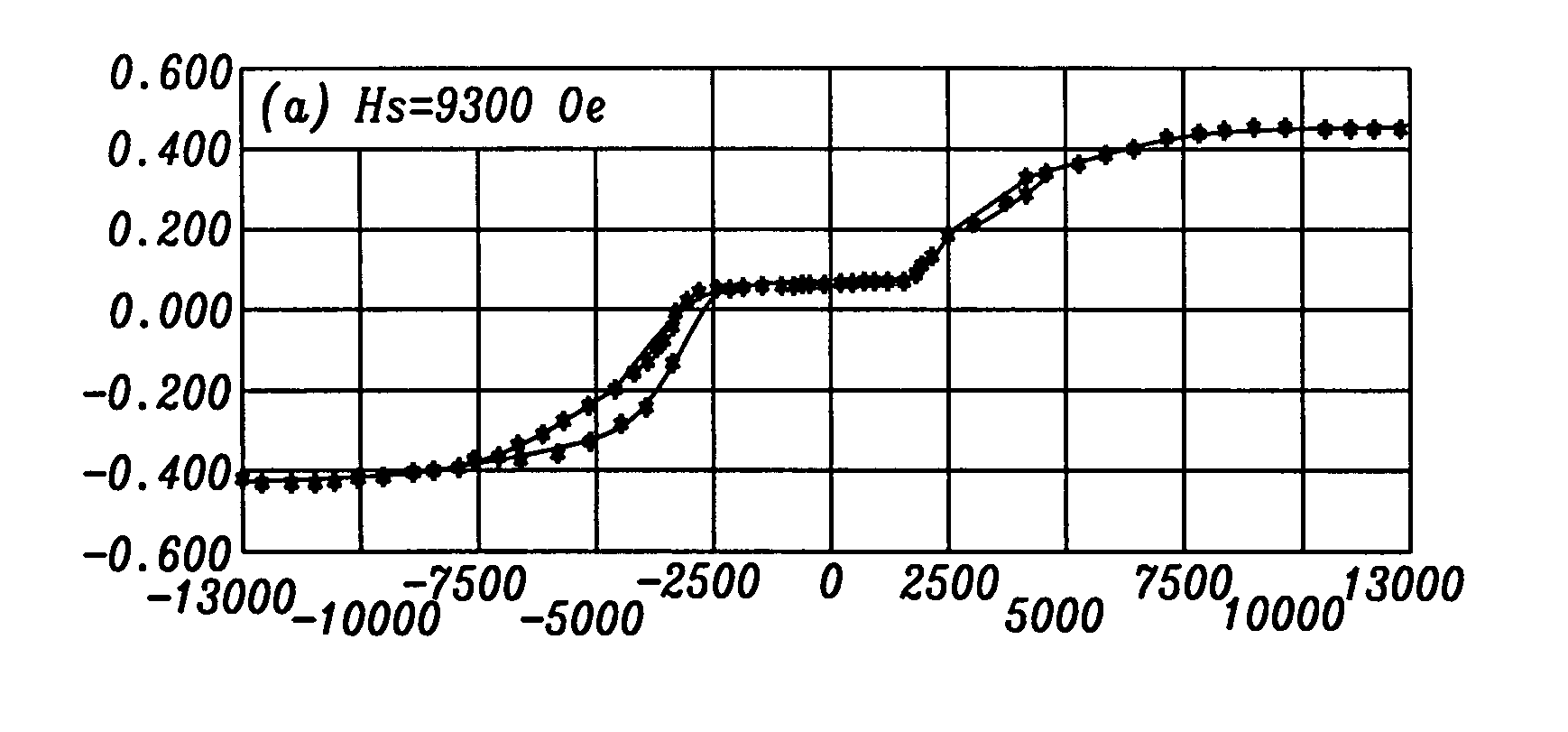

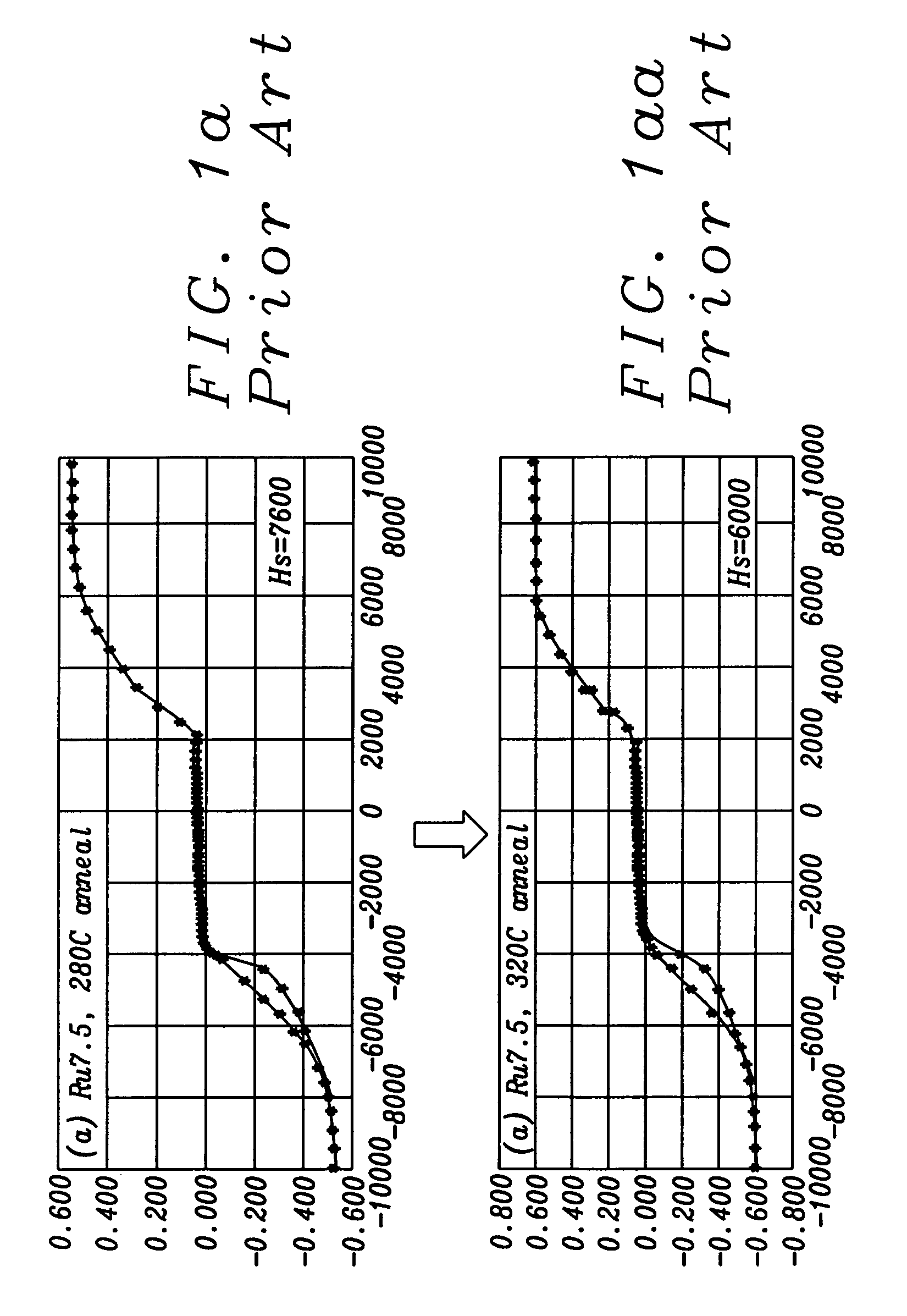

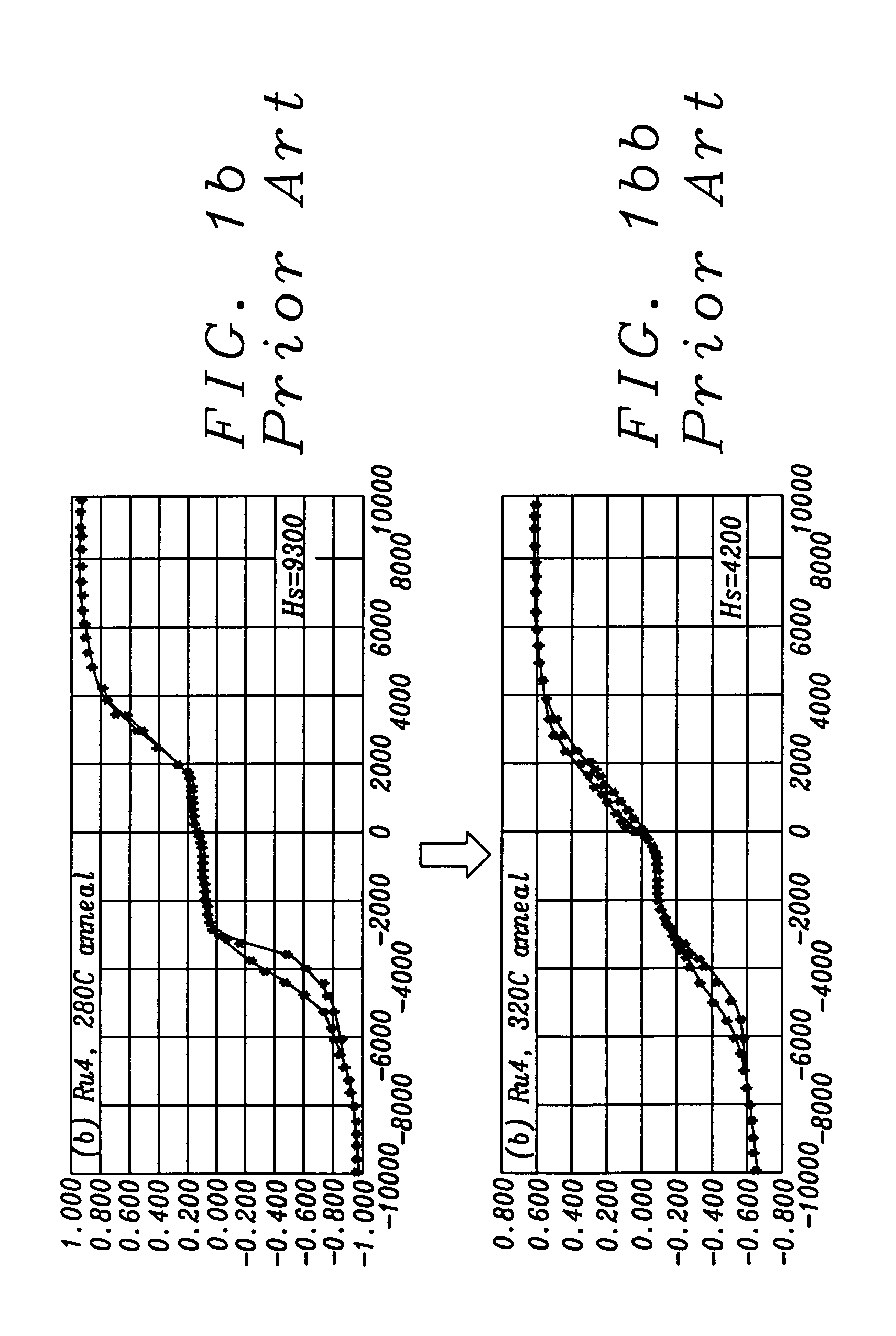

Pinning field in MR devices despite higher annealing temperature

ActiveUS20120205757A1High pinning strengthRaise the ratioMagnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingManganeseRuthenium

The pinning field in an MR device was significantly improved by using the Ru 4A peak together with steps to minimize interfacial roughness of the ruthenium layer as well as boron and manganese diffusion into the ruthenium layer during manufacturing. This made it possible to anneal at temperatures as high as 340° C. whereby a high MR ratio could be simultaneously achieved.

Owner:HEADWAY TECH INC

Magnesium alloy surface pretreatment method

ActiveCN102505104AIncrease roughnessImprove bindingMolten spray coatingAbrasive blastingPretreatment method

A magnesium alloy surface pretreatment method is characterized by including step one, leveling; step two, groove turning; step three, shot blasting; step four, shot clearing; and step five, aluminum spraying. Compared with the prior art, the magnesium alloy surface pretreatment method has the advantages that composite coarsening treatments of shot blasting and groove turning are carried out through a joint interface so that roughness of the joint interface is enhanced and adhesion between a coating and a base can be increased; coating stress can be reduced under groove turning, microcracks inside the coating and at the contact interface of the coating and the base are eliminated, and coating shedding is prevented.

Owner:NO 52 INST OF CHINA NORTH IND GRP CORP

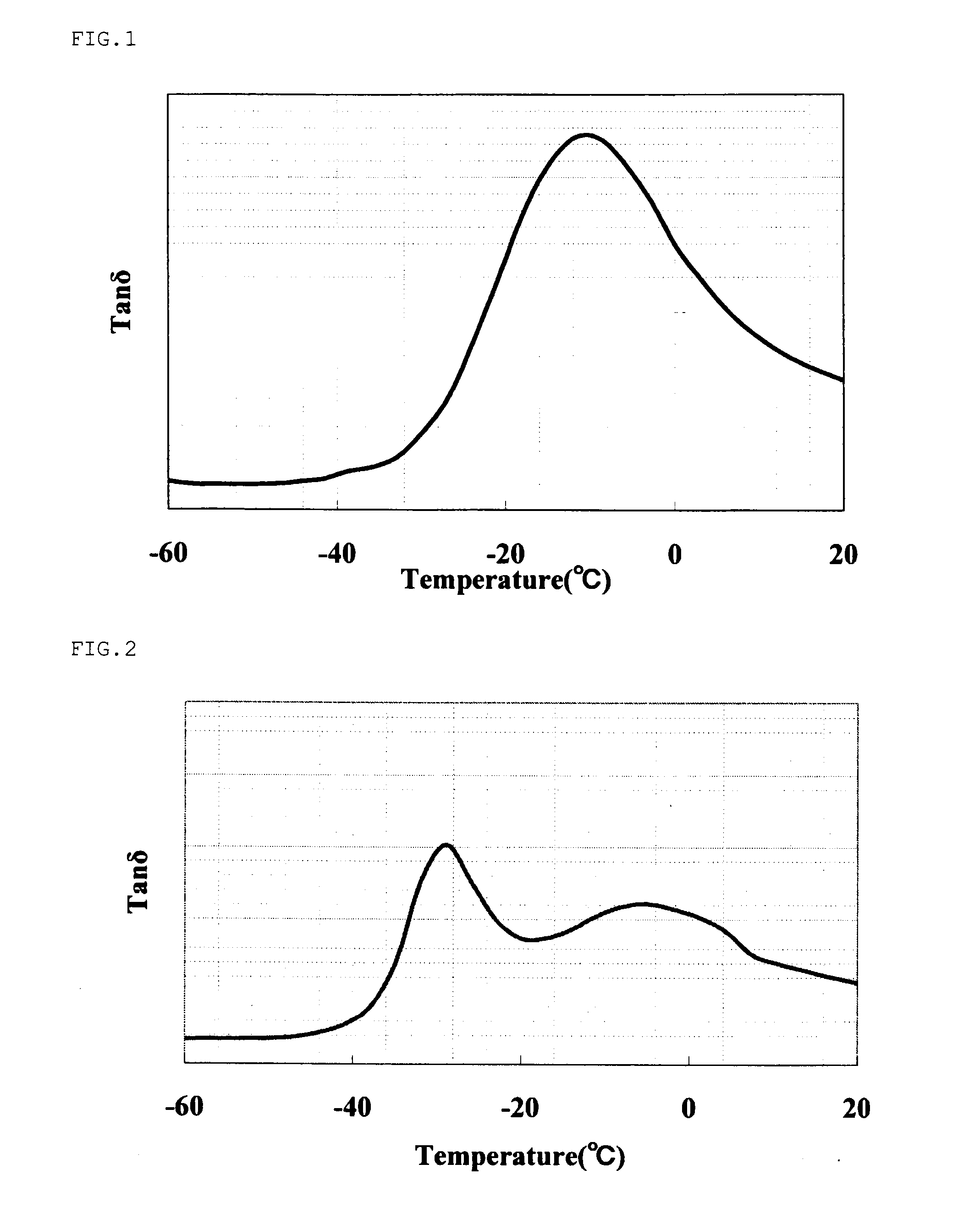

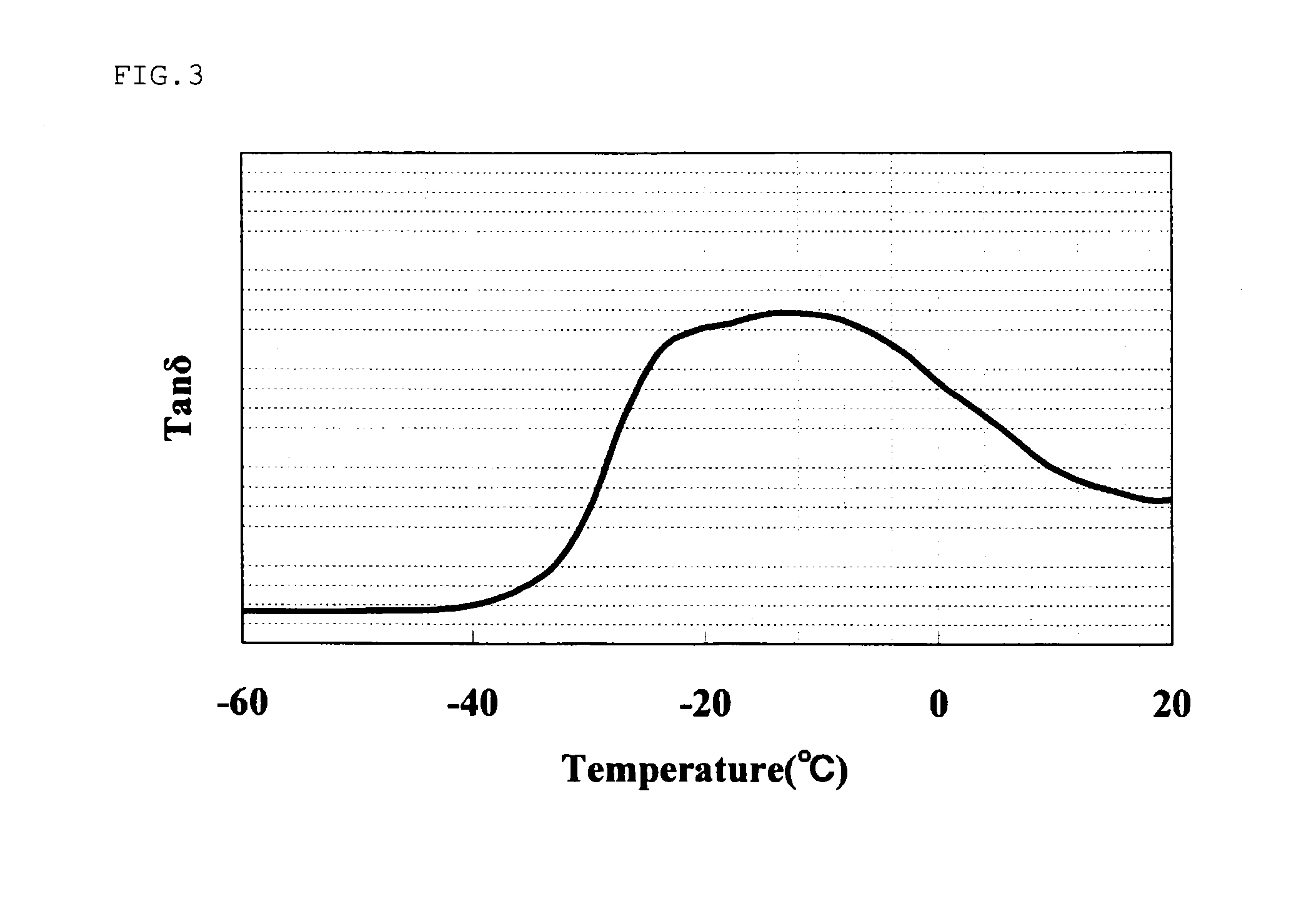

Propylene resin sheet and heat processing packaging body using same

InactiveUS20130177721A1Increase flexibilityIncrease resistanceSynthetic resin layered productsBagsPolymer scienceCopolymer

The invention discloses a propylene resin sheet and a heat-treatable packaging material which have an excellent transparency, flexibility and very-low-temperature impact resistance, and which reduce the thickness variation during lamination, suppress appearance defects such as interfacial roughness. A propylene resin sheet composed of at least one layer, the main layer being made up of a resin composition containing: (1) 50 to 90 wt % of a propylene resin composition (A) which includes from 30 to 70 wt % of a propylene-α-olefin random copolymer component (A1) having a melting peak temperature of 120 to 150° C., and from 70 to 30 wt % of a propylene-α-olefin random copolymer component (A2) having a C2 or C4-8 α-olefin content of at least 10 wt % but less than 20 wt %; and (2) 10 to 50 wt % of a specific ethylene-α-olefin copolymer (B).

Owner:JAPAN POLYPROPYLENE CORP

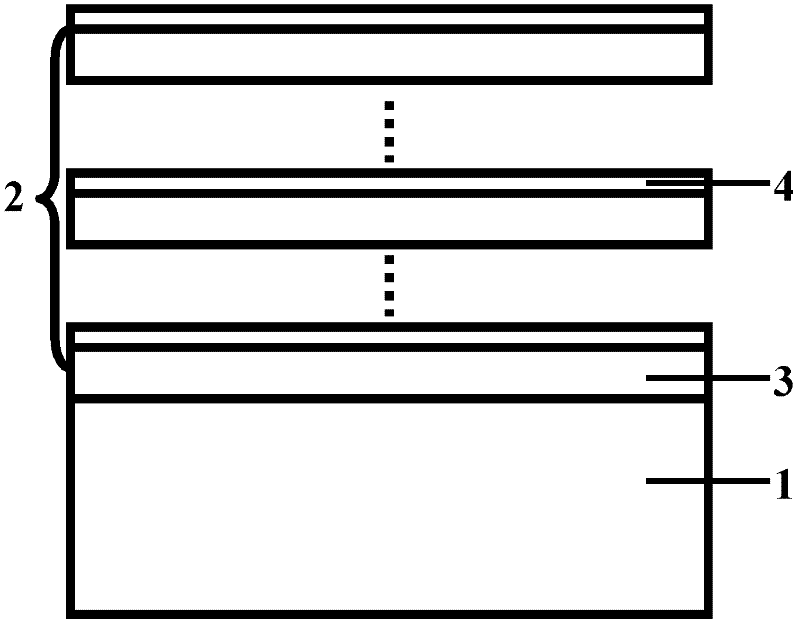

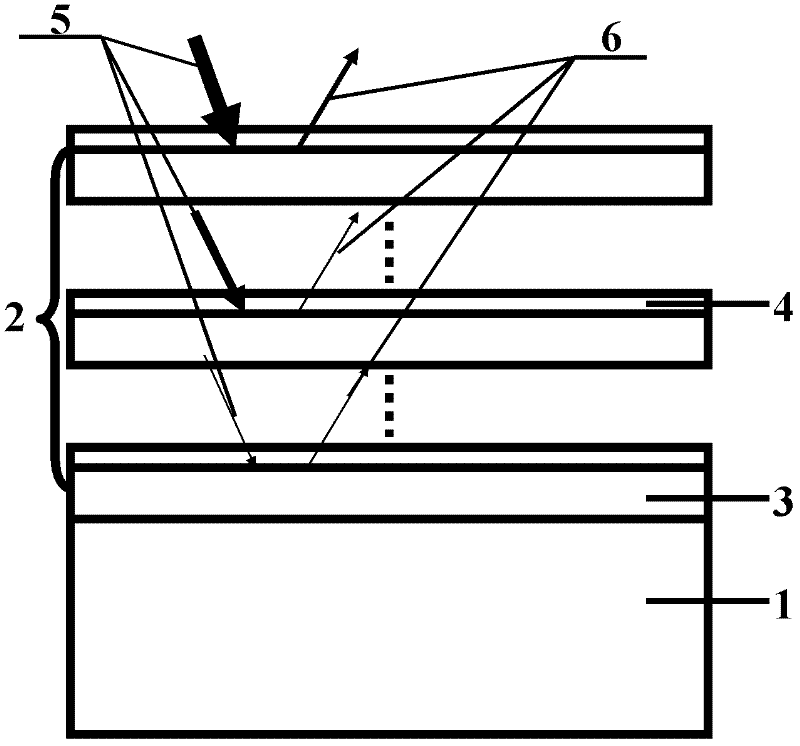

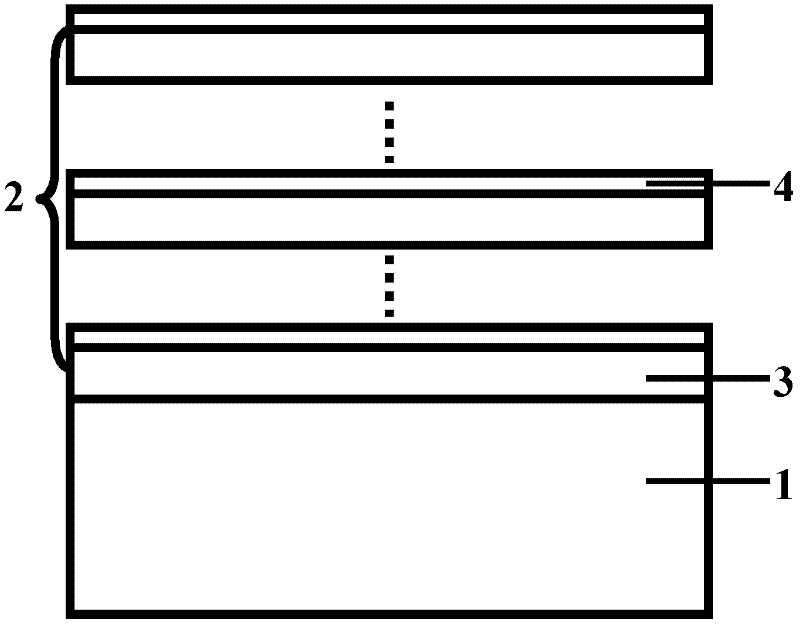

Duralumin/silicon carbide extreme ultraviolet multilayer reflector and manufacturing method for the same

InactiveCN102520470ASimple interfaceReduce manufacturing costMirrorsVacuum evaporation coatingManufacturing technologyDuralumin

The invention belongs to the technical field of precision optical component manufacturing, and discloses a duralumin / silicon carbide extreme ultraviolet multilayer reflector and a manufacturing method for the same. The reflector of the invention comprises a substrate (1) and a duralumin / silicon carbide periodic multilayer film (2), wherein duralumin thin film layers (3) and silicon carbide thin film layers (4) are alternatively deposited on the surface of the substrate (1). The reflector manufacturing method of the invention comprises the following steps of: firstly, washing the substrate (1), and then, plating the duralumin / silicon carbide periodic multilayer film (2) on the substrate (1). The reflector of the invention overcomes the defects, such as larger interface roughness and higher mutual penetration between film layer materials, of the conventional aluminum / silicon carbide multilayer film, reduces the difficulty in the manufacturing technology and reduces the price of metal materials by 2 orders of magnitude; and the novel duralumin / silicon carbide extreme ultraviolet multilayer reflector has the advantages of good film-forming quality, easy manufacturing process, cheap price, excellent optical performance meeting the needs, and the like, thereby being more suitable for realizing industrialization of such products.

Owner:TONGJI UNIV

Semiconductor-on-insulator (SOI) structures including gradient nitrided buried oxide (BOX)

ActiveUS7396776B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureNitrogen

A semiconductor-on-insulator structure includes a buried dielectric layer interposed between a base semiconductor substrate and a surface semiconductor layer. The buried dielectric layer comprises an oxide material that includes a nitrogen gradient that peaks at the interface of the buried dielectric layer with at least one of the base semiconductor substrate and surface semiconductor layer. The interface of the buried dielectric layer with the at least one of the base semiconductor substrate and surface semiconductor layer is abrupt, providing a transition in less than about 5 atomic layer thickness, and having less than about 10 angstroms RMS interfacial roughness. A second dielectric layer comprising an oxide dielectric material absent nitrogen may be located interposed between the buried dielectric layer and the surface semiconductor layer.

Owner:META PLATFORMS INC

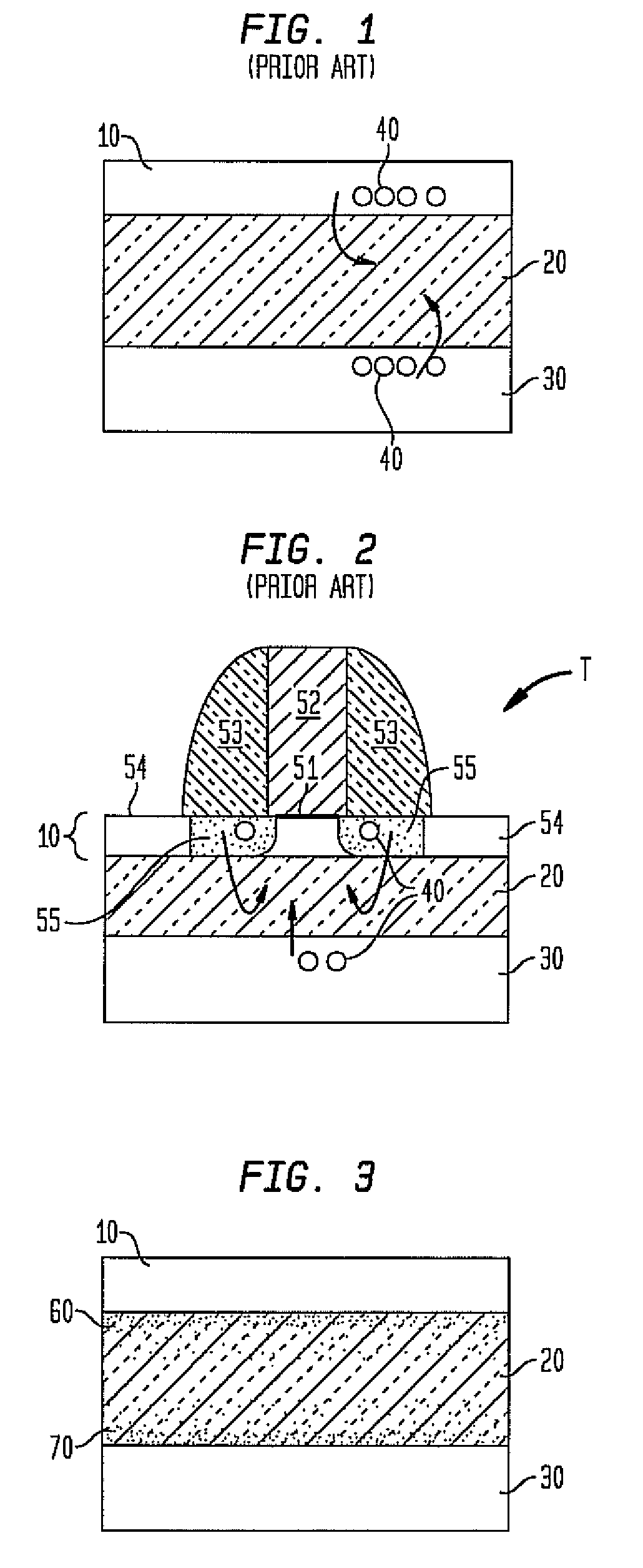

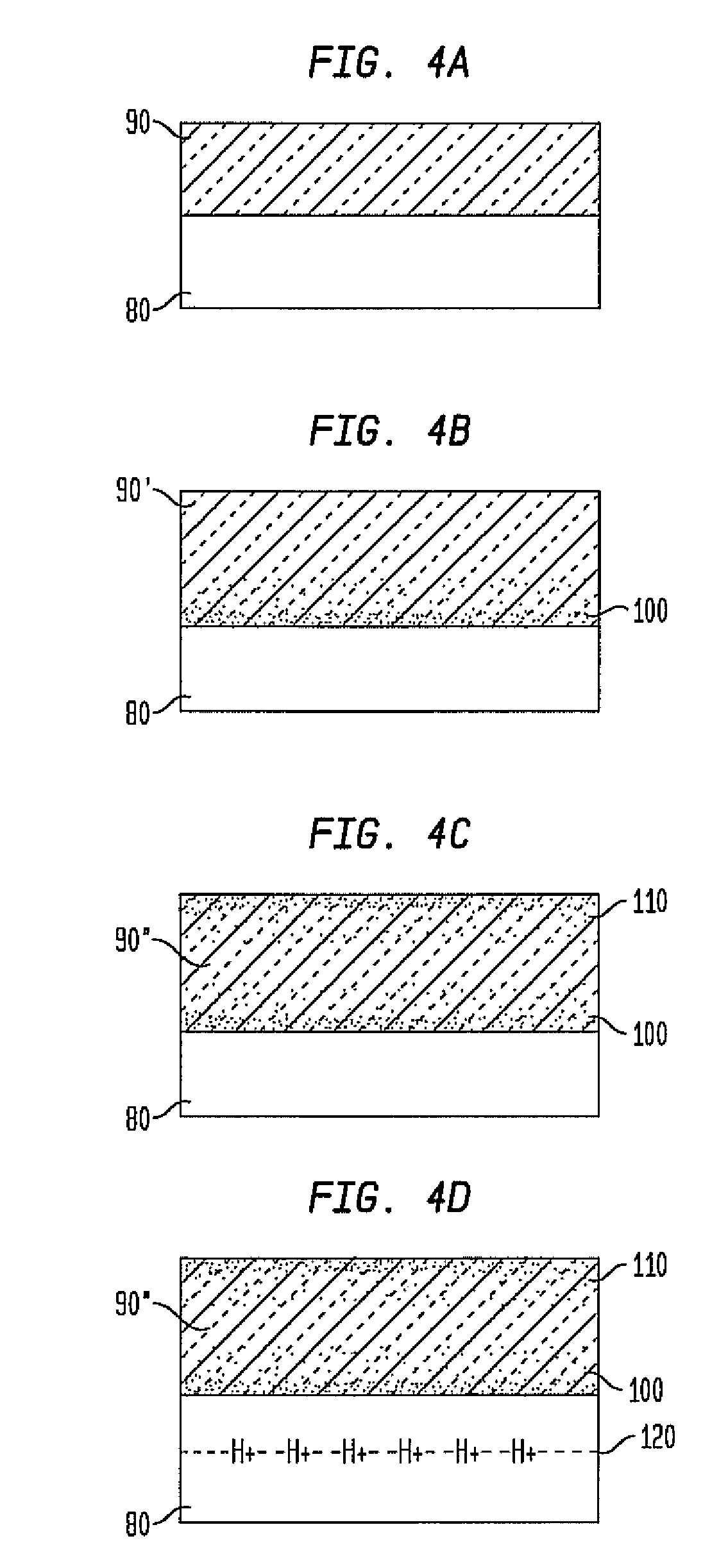

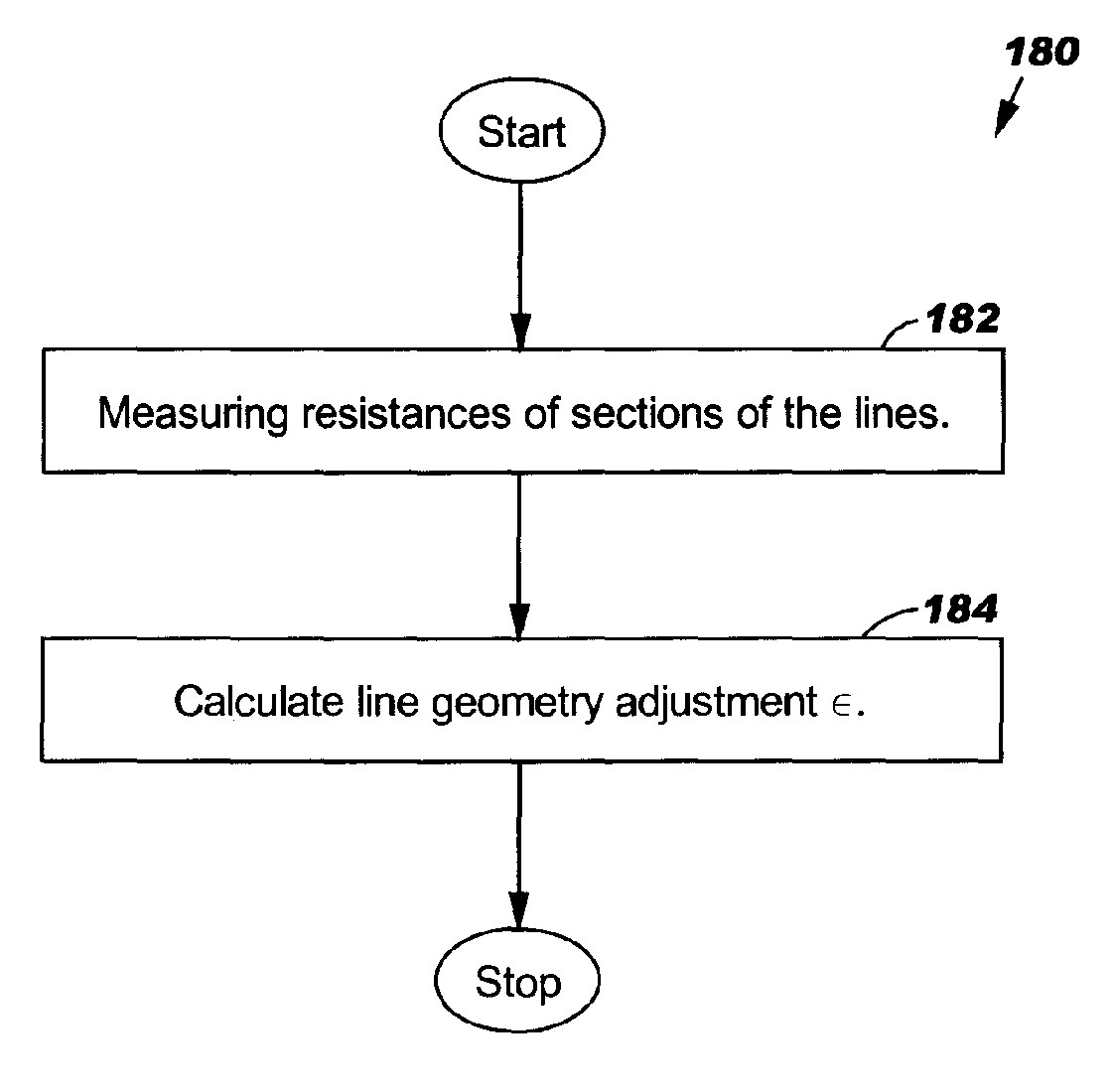

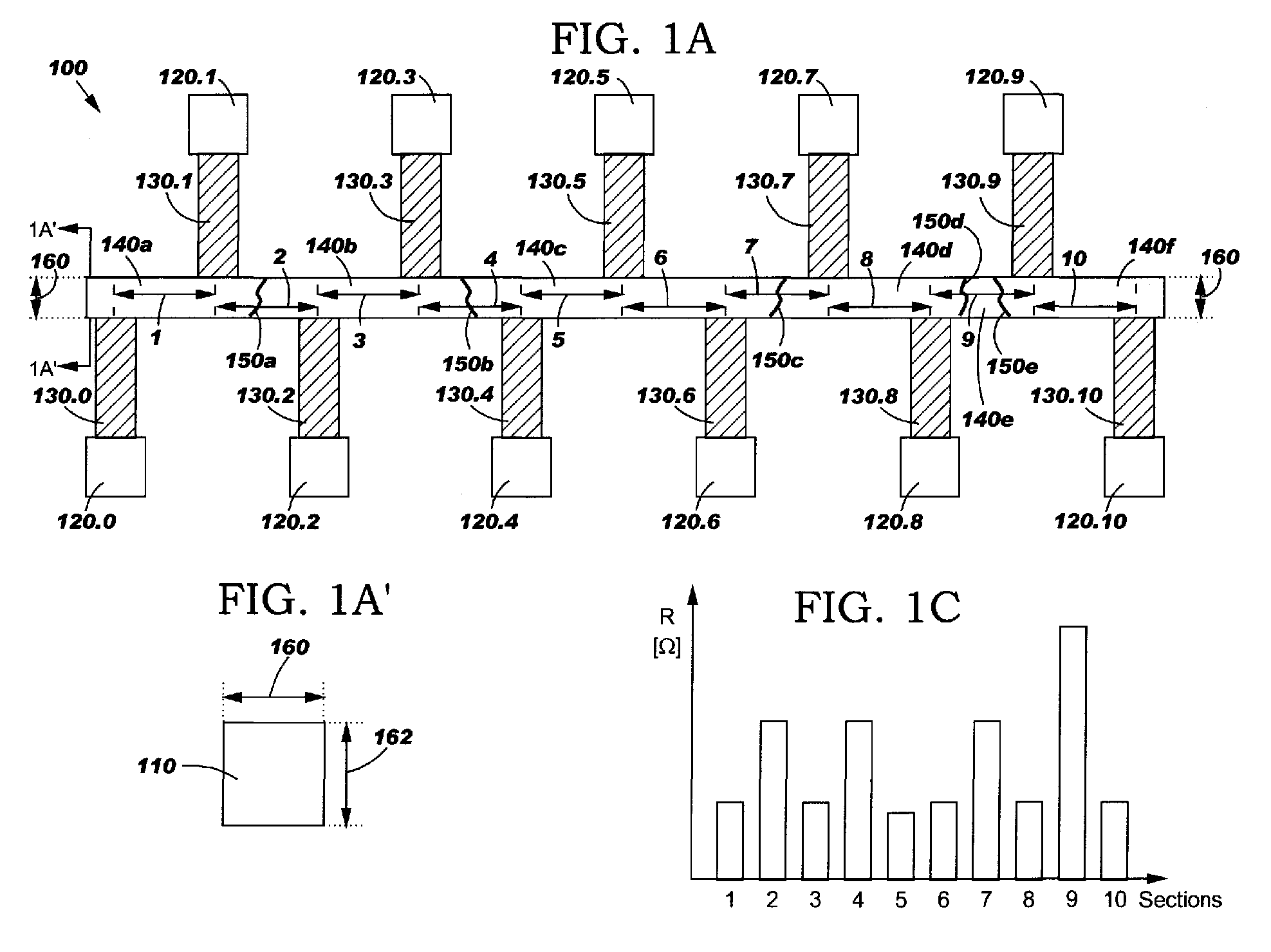

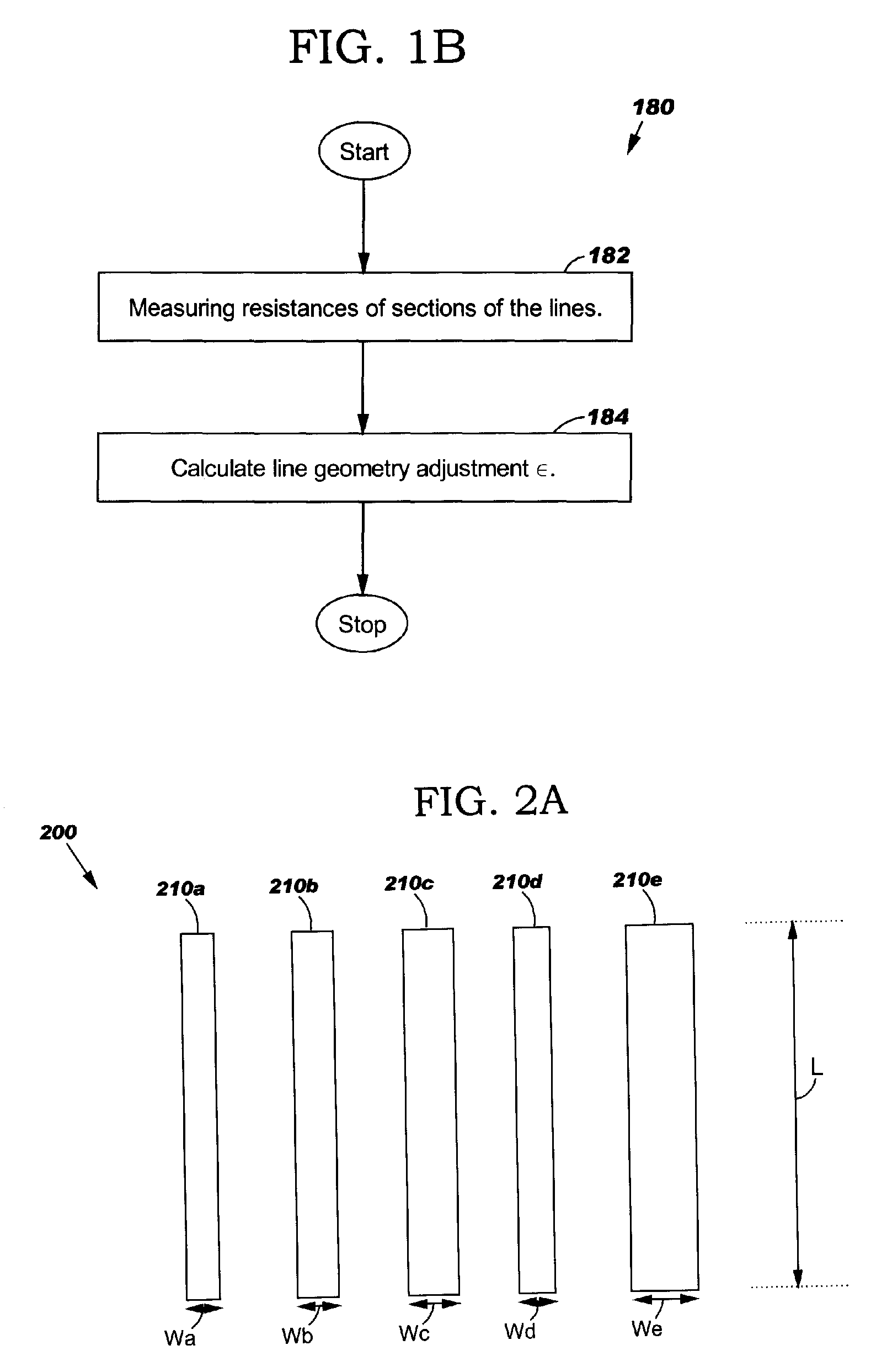

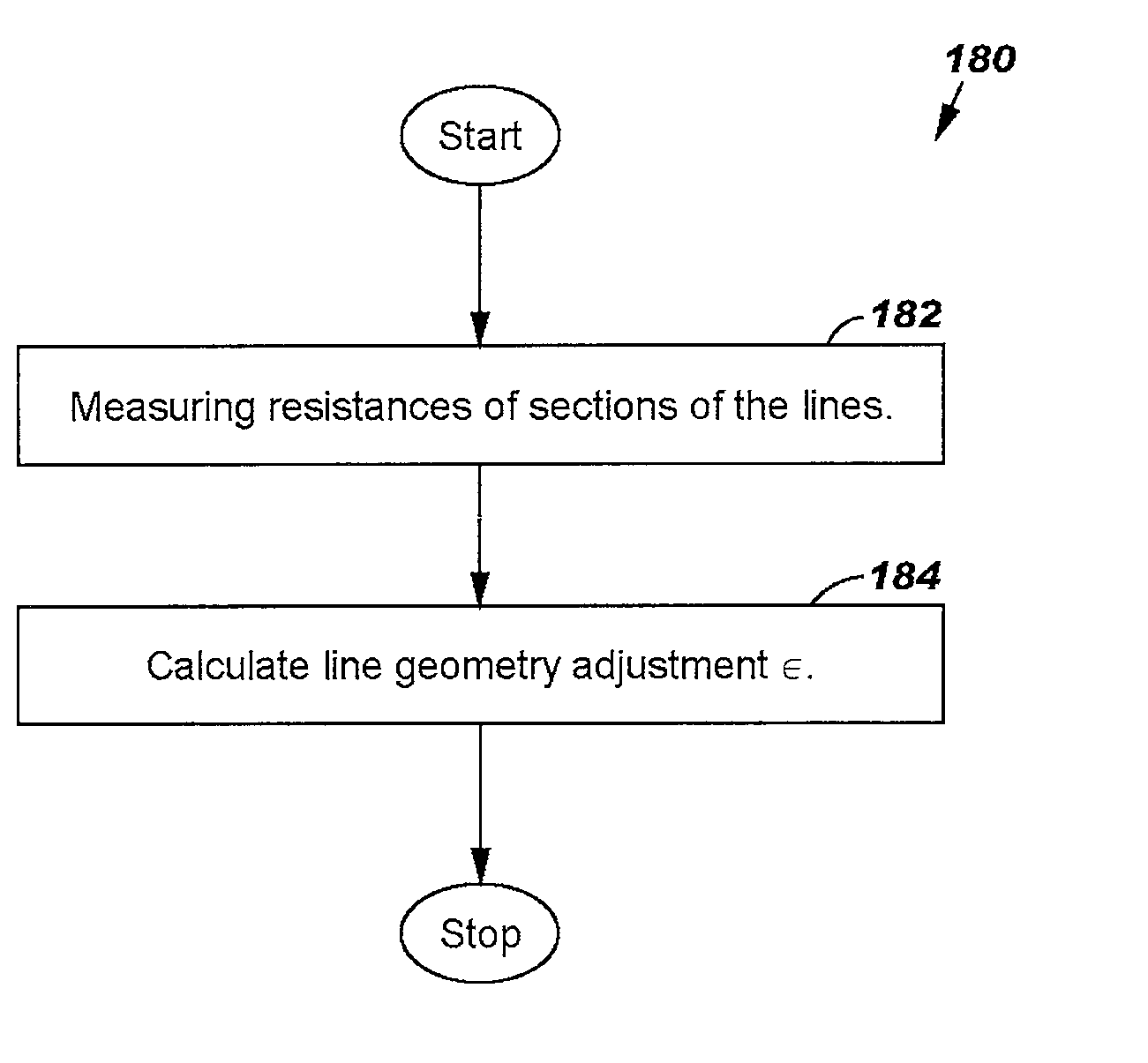

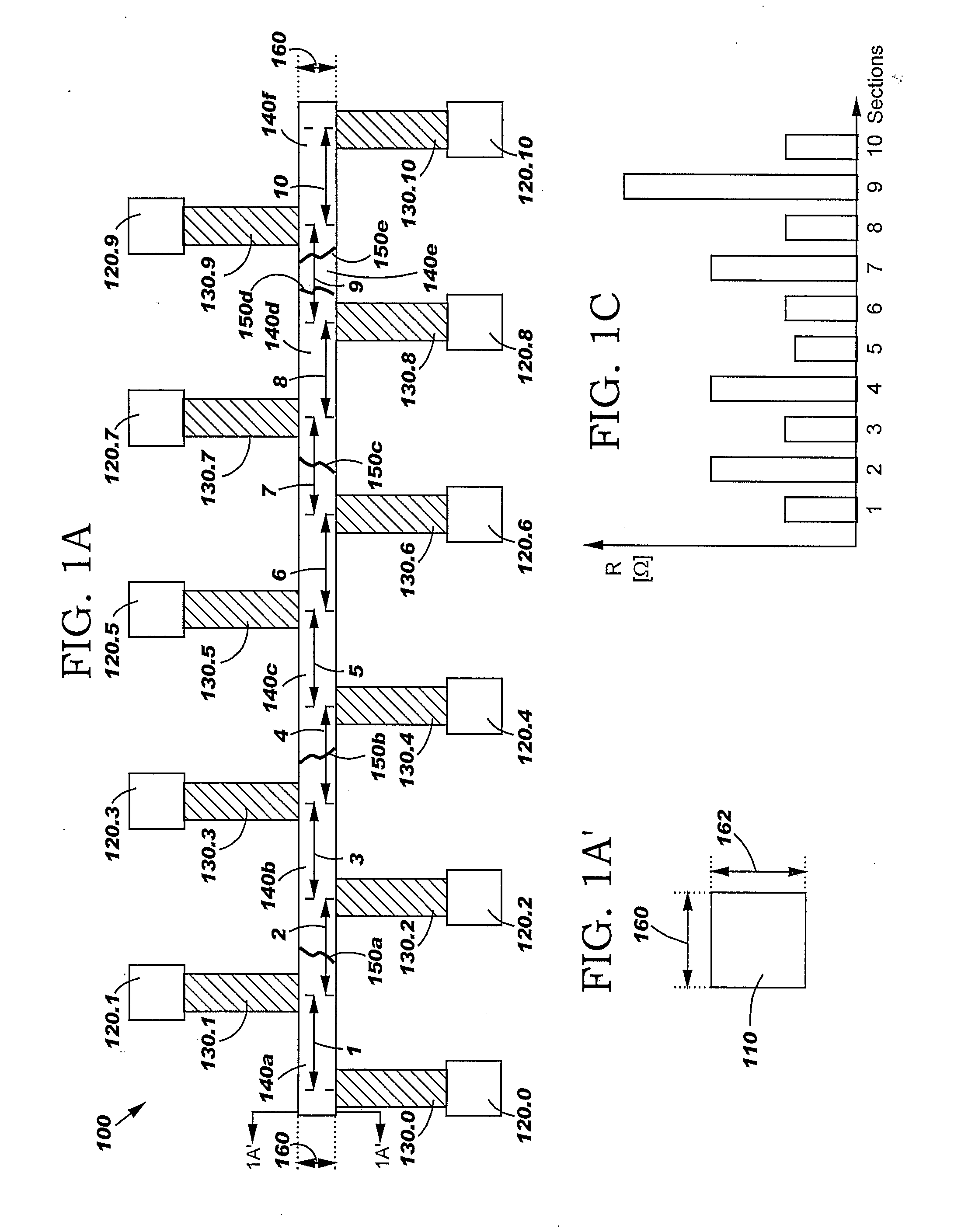

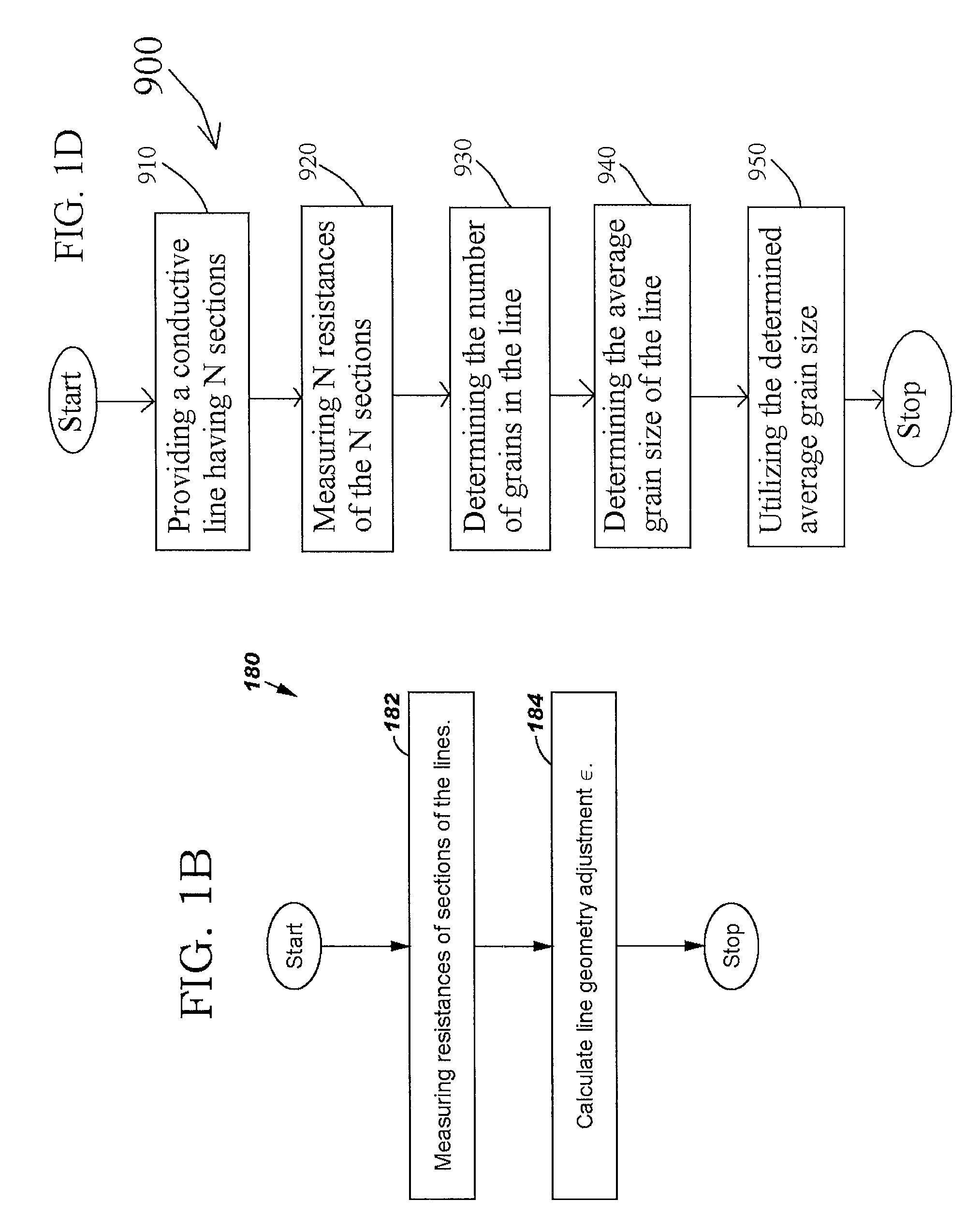

Non-destructive evaluation of microstructure and interface roughness of electrically conducting lines in semiconductor integrated circuits in deep sub-micron regime

InactiveUS20060071676A1Reduction in size of cross sectionEffective line-widthSemiconductor/solid-state device testing/measurementSolid-state devicesNon destructiveElectrical resistance and conductance

Novel structures and methods for evaluating lines in semiconductor integrated circuits. A first plurality of lines can be formed on a wafer each of which comprises multiple line sections. All the line sections are of the same length. The electrical resistances of the line sections are measured. Then, a first line geometry adjustment is determined based on the electrical resistances of all the sections of all the lines. The first line geometry adjustment represents an effective reduction of cross-section size of the lines due to grain boundary electrical resistance. A second plurality of lines of same length and thickness can be formed on the same wafer. Then, second and third line geometry adjustments can be determined based on the electrical resistances of these lines measured at different temperatures. The second and third line geometry adjustments represent an effective reduction of cross-section size of the lines due to grain boundary electrical resistance and line surface roughness.

Owner:GLOBALFOUNDRIES INC

Metal alloy with an abrupt interface to III-V semiconductor

InactiveUS8829567B2Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsSemiconductor structure

Owner:SEMATECH

Non-destructive evaluation of microstructure and interface roughness of electrically conducting lines in semiconductor integrated circuits in deep sub-micron regime

InactiveUS20070130551A1Semiconductor/solid-state device testing/measurementSolid-state devicesElectrical resistance and conductanceNon destructive

Novel structures and methods for evaluating lines in semiconductor integrated circuits. A first plurality of lines are formed on a wafer each of which includes multiple line sections. All the line sections are of the same length. The electrical resistances of the line sections are measured. Then, a first line geometry adjustment is determined based on the electrical resistances of all the sections. The first line geometry adjustment represents an effective reduction of cross-section size of the lines due to grain boundary electrical resistance. A second plurality of lines of same length and thickness can be formed on the same wafer. Then, second and third line geometry adjustments are determined based on the electrical resistances of these lines measured at different temperatures. The second and third line geometry adjustments represent an effective reduction of cross-section size of the lines due to grain boundary electrical resistance and line surface roughness.

Owner:GLOBALFOUNDRIES INC

Pinning field in MR devices despite higher annealing temperature

ActiveUS8325448B2High strengthRaise the ratioMagnetic-field-controlled resistorsSemiconductor/solid-state device manufacturingDiffusionManganese

The pinning field in an MR device was significantly improved by using the Ru 4A peak together with steps to minimize interfacial roughness of the ruthenium layer as well as boron and manganese diffusion into the ruthenium layer during manufacturing. This made it possible to anneal at temperatures as high as 340° C. whereby a high MR ratio could be simultaneously achieved.

Owner:HEADWAY TECH INC

Semiconductor device and method of manufacturing the same

ActiveUS8222099B2Reduce EOTInhibited DiffusionTransistorSolid-state devicesDielectricGate dielectric

A semiconductor device and a method of manufacturing the same are provided. A multi-component high-k interface layer containing elements of the substrate is formed from a ultra-thin high-k dielectric material in a single-layer structure of atoms by rapid annealing in the manufacturing of a CMOS transistor by the replacement gate process, and a high-k gate dielectric layer with a higher dielectric constant and a metal gate layer are formed thereon. The EOT of the device is effectively decreased, and the diffusion of atoms in the high-k gate dielectric layer from an upper level thereof is effectively prevented by the optimized high-k interface layer at high-temperature treatment. Thus, the present invention may also avoid the growth of the interface layers and the degradation of carrier mobility. Furthermore, the present invention may further alleviate the problem of high interface state and interface roughness caused by direct contact of the high-k gate dielectric layer with high dielectric constant and the substrate, and thus the overall performance of the device is effectively enhanced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

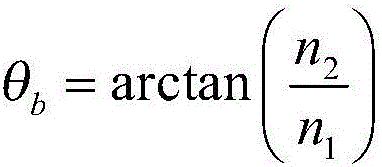

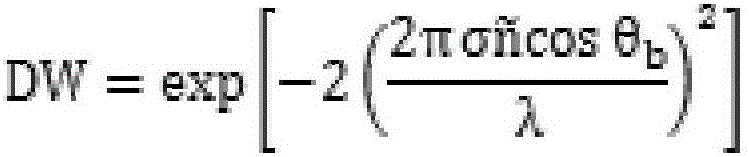

Method for detecting low sub surface damages of rigid brittle optical material

InactiveCN106501279ASimple structureImprove accuracyOptically investigating flaws/contaminationUsing optical meansMicro structureSurface structure

The invention relates to a method for detecting low sub surface damages of a rigid brittle optical material. The method is characterized by obtaining a Brewster angle of a to-be-detected sample through preparation of a tester and detection on sample surface damages and further utilizing the Brewster angle to represent the surface interface roughness of the sample, wherein the tester comprises a dial, an object stage, a laser, a first polarizing film, a light intensity meter and a second polarizing film. According to the method disclosed by the invention, the structure is simple, the cost is low, the size of the Brewster angle of light rays incident to the sample can be accurately measured by utilizing linearly polarized light, the Brewster angle is used for representing the surface interface roughness of the sample, the measurement deviation can be kept within one percent, and the accuracy of a detection result is high; the method for detecting the low sub surface damages of the rigid brittle optical material is simple and rapid, and the surface of the to-be-detected sample is not damaged; meanwhile, the method disclosed by the invention can also be used for measuring other micro surface structures of an optical element and is capable of achieving nano-scale surface micro structure detection, and a condition is provided for preparing a high-quality high-damage threshold thin film.

Owner:CHINA WEAPON SCI ACADEMY NINGBO BRANCH

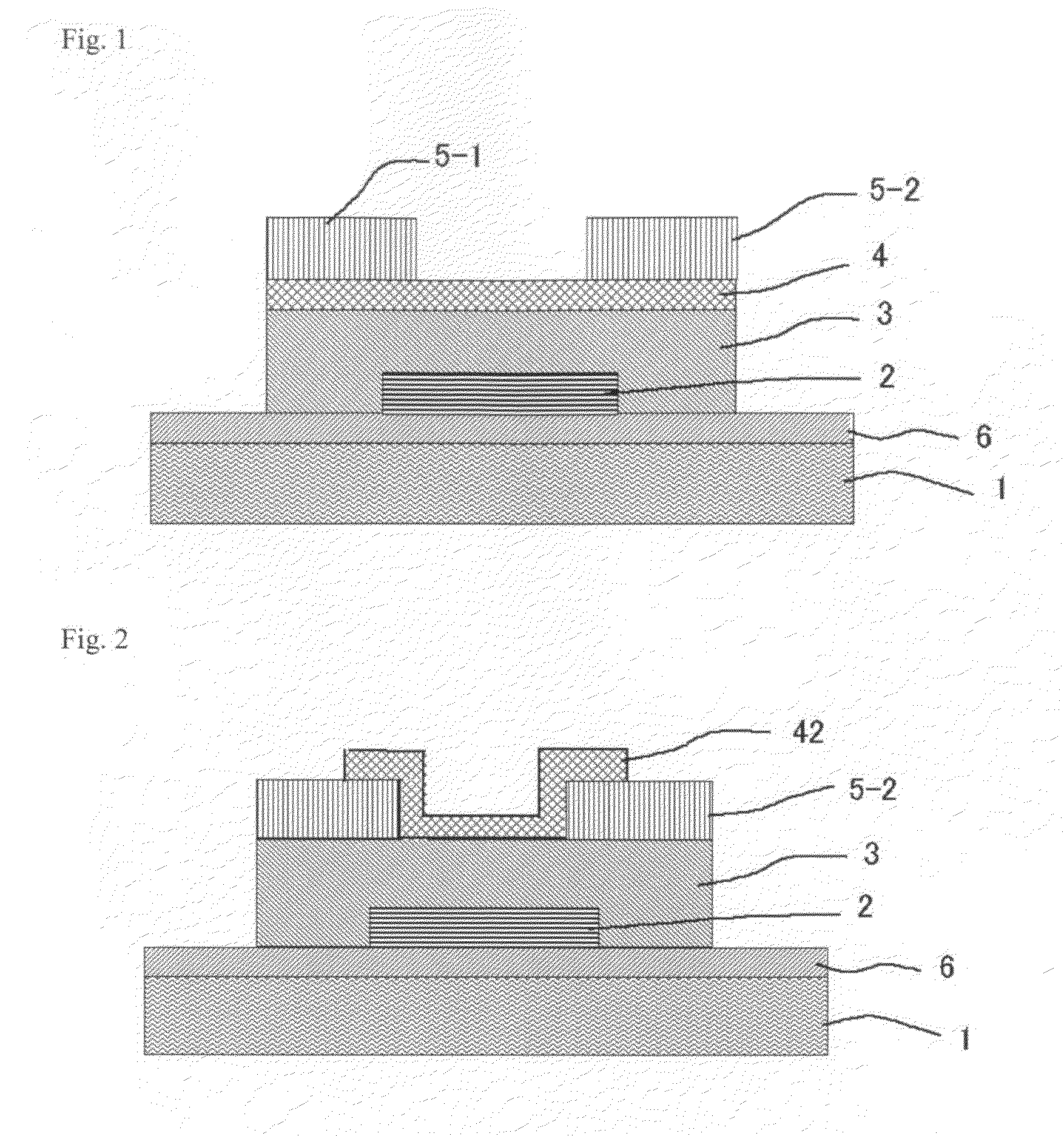

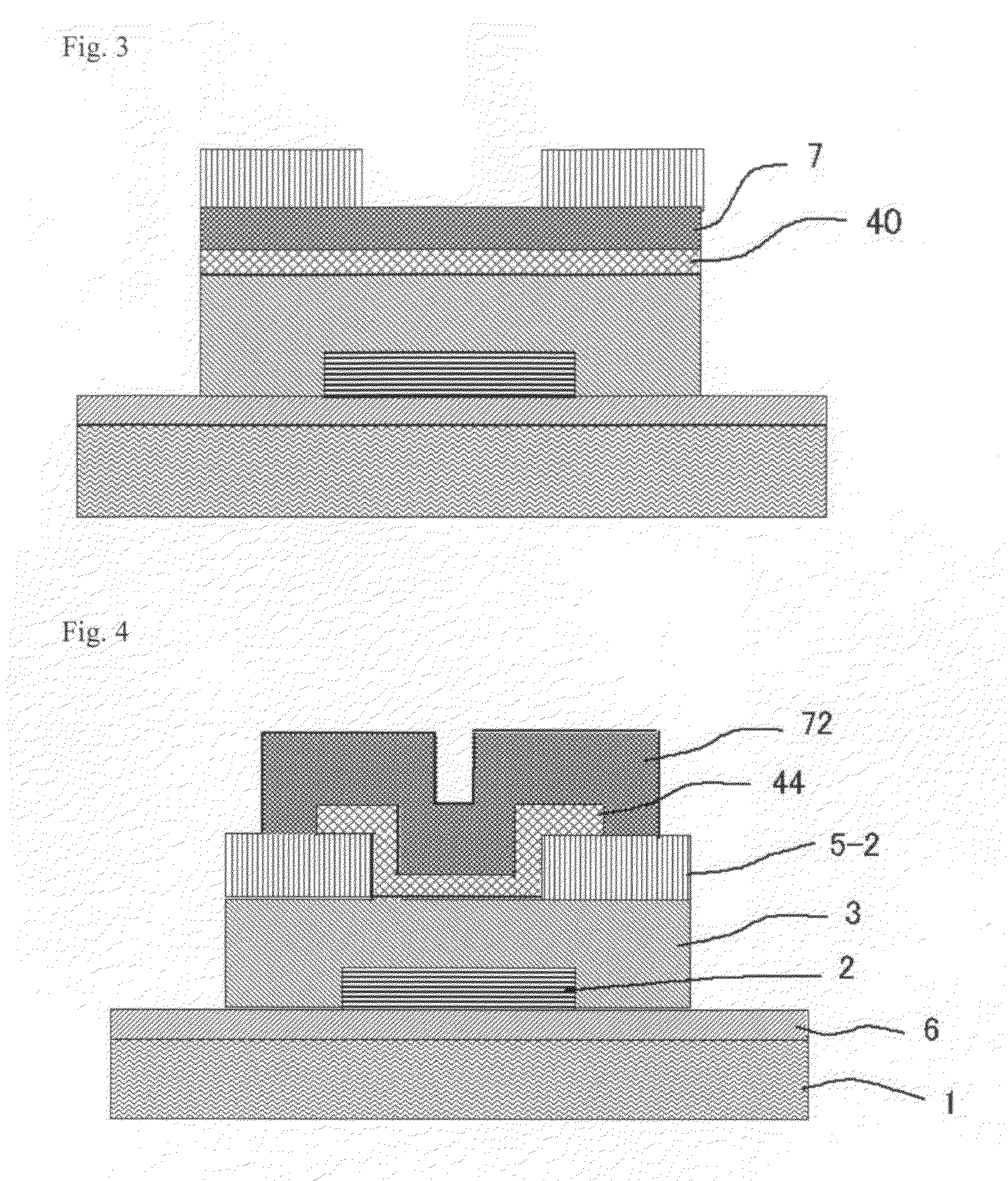

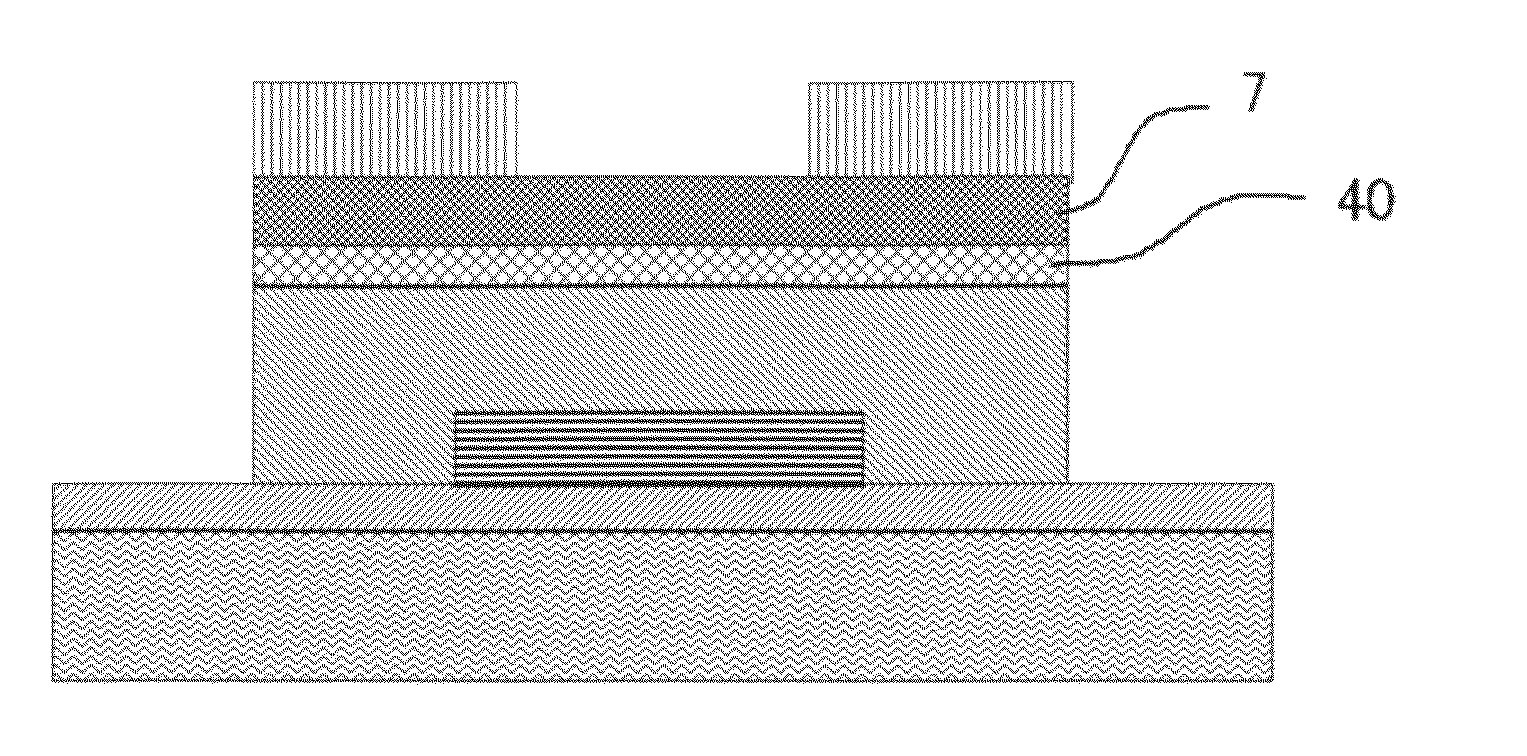

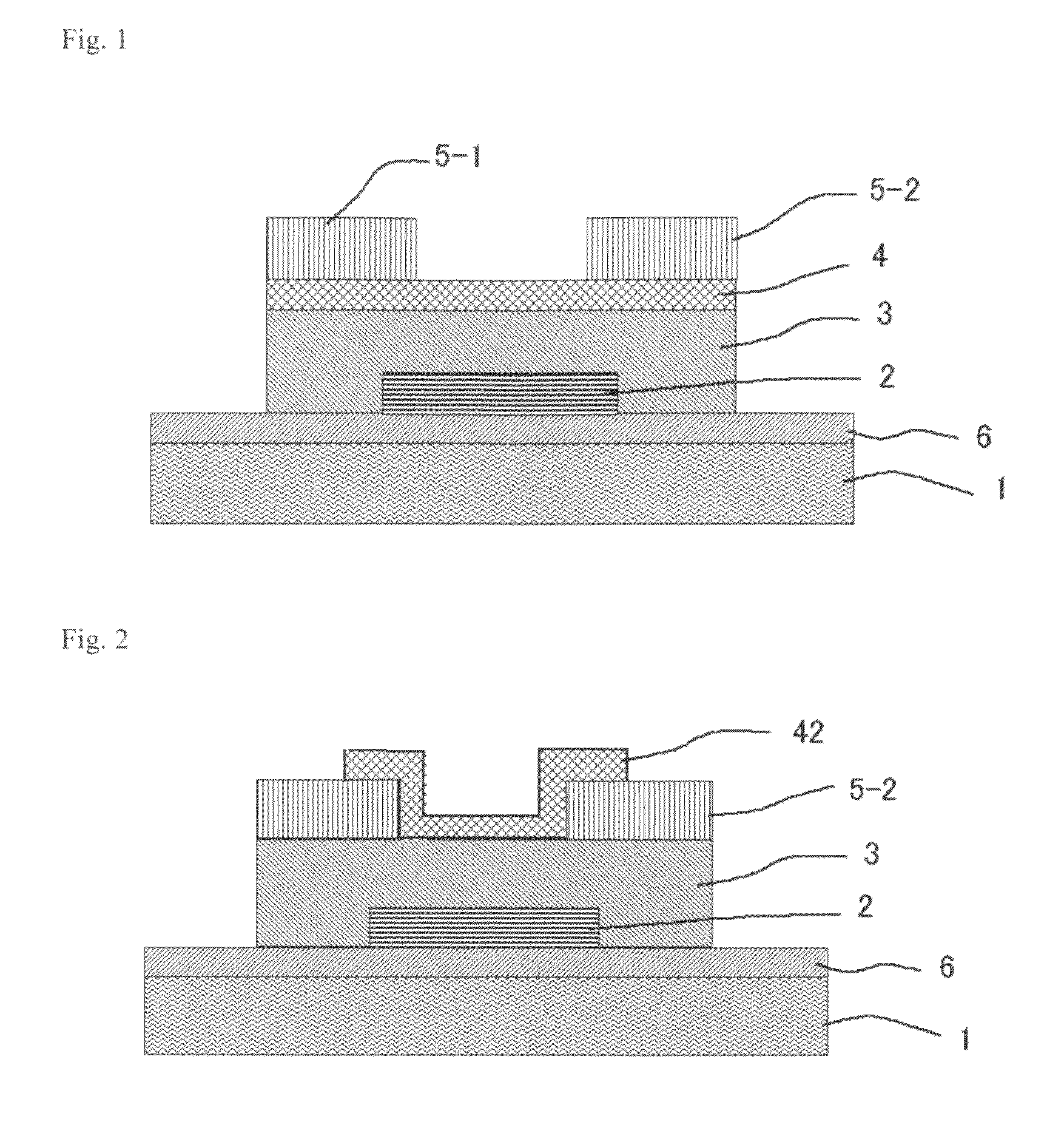

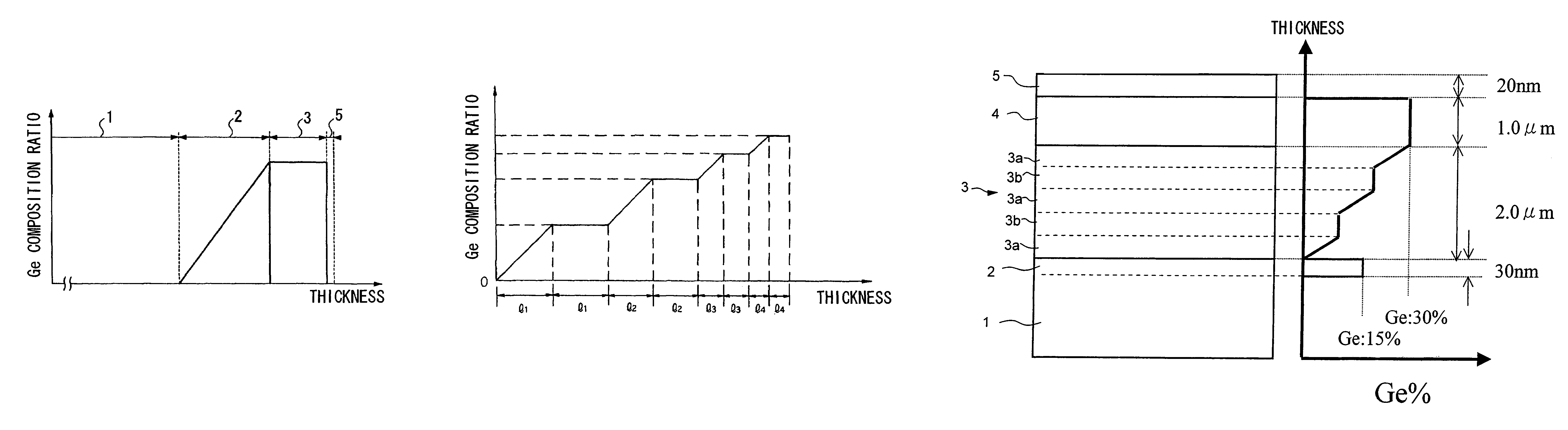

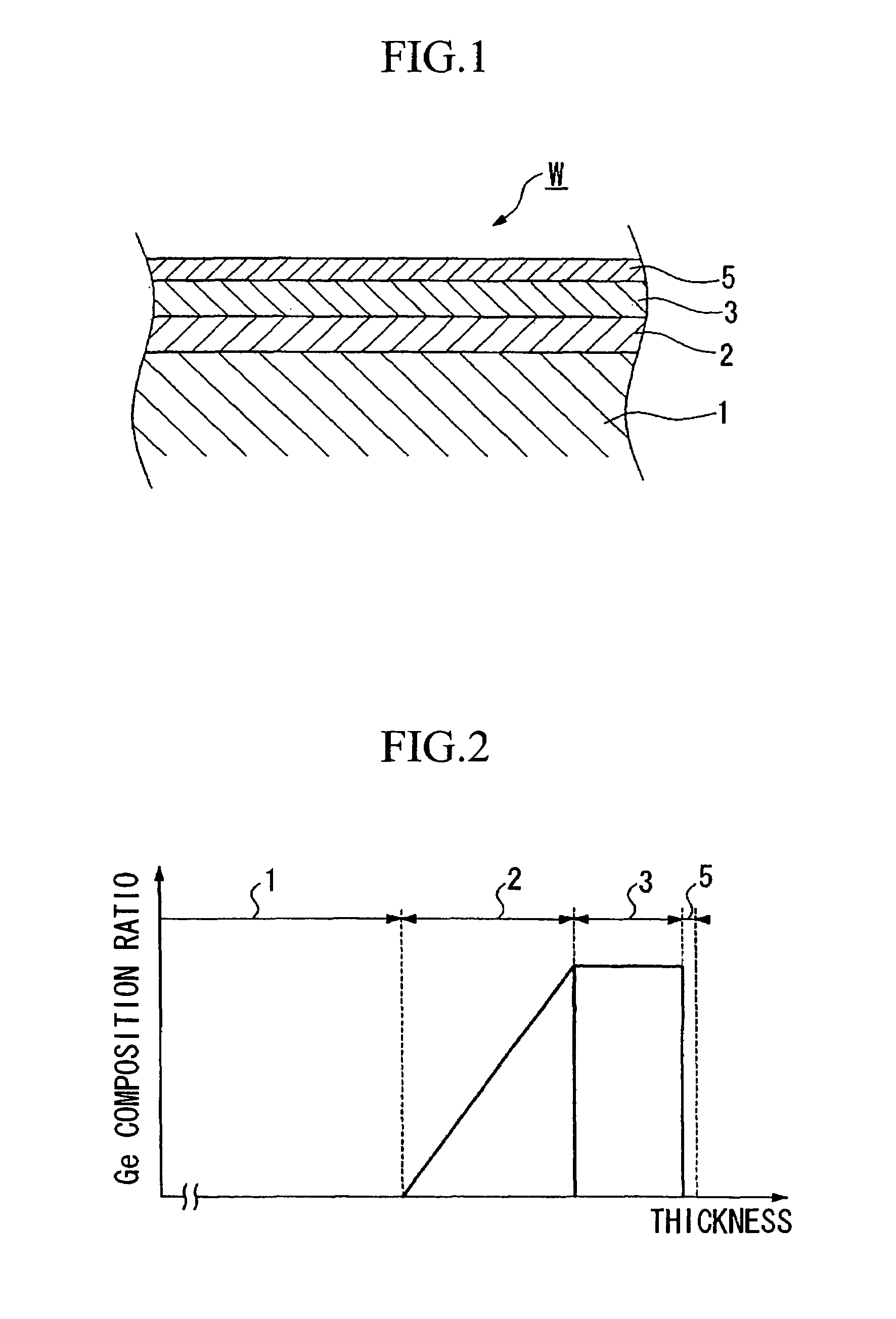

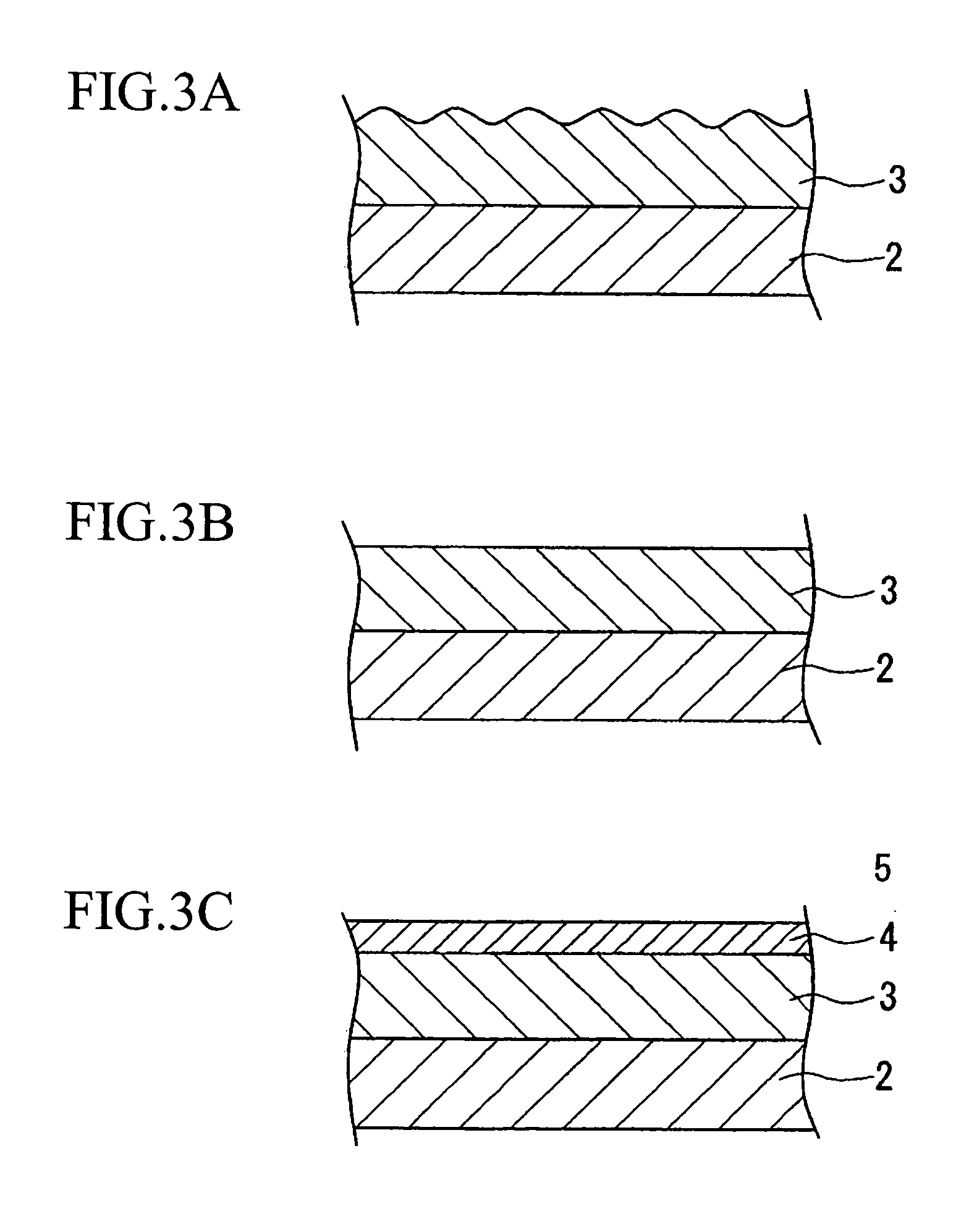

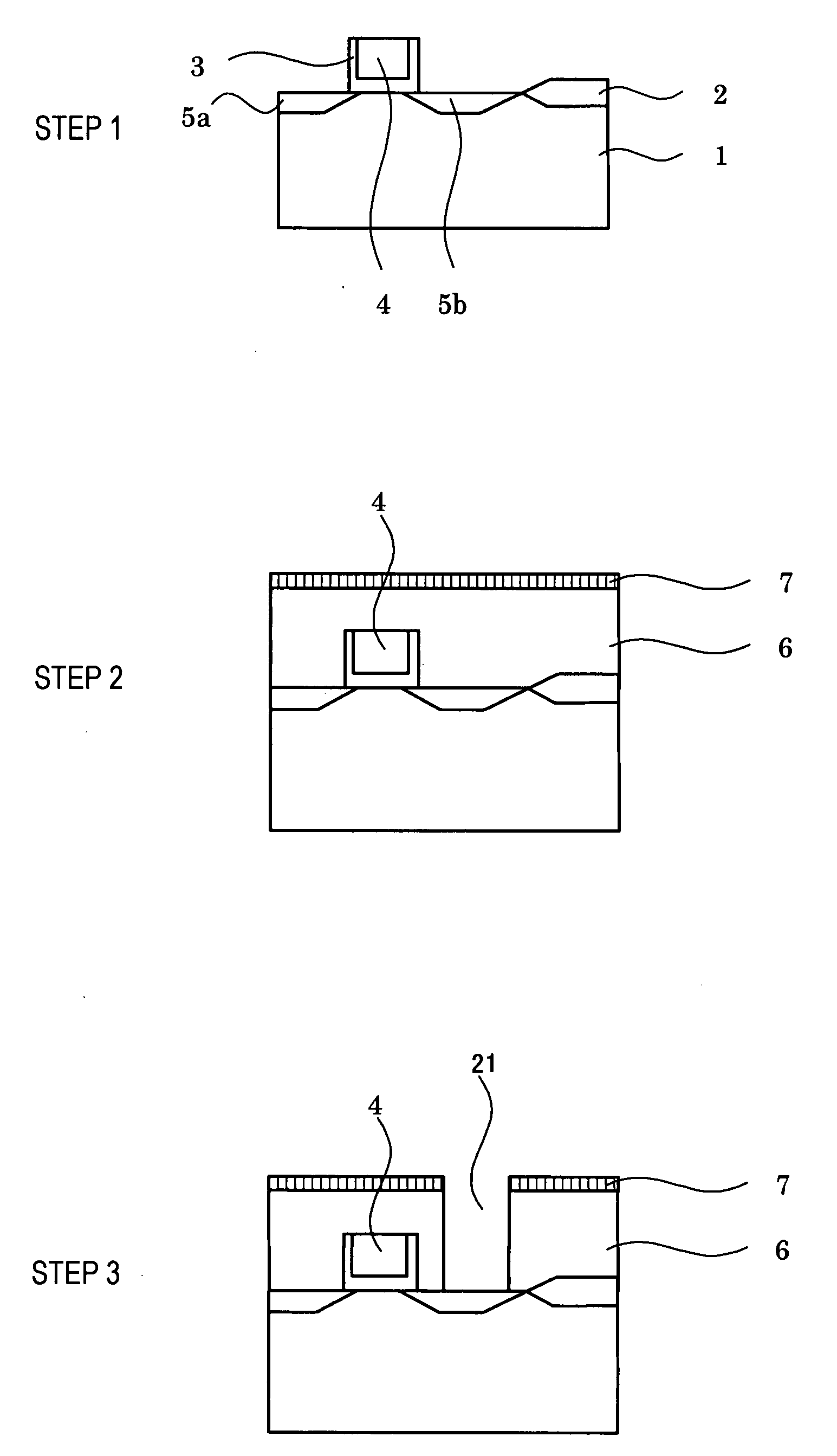

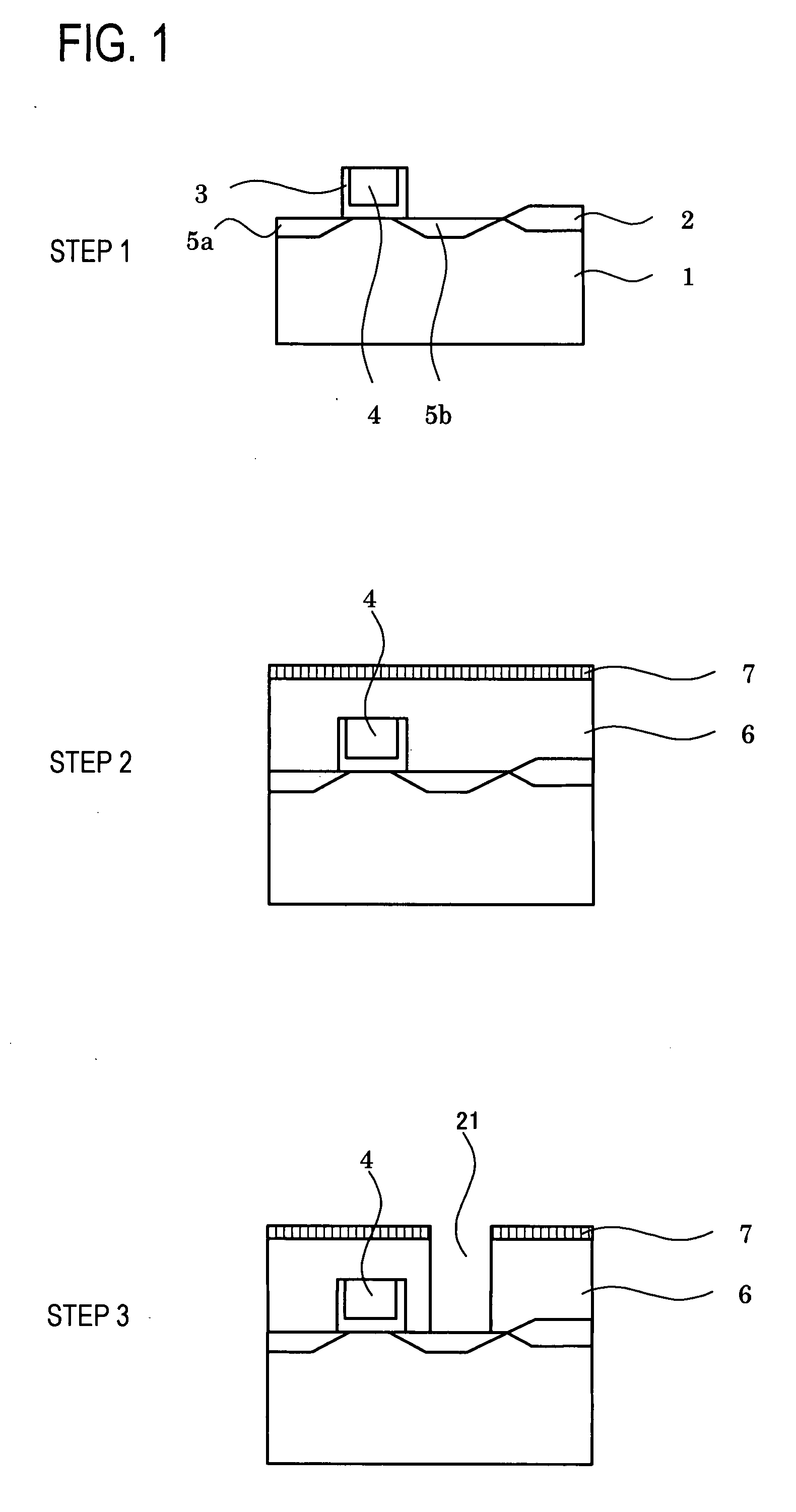

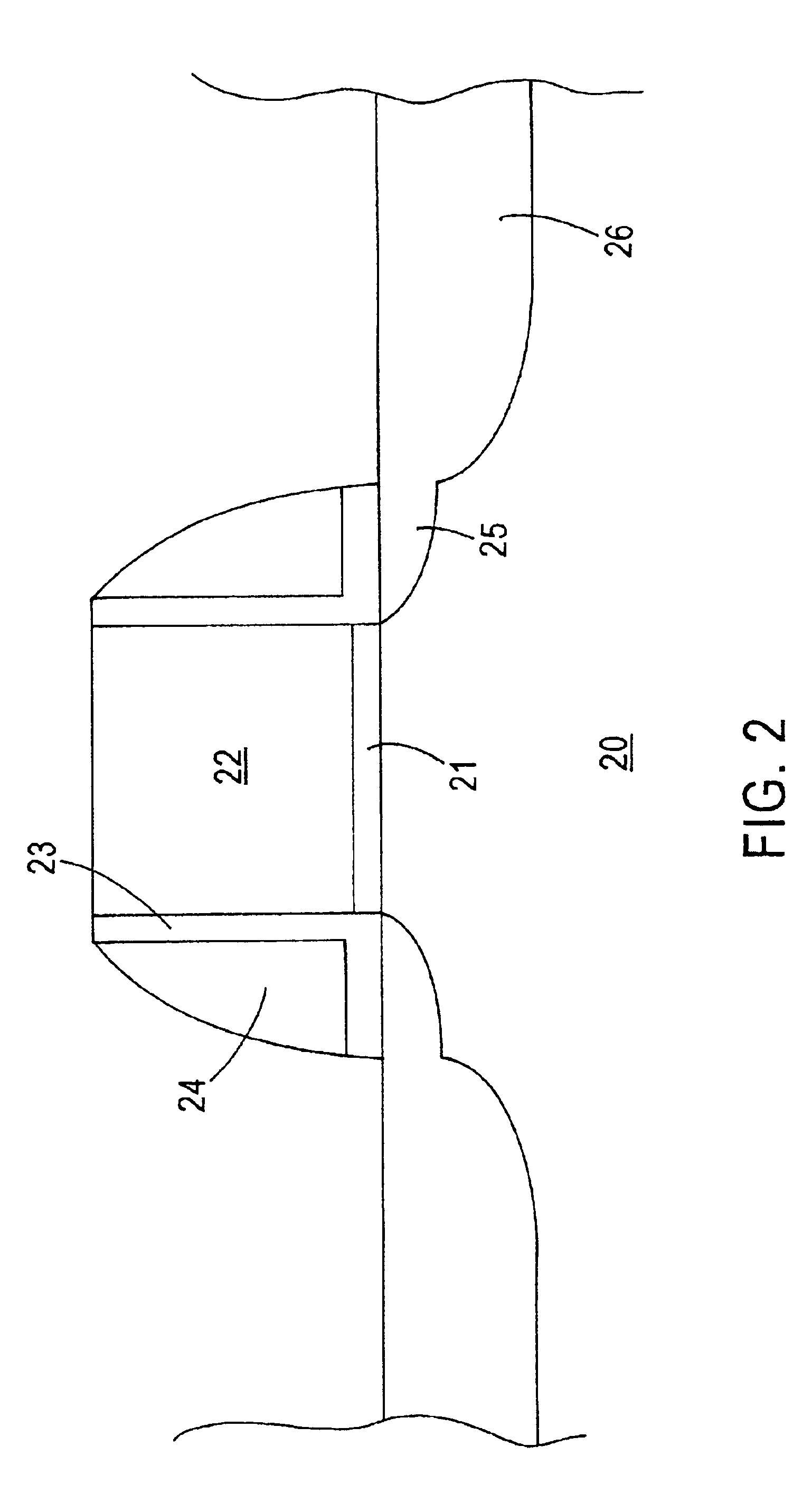

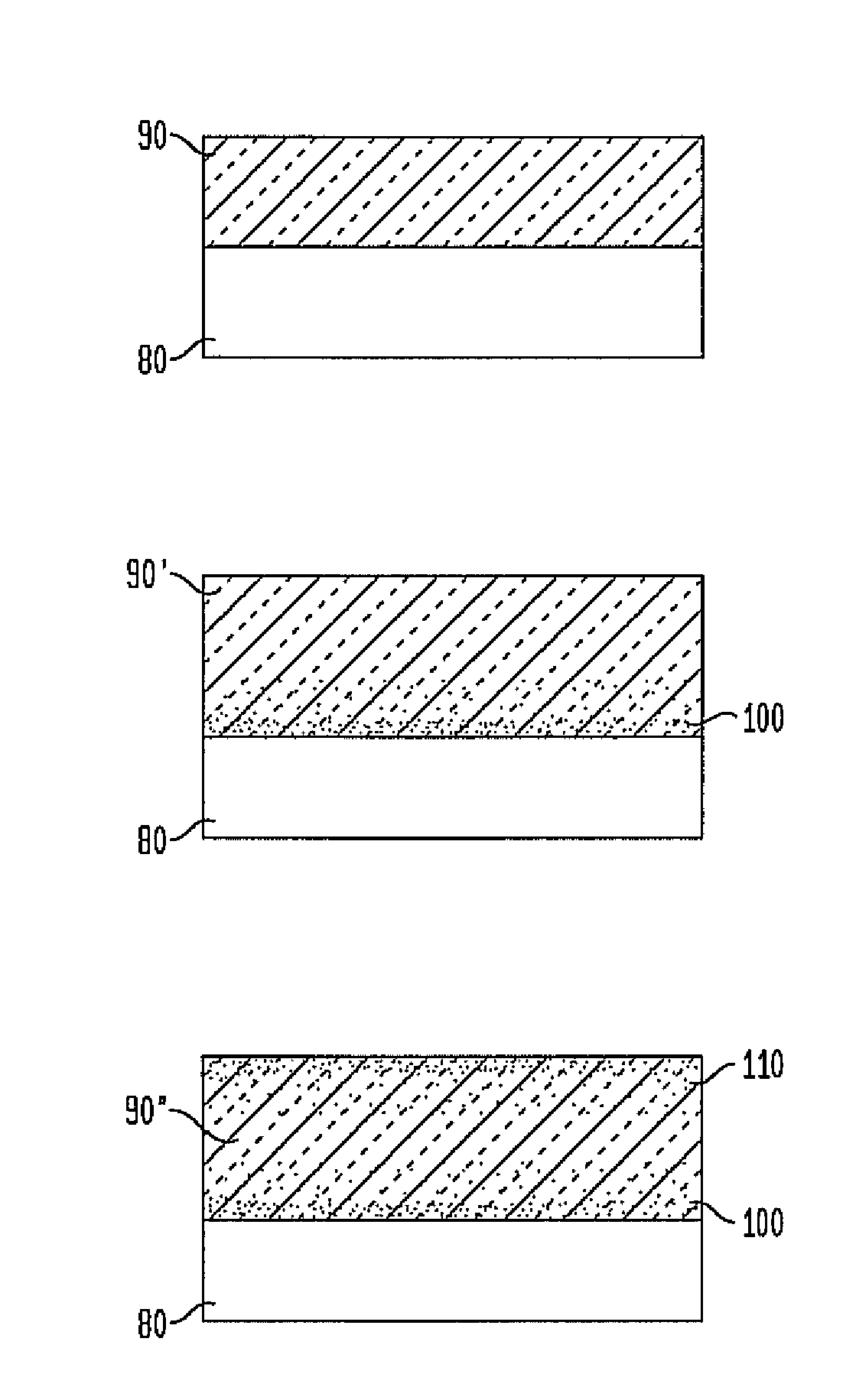

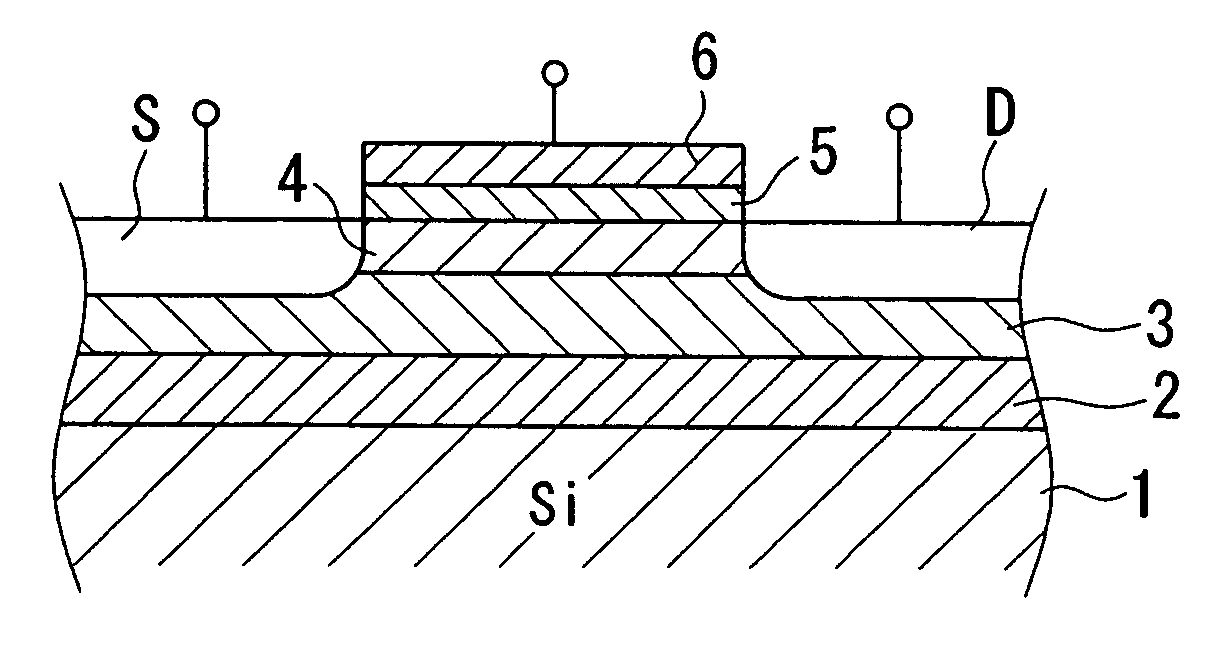

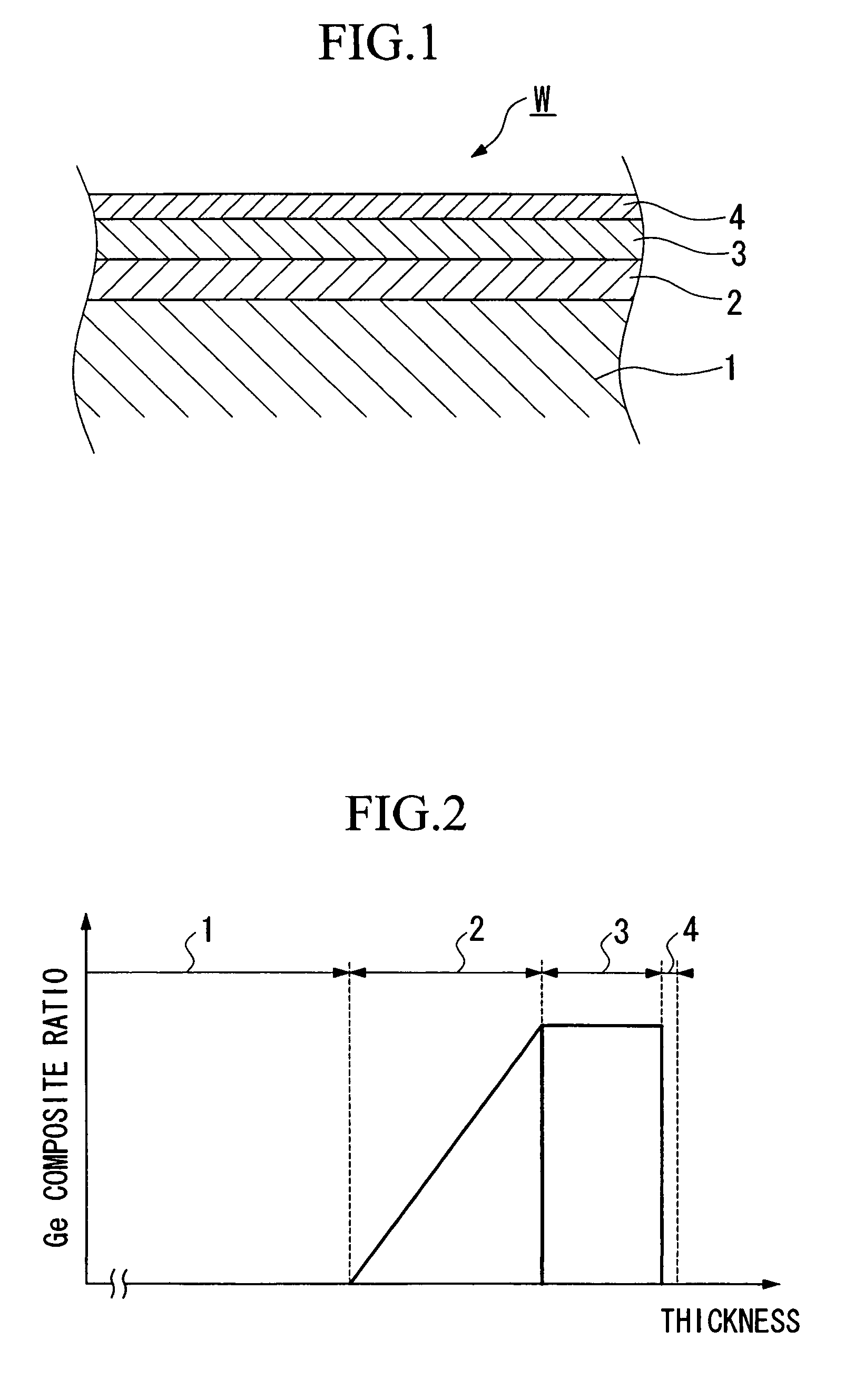

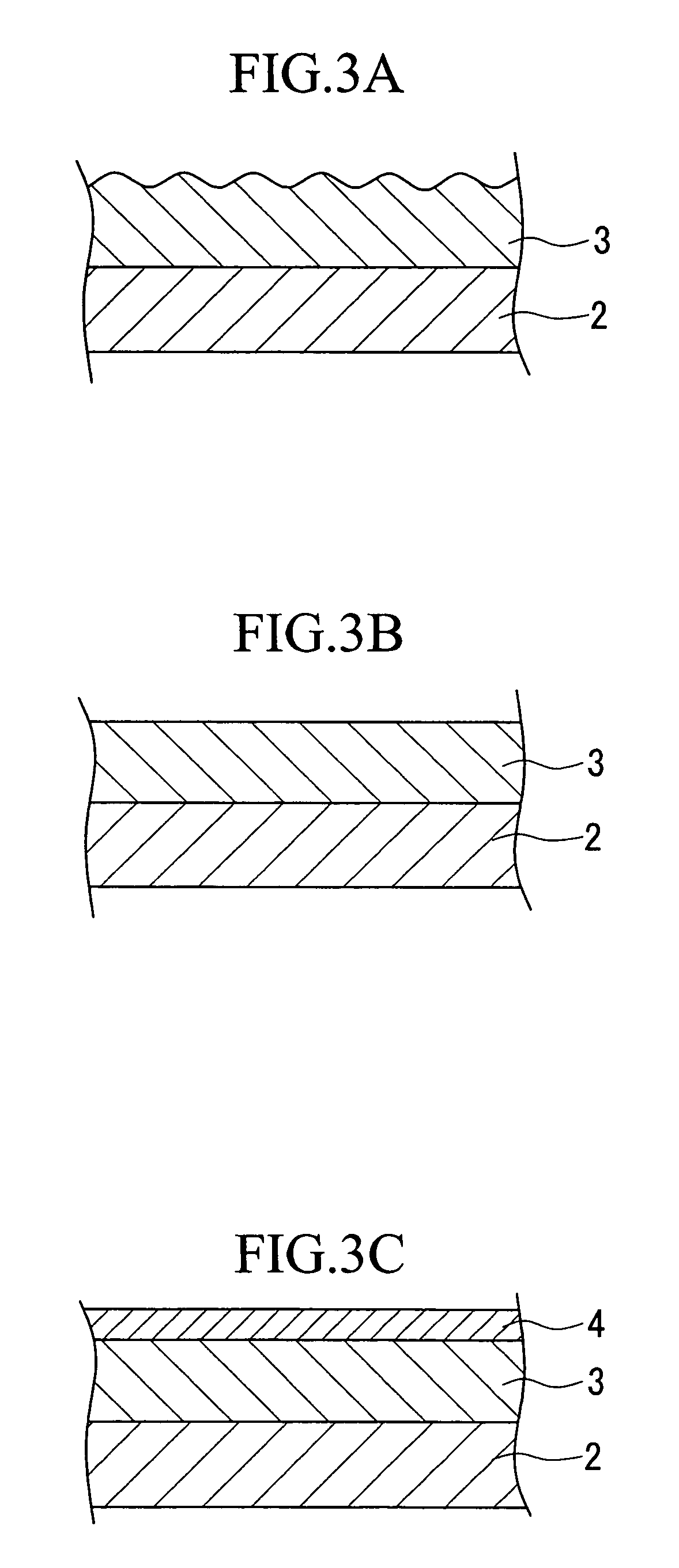

Production method for semiconductor substrate and production method for field effect transistor and semiconductor substrate and field effect transistor

InactiveUS7056789B2Worsening of roughnessWorsening of surfaceSolid-state devicesSemiconductor/solid-state device manufacturingSurface roughnessEngineering

The present invention relates to a semiconductor substrate production method, field effect transistor production method, semiconductor substrate and field effect transistor which, together with having low penetrating dislocation density and low surface roughness, prevent worsening of surface and interface roughness during heat treatment of a device production process and so forth. A production method of a semiconductor substrate W, in which SiGe layers 2 and 3 are formed on an Si substrate 1, is comprised of a heat treatment step in which heat treatment is performed either during or after the formation of the SiGe layers by epitaxial growth, at a temperature that exceeds the temperature of the epitaxial growth, and a polishing step in which irregularities in the surface formed during the heat treatment are removed by polishing following formation of the SiGe layers.

Owner:SUMITOMO MITSUBISHI SILICON CORP