Low-temperature polycrystalline silicon thin film transistor, manufacturing method, array substrate, and display panel

A technology of thin-film transistors and low-temperature polysilicon, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as interface defect state density, interface roughness, etc., to improve characteristics, simplify manufacturing process, and reduce interface roughness and the effect of interface defect state density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

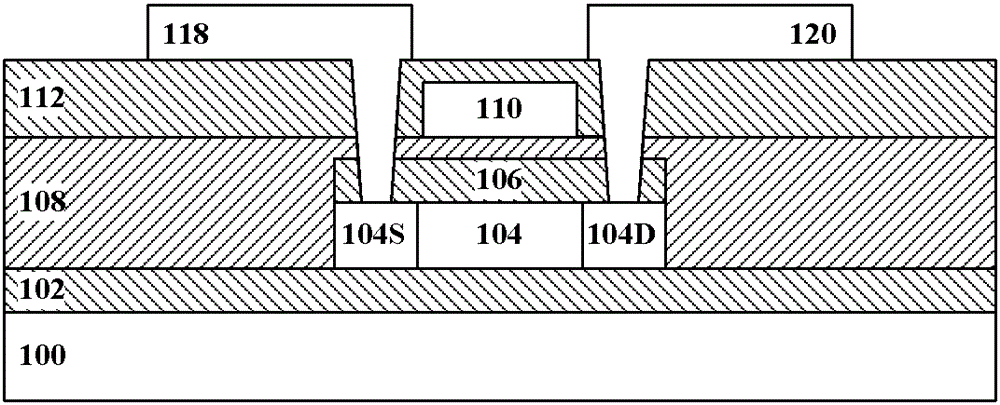

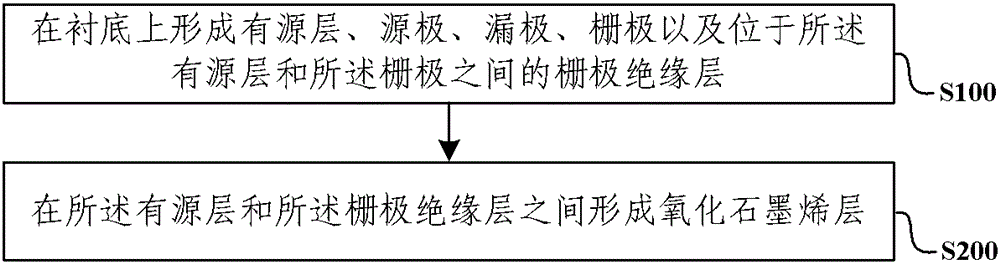

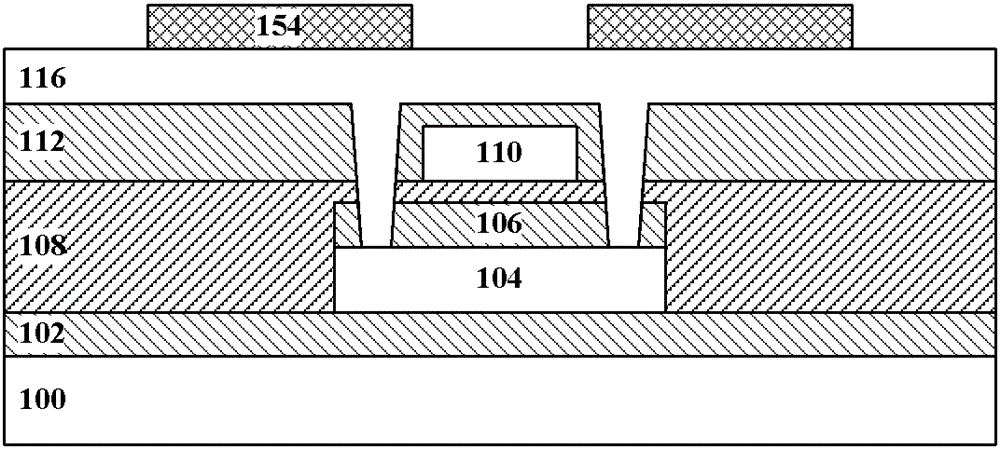

[0044] The specific implementation modes of the low-temperature polysilicon thin film transistor and its manufacturing method, array substrate, and display panel of the present disclosure will be described in detail below with reference to the accompanying drawings. The drawings of the present disclosure schematically show structures, parts and / or steps related to the invention, but not or only partially show structures, parts and / or steps not related to the invention. The thickness and shape of each film layer in the drawings do not reflect the true scale, but are only intended to schematically illustrate the content of the present disclosure.

[0045] The components shown in the drawings are labeled as follows:

[0046] 100, 200 substrates;

[0047] 102, 202 buffer layer;

[0048] 104, 210 active layer;

[0049] 104S source contact region;

[0050] 104D drain contact region;

[0051] 106, 208 graphene oxide layers;

[0052] 108, 206 gate insulation layer;

[0053] 110...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More