Universal multi-operand summator

A multi-operand and adder technology, applied in the electronic field, can solve the problems of synchronous and parallel addition of operands, increasing operation time, etc., and achieve the effects of reducing time consumption, increasing scalability, and reducing hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the accompanying drawings. Note that what is described below is a representative embodiment of the present invention, and the understanding of the present invention should not be limited to the following description.

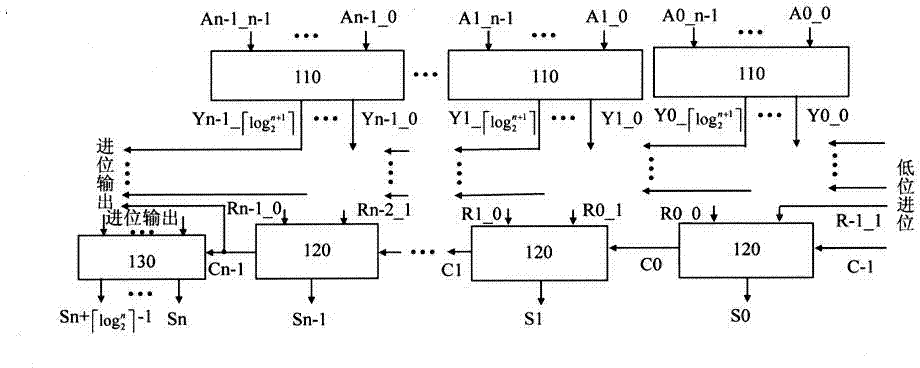

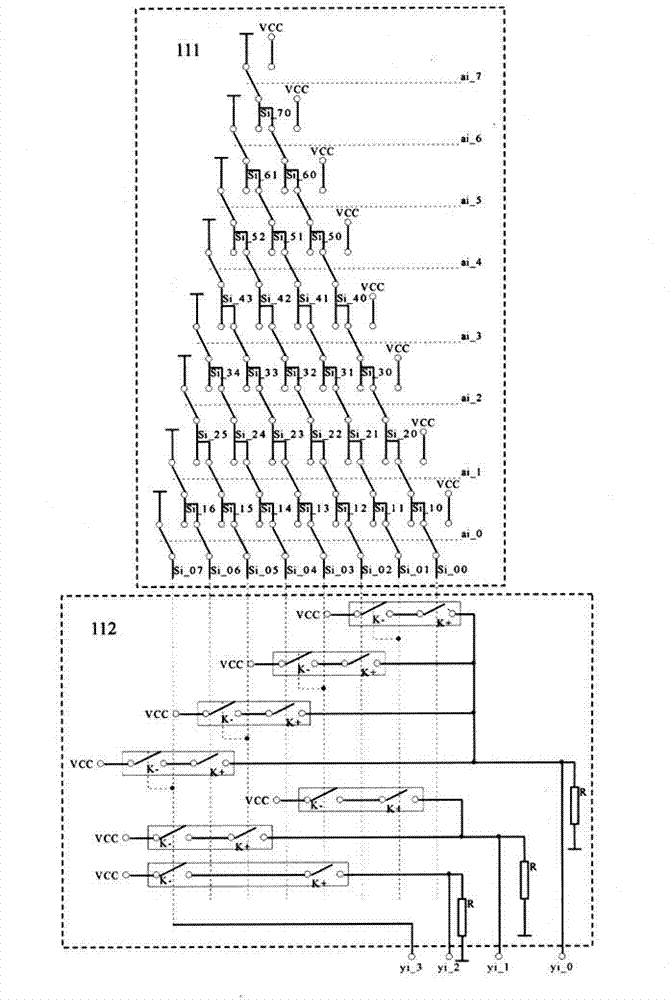

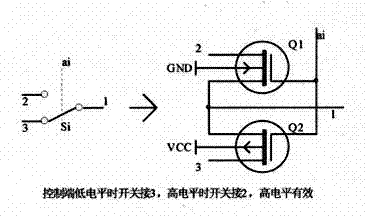

[0028] figure 1 It is a principle block diagram of the present invention. It mainly consists of a plurality of adder modules 110 for one-bit binary numbers, two adder modules 120 for one-bit binary numbers and a carry synthesis module 130 . The invention first uses the module 110 to perform synchronous parallel calculations on all operand values corresponding to each bit weight, and then reorganizes the addition numbers of each bit according to the corresponding relationship of the bit weights for the calculation results of all bits, and uses the module 110 again, and so on until the reorganization After that, each bit weight has only 2 addition n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More