Through silicon via (TSV) exposure process

A process and semiconductor technology, applied in the field of microelectronics, can solve problems such as unmet requirements and problems with TSV electrical connection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

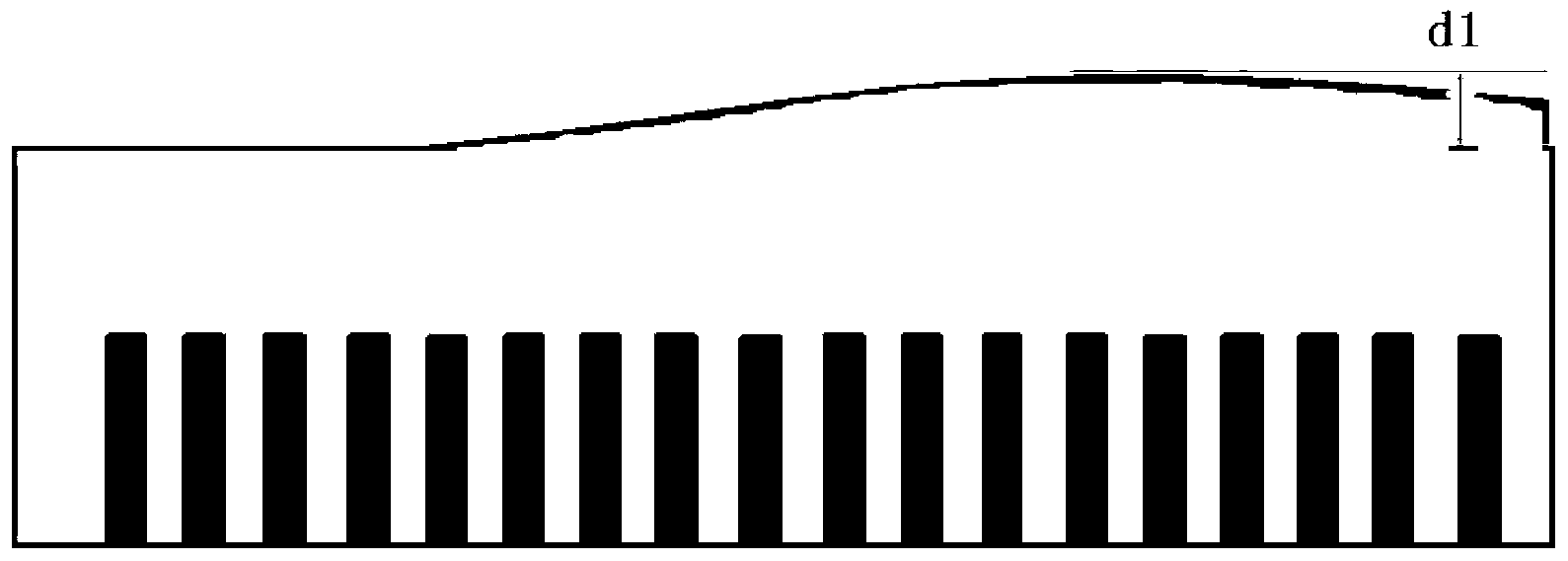

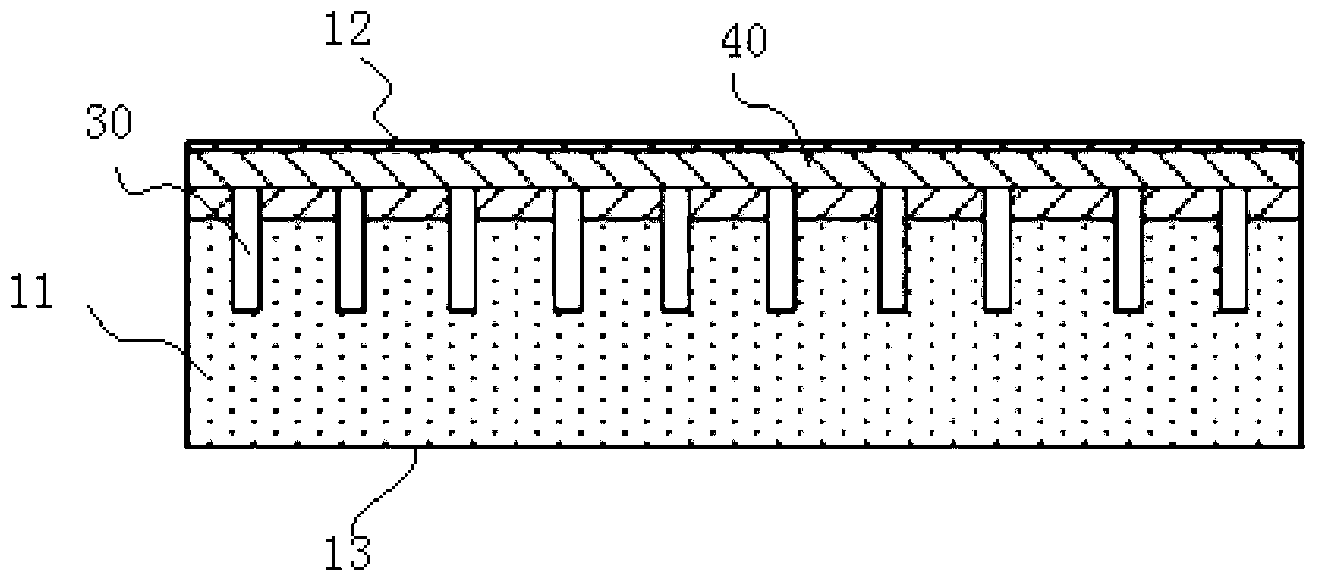

[0023] As mentioned in the background technology, in the existing TSV outcropping process, when the mechanical grinding machine is grinding, the thickness variation (TTV) d1 of the wafer surface is controlled at 2.5 microns, and this variation will be wet ( / dry) in the next step In the method etching outcrop, it is maintained due to the isotropy of the etching. As a result, after the etching is completed, the heights of the TSV outcrops in different regions are different, and the height of the TSV outcrop in some places may meet the requirements, while the height of the TSV outcrop in some places may not meet the requirements. Taking the outcrop height of 10 μm as an example, in the thicker areas of the wafer, the exposed copper may only be 7-8 μm, which will cause problems in the subsequent electrical connection of TSVs in these areas.

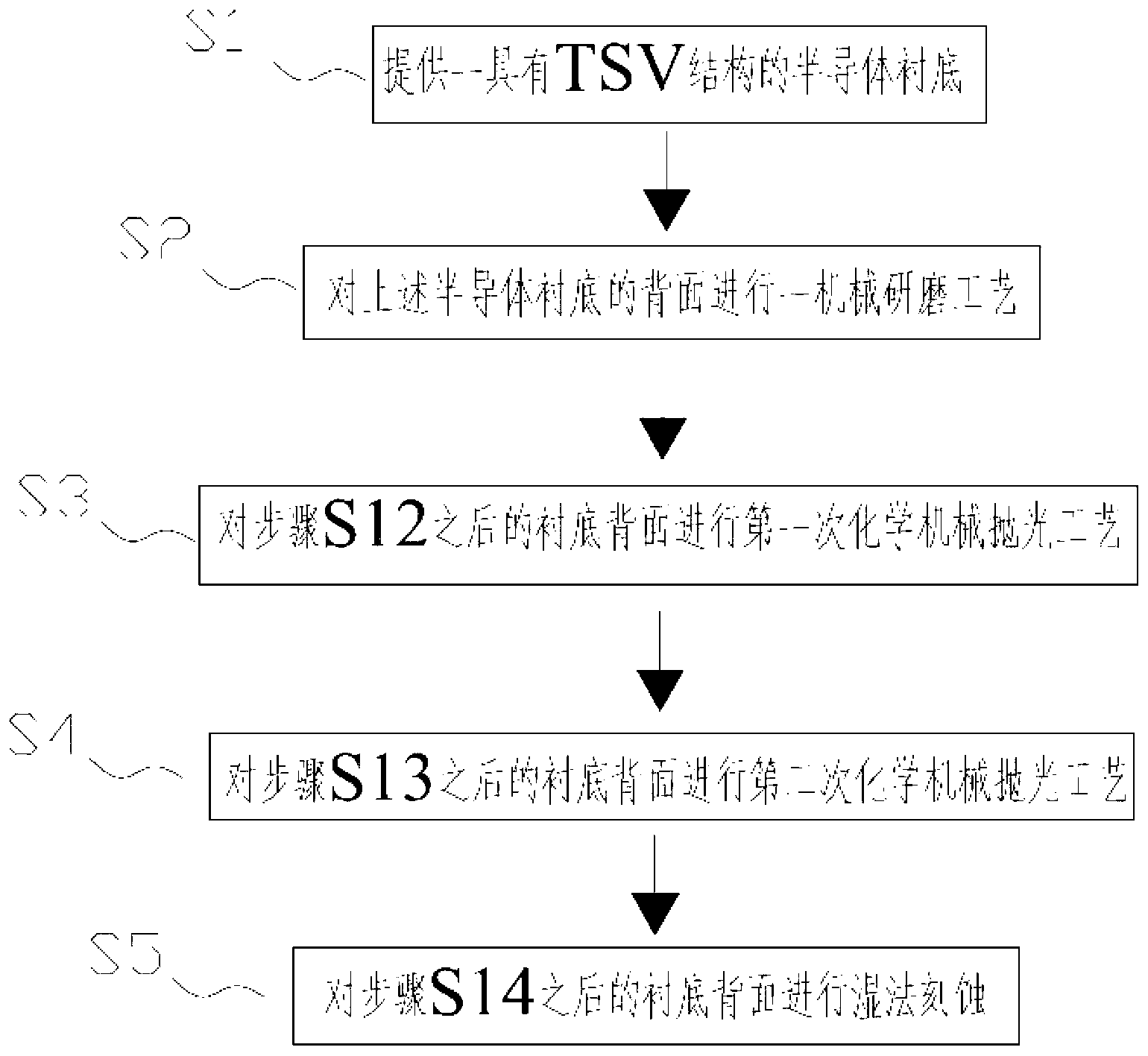

[0024] Therefore, in response to these problems, the present invention proposes a new TSV outcropping process, which can not only avoid the ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap