Hybrid dram memory and method for reducing power consumption when the dram memory is refreshed

A memory and main memory technology, applied in the fields of instruments, electrical digital data processing, energy-saving computing, etc., can solve the problems of no reduction in refresh power consumption, increase in cost, and high process requirements, and achieve lower refresh power consumption, lower power consumption, and higher The effect of refresh cycles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0055] Although the ability of the end memory cells to hold data is very poor, the hold time of more than 99% of the memory cells can reach more than 1s. Based on the above analysis, the present invention proposes a structure of a hybrid DRAM memory, Figure 7 It is a structural schematic diagram of the hybrid DRAM memory of the present invention; as Figure 7 As shown, the hybrid DRAM memory includes a DRAM main memory, a non-volatile memory and a logic detection module, and the DRAM main memory is connected with the logic detection module in bidirectional communication, and can detect the working status of the DRAM main memory, such as The access frequency and refresh frequency of the DRAM main memory. If the access frequency is greater than or equal to the refresh frequency, it indicates that the DRAM main memory is in a busy state, and the DRAM main memory operates in the original refresh mode, and the refresh cycle is the second refresh time. At this time, the logic detec...

Embodiment 2

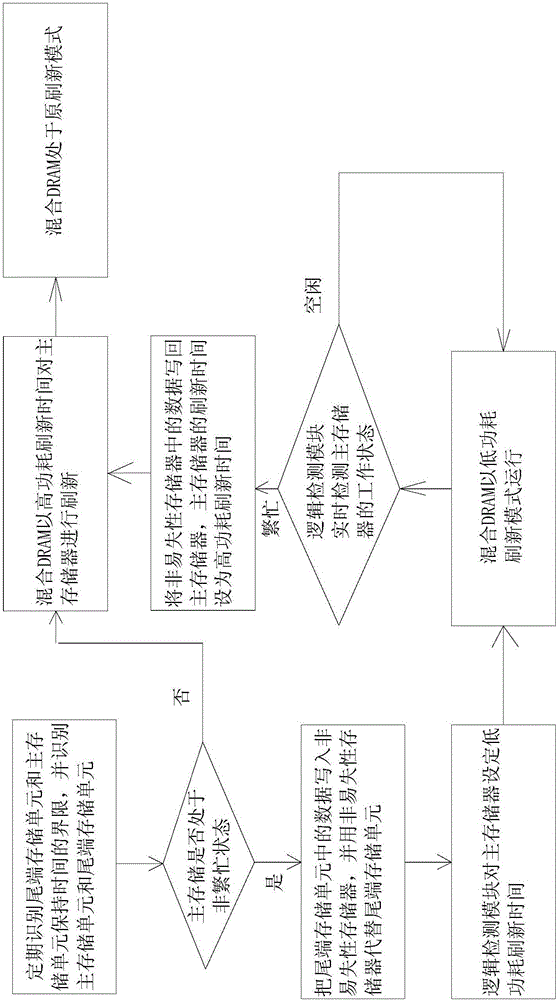

[0060] This embodiment discloses a method for implementing a hybrid dynamic random access memory, Figure 9 For the flow chart that the hybrid DRAM memory function of the present invention realizes; As Figure 9 As shown, its methods include:

[0061] Step 1: The logic detection module detects the data storage time of each storage unit at intervals, and divides the storage units into tail storage units and main storage units according to the detected data storage time of the storage units.

[0062] Step 2: When the hybrid DRAM memory is in a normal working state, the logic detection module will detect the working state of the DRAM main memory: that is, whether the DRAM main memory is in a busy state, such as the DRAM main memory access frequency is greater than or equal to the refresh frequency of the hybrid DRAM. The power consumption of the hybrid DRAM is mainly from the access to the hybrid DRAM, and the refresh power consumption of the hybrid DRAM can be ignored. At this...

Embodiment 3

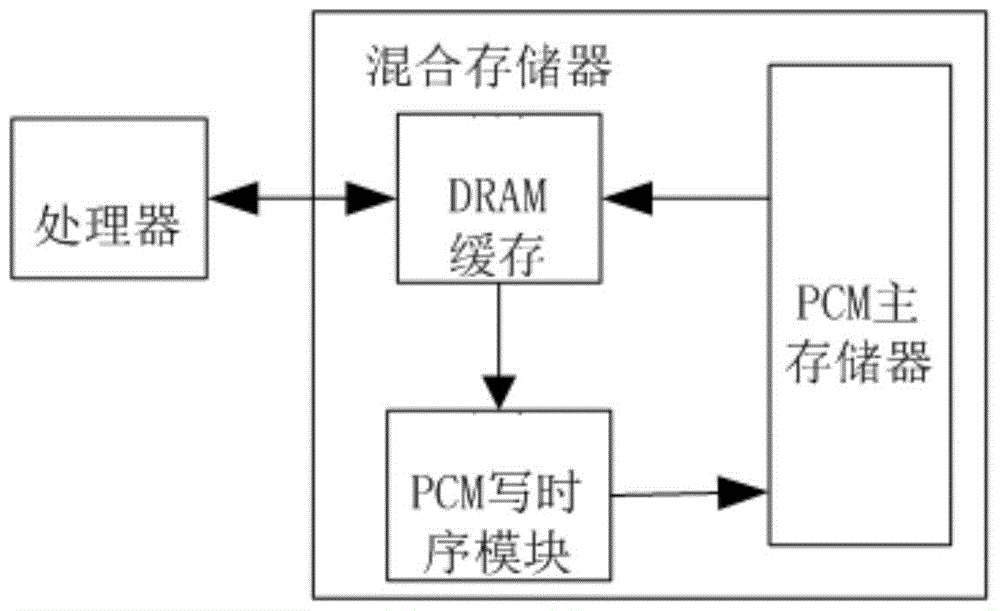

[0067] The hybrid DRAM memory structure in this embodiment is applied to non-volatile dynamic memory (NVDIMM) (such as image 3 ) products, the purpose is to reduce the refresh power consumption of the internal DRAM main memory. Compared with the original NVDIMM, the DRAM main memory is periodically refreshed at the original refresh frequency, and the refresh time is the second refresh time, which consumes a lot of refresh power. After power-off, the non-volatile memory is used to store the data in the DRAM main memory after power-off Data, the data in the non-volatile memory is transferred back to the DRAM main memory after power-on.

[0068] Figure 10 It is a schematic structural diagram of Embodiment 3 of the present invention; as Figure 10 shown. For example: the capacity of the DRAM main memory is 1GB, which is divided into 8 DRAM blocks, each DRAM block contains several storage units, and the capacity of the non-volatile memory is 1GB, which is used to replace the e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More