A low-power refresh method based on block dram

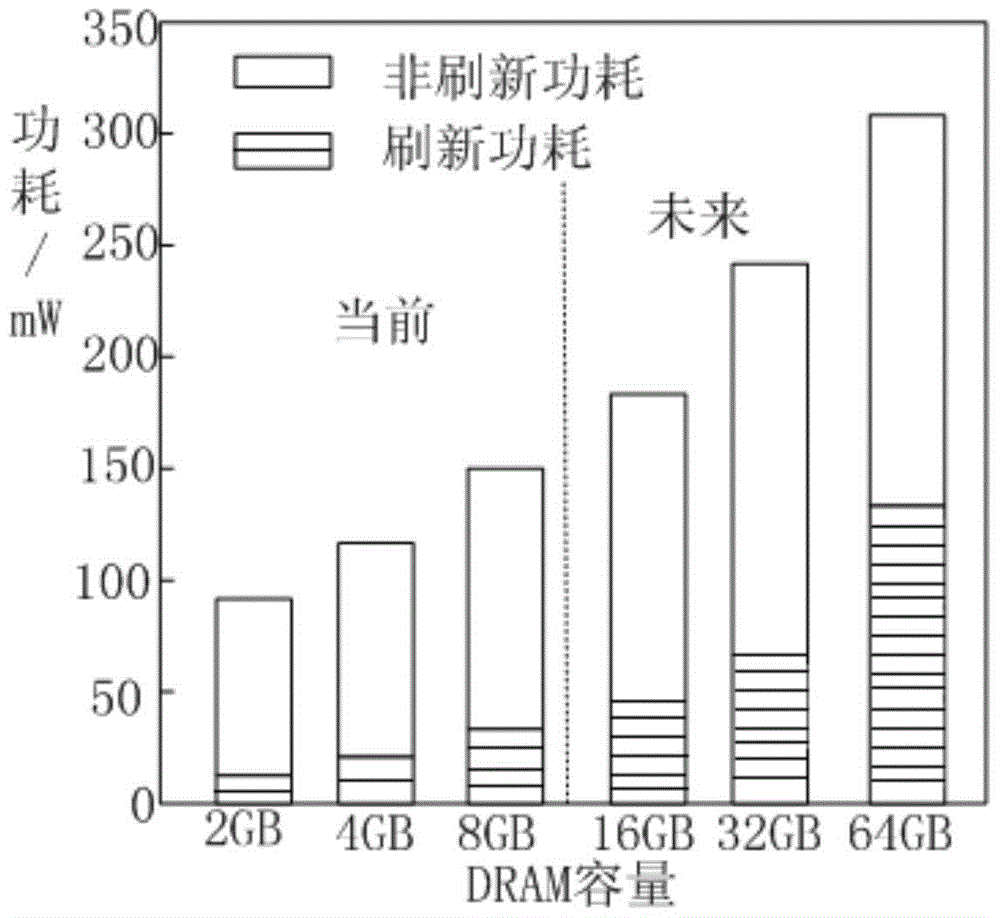

A technology with low power consumption and power consumption, applied in information storage, static memory, digital memory information and other directions, it can solve the problems of slow storage and access speed of PCM, and overall performance degradation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

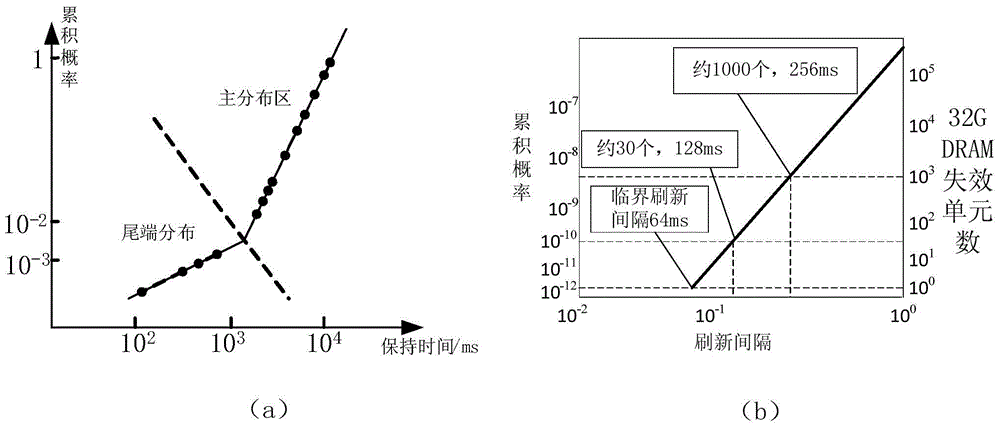

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0034] It should be noted that, in the case of no conflict, the embodiments of the present invention and the features in the embodiments can be combined with each other.

[0035] Embodiments of the present invention will be specifically explained below in conjunction with the accompanying drawings.

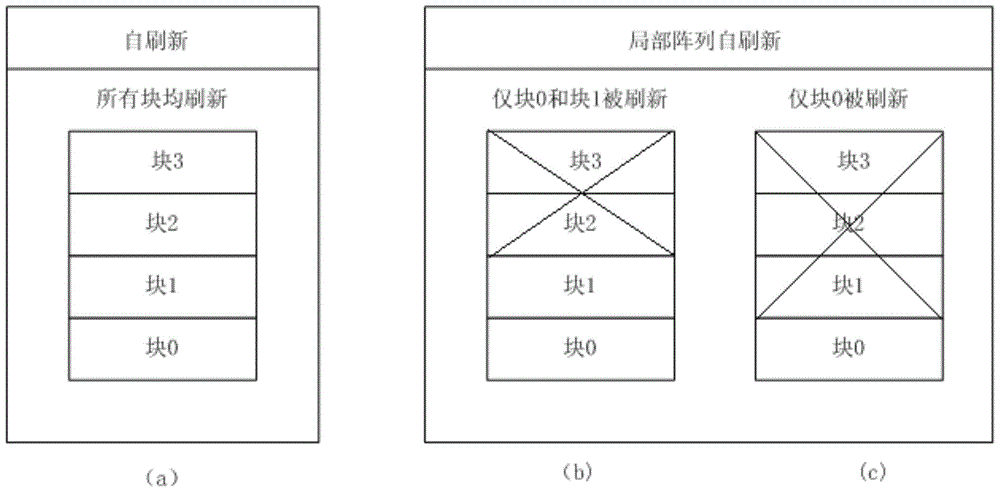

[0036] There are several DRAM chips in the memory stick, such as Image 6 As shown in -A (a memory bar in the figure contains 8 DRAM chips), each chip can be divided ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More