Graded sending dispatching circuit structure based on AFDX network switch chip

A switch and circuit technology, used in data exchange networks, electrical components, digital transmission systems, etc., can solve problems such as difficulty in implementation, and achieve the effect of improving operating efficiency and meeting real-time scheduling requirements.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The technical solutions of the present invention are clearly and completely described below in conjunction with the accompanying drawings and specific embodiments. Obviously, the described embodiments are only a part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by those skilled in the art without making creative work are all Belong to the protection scope of the present invention.

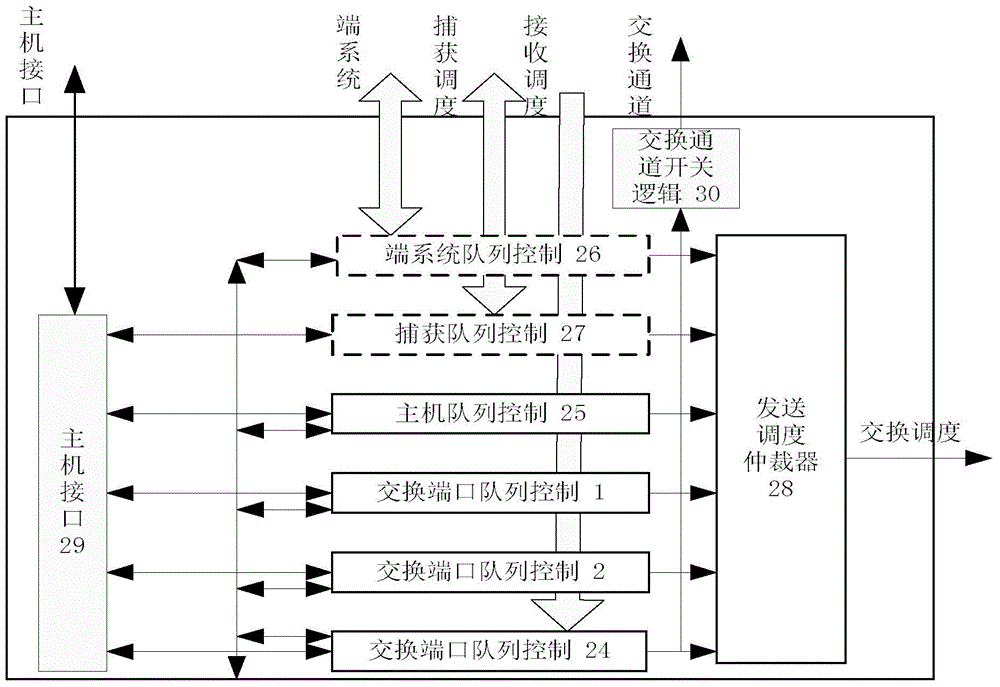

[0031] Such as figure 1 As shown, the present invention provides a hierarchical transmission scheduling circuit structure based on an AFDX network switch chip, including a host interface 29, a switching channel switch logic 30, switching port queue control modules 1-24, a host queue control module 25, and an end system queue control module. module 26, capture queue control module 27 and sending scheduling arbiter 28. Wherein, the host interface 29 is connected with the switch port queue contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More