A kind of CSP packaging chip structure and manufacturing method

A manufacturing method and chip mounting technology, which can be used in electrical components, circuits, semiconductor devices, etc., can solve the problems of loss of light-emitting area and further improvement of light-emitting efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

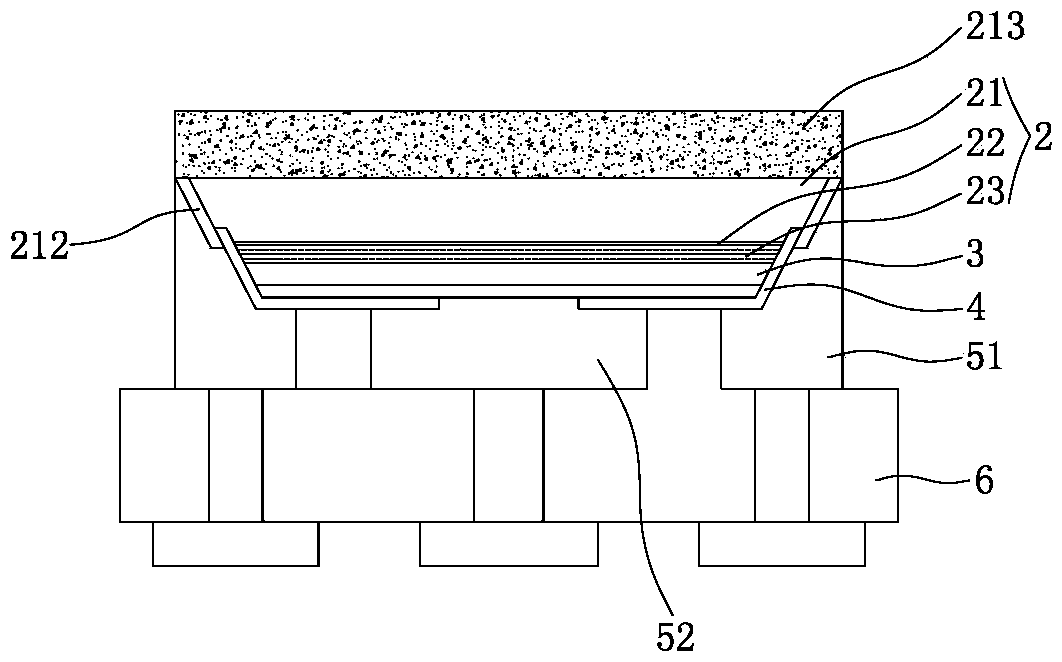

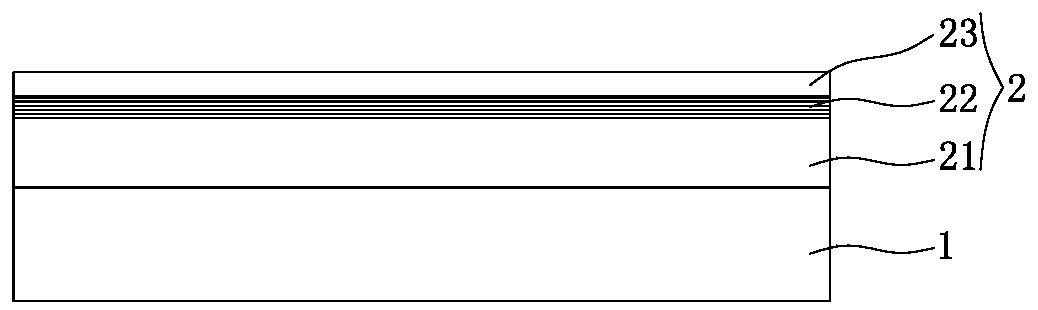

[0045] refer to Figure 1 to Figure 2g As shown, Embodiment 1 of a CSP packaged chip structure disclosed by the present invention includes an epitaxial layer 2 , a conductive layer 3 , an insulating layer 4 , an N electrode 51 , a P electrode 52 and a substrate 6 .

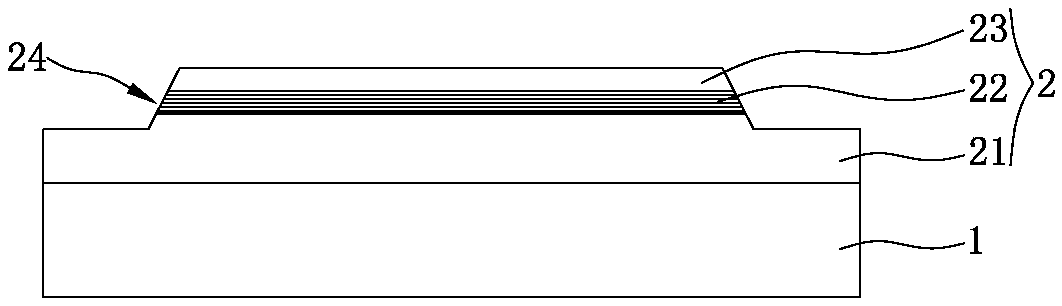

[0046] Such as figure 1 As shown, the epitaxial layer 2 is composed of N-GaN 21 , active light-emitting layer 22 and P-GaN 23 which are sequentially formed. The conductive layer 3 is formed on the P-GaN 23, and the P electrode 52 is formed on the conductive layer 3; in this embodiment, the conductive layer 3 is a metal reflective layer 31, forming a flip chip. The metal reflective layer 31 is made of silver, titanium, aluminum, chromium, indium, tin, gold and alloys thereof, and is arranged in a single-layer or multi-layer structure.

[0047] A first slope 24 is formed on the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More