Mini-LED chip and preparation method thereof

A mini-led and chip technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems affecting the performance of Mini-LED chips, high contact resistance of P-type contact layers, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

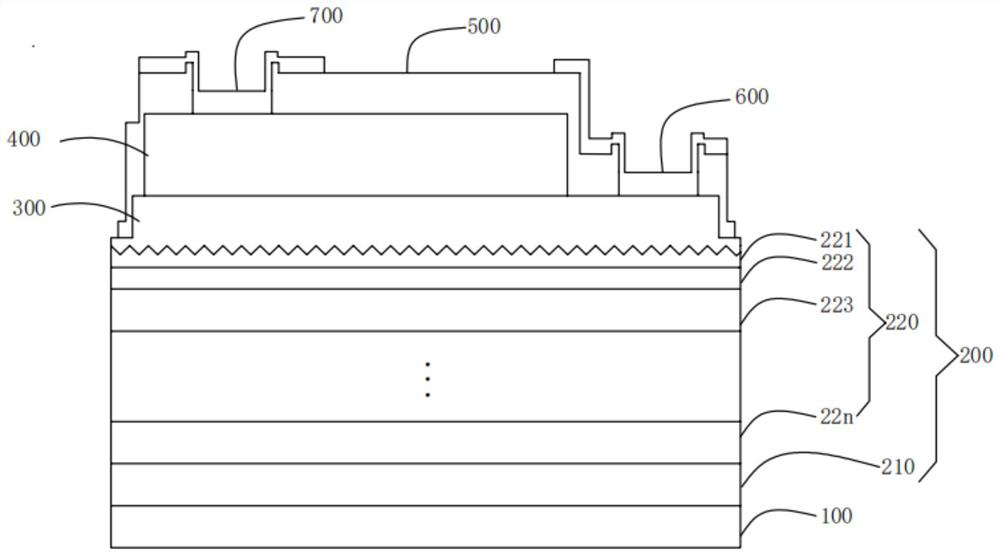

[0039] see figure 1 , shows a Mini-LED chip provided by the first embodiment of the present invention, the Mini-LED chip includes a transparent substrate 100, and a bonding layer 200, a P-type contact layer 300, a bonding layer 200, a P-type contact layer 300, Epitaxial layer 400 and specular reflection layer 500 . The transparent substrate 100 is used to support and protect the epitaxial wafer. Light is emitted from the epitaxial layer 400 to the transparent substrate 100 and scattered into the air through the transparent substrate 100 without absorbing the light source. The material of the transparent substrate 100 can be preferably selected from glass, sapphire , silicon carbide or organic transparent materials. The Mini-LED chip is a flip-chip LED chip. The transparent substrate 100 is bonded to the epitaxial wafer through the bonding layer 200 , and then the structure of the epitaxial layer 400 is turned over. Specifically, the bonding layer 200 on the epitaxial wafer a...

Embodiment 2

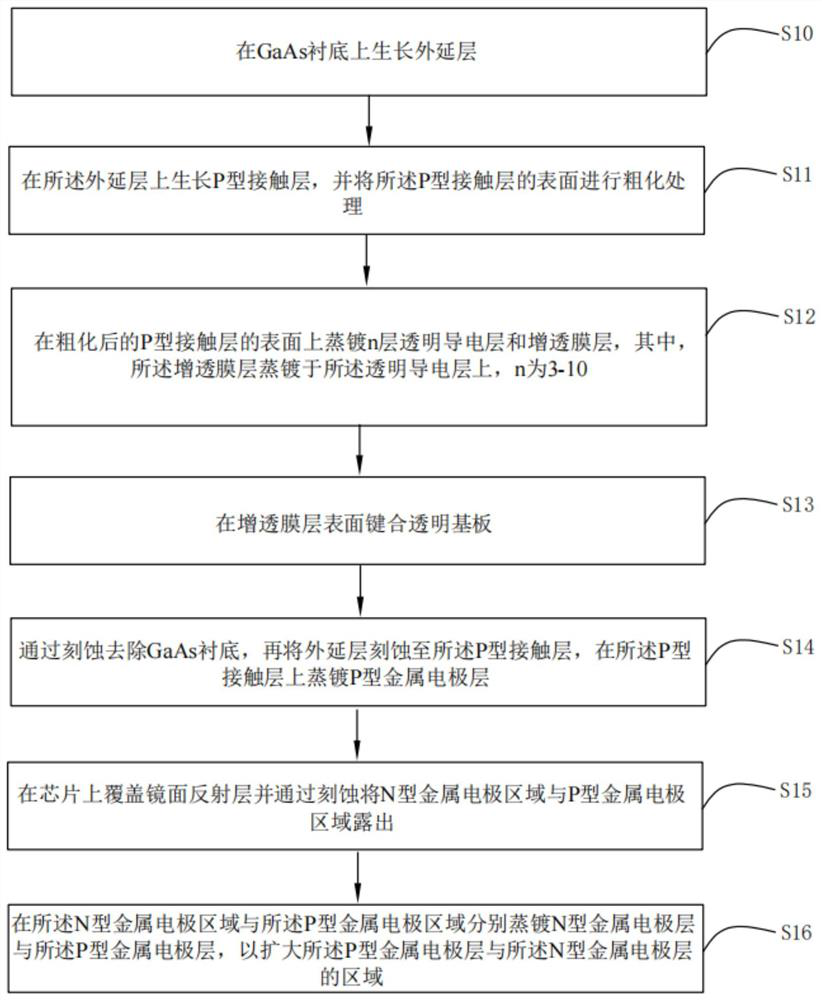

[0053] The second embodiment of the present invention provides a preparation method of a Mini-LED chip, the preparation method includes steps S10-S16:

[0054] Step S10, growing an epitaxial layer on the GaAs substrate;

[0055] Among them, the Mini-LED chip is a flip-chip LED chip. After growing the epitaxial layer, the P-type contact layer, the bonding layer and the transparent substrate in sequence on the GaAs substrate, the structure is turned upside down, and then the GaAs substrate is removed. , to grow other thin film layers.

[0056] Step S11, growing a P-type contact layer on the epitaxial layer, and roughening the surface of the P-type contact layer;

[0057] The P-type contact layer is a P-type gallium phosphide ohmic contact layer, and the surface of the P-type contact layer is roughened to destroy the total reflection angle and increase the light extraction angle of the epitaxial layer, thereby increasing the light extraction efficiency of the chip.

[0058] Ste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More