Single-particle reinforced power-on reset circuit applicable to SRAM type FPGA for aerospace

A single-particle reinforcement and circuit technology, applied in electrical components, electronic switches, pulse technology, etc., can solve problems such as difficulty in ensuring reset pulse width, chip power-off, and affecting the reliability of SRAM-type FPGAs for aerospace

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

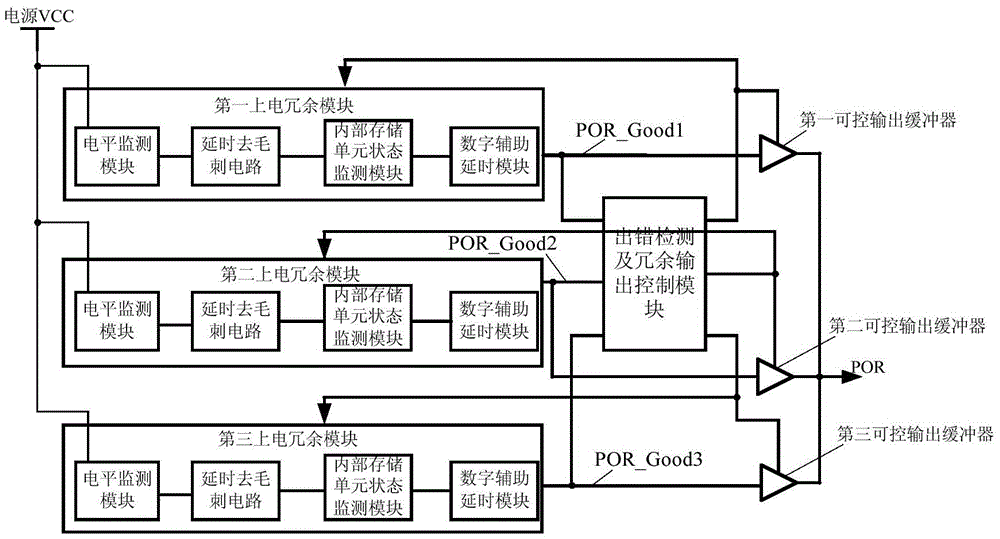

[0046]The basic idea of the present invention is: a single particle reinforced power-on reset circuit suitable for aerospace SRAM type FPGA, which internally includes a power supply VCC, three identical power-on redundant modules, error detection and redundant output control modules And three controllable output buffers, the error detection and redundant output control module can detect the faulty power-on redundant module, and reset the power-on redundant module to clear the accumulation of single event effects; error detection and redundancy The output control module can control the controllable output buffer to cut off the output of the faulty power-on redundant module, so as to ensure the correct output of the power-on reset circuit. The power-on reset circuit clears the error accumulation phenomenon caused by the single event reversal effect, and at the same time controls the output of the module, eliminates the influence of the single event effect on the output, and ach...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com