Wiring method of superconducting quantum bit system for surface coding scheme and wiring board

A technology of superconducting quantum and quantum bits, applied in the field of quantum systems, can solve the problems of reduced decoherence time and inability to work of quantum bits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

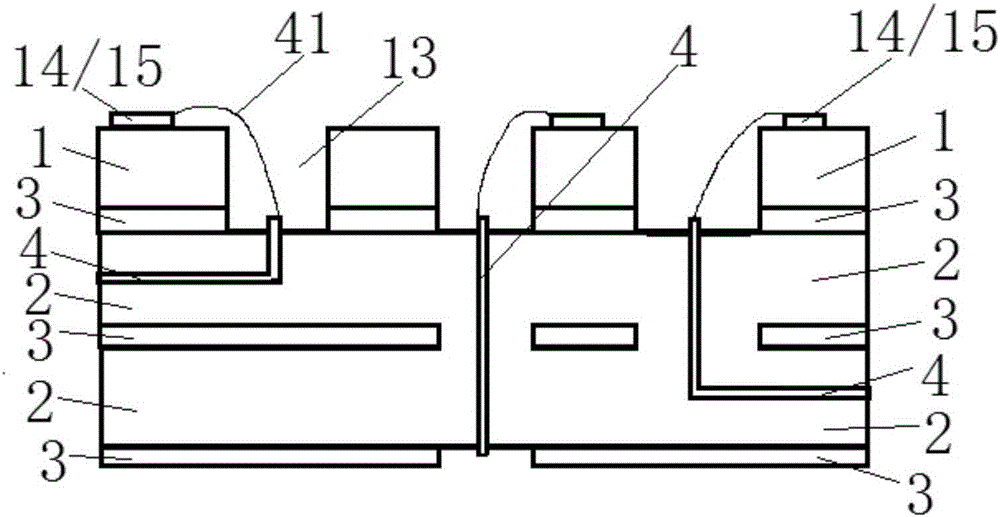

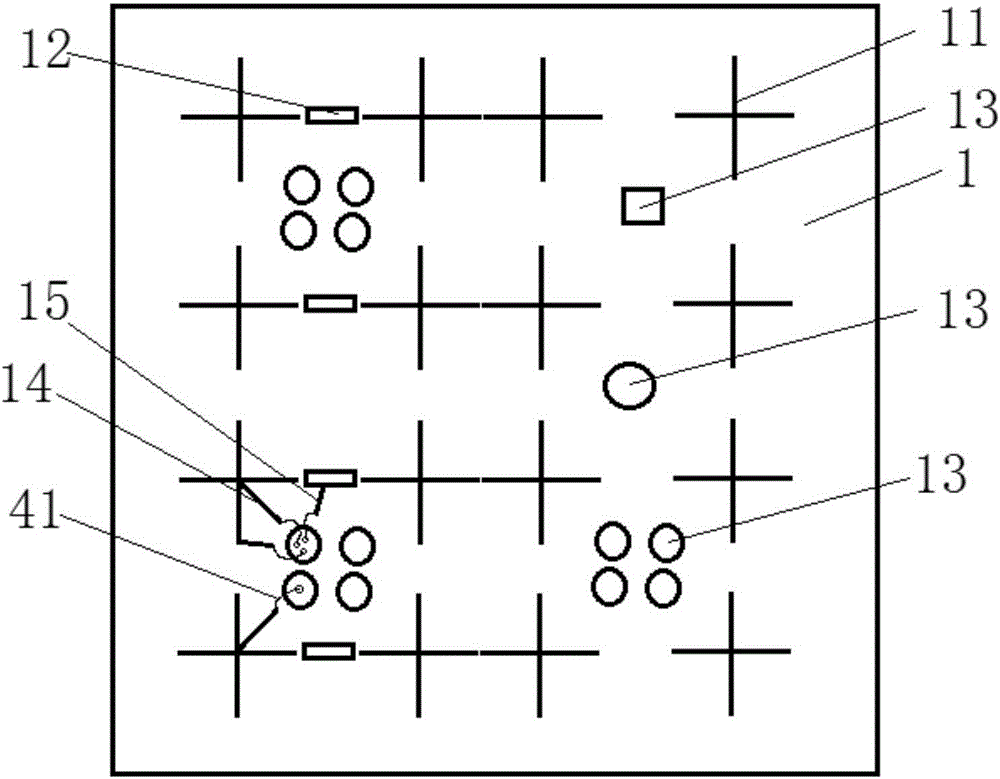

[0026] figure 1 It is a structural schematic diagram of a wiring board for a surface coding scheme superconducting qubit system according to an embodiment of the present invention, figure 2 It is a schematic top view of a wiring board used in a surface coding scheme superconducting qubit system according to an embodiment of the present invention. Such as figure 1 As shown, a wiring board for a superconducting qubit system of a surface coding scheme includes: a quantum chip substrate 1 , several insulating layers 2 , several grounding layers 3 and wiring layers 4 . Quantum chip substrate 1 is provided with several qubits 11 ( figure 2 shown) and several couplers 12 ( figure 2 shown), the several qubits 11 ( figure 2 shown) between any two adjacent qubits 11 directly coupled or through the several couplers 12 ( figure 2 Shown) in the corresponding coupler 12 coupling; Insulation layer 2 covers and is arranged on the lower surface of described quantum chip substrate 1; ...

Embodiment 2

[0031] The present invention also provides a wiring method for a superconducting qubit system of a surface coding scheme, which is applied to the wiring of a superconducting qubit system having a quantum chip substrate 1, an insulating layer 2, and a grounding layer 3 as described above The plate includes: wiring under the quantum chip substrate 1, punching a hole 13 on the quantum chip substrate 1, and connecting the wiring to the circuit on the quantum chip substrate 1 through the hole 13, The wiring forms the wiring layer 4 .

[0032] In a preferred embodiment, the wiring layer 4 is penetrated in the insulating layer 2 below the quantum chip substrate 1, and the insulating layer 3 pierced with the wiring layer 4 can be one or more layers; the wiring layer 4 can be set in the same insulating layer 2 or in different insulating layers 2 . Preferably, the upper surface and the lower surface of the insulating layer 2 are covered with a ground layer 3 made of metal. The metal m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More