A fft floating-point optimization method based on instruction-level parallel ilp and data-level parallel dlp

A floating-point optimization and data-level technology, applied in the direction of concurrent instruction execution, electrical digital data processing, special data processing applications, etc., can solve the problems of complex hardware platforms, fast Fourier transform research has not been developed, etc., to achieve efficient deployment , reduce the running clock overhead, and avoid the effect of clock overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

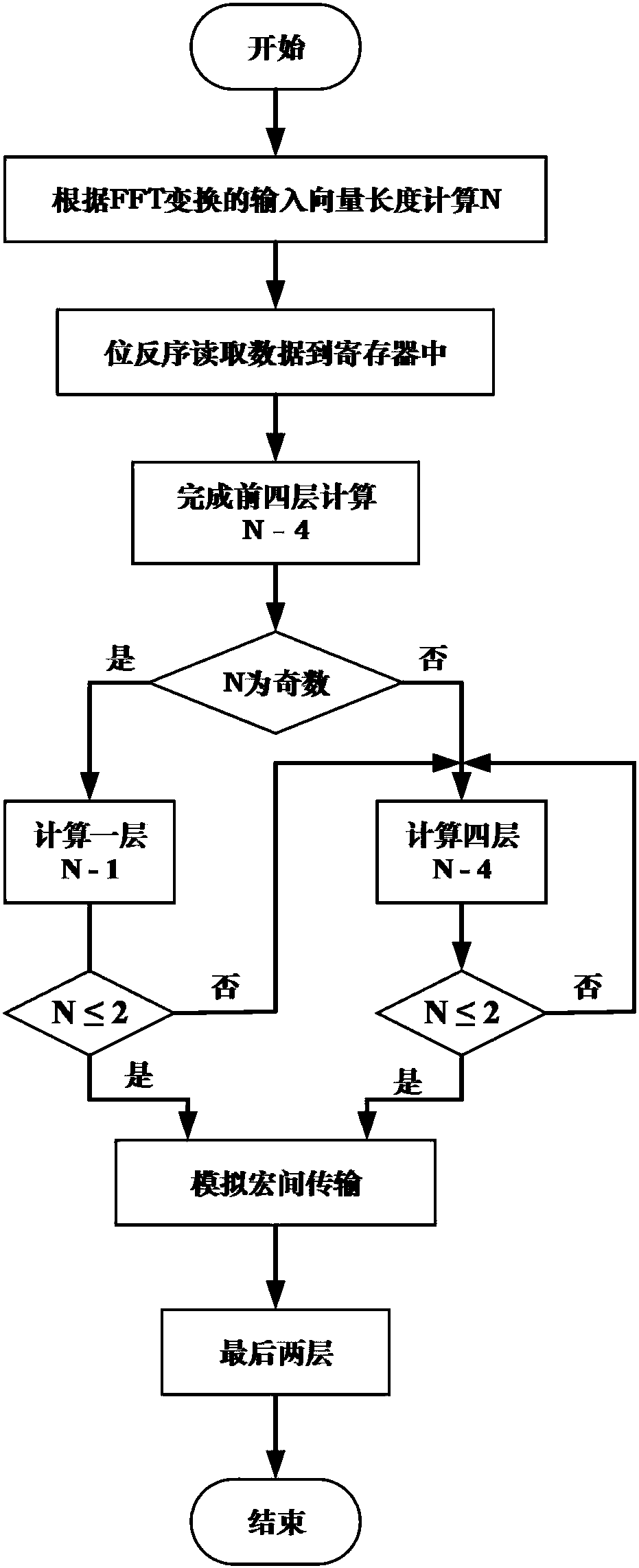

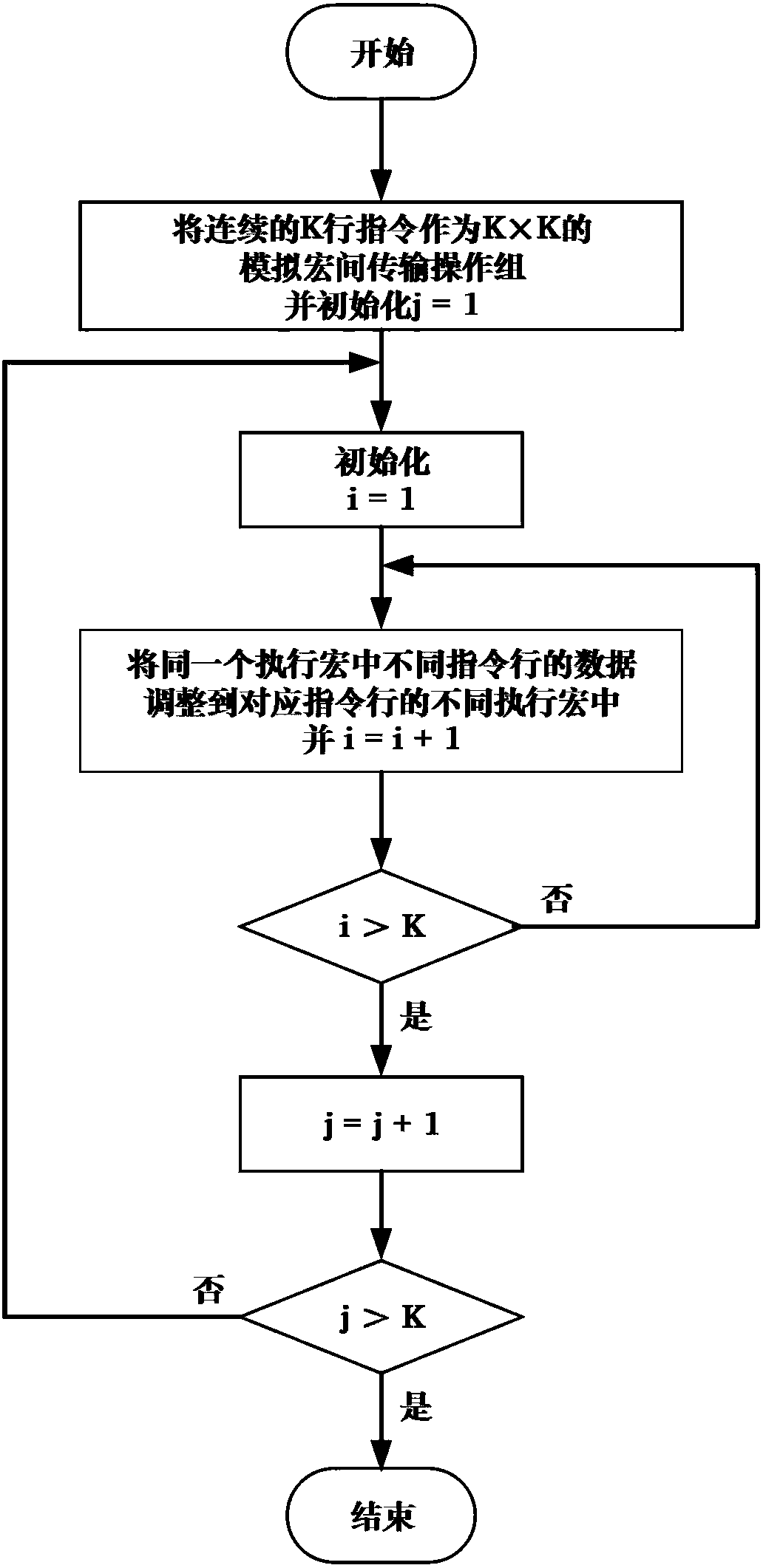

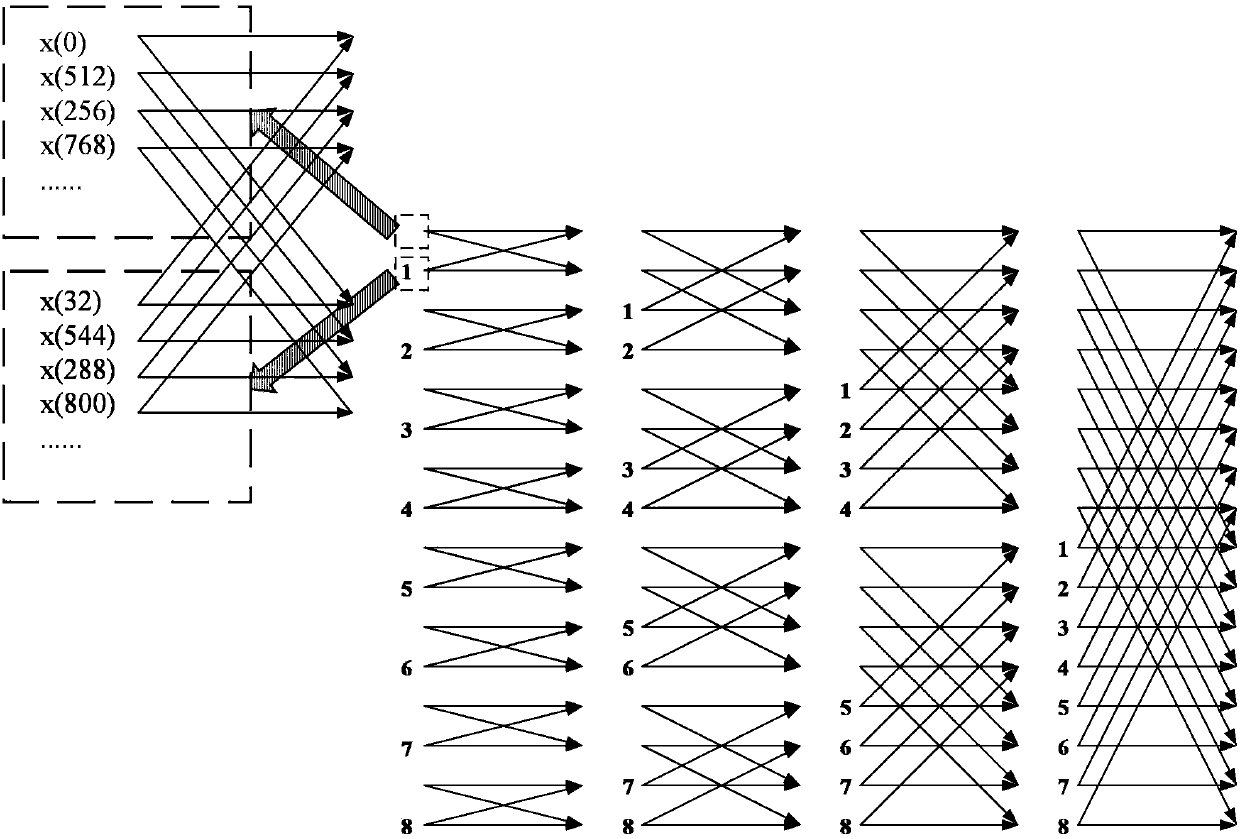

[0037] The purpose of the present invention is to propose a floating-point version FFT optimization method suitable for instruction-level parallel ILP and data-level parallel DLP hardware platforms, in order to perform high-performance optimization on the hardware infrastructure provided by it. The following specific implementations only use the BWDSP104x platform as an example to discuss optimization methods, but the optimization techniques and methods in the present invention are not limited to the BWDSP104x platform. Any hardware platform of ILP and DLP is suitable for the optimization scheme of the present invention.

[0038] The BWDSP104x platform has 4 execution macros (x, y, z, t), each macro has 8 arithmetic logic units (ALU), 8 multipliers (MUL), 4 shifters (SHIFT), and 1 Supercomputer and a set of general-purpose register sets containing 128 registers. It has 11 stages of pipelines, and each instruction line can simultaneously parallel 16-word instructions.

[0039] In ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More