Long bit width time sequence accumulation multiplying unit

A multiplier and long-bit technology, which is applied in the field of long-bit-width sequential accumulation multipliers, can solve the problems of complex clock frequency and full adder complexity increase, and achieve the effect of high clock frequency and margin guarantee

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be further described below in conjunction with the accompanying drawings. Of course, the present invention is not limited to this specific embodiment, and general replacements known to those skilled in the art are also covered within the protection scope of the present invention.

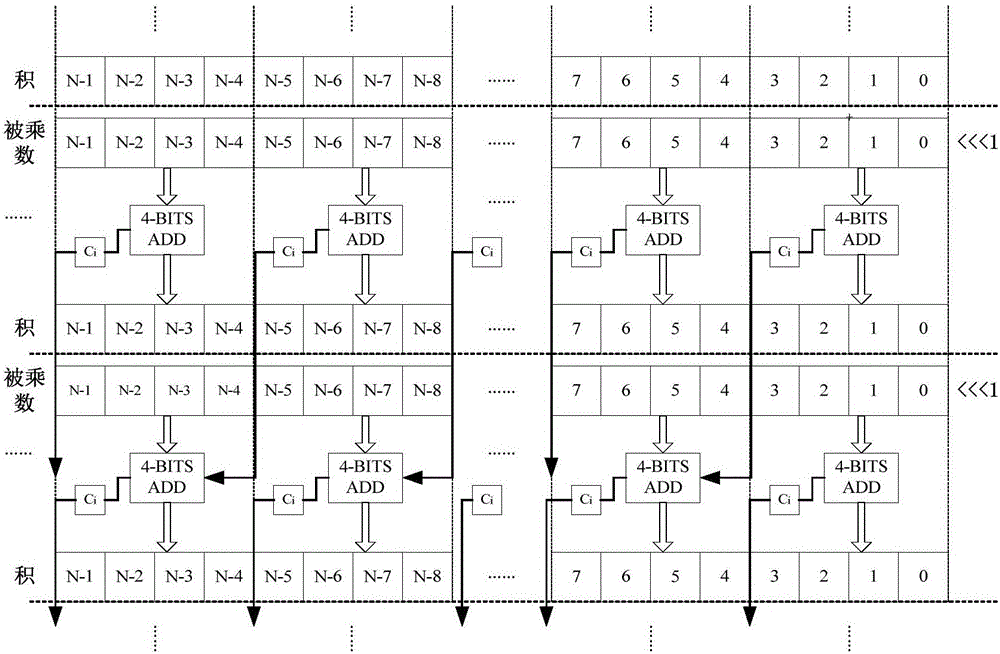

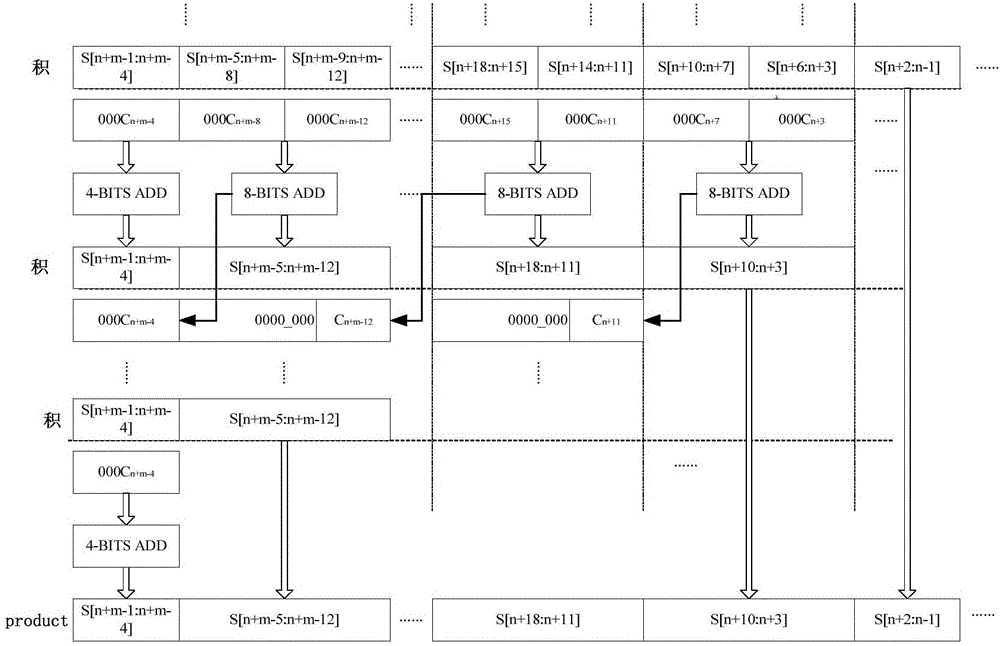

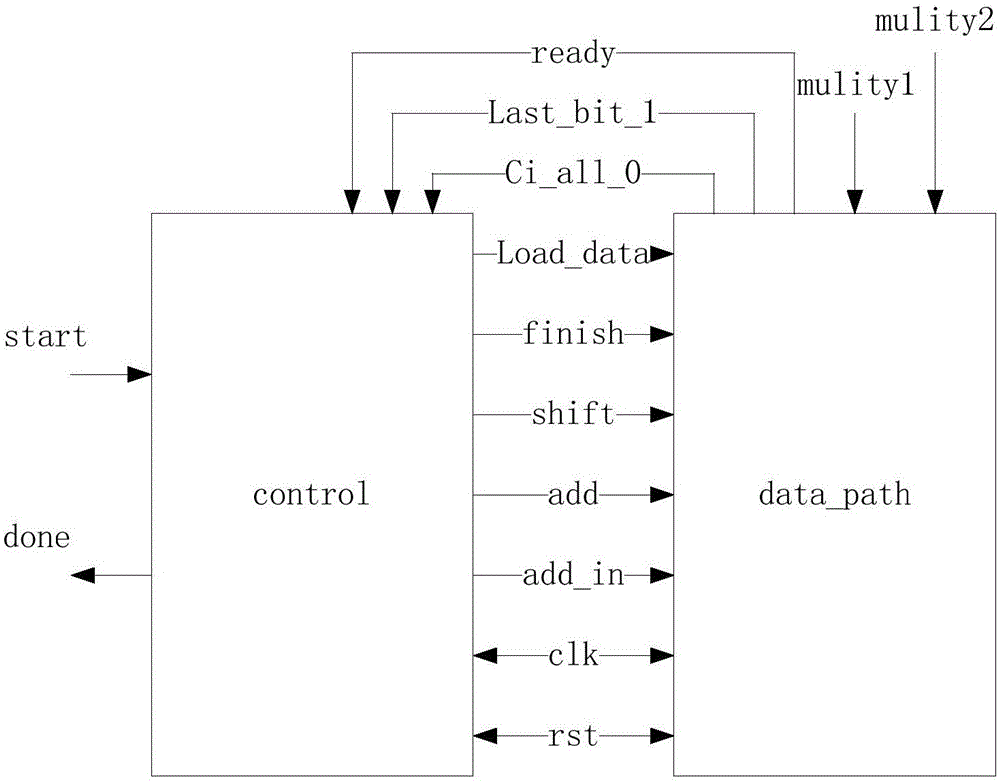

[0024] The following is attached Figure 1-4 The present invention will be described in further detail with specific examples. It should be noted that the drawings are all in a very simplified form, using imprecise scales, and are only used to facilitate and clearly achieve the purpose of assisting in describing the present embodiment.

[0025] In this embodiment, during the accumulation process, the original complete long bit width full adder structure is split into a combination of multiple k-bit full adders and one k-bit half adder. The full adder performs a c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More