FPGA-based digital video display interface module and communication method thereof

A technology of display interface and digital video, which is applied in the field of digital video display interface module and its communication, can solve the problems of image smear phenomenon and insufficient cache rate, and achieve the effect of increasing cache rate, improving display performance and eliminating smear phenomenon

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

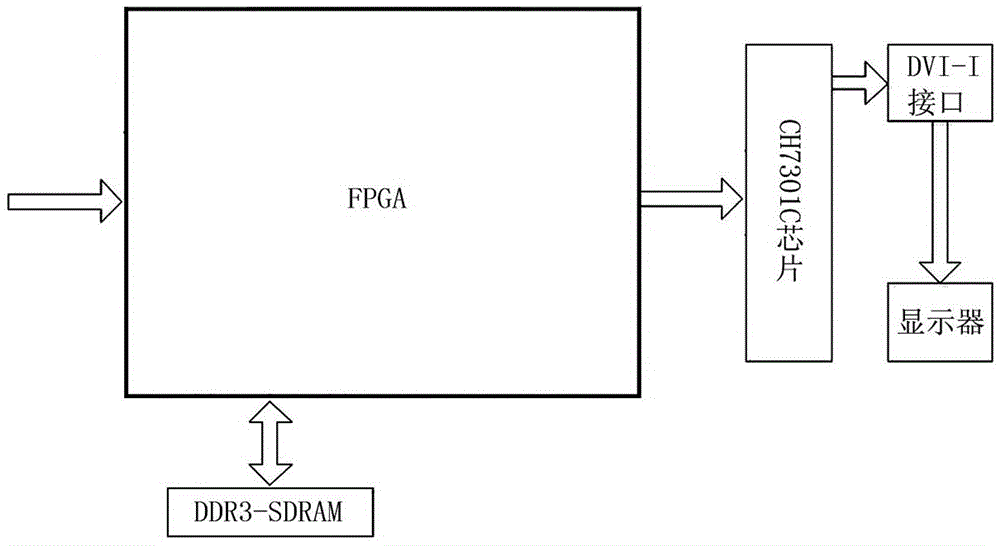

[0018] A digital video display interface module based on FPGA, including FPGA, DDR3-SDRAM, CH7301C chip and DVI-I interface; wherein, FPGA is connected with DDR3-SDRAM and CH7301C chip respectively; CH7301C chip is connected with DVI-I interface; DVI- The I interface is connected with the display device.

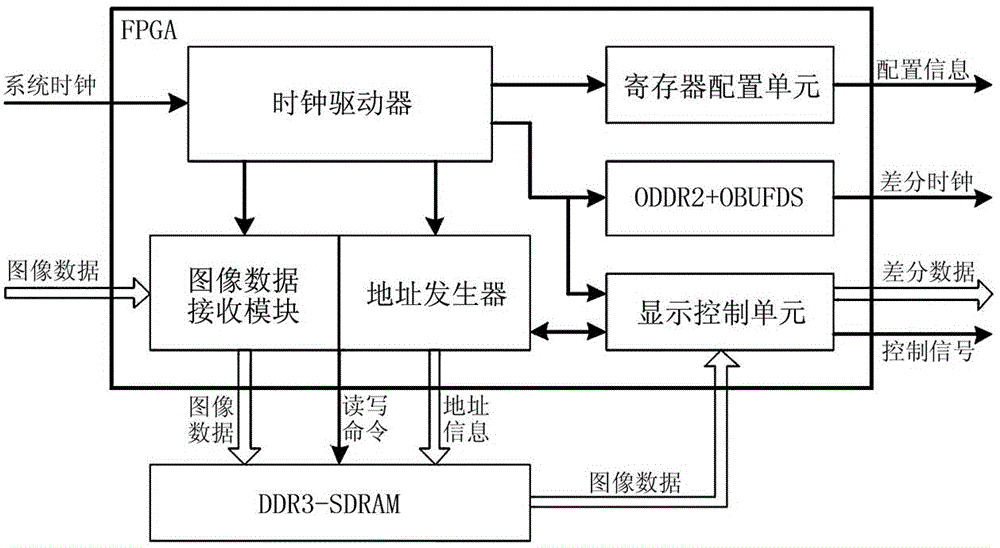

[0019] Described FPGA comprises clock driver, image data receiving module, address generator, register configuration unit, ODDR2+OBUFDS, display control unit; Wherein, clock driver is respectively connected with image data receiving module, address generator, register configuration unit, ODDR2+OBUFDS , display control unit connection; image data receiving module and address generator are connected with DDR3-SDRAM; address generator is connected with display control unit; register configuration unit, ODDR2+OBUFDS, display control unit are connected with CH7301C chip; display control unit Connect with DDR3-SDRAM.

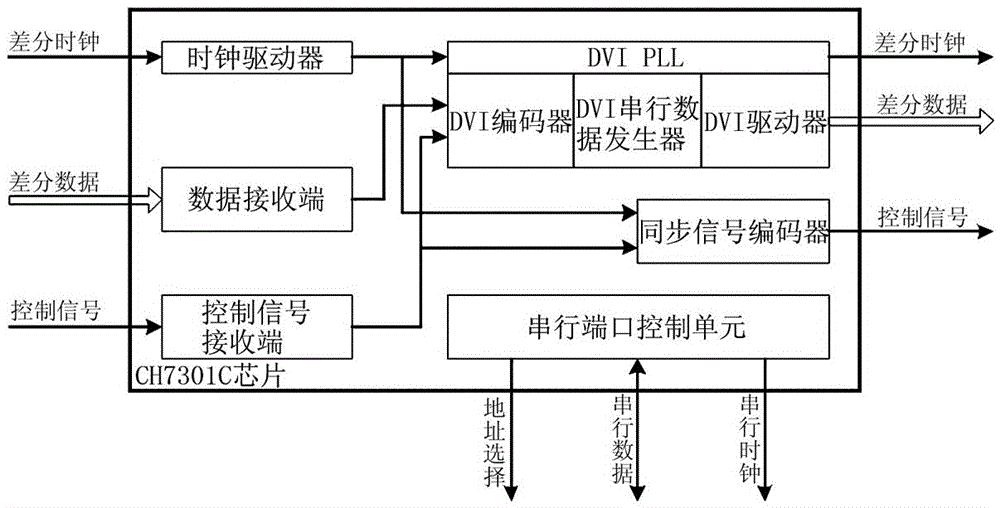

[0020] Described CH7301C chip comprises clock driver, data re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More