Patents

Literature

35 results about "DDR3 SDRAM" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Double Data Rate 3 Synchronous Dynamic Random-Access Memory, officially abbreviated as DDR3 SDRAM, is a type of synchronous dynamic random-access memory (SDRAM) with a high bandwidth ("double data rate") interface, and has been in use since 2007. It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory (SDRAM) chips. DDR3 SDRAM is neither forward nor backward compatible with any earlier type of random-access memory (RAM) because of different signaling voltages, timings, and other factors.

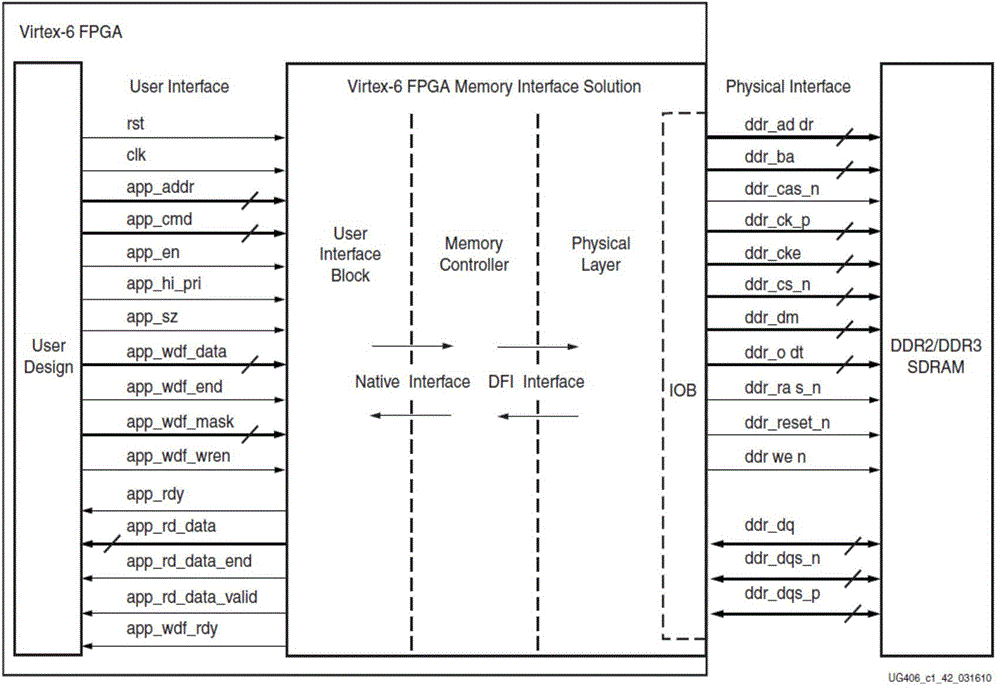

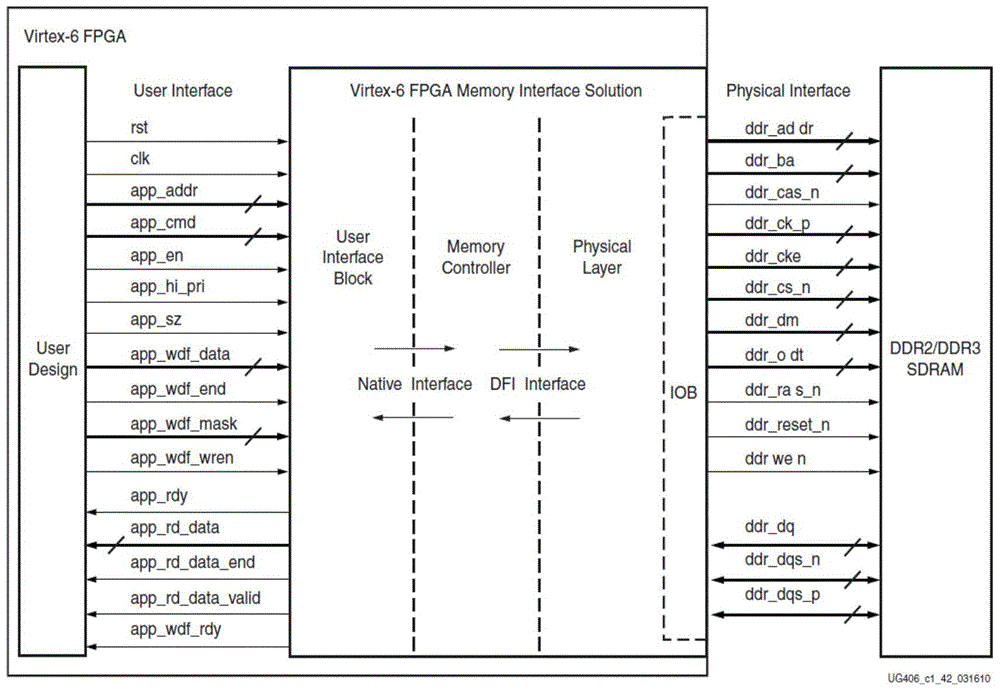

FPGA realization method of SAR signal processing algorithm

InactiveCN106896360ARealize ultra-high resolution imaging processingSolving the Challenges of High-Resolution ImagingProgramme controlComputer controlDigital signal processingHigh resolution imaging

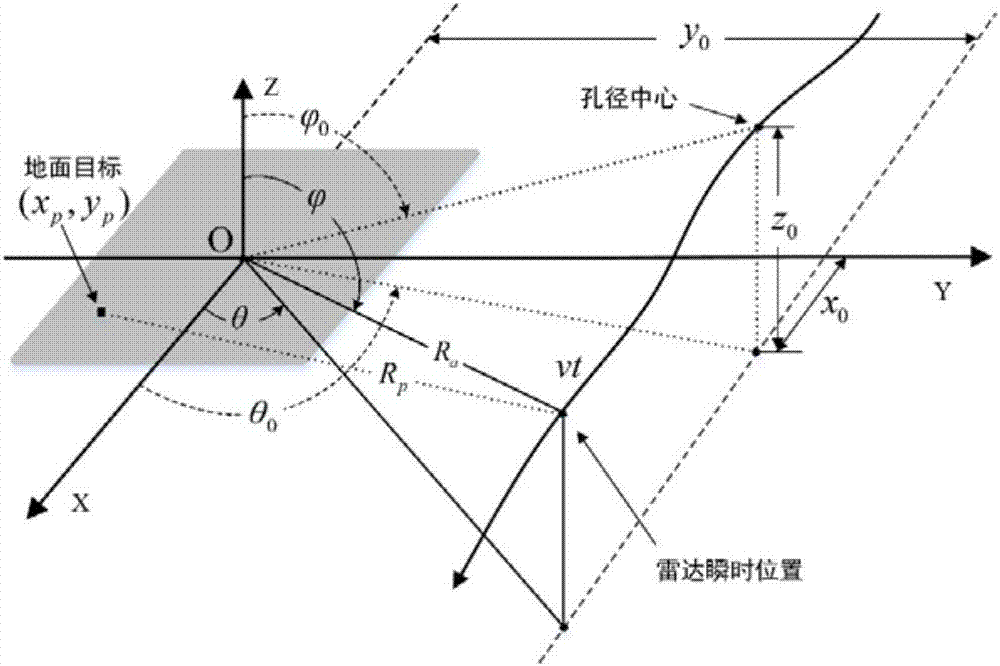

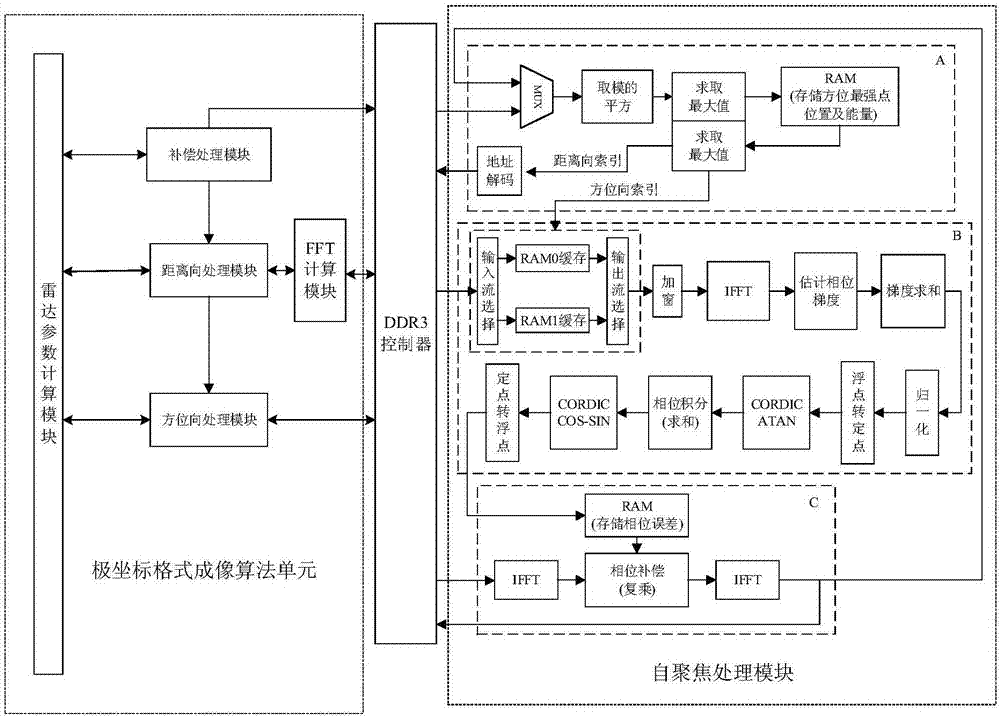

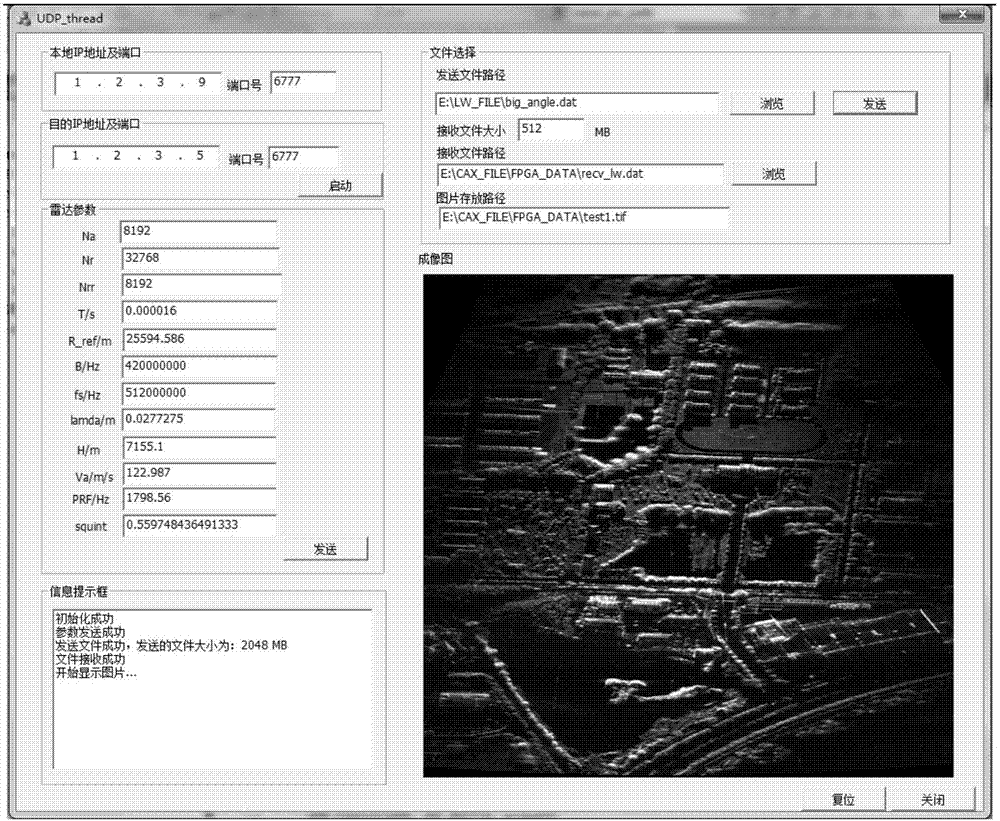

The present invention discloses an FPGA (Field Programmable Gate Array) realization method of a SAR (Synthetic Aperture Radar) signal processing algorithm, belonging to the radar imaging and digital signal processing technology field. The method comprises: building hardware configuration of an upper computer, an Ethernet data communication module, an algorithm processing module, a DDR3 SDRAM and a control module thereof, a data selection module, a reset module, a clock management module, the algorithm processing module is provided with a polar coordinate format imaging algorithm of dechirp signals based on the Chirp Scaling principle and a two-dimensional self-focusing algorithm, and therefore the problem of high resolution ratio imaging of a mini-type SAR system and the ultrahigh resolution imaging processing of SAR etch signals are realized.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Synthetic aperture radar imaging and processing transposition storage method and data access method

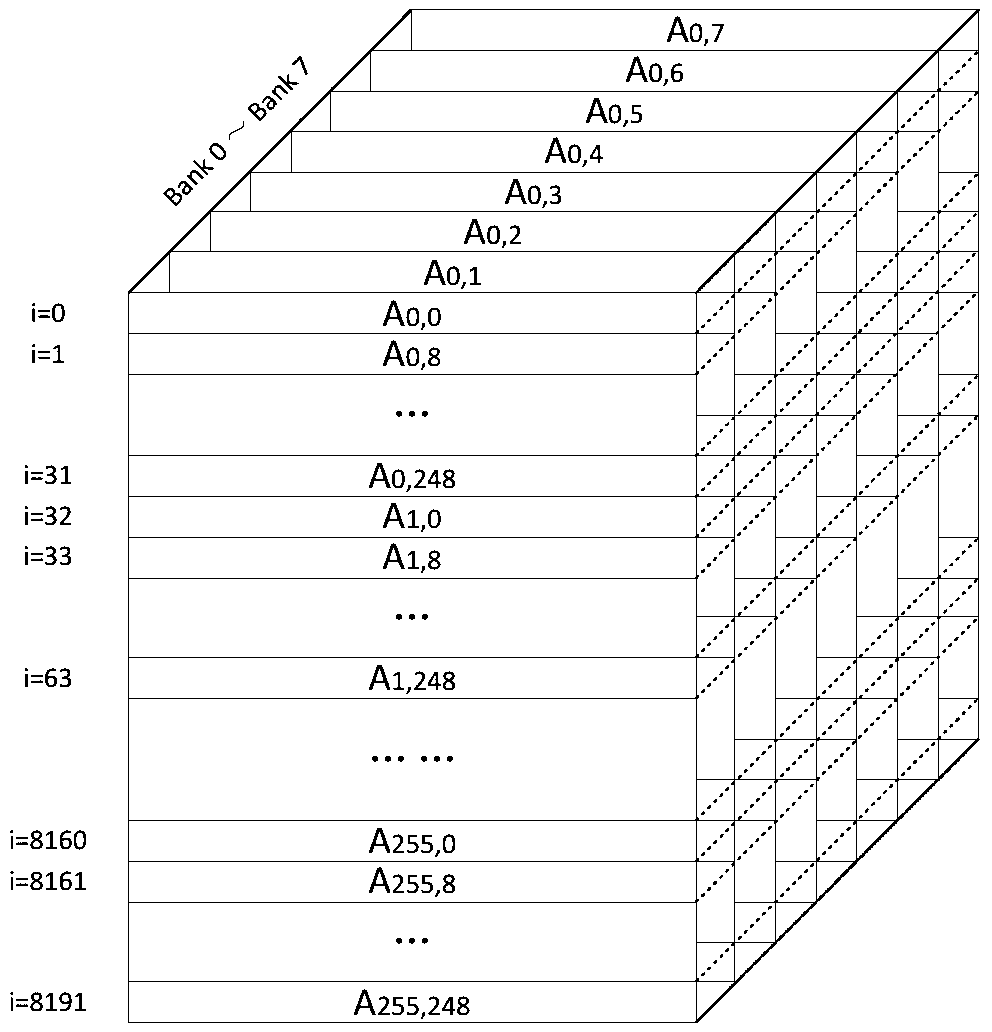

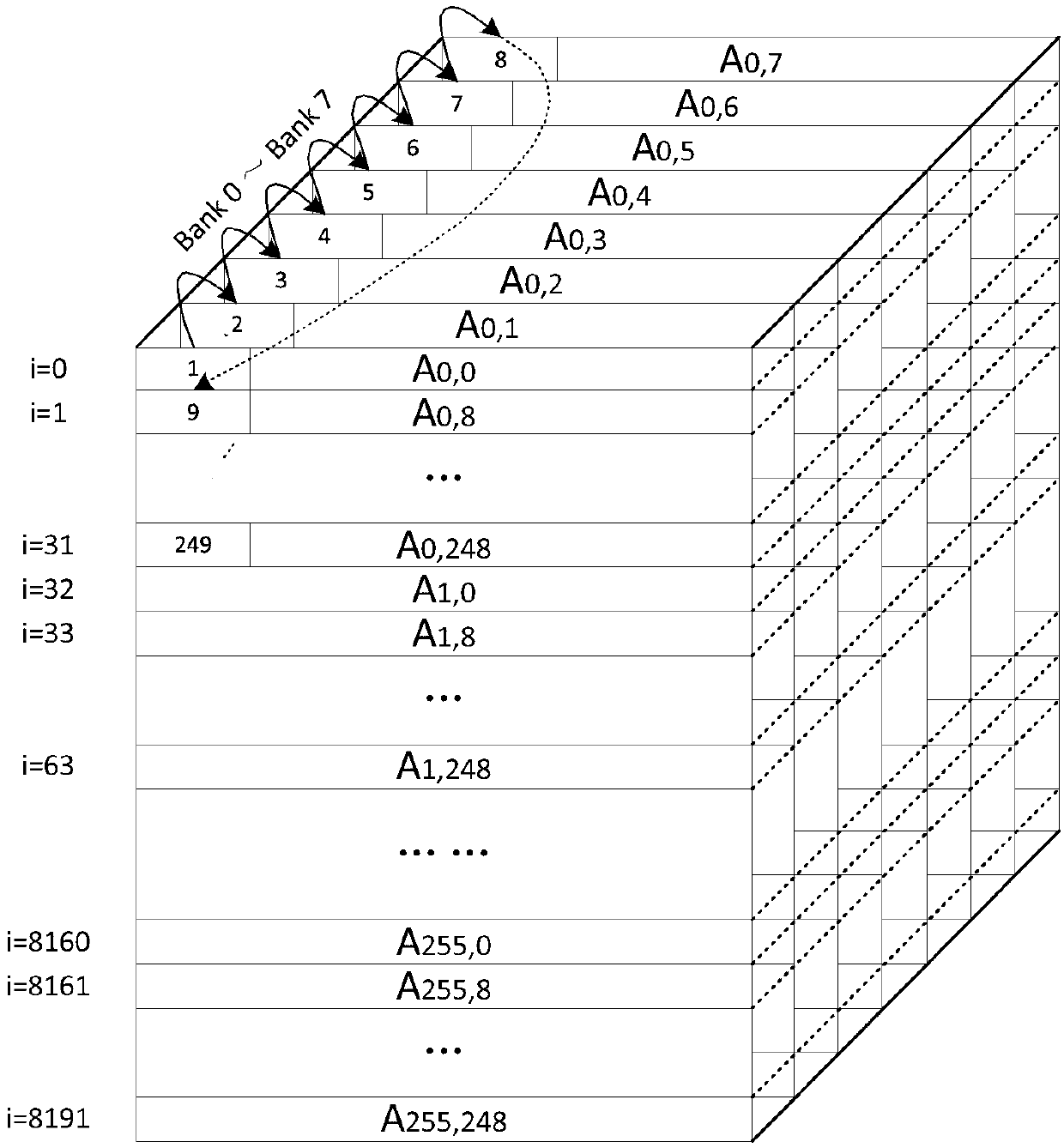

InactiveCN103135096AAccess balanceLower latencyWave based measurement systemsDouble data rateSynthetic aperture radar

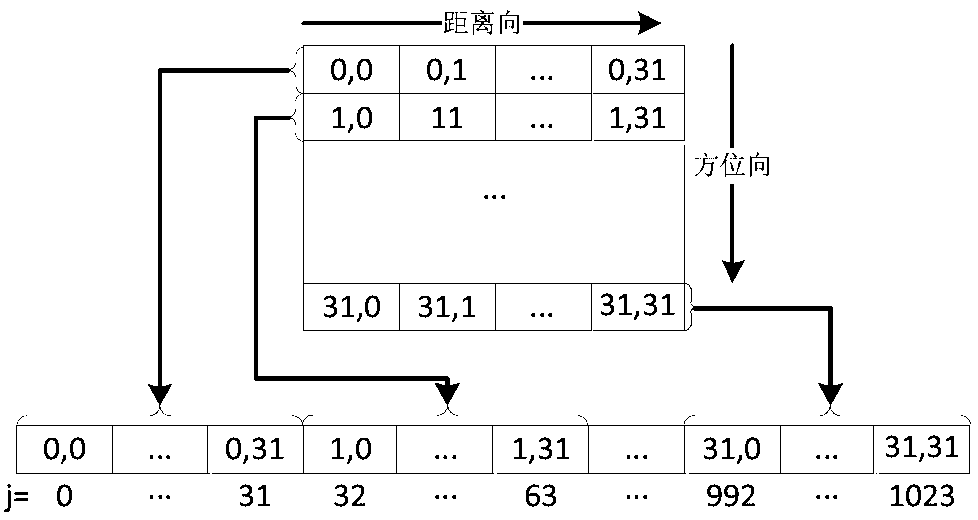

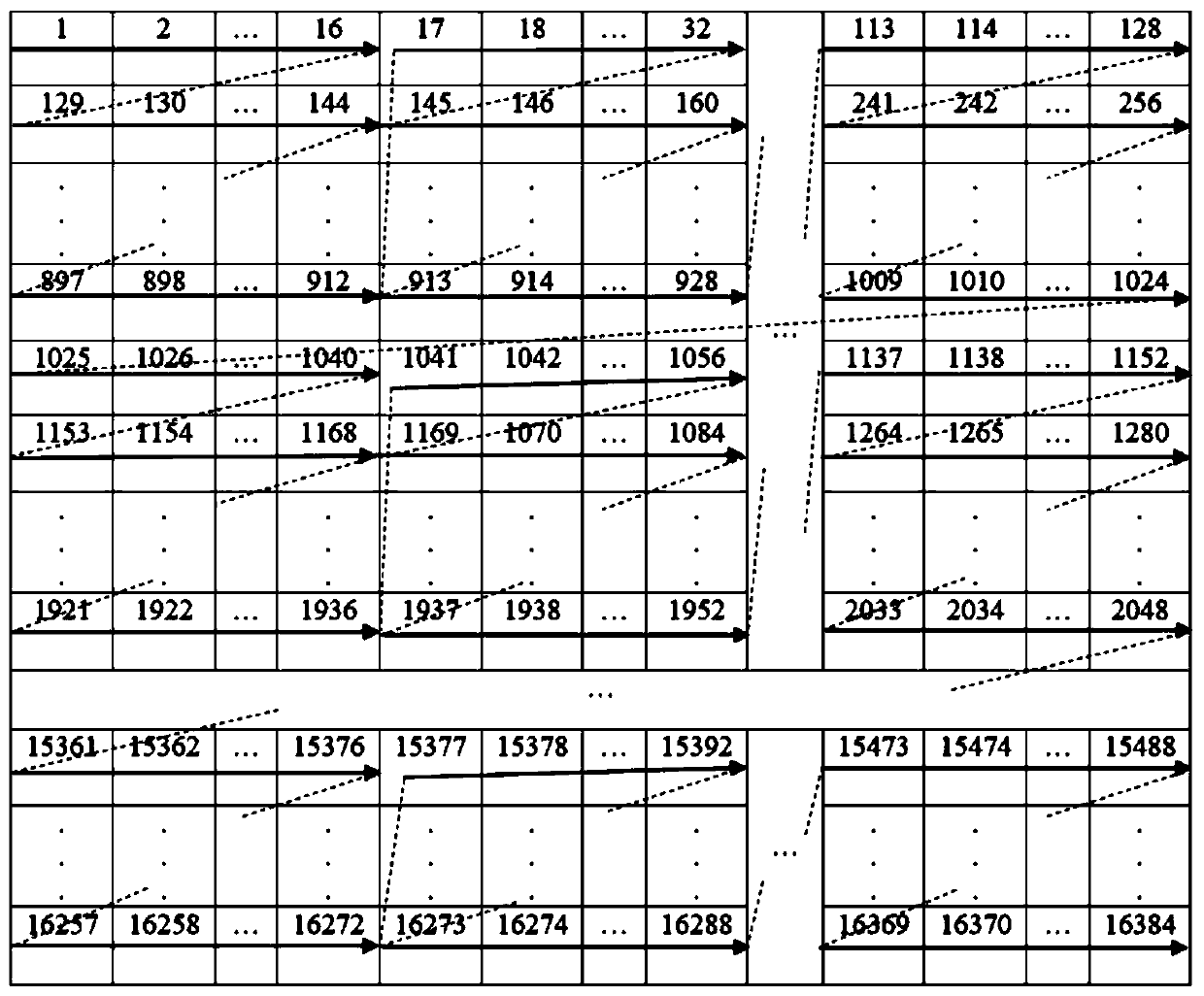

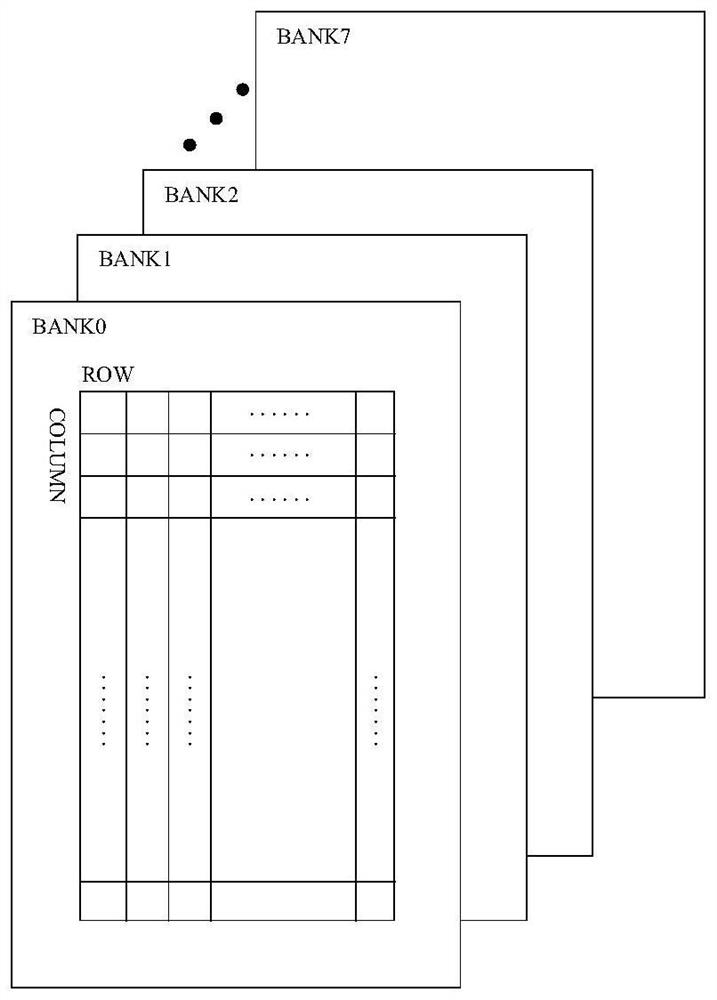

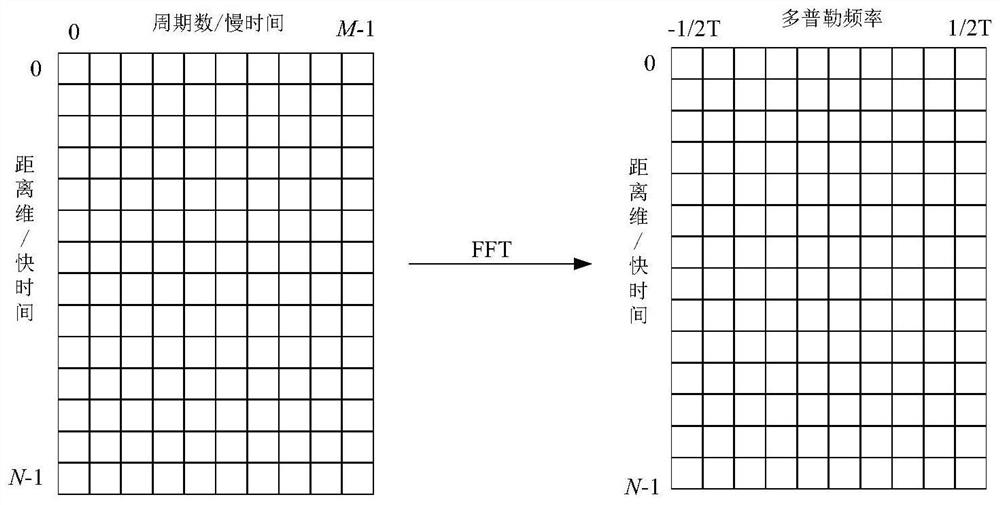

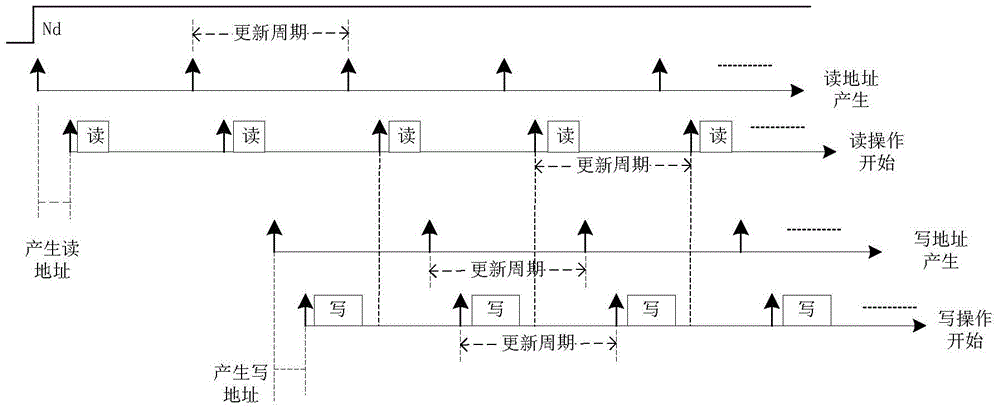

The invention discloses an efficient transposition storage method in the synthetic aperture radar imaging and processing process. The method includes a first step of dividing a synthetic aperture radar two-dimensional data matrix into a plurality of submatrix blocks with the same size, wherein data points in each submatrix block are just equal to the data points stored in one line of a double data rate 3 synchronous dynamic random access memory (DDR3 SDRAM) in number, a second step of carrying out numbering on the submatrix blocks line by line and gradually mapping data in the first submatrix block into the first line of a Bank 0 of the DDR3 SDRAM, and a third step of mapping the data in the second submatrix block into the first line of a Bank 1 of the DDR3 SDRAM line by line according to the same method, by parity of reasoning, completing mapping the first line of a last Bank and then turning to the second line of the Bank 0 until the data of all the submatrix blocks are mapped. The synthetic aperture radar imaging and processing transposition storage method is capable of solving the problem of too low transposition storage efficiency in the synthetic aperture radar imaging and processing.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

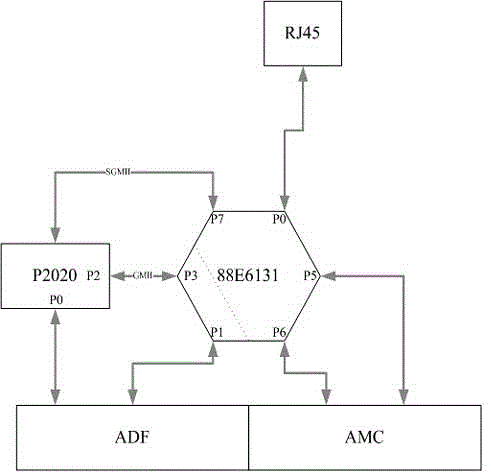

Data processing board system based on standard AMC platform

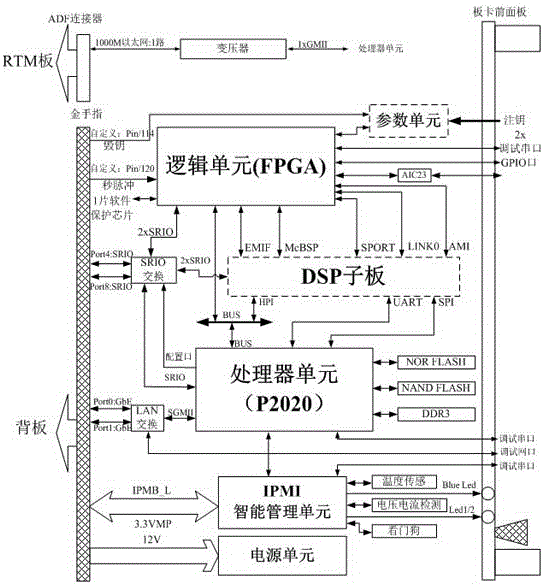

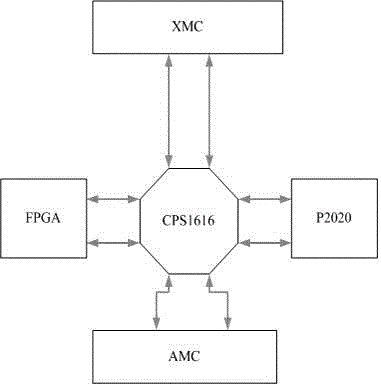

InactiveCN106126473AEasy to handleIncrease exchange speedArchitecture with single central processing unitData switching networksComputer moduleGigabit

The invention discloses a data processing board system based on a standard AMC platform, including a power supply module, an intelligent management unit, a processor unit, a logic unit, an SRIO switching module and a Gigabit Ethernet switching module, and the power supply module is used to supply power to the entire board , the intelligent management unit communicates with the processor unit, the logic unit is connected to the processor unit through the SRIO switch module, and the processor unit is also connected to the Gigabit Ethernet switch module. The processor unit includes a P2020 processor produced by Freescale, P2020 The processor is externally connected with 64-bit DDR3 SDRAM, and 3 FLASH chips are connected by CPLD logic. The invention improves the data processing ability through the P2020 processor, and increases the signal exchange speed by combining the SRIO switching module and the Gigabit Ethernet switching module. The P2020 processor is externally connected with 4 pieces of 64-bit 512MBx16 DDR3 SDRAM chips and 3 pieces of FLASH, so that the present invention has strong data storage performance and helps to strengthen the data processing and transmission capabilities of the P2020.

Owner:SICHUAN SDRISING INFORMATION TECH

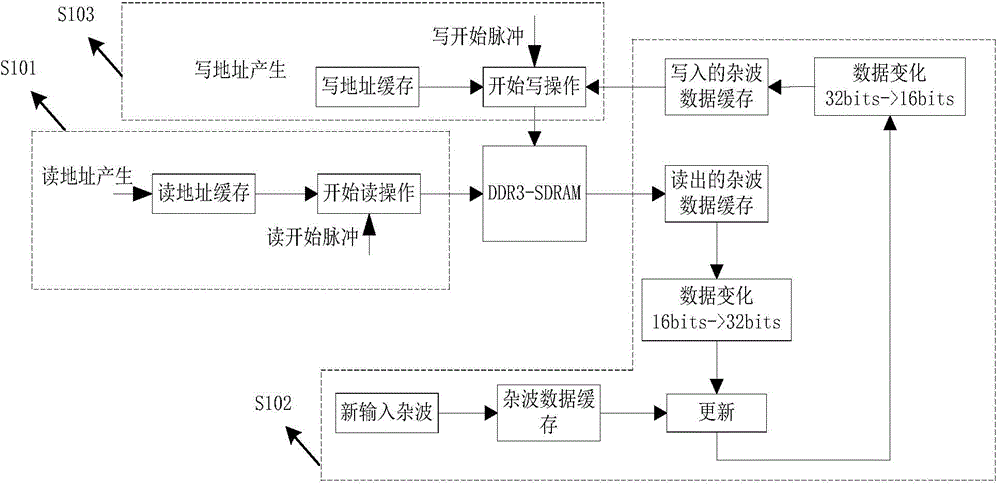

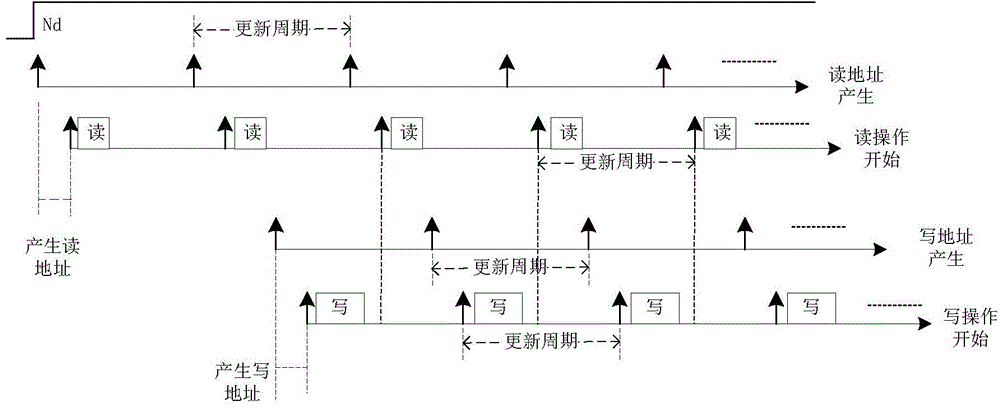

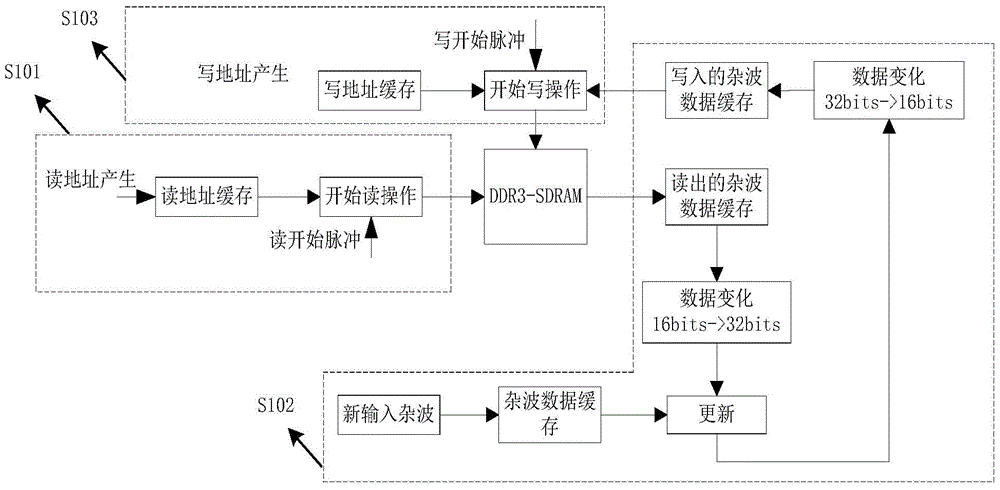

Five-dimensional dynamic stereoscopic clutter map implementation method based on DDR3-SDRAM

ActiveCN104535980AEasy accessEasy to handleWave based measurement systemsClustered dataComputer science

The invention relates to a five-dimensional dynamic stereoscopic clutter map implementation method based on a DDR3-SDRAM. According to the five-dimensional dynamic stereoscopic clutter map implementation method, reading and writing control over the DDR3-SDRAM is achieved through an FPGA, and then a five-dimensional dynamic stereoscopic clutter map is established. The method comprises the following steps that (a) reading operation is conducted on the DDR3-SDRAM, and clutter data are read out; (b) a clutter map is updated through a recursive filter, and data conversion is conducted; (c) the updated cluster data are rewritten to the corresponding position of the DDR3-SDRAM, updating of the cluster map is completed, and a clutter map is established. Compared with a traditional cluster map implementation method, the five-dimensional dynamic stereoscopic clutter map implementation method based on the DDR3-SDRAM is characterized in that a clutter area is finely divided, and besides traditional distance division, direction division and pitching division, a PRF mode and clutters of a full-Doppler channel are also divided. Clutter data are specially processed, the storage capacity of the clutter map is doubled.

Owner:CNGC INST NO 206 OF CHINA ARMS IND GRP

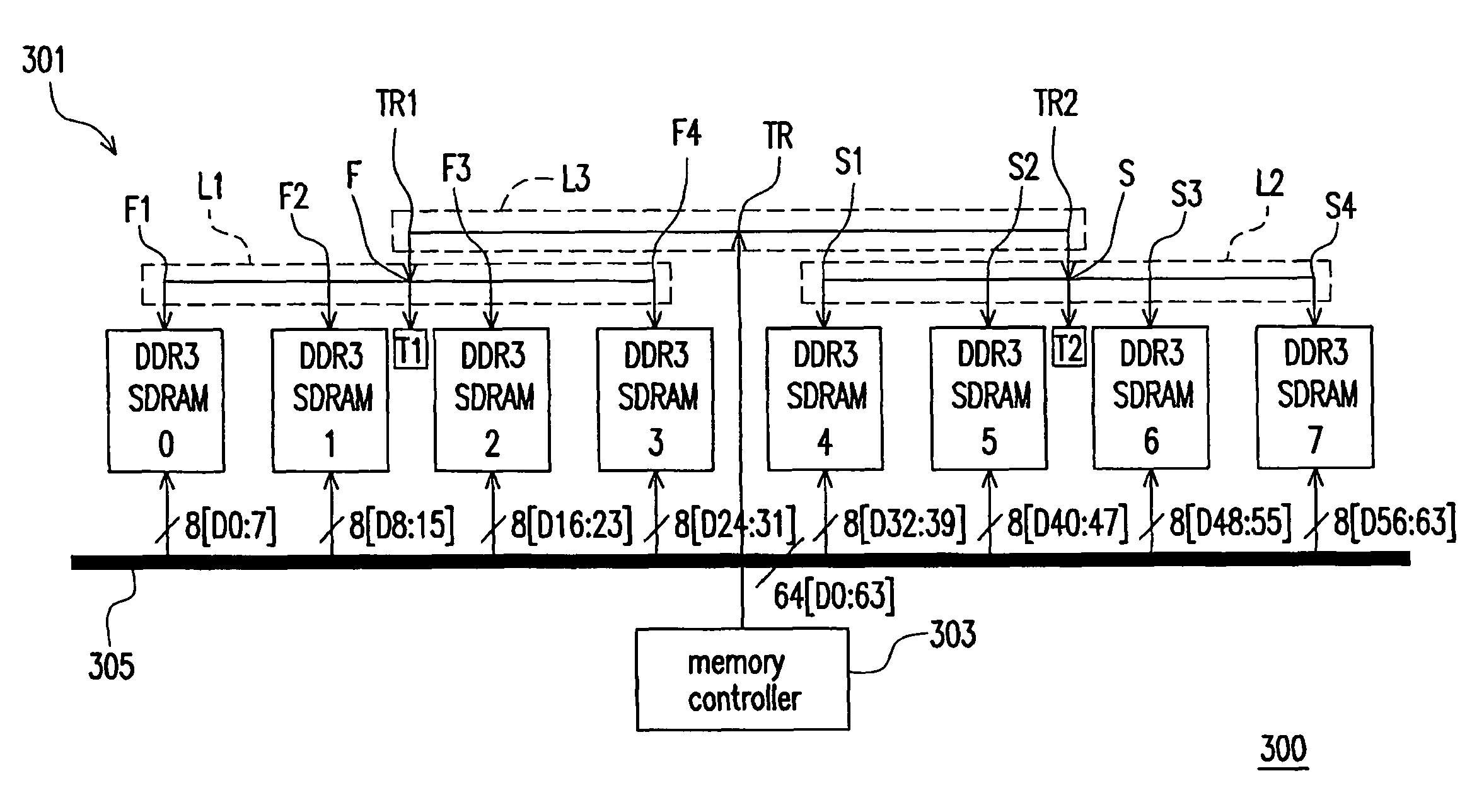

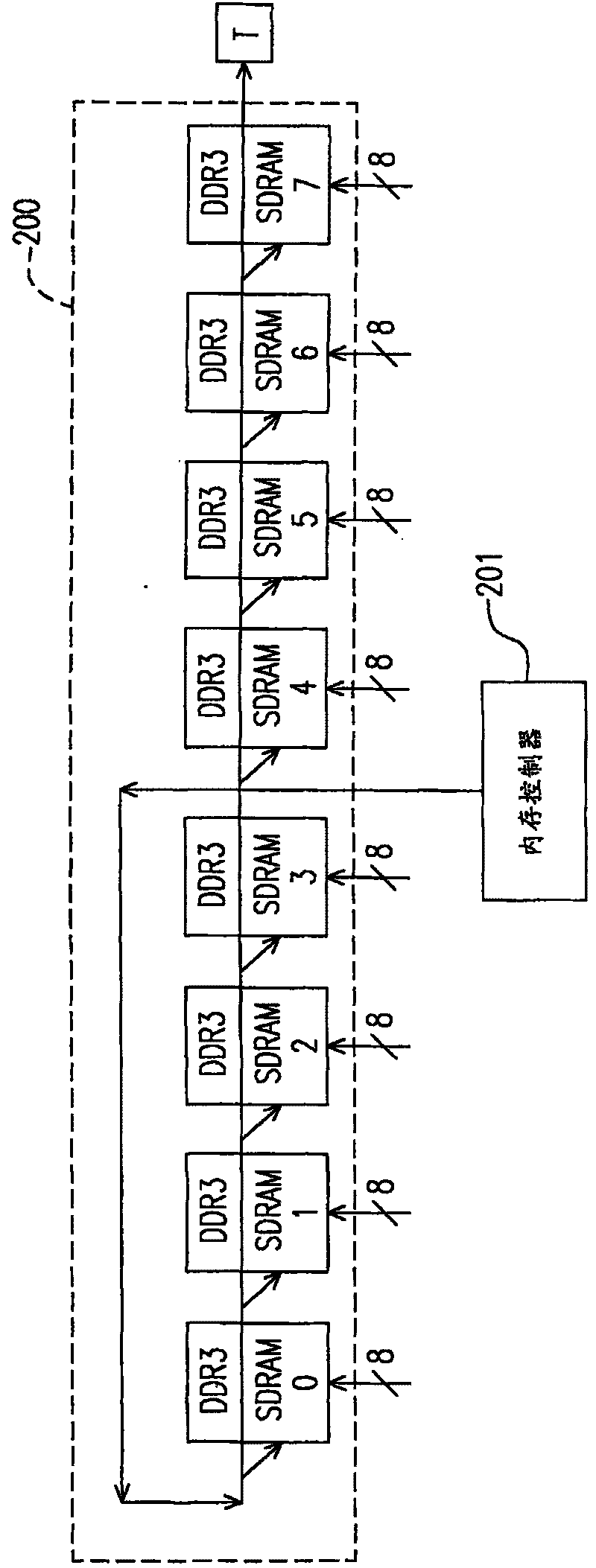

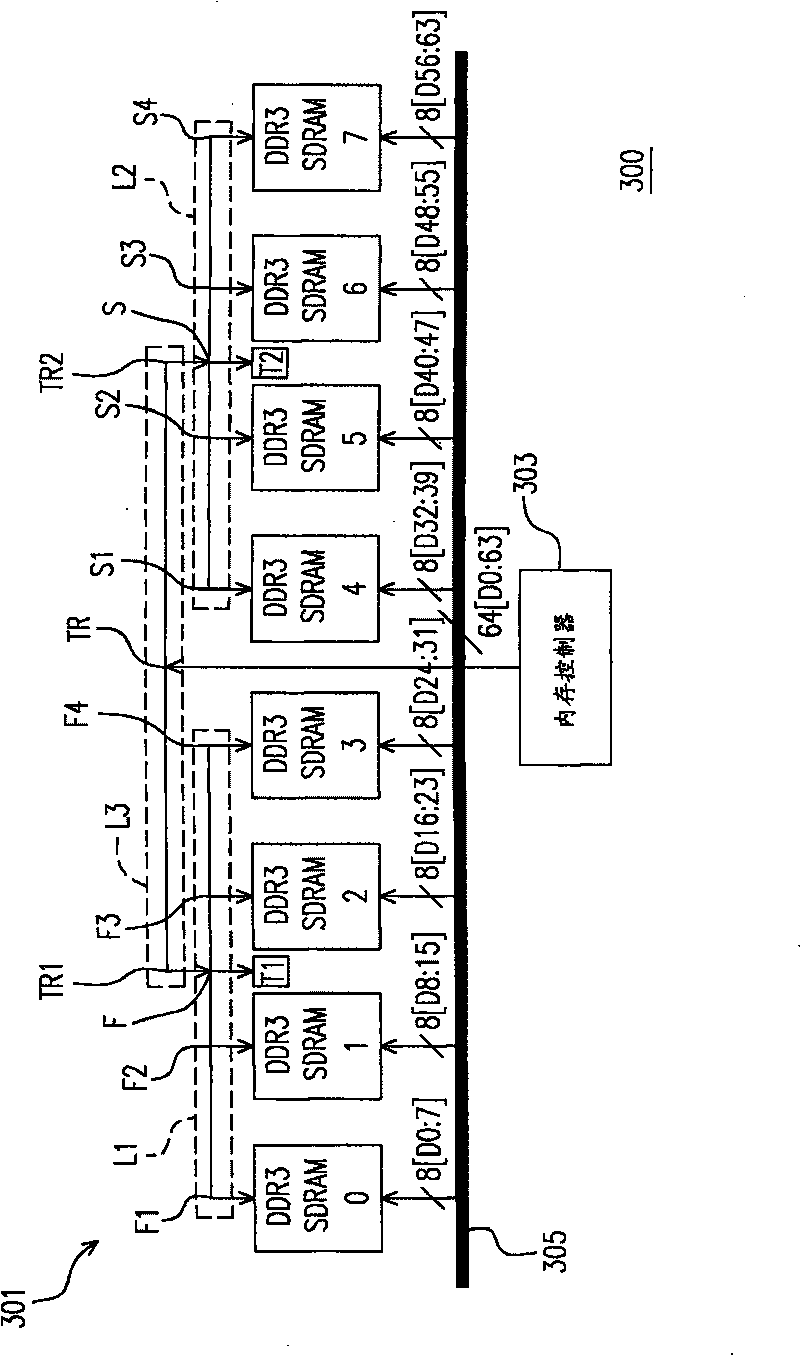

Motherboard and memory device thereof

ActiveUS8031504B2Wiring mode for laying out the wires on the motherboard is simpleImprove system performanceDigital storageMemory systemsEngineeringBus network

A memory device can be directly mounted on a motherboard supporting DDR3 SDRAM, and then the memory device have advantages of the fly-by bus topology and the T branch topology established by the joint electron device engineering council (JEDEC). Thus, the system performance of a desktop computer in a unit interval can be enhanced.

Owner:ASUSTEK COMPUTER INC

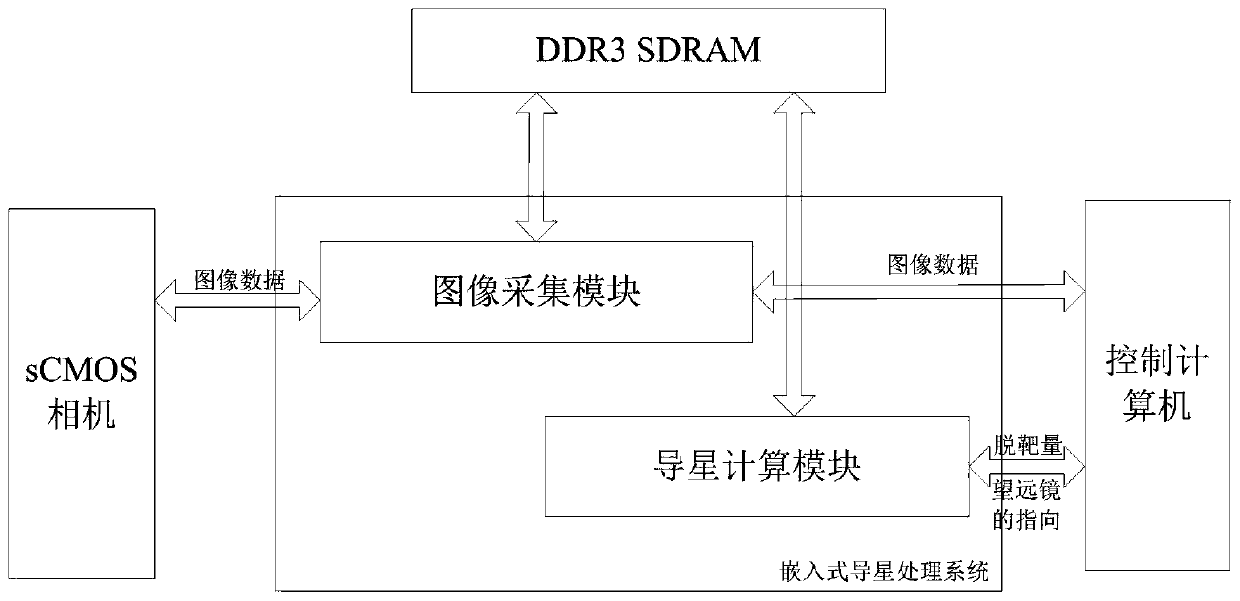

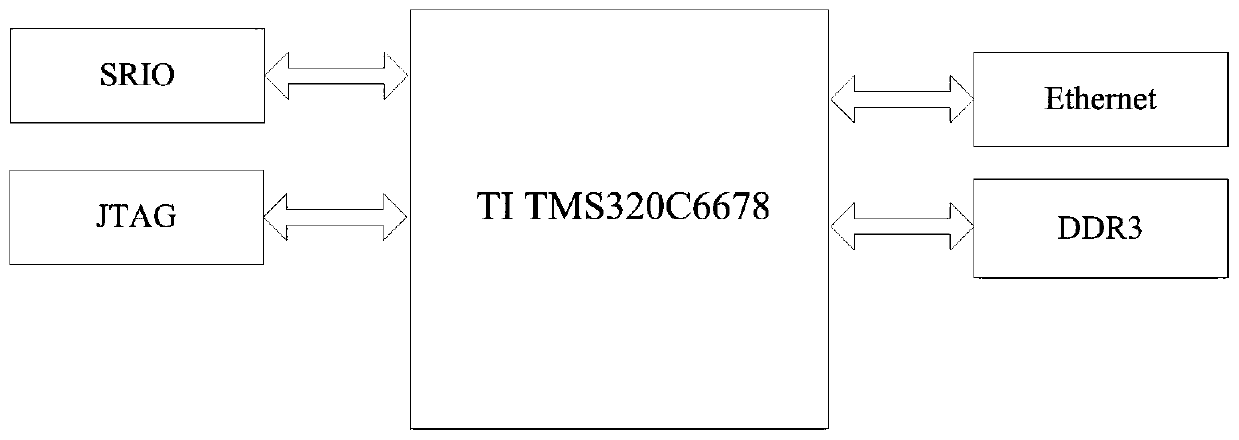

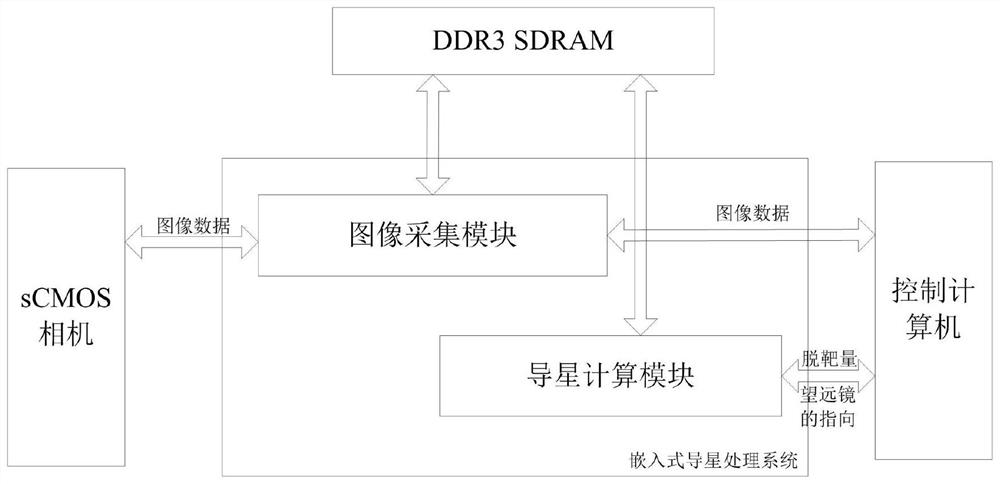

Embedded guiding star processing system

ActiveCN109991900ABig amount of dataEasy to implementProgramme controlTelevision system detailsAstronomical telescopesHandling system

The invention discloses an embedded guiding star processing system, relates to a space target guiding star-oriented embedded processing system, and aims at solving the problem that the existing imageacquisition and processing systems are difficult to answer huge real-time data size and difficult to guide stars so that the main visual fields cannot observe space targets for a long time. The systemcomprises an image acquisition module and a guiding star calculation module, wherein the guiding star calculation module adopts a guiding star processing system constructed by FPGA and DSP heterogeneous processors; the image acquisition module acquires video signals of an sCMOS camera in real time and stores the video signals to a DDR3 SDRAM; and the image data in the DDR3 SDRAM is transmitted tothe guiding star calculation module. According to the system, strong image processing and calculation analysis abilities are provided, space targets can be recognized and accurate mass center positions of the space targets can be obtained, the calculated error vectors are converted into practical miss distances of telescopes, and the practical miss distances are fed back to pointing control systems of the astronomical telescopes. The embedded guiding star processing system is capable of improving the stability and accuracy of the guiding stars and achieving the long-time observation for the targets.

Owner:中国科学院国家天文台长春人造卫星观测站

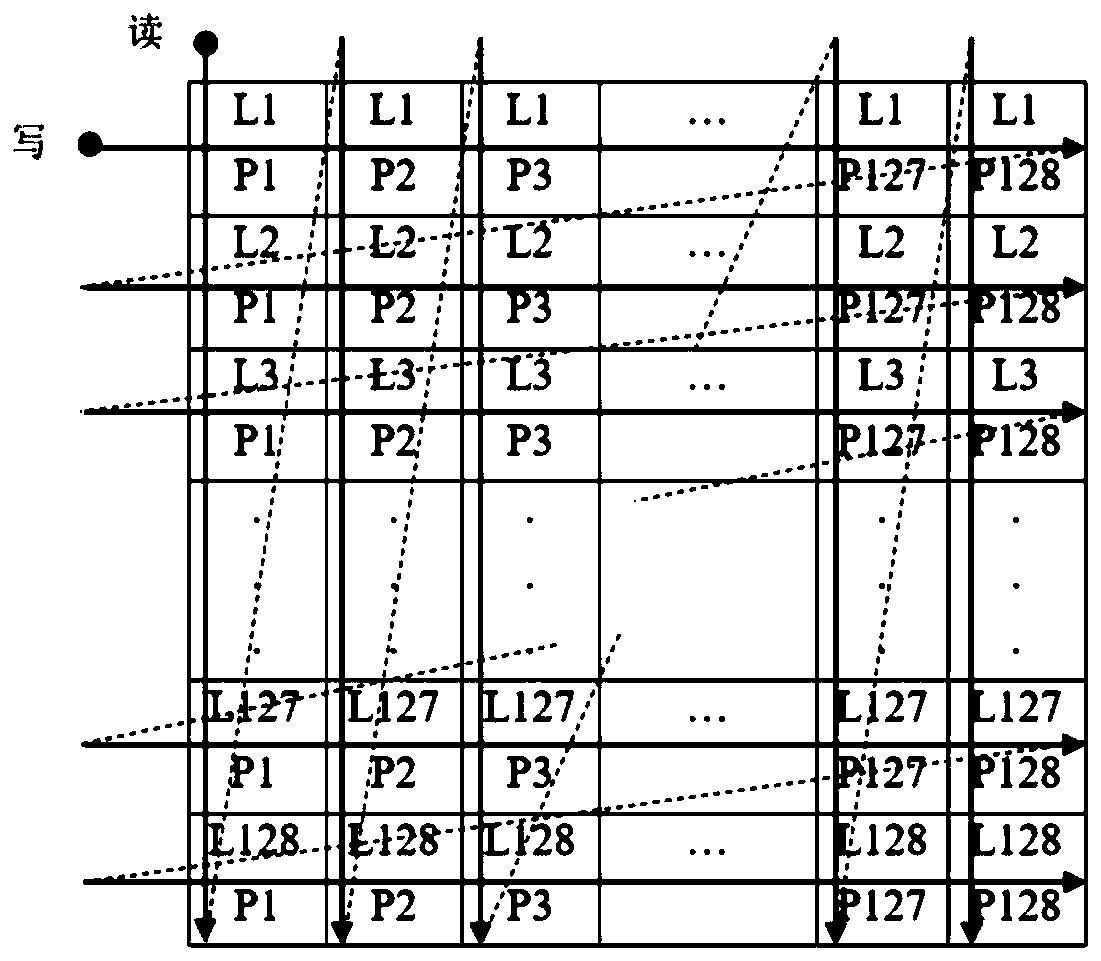

DDR-based high-efficiency matrix transposition processing method

ActiveCN110781447AImprove efficiencyTroubleshoot processing rate dropsEnergy efficient computingComplex mathematical operationsComputer hardwareComputer architecture

The invention discloses a DDR-based high-efficiency matrix transposition processing method. The method comprises the following steps of matching a write RAM and a read RAM with an IP core of a DDR3 SDRAM; wherein a to-be-transposed matrix is a 128 * 128 matrix with 64 bits of single data, and data of each row of the to-be-transposed matrix is taken as a small matrix; writing 16 data in each activesignal in the writing operation process; reading 8 * 16 pieces of data by each active signal in the reading operation process; and performing reading in DDR according to a same inter-row and data cyclic skip rule, so that the occurrence of row active signals is reduced as much as possible. According to the invention, the problem that the overall processing rate of the system is reduced due to the jump access of the DDR SDRAM in large-order matrix transposition is solved. By the matrix partitioning technology, on the basis that the writing rate is reduced to a small extent, the reading rate is greatly increased, the DDR reading and writing rate is balanced when a matrix is transposed, and therefore the average DDR reading and writing efficiency is improved.

Owner:TIANJIN UNIV

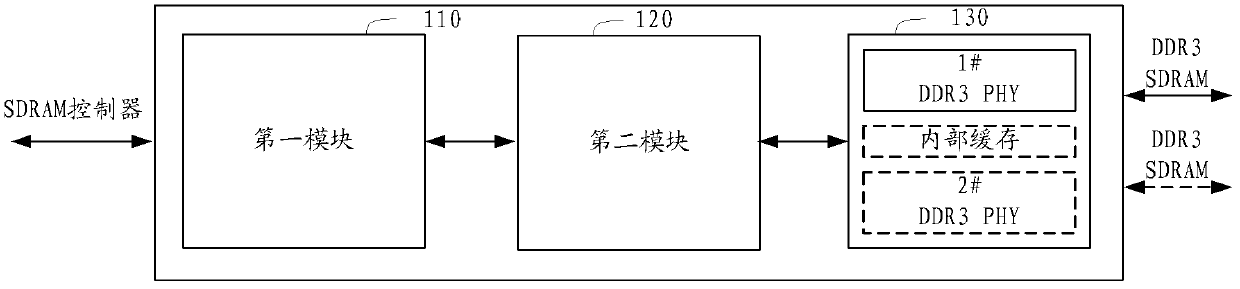

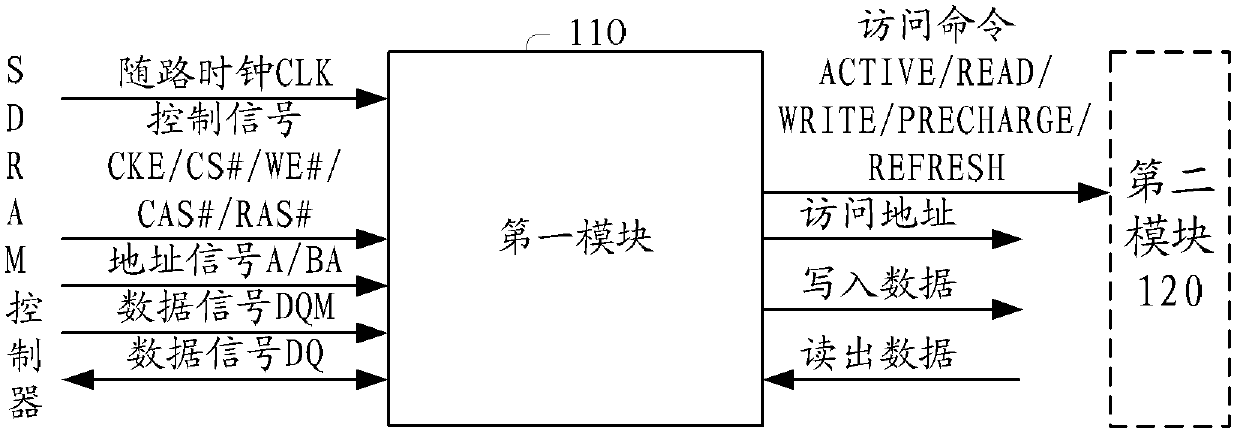

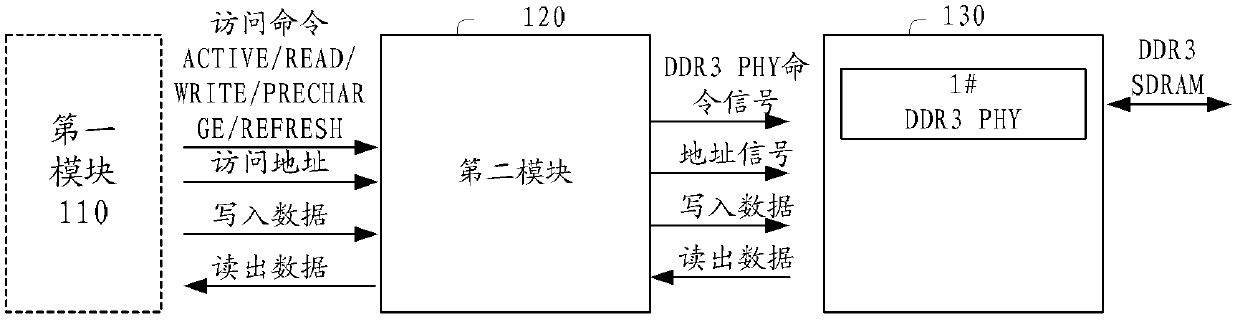

SDRAM bridge circuit

The invention relates to an SDRAM bridge circuit, comprising a first module, a second module and a PHY module, wherein the first module is used for analyzing SDRAM access commands sent by a controller, the second module is used for converting the SDRAM access commands into commands which are acceptable to the PHY module, the PHY module is used for accessing a memory by using the commands which are acceptable to the PHY module, and the memory and the controller are different in SDRAM type. According to the invention, the SDRAM controller can be allowed to realize the access to the DDR3 SDRAM to carry out data access through the bridge circuit; compared with replacing or redeveloping chips of the integrated SDRAM controller, the circuit modification is small, the development period is short, the cost is low, and the bridge circuit is well compatible with the original system.

Owner:HUAWEI TECH CO LTD

Adaptive Novel Memory Matching Data Strobe Method

InactiveCN102298974AAvoid effectivenessAvoid environmental problemsStatic storageDDR2 SDRAMPhase point

The present invention relates to data storage technology. The present invention solves the problem that the existing same system is easy to cause memory overflow and collapse when using new memory and / or new memory from different manufacturers in different temperature environments, and provides a self-adaptive new memory matching data strobe pulse The method, and its technical solution can be summarized as: detecting the high-order and low-order DQS / DQ phase points of each DDR SDRAM at each initialization to obtain an effective point, and then selecting the intermediate value to preset as an environmental parameter. The invention has the beneficial effects of stable operation and is suitable for systems using DDR2 SDRAM and / or DDR3 SDRAM.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

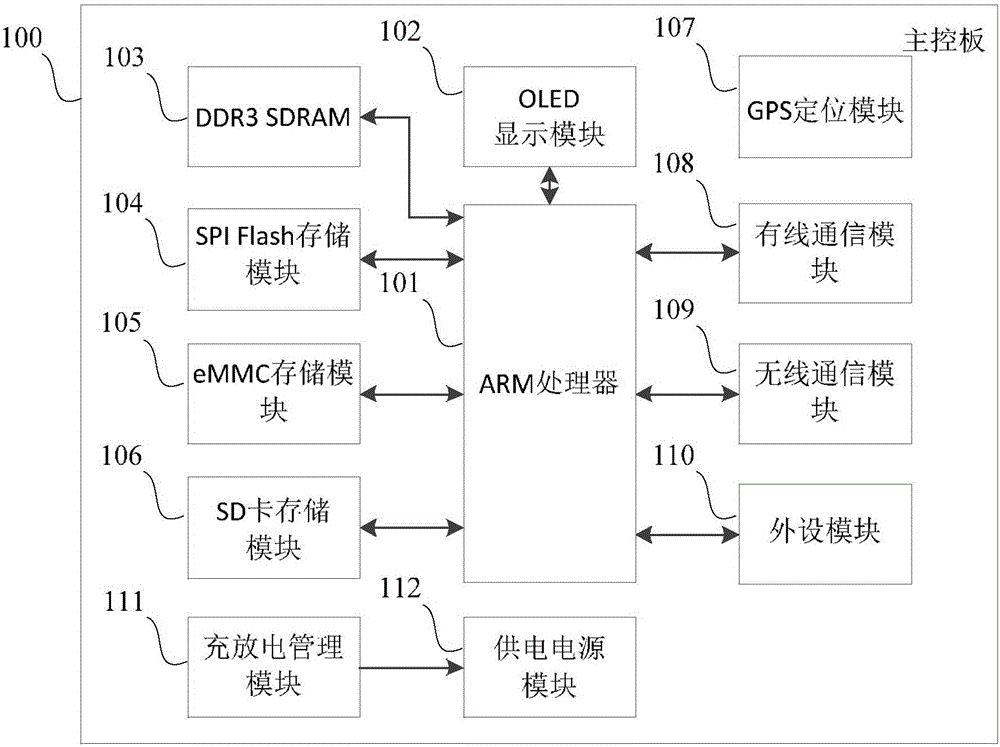

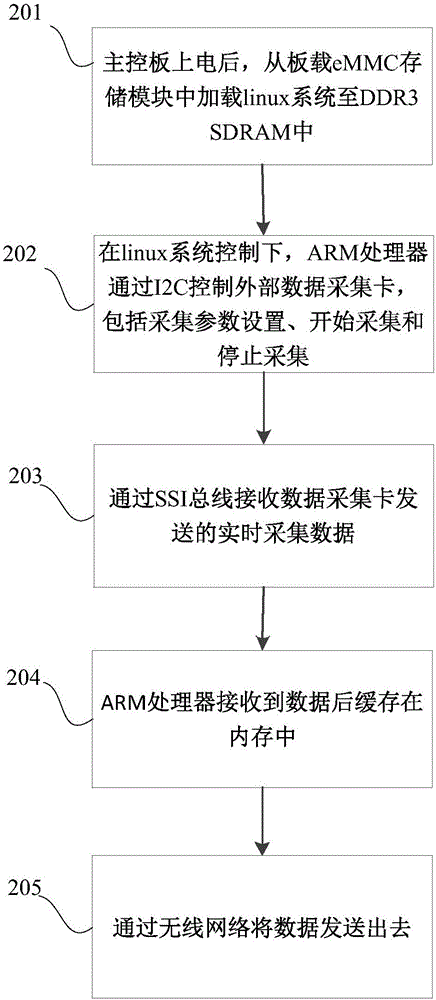

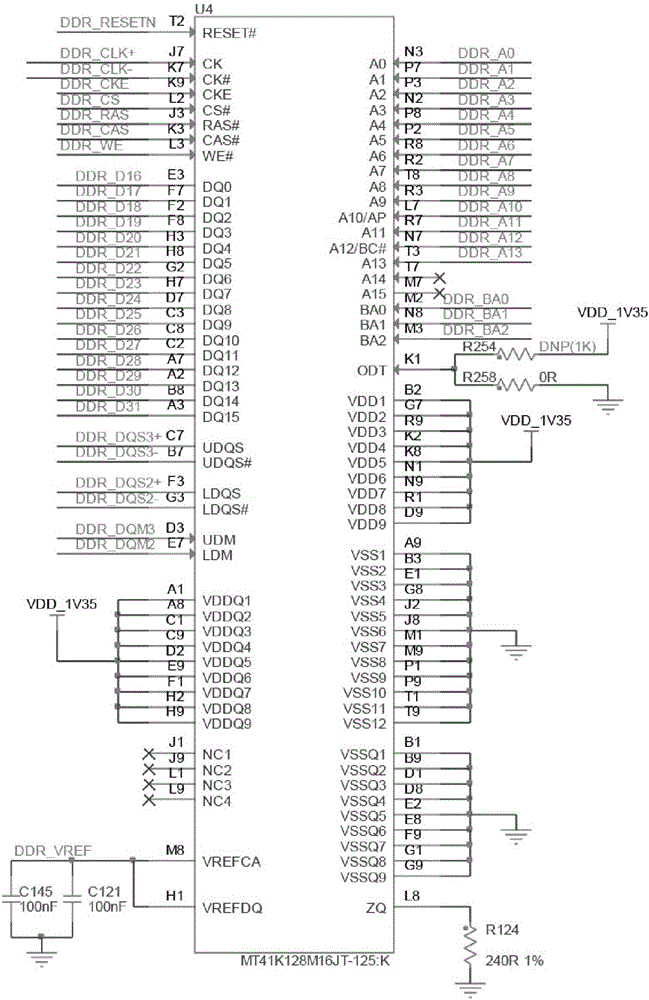

Multipurpose low-power control device and multipurpose low-power control method for dynamic characteristic tests

InactiveCN106773948AImprove compatibilityPerfectly compatibleProgramme controlComputer controlAC adapterDouble data rate

The invention discloses a multipurpose low-power control device and a multipurpose low-power control method for dynamic characteristic tests. The multipurpose low-power control device comprises an ARM [advanced RISC (reduced instruction set computer) machine] processor, an OLED (organic light emitting diode) display module, a DDR3 SDRAM (double data rate 3 synchronous dynamic random access memory), an SPI (serial peripheral interface) Flash storage module, an eMMC (embedded multimedia card) storage module, an SD (secure digital) card storage module, a GPS (global positioning system) positioning module, a wire communication module, a wireless communication module, a charge and discharge management module, a power supply module and a peripheral module. Battery charge and discharge can be managed by the charge and discharge management module, and external AC adapter power supply and battery power supply paths can be dynamically switched over according to requirements of systems. The multipurpose low-power control device and the multipurpose low-power control method have the advantages that the problem of poor compatibility of existing master control and data acquisition cards can be solved by the aid of the multipurpose low-power control device and the multipurpose low-power control method, and the multipurpose low-power control device and the multipurpose low-power control method are conveniently compatible with existing high-precision universal data acquisition cards.

Owner:BEIJING T&S TECHNOLOGIES CO LTD

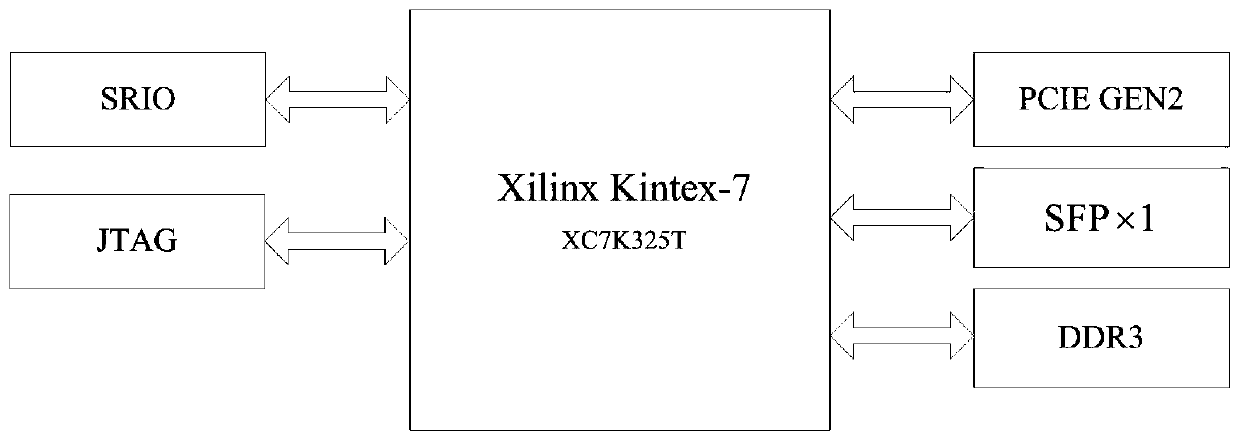

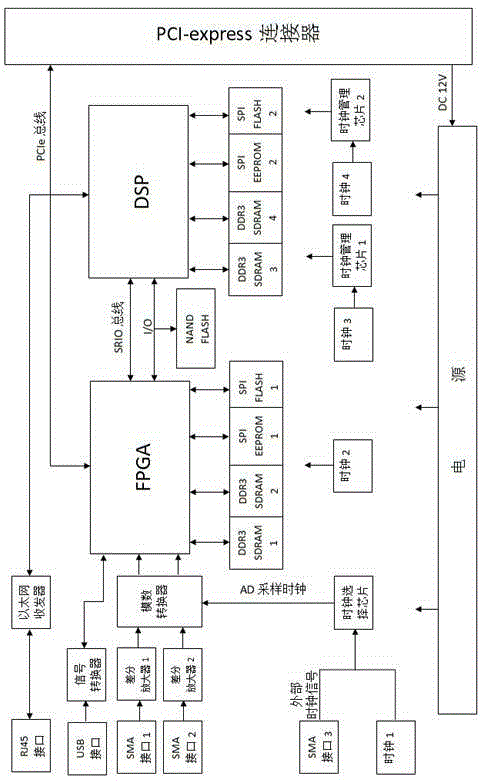

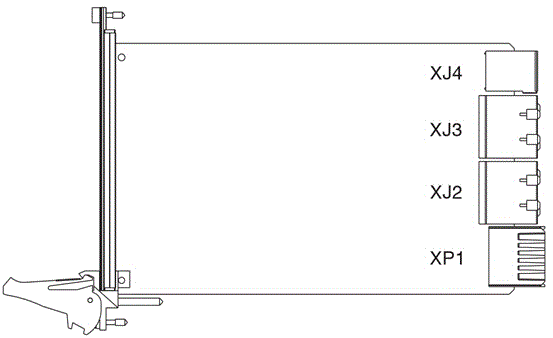

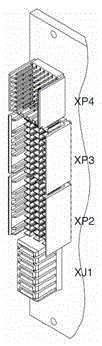

Double-channel high-speed analog digital signal collecting and processing board card

InactiveCN105320633AGuaranteed accuracyImprove efficiencyElectric digital data processingTransceiverPCI Express

The invention discloses a double-channel high-speed analog digital signal collecting and processing board card. The board card comprises an FPGA, a DSP, four DDR3 SDRAMs, two SPI EEPROMs, two SPI FLASHs, two differential amplifiers, an analog-digital converter, an NAND FLASH, an Ethernet transceiver, a PCI-express connector, a clock selecting chip and clock managing chips, wherein the clock selecting chip and the clock managing chips are connected with clocks respectively. The mature and reliable components are adopted in the design, the normative circuit design is supplemented, and accuracy and efficiency of signal collecting and processing are ensured. The standard 3U board card size is adopted and can be matched with a standard 3U case. The standard PCI-express connector is adopted to be in butt joint with a case or a board card with a corresponding interface conveniently to achieve data interaction between the signal collecting and processing board card and other structures of a system.

Owner:TOEC TECH

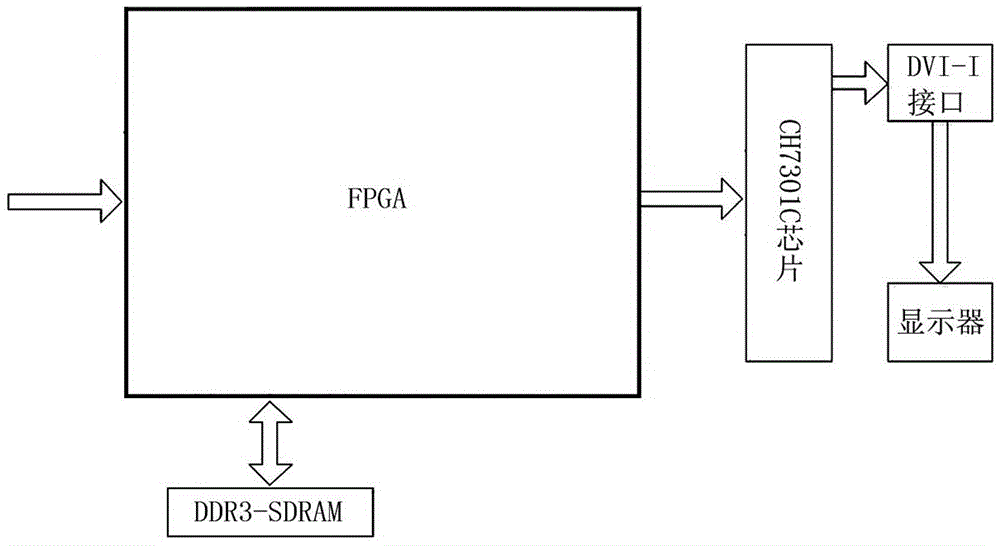

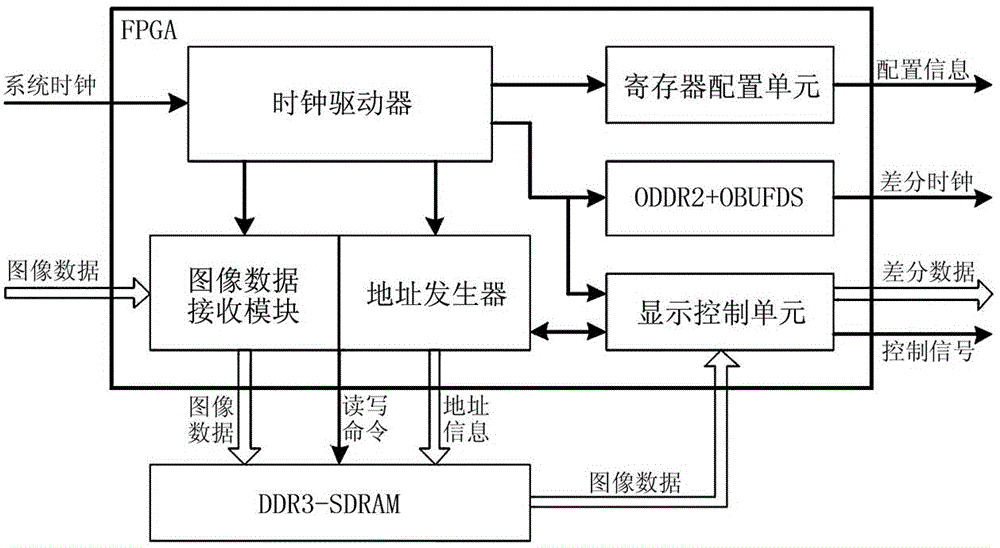

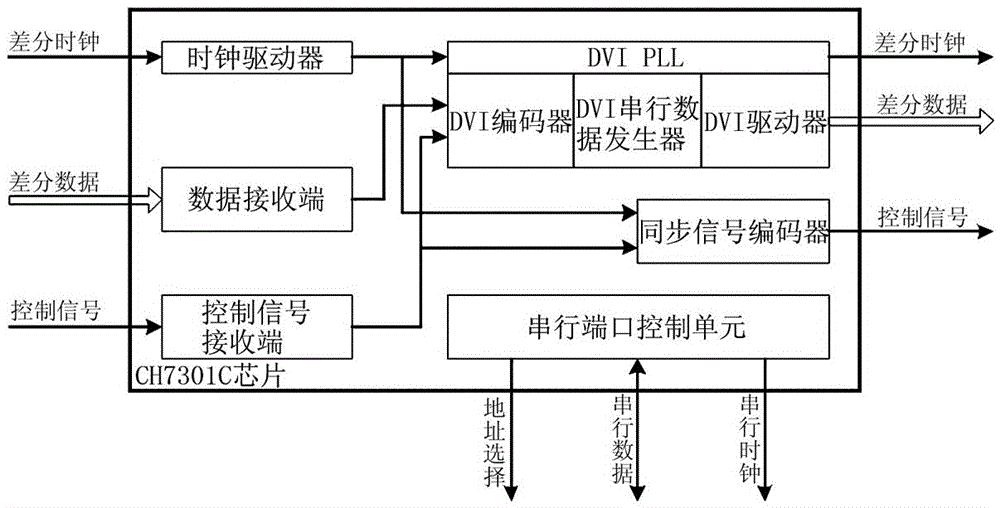

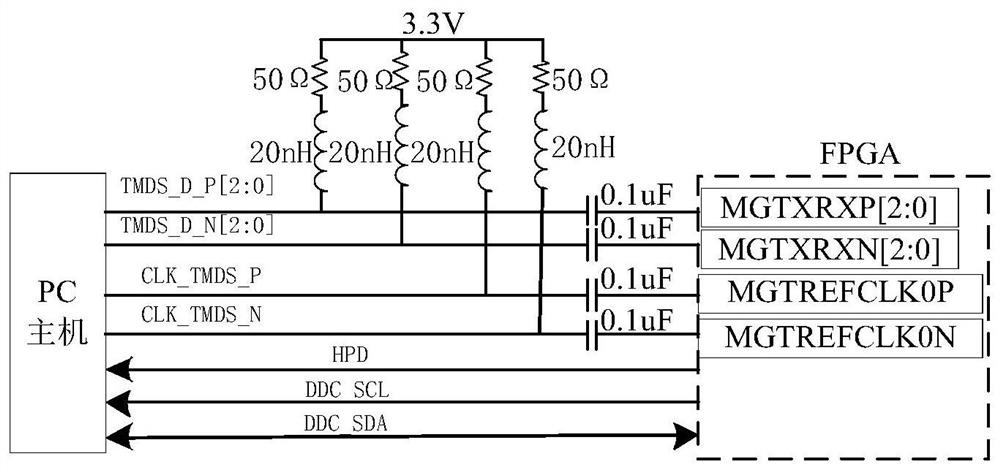

FPGA-based digital video display interface module and communication method thereof

ActiveCN106713805AIncrease cache rateImprove the display effectTelevision system detailsStatic indicating devicesDigital videoComputer module

The invention relates to display interfaces, in particular to an FPGA-based digital video display interface module and a communication method thereof, through which the problem of the conventional display interface that an insufficient cache rate causes smearing of an image displayed on equipment is solved. The FPGA-based digital video display interface module comprises an FPGA, a DDR3-SDRAM, a CH7301C chip, and a DVI-I interface, wherein the FPGA is connected with both the DDR3-SDRAM and the CH7301C chip, the CH7301C chip is connected with the DVI-I interface, and the DVI-I interface is connected with a display. The FPGA-based digital video display interface module and the communication method thereof provided by the invention are applicable to aerospace, military, medicine and other fields.

Owner:ZHONGBEI UNIV

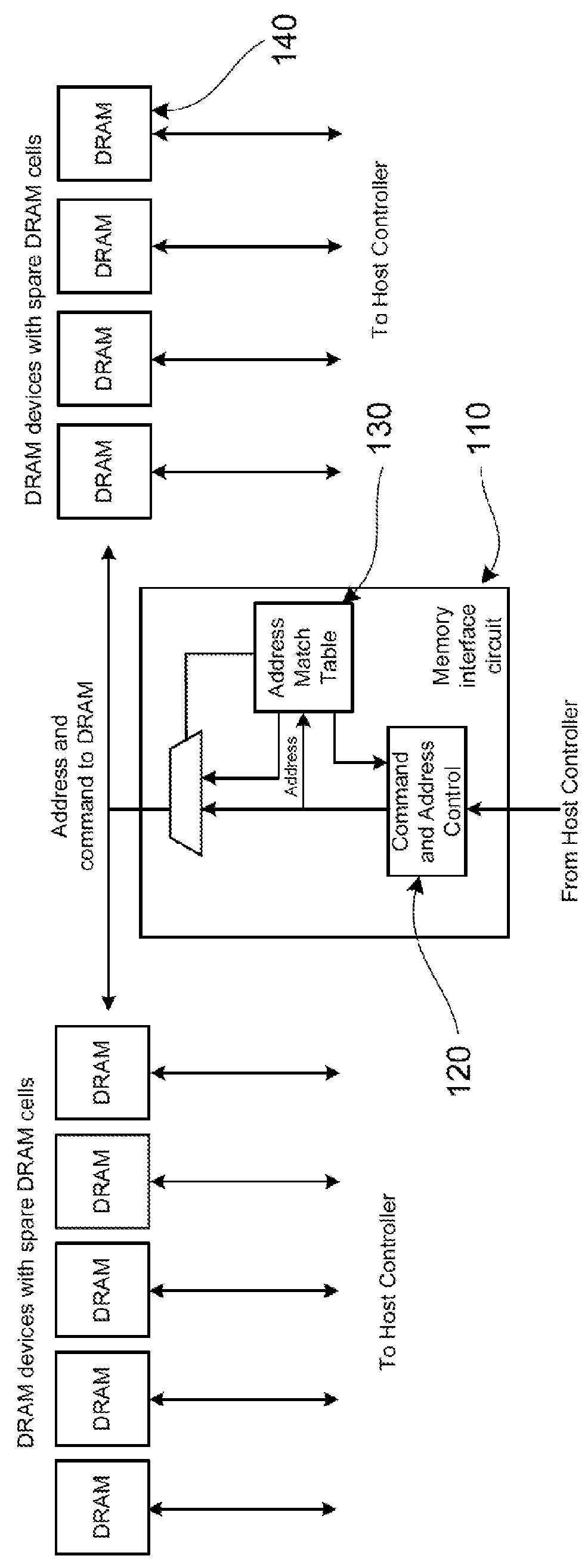

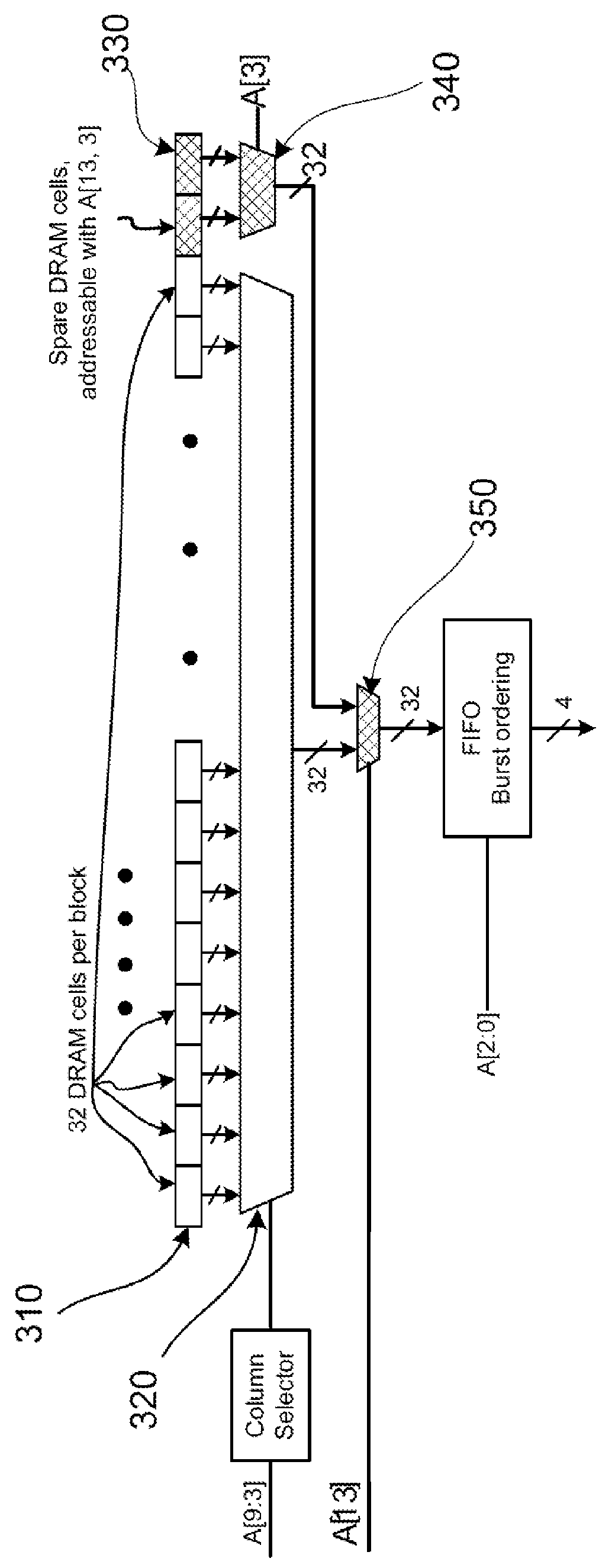

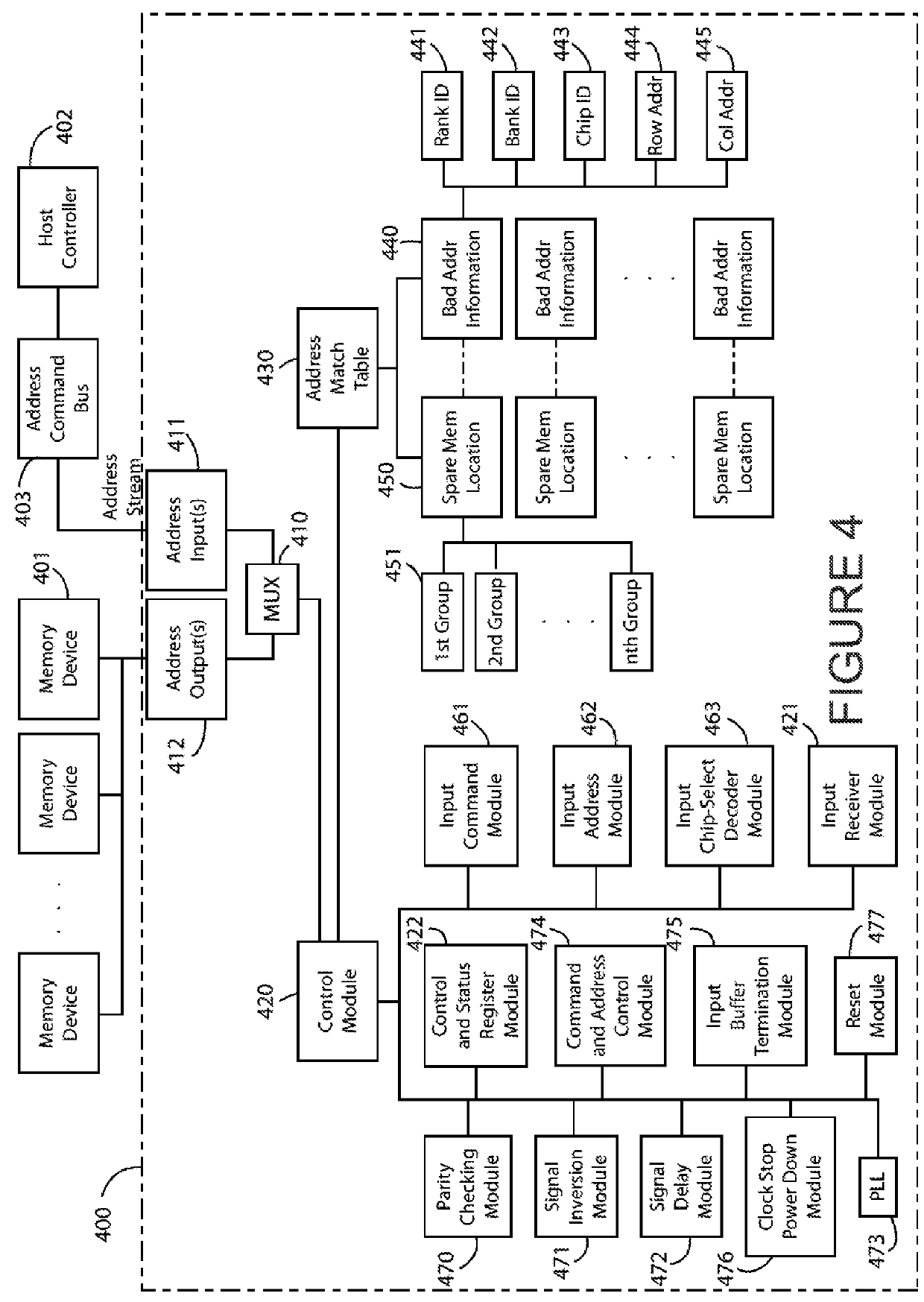

Memory parametric improvements

ActiveUS9230635B1Increase refresh timeHigh bandwidthDetecting faulty computer hardwareMemory adressing/allocation/relocationRandom access memoryDDR4 SDRAM

A method for manufacturing a dynamic random access memory device is provided. The method includes fabricating a dynamic random access memory device having a plurality of memory cells. Each of the memory cells has a refresh characteristic that meets or exceeds a refresh specification provided for a DDR3 SDRAM device or a DDR4 SDRAM device. The method includes testing the dynamic random access memory device. The testing includes determining the refresh characteristic for each of the memory cells, classifying each of the memory cells as a good memory cell or a bad memory cell based upon the refresh characteristic, identifying each of the bad memory cells, and storing an address location for each of the bad memory cells. The method then includes transferring the address location for each of the bad memory cells into an address match table.

Owner:RAMBUS INC

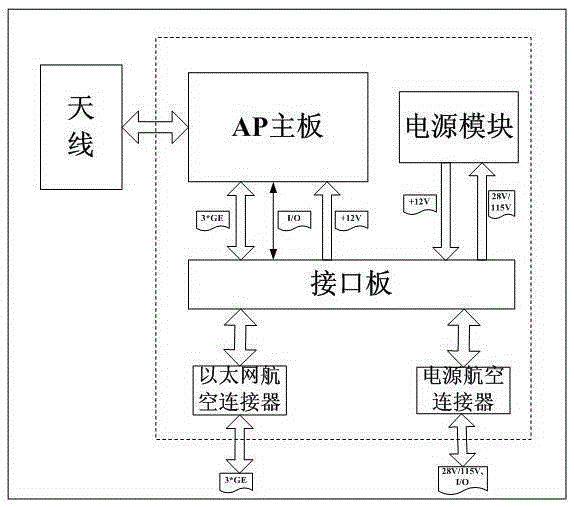

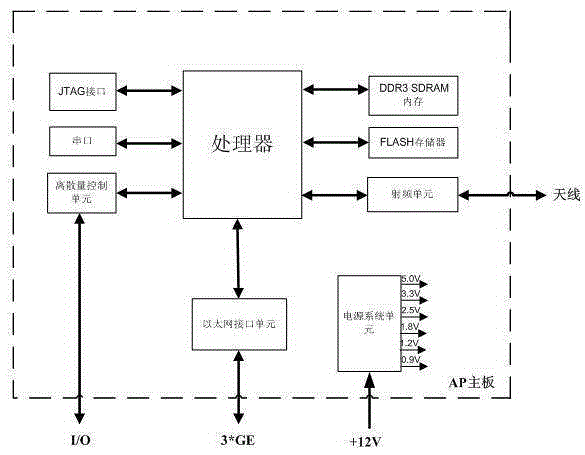

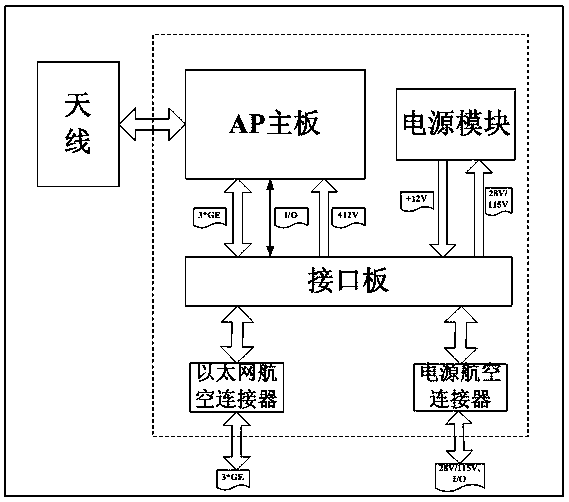

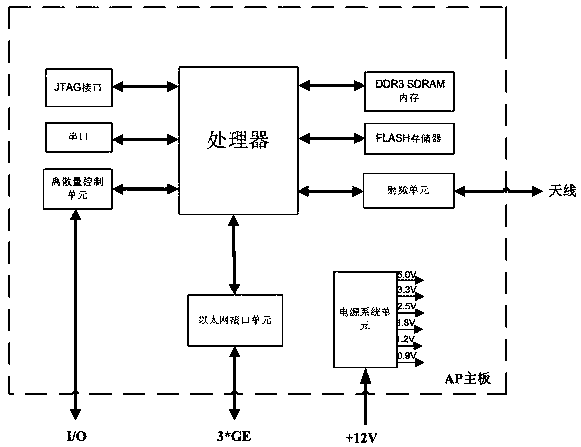

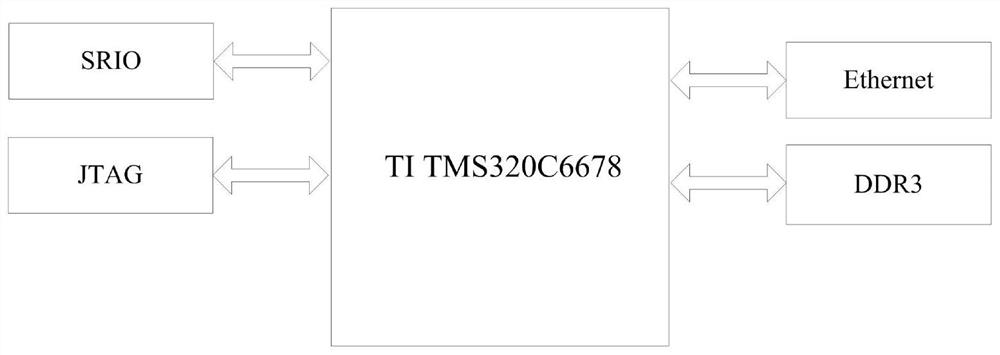

Airborne wireless access point (AP) device

ActiveCN105338665ASimple structureStrong reliabilityWireless communicationAviationJoint Test Action Group

The invention discloses an airborne wireless access point (AP) device. The airborne wireless AP device comprises a power supply module, an AP main board, an interface board, an Ethernet airspace connector, a power supply aerospace connector and an antenna, wherein the antenna is connected with the AP main board, and the power supply module, the AP main board, the Ethernet aerospace connector and the power supply aerospace connector are respectively connected with the interface board. The AP main board comprises a processor, and an Ethernet interface unit, a discrete magnate control unit, a radio frequency unit, a DDR3 SDRAM memory, a flash memory, a JTAG interface and a serial port, which are respectively connected with the processor, and the AP main board also comprises a power supply system unit, and the power supply system unit is used for powering each device on the AP main board. The airborne wireless AP device can implement WIFI connection in a cabin and has advantages of improving the user experience. The application stability is good, and the practicability is high.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD

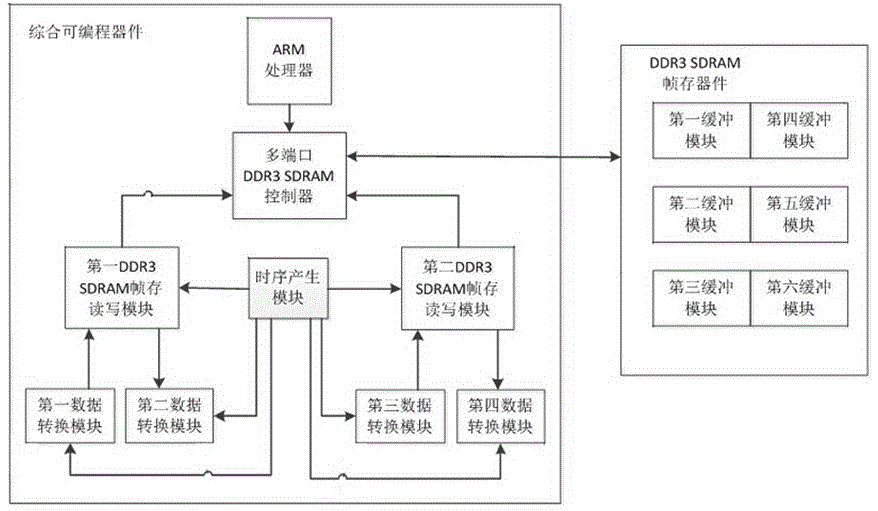

Double-screen different-image graphic generating system

InactiveCN105573703ARealize synchronous outputIncrease data bandwidthDigital output to display deviceGraphicsComputer module

The invention discloses a double-screen different-image graphic generating system. The system comprises a comprehensive programmable device and a DDR3 SDRAM frame memory device which are connected, wherein the comprehensive programmable device comprises an ARM processor, a multi-port DDR3 SDRAM controller, a first DDR3 SDRAM frame memory reading and writing module, a first data conversion module, a second data conversion module, a second DDR3 SDRAM frame memory reading and writing module, a thirddata conversion module, a fourth data conversion module and a timing sequence generation module; the DDR3 SDRAM frame memory device comprises a first buffer module, a second buffer module, a third buffer module, a fourth buffer module, a fifth buffer module and a sixth buffer module. The double-screen different-image graphic generating system is characterized by high circuit integration level, low power consumption and small size; synchronous output of double-screen different-image frames can be achieved, and the double-screen frames can be spliced into a complete frame; data bandwidth is high, and processing speed is high; graphic generation efficiency is high, and dynamic frame display is smooth; compatibility is high, and the system can support various high-resolution frames.

Owner:SUZHOU CHANGFENG AVIATION ELECTRONICS

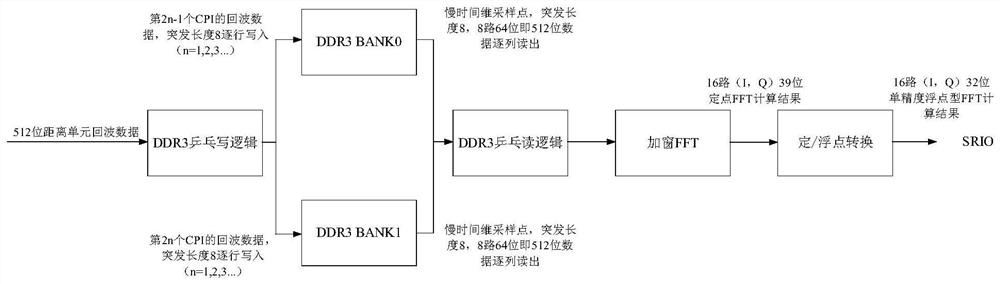

FPGA implementation method for LFMCW radar MTD processing

ActiveCN111830478AFast cacheCache, using the burst length of DDR3 to read and write fastProgramme controlWave based measurement systemsComputer architectureDouble data rate

The invention provides an FPGA implementation method for LFMCW radar MTD processing, and provides a method capable of realizing the LFMCW radar MTD processing on an FPGA aiming at the requirements ofan LFMCW radar system for the real-time performance and high throughput rate of the MTD processing. According to the method, the parallel processing capability of the FPGA and the high efficiency of pipeline processing and ping-pong operation processing can be fully utilized, and in cooperation with the characteristics of double data rate and large capacity of the DDR3 SDRAM, the bottleneck problems of the processing speed of the DSP and the storage space of the FPGA are solved, and finally, effectiveness and reliability of the method are proved through ModelSim simulation and actual system testing.

Owner:HARBIN ENG UNIV

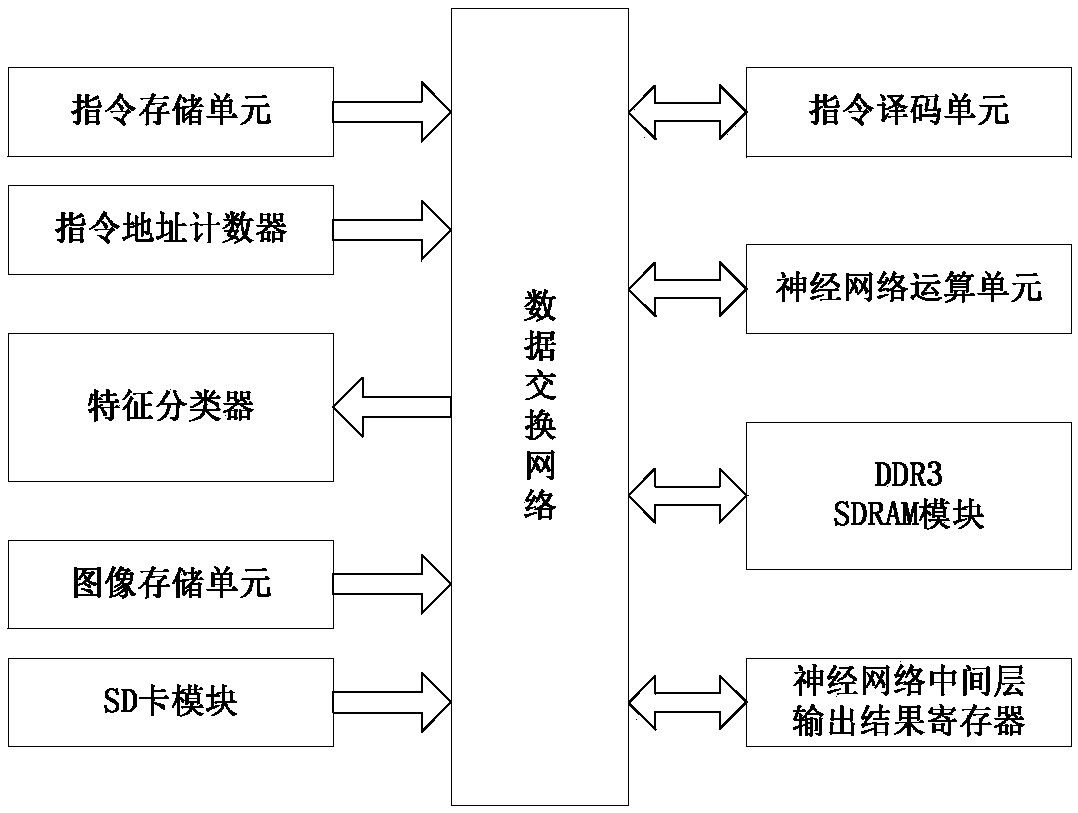

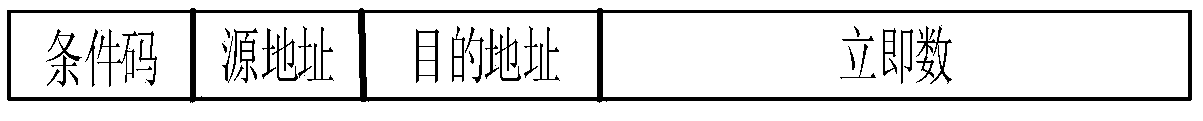

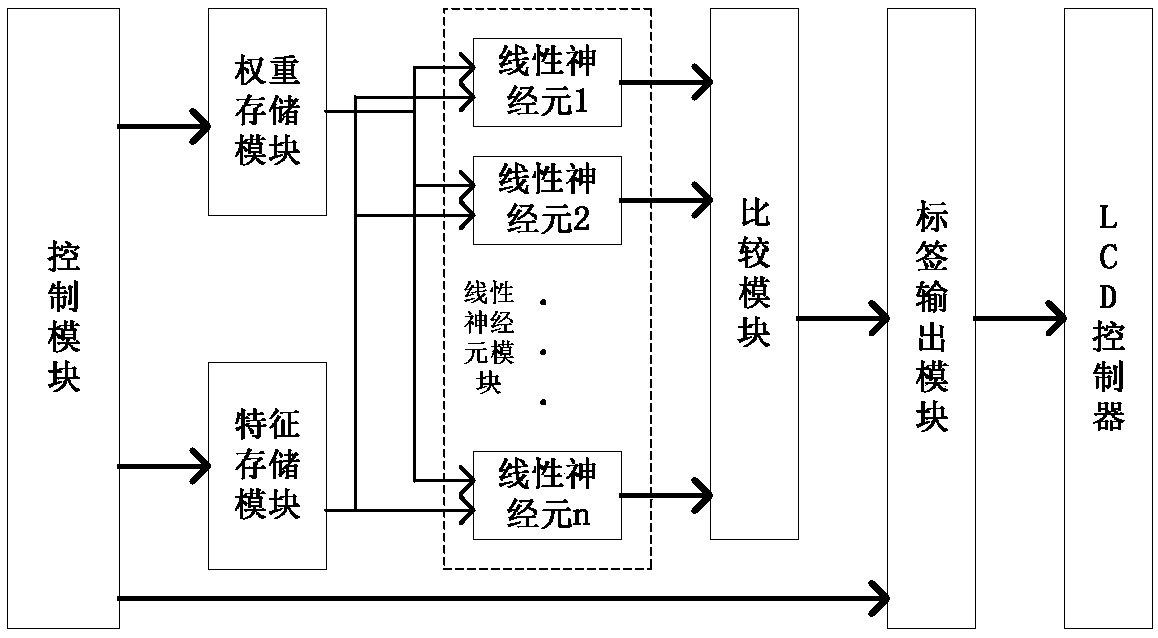

Neural network processor based on TTA architecture

InactiveCN107844831AScale upIncrease flexibilityConcurrent instruction executionProcessor architectures/configurationComputer architectureImaging processing

The invention provides a neural network processor based on TTA architecture. The neural network processor based on TTA architecture aims at giving consideration to low power consumption and high speedwhile increasing the neural network scale supported by the processor, and can improve flexibility of design of the processor. The neural network processor based on TTA architecture includes a data exchange network and a plurality of function units which are connected with the data exchange network through the TTA architecture mode, wherein the data exchange network and the function units except for an SD card module and a DDR3 SDRAM module are implemented through FPGA; the function units are used for realizing storage, control and decoding of commands and storage and operating of data; and the data exchange network is used for realizing transmission of the data among each function list. The neural network processor based on TTA architecture can be applied to an image processing system forperforming high speed and real-time processing and identification on images.

Owner:XIDIAN UNIV

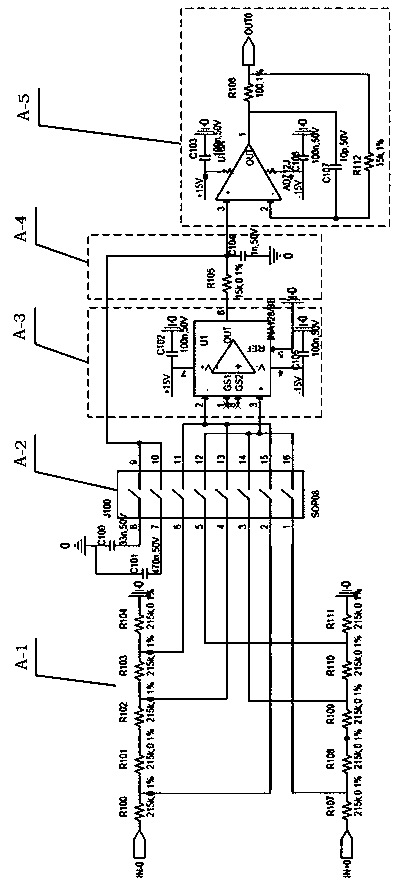

High-speed analog quantity acquisition board card based on FPGA + MCU

PendingCN110968001AAchieve high-speed acquisitionRealize command and controlProgramme controlComputer controlInstrumentation amplifierHemt circuits

The invention discloses a high-speed analog quantity acquisition board card based on FPGA + MCU. The high-speed analog quantity acquisition board card comprises a signal conditioning circuit, an ADC sampling circuit, an FPGA chip, an MCU processor and a communication module. The FPGA chip comprises an ADC controller, a front end FIFO memory, a DDR3 controller, a rear end FIFO memory and a DDR3 SDRAM memory. The signal conditioning circuit comprises a differential circuit, an 8-bit dial switch, an instrument amplifier, a low-pass filter circuit and a voltage follower circuit, and the signal conditioning circuit receives analog signals sent by sending equipment, filters noise of the analog signals, conditions the analog signals into + / -10V analog signals and outputs the + / -10V analog signals. According to the invention, the signal conditioning circuit is used for differential input; the voltage drop on the ground wire can be compensated; the input ranges of + / -50V, + / -25V and + / -12.5 V signals and the three low-pass filtering cut-off frequencies of 20Hz, 300Hz and 10kHz can be configured by toggling corresponding switches of the 8-bit dial switch, so that the detection of signals indifferent ranges and the filtering of noise in different frequency bands are realized.

Owner:HANGZHOU WOLEI INTELLIGENT TECH

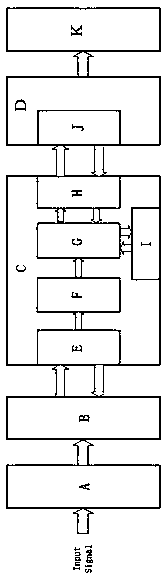

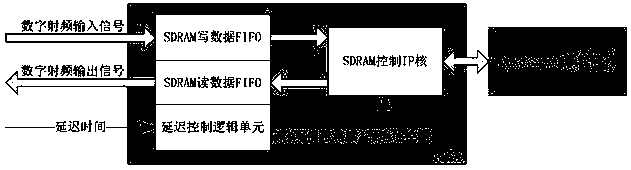

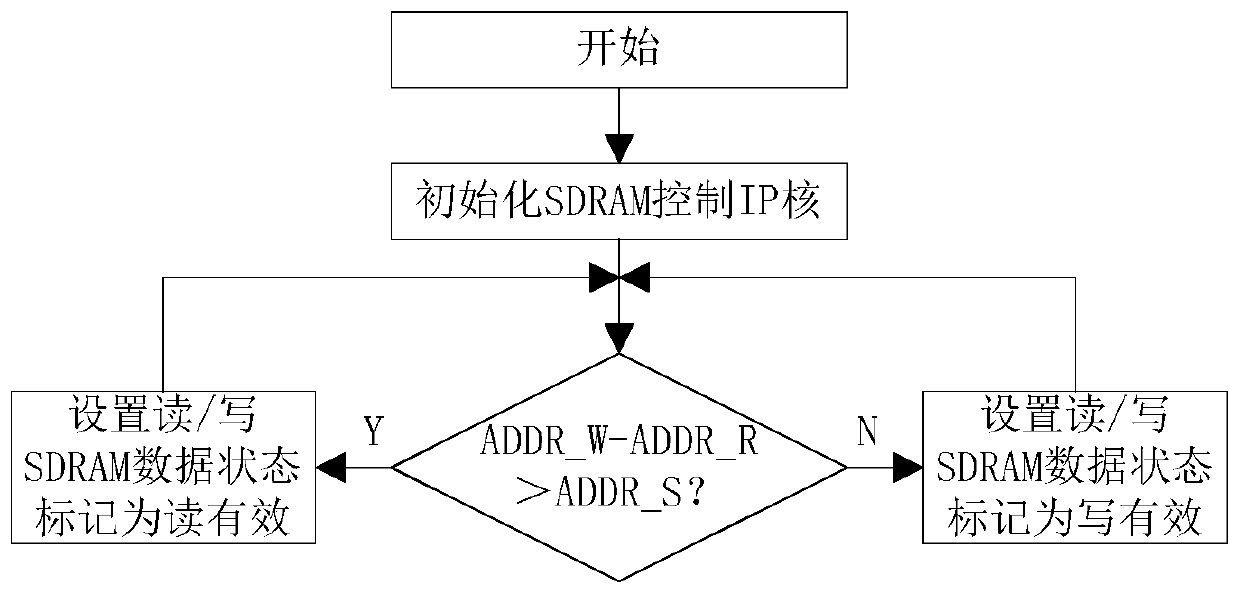

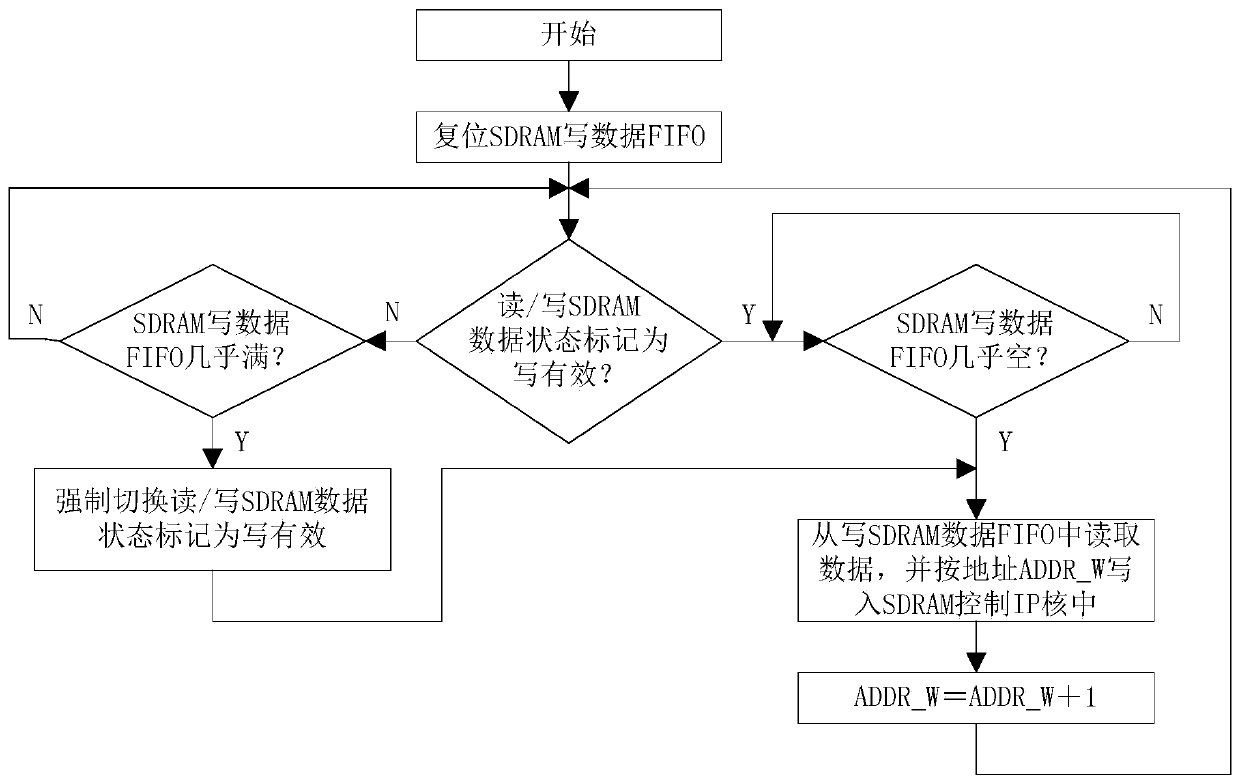

Pipelined digital radio frequency memory module

InactiveCN110287134AMeet the needs of digital radio frequency storageWave based measurement systemsElectric digital data processingComputer moduleRadio frequency

The invention provides a pipelined digital radio frequency memory module. A delay control logic unit generates an address written from SDRAM write data FIFO to DDR3 SDRAM according to a set delay time parameter. The DDR3 SDRAM is read out to an address of SDRAM read data FIFO The difference between these two addresses equal to delay time divided by DDR3 SDRAM read and write clock cycles A control SDRAM controls IP to read a nuclear time sheet to read SDRAM write data FIFO data and writes into data of SDRAM read data FIFO. At the position of written labeling of SDRAM read data FIFO, the time sheet is distributed to read and write SDRAM writedata FIFO data. At the position of written emptiness of SDRAM read data FIFO, the time sheet is distributed to read and write SDRAM writedata FIFO data.

Owner:NANJING GUORUI ANTAIXIN TECH

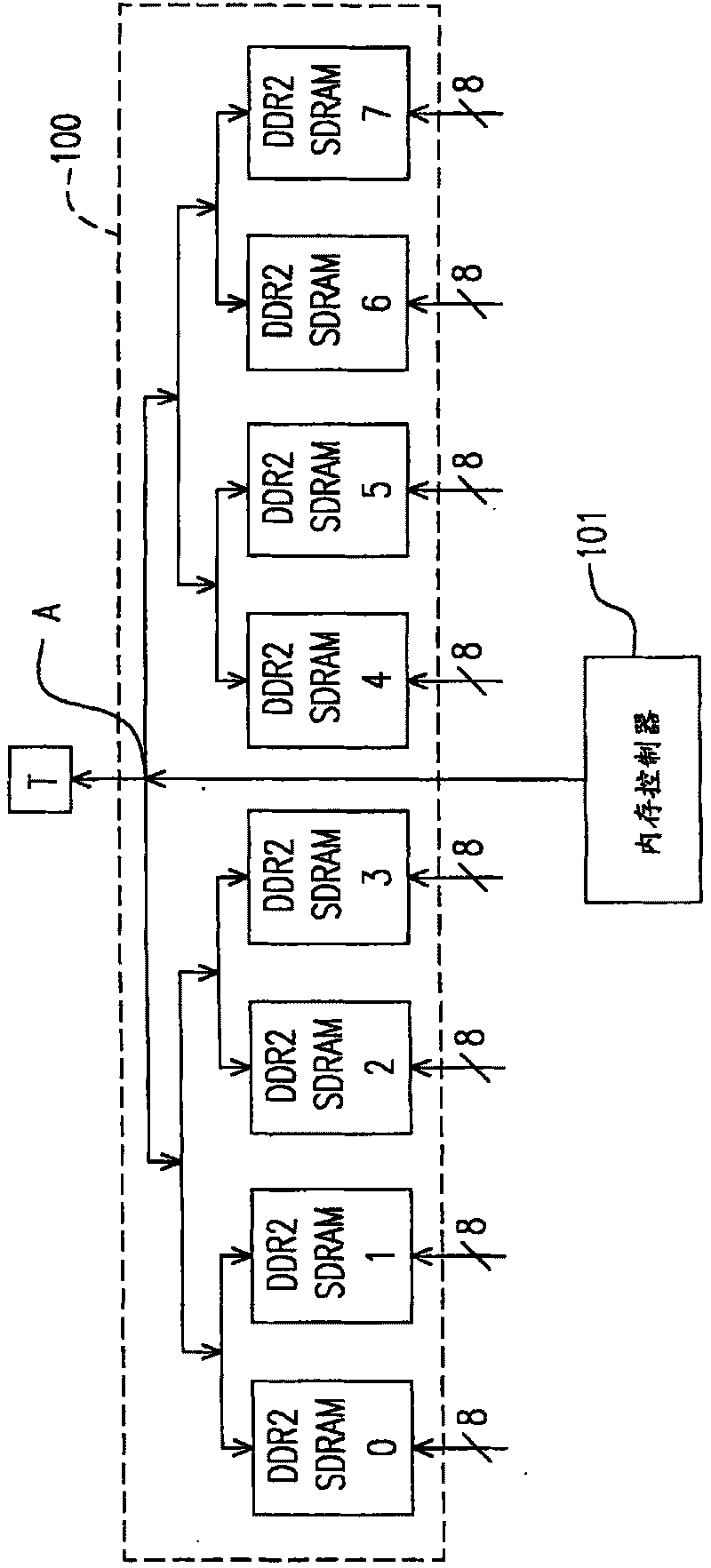

Motherboard and its internal memory apparatus

ActiveCN101320589BImprove system performanceEasy way to pull the wireDigital storageElectric digital data processingInternal memorySynchronous dynamic random-access memory

The present invention relates to a memory device, which can be directly arranged on any motherboard in the prior art which can support the third-generation dual-channel synchronous dynamic random access memory DDR3 SDRAM, so as to integrate the advantages of the fly-by bus bracket and the T-shaped branch bracket, which are prepared in the JEDEC. Therefore, the memory device can improve the systemefficiency of the table computer in unit time.

Owner:ASUSTEK COMPUTER INC

A five-dimensional dynamic stereo clutter map realization method based on ddr3-sdram

ActiveCN104535980BStorage capacity doubledEasy accessWave based measurement systemsClustered dataComputer science

The invention relates to a five-dimensional dynamic stereoscopic clutter map implementation method based on a DDR3-SDRAM. According to the five-dimensional dynamic stereoscopic clutter map implementation method, reading and writing control over the DDR3-SDRAM is achieved through an FPGA, and then a five-dimensional dynamic stereoscopic clutter map is established. The method comprises the following steps that (a) reading operation is conducted on the DDR3-SDRAM, and clutter data are read out; (b) a clutter map is updated through a recursive filter, and data conversion is conducted; (c) the updated cluster data are rewritten to the corresponding position of the DDR3-SDRAM, updating of the cluster map is completed, and a clutter map is established. Compared with a traditional cluster map implementation method, the five-dimensional dynamic stereoscopic clutter map implementation method based on the DDR3-SDRAM is characterized in that a clutter area is finely divided, and besides traditional distance division, direction division and pitching division, a PRF mode and clutters of a full-Doppler channel are also divided. Clutter data are specially processed, the storage capacity of the clutter map is doubled.

Owner:CNGC INST NO 206 OF CHINA ARMS IND GRP

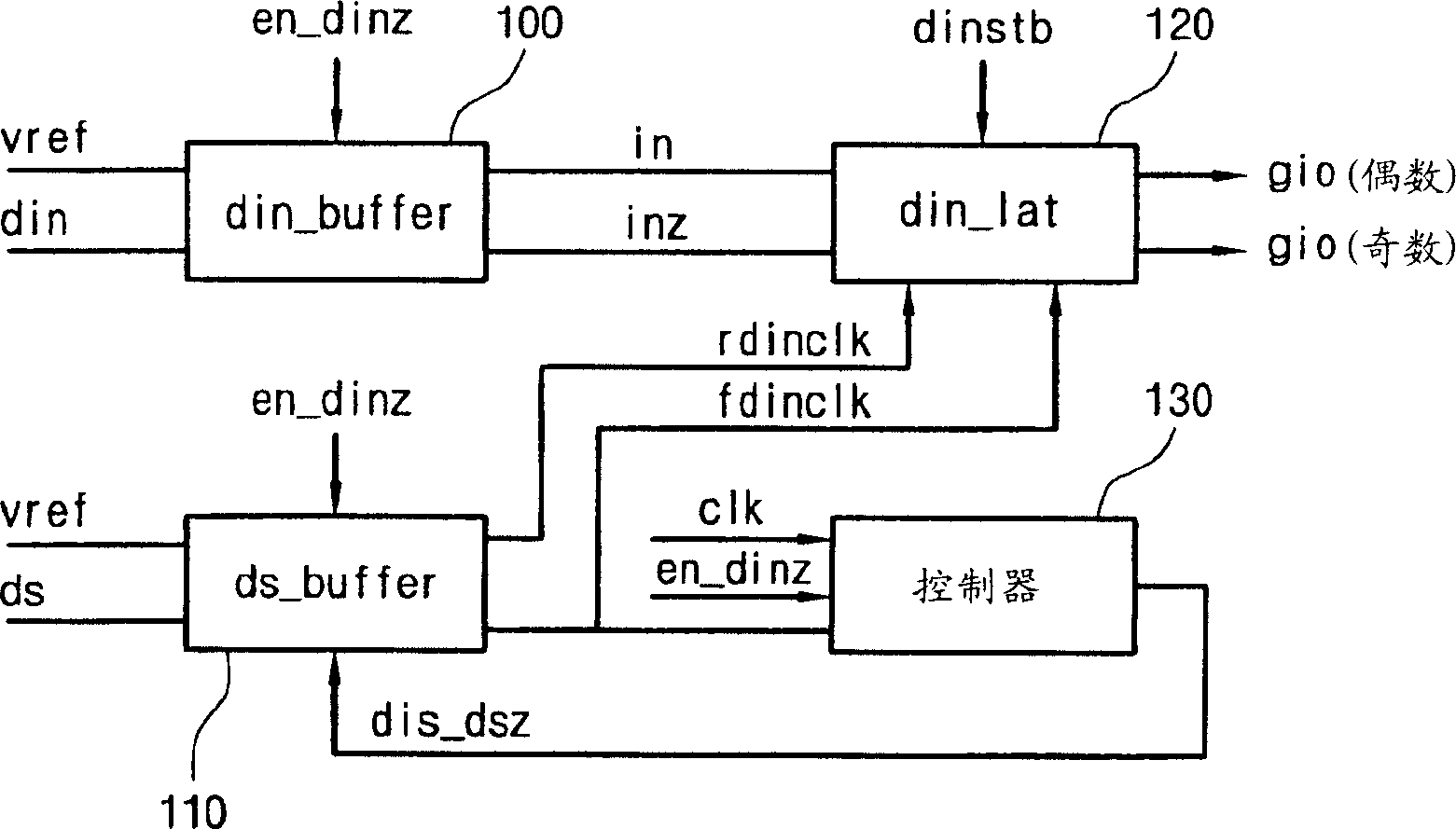

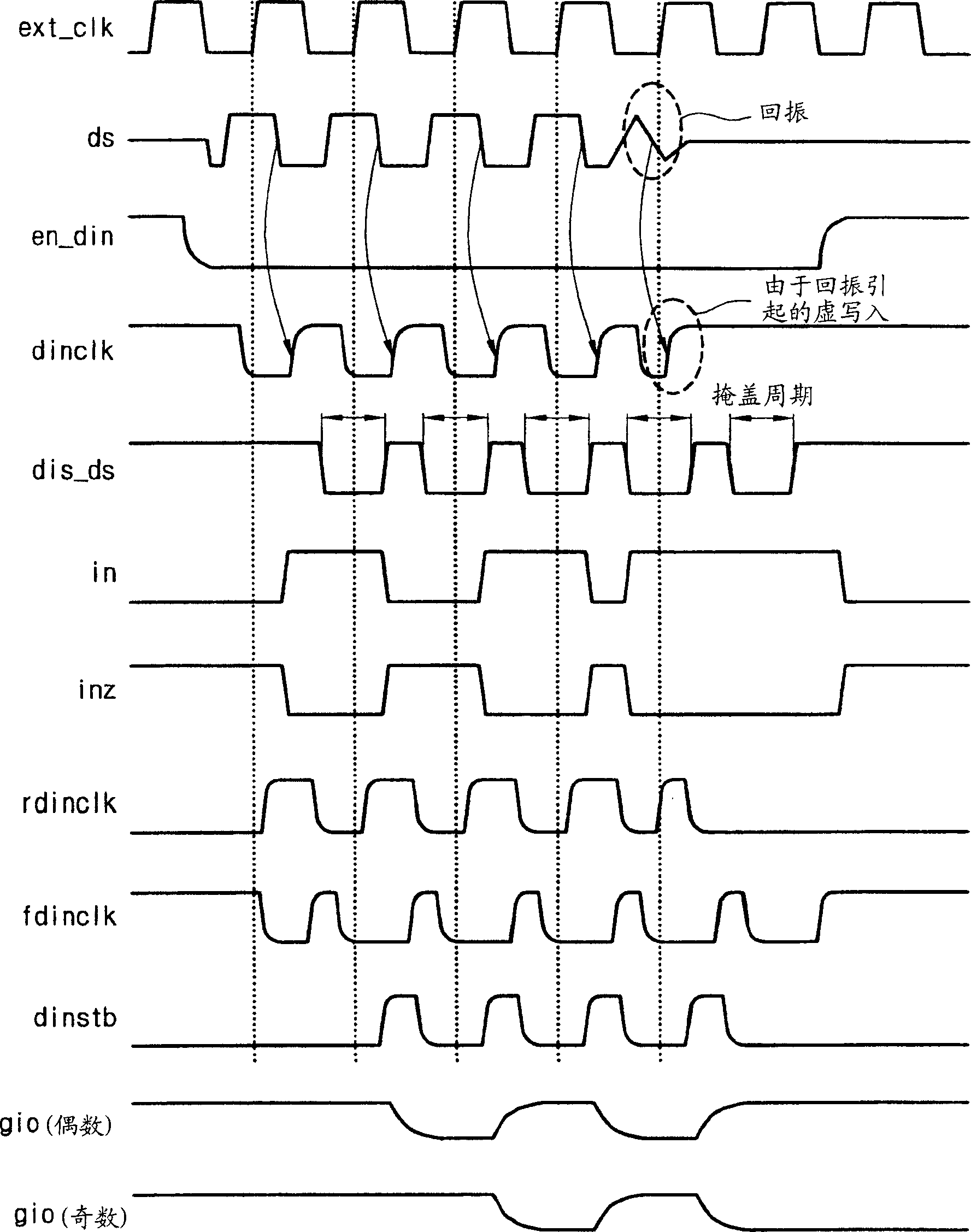

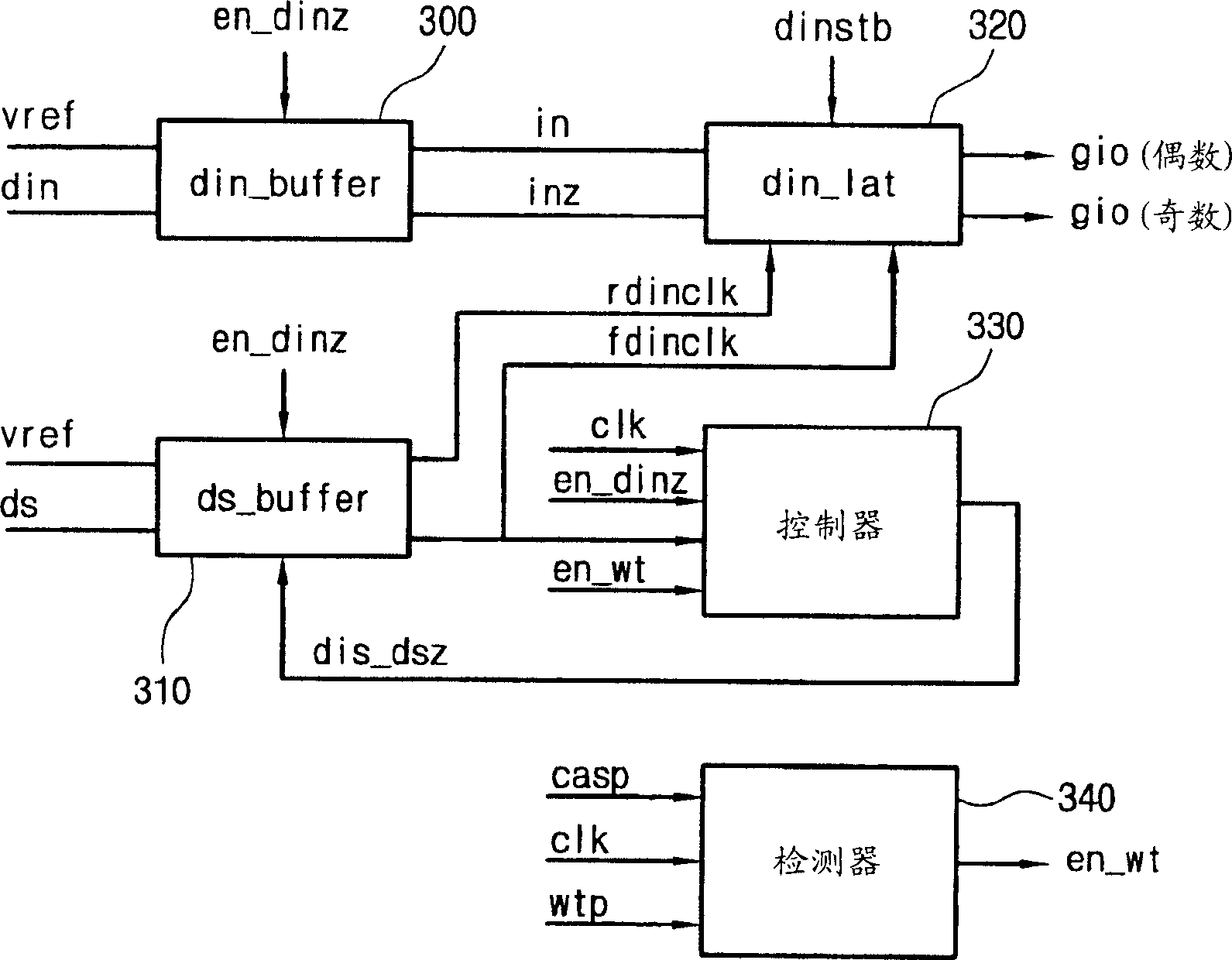

Data pass control device for masking write ringing in ddr sdram and method thereof

The present invention relates to a data pass control device for masking a ringing of a data strobe that occurs when a write operation in a DDR SDRAM is completed. The data pass control device for masking the write ringing in the DDR SDRAM can be advantageously used for masking only a section with the ringing problem during the write operation, so that any unnecessary operations during the write operation can be eliminated and a more stable write operation can be realized by eliminating a write fail.

Owner:SK HYNIX INC

An airborne wireless access point ap device

ActiveCN105338665BSimple structureStrong reliabilityWireless communicationJoint Test Action GroupRadio frequency

The invention discloses an airborne wireless access point (AP) device. The airborne wireless AP device comprises a power supply module, an AP main board, an interface board, an Ethernet airspace connector, a power supply aerospace connector and an antenna, wherein the antenna is connected with the AP main board, and the power supply module, the AP main board, the Ethernet aerospace connector and the power supply aerospace connector are respectively connected with the interface board. The AP main board comprises a processor, and an Ethernet interface unit, a discrete magnate control unit, a radio frequency unit, a DDR3 SDRAM memory, a flash memory, a JTAG interface and a serial port, which are respectively connected with the processor, and the AP main board also comprises a power supply system unit, and the power supply system unit is used for powering each device on the AP main board. The airborne wireless AP device can implement WIFI connection in a cabin and has advantages of improving the user experience. The application stability is good, and the practicability is high.

Owner:WUHAN HONGXIN TELECOMM TECH CO LTD

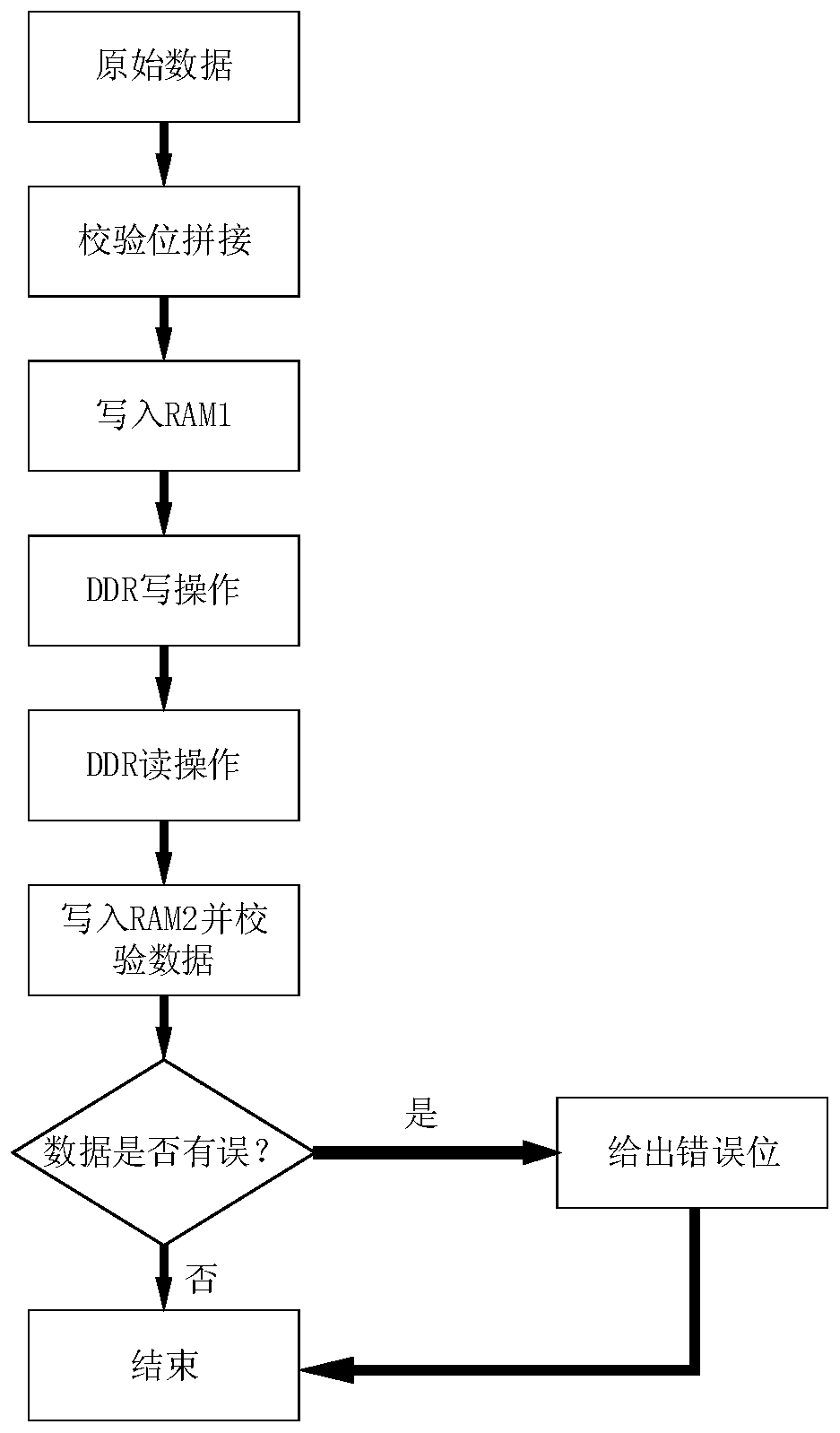

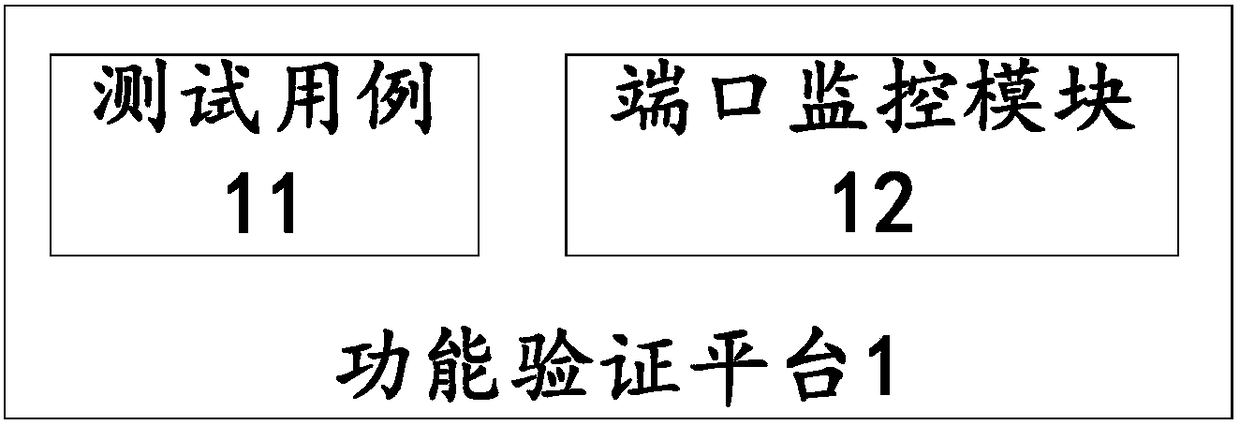

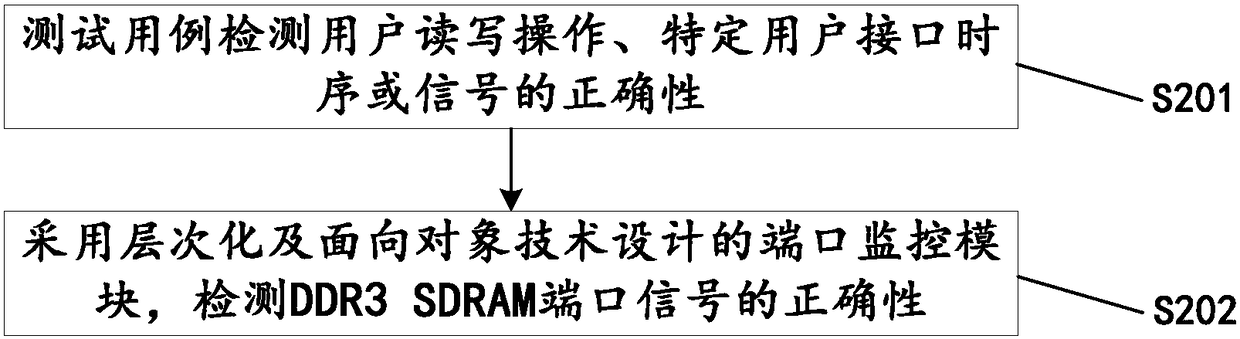

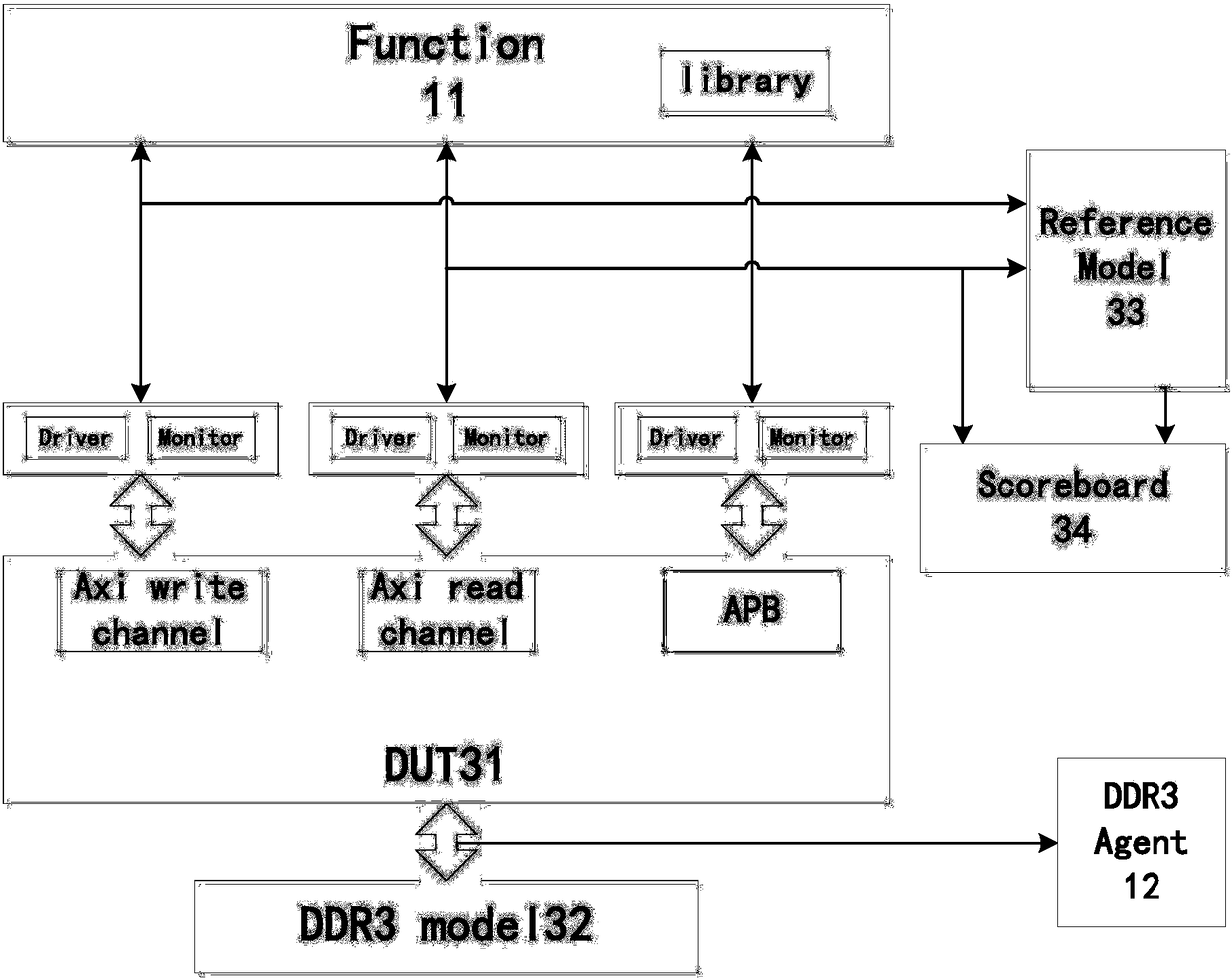

Functional verification method and platform for ddr3 SDRAM controller

ActiveCN105654993BNot easy to missEasy maintenanceStatic storageDouble data rateSynchronous dynamic random-access memory

Owner:SHENZHEN PANGO MICROSYST CO LTD

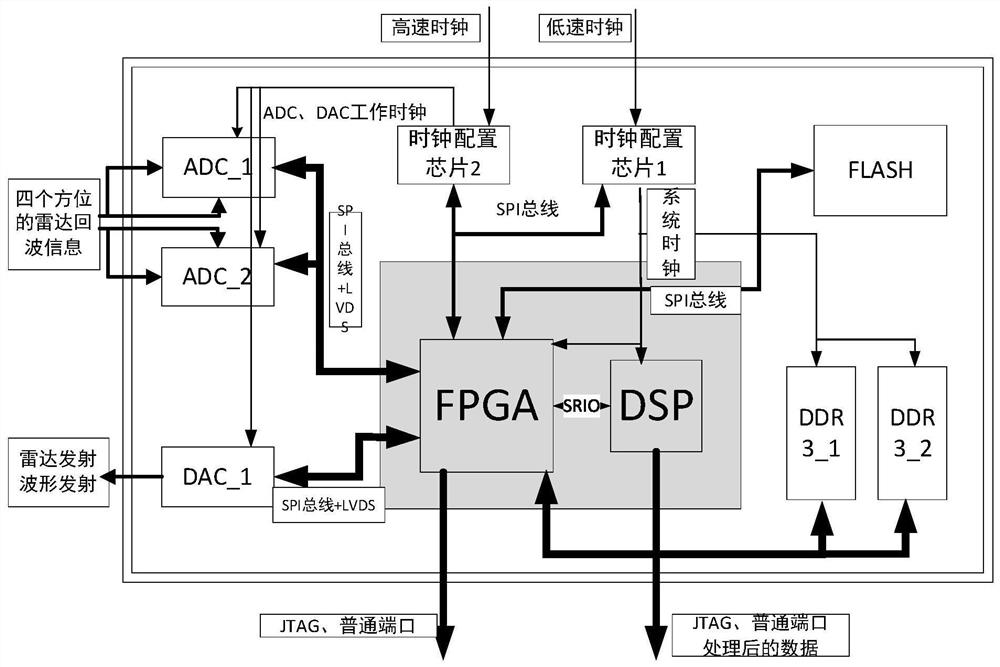

Phased array radar signal processing system-level chip based on SIP (Session Initiation Protocol) technology

PendingCN114779196AImprove stabilityHighly integratedWave based measurement systemsSession Initiation ProtocolHigh density

The invention relates to a phased array radar signal processing system-on-chip based on an SIP technology. The phased array radar signal processing system-on-chip comprises a substrate, an FPGA chip, a DSP chip, a first clock chip, a second clock chip, a DAC chip, a plurality of ADC chips, a plurality of DDR3 SDRAM chips and a FLASH EEPROM chip. The SIP technology is adopted, bare chips of all chips are reasonably placed on the high-density ceramic circuit substrate with the cavity, and all the chips are connected through lines in the substrate. While basic functions of the phased array radar are completed, minimization and low power consumption processing is carried out on the system, and the stability of the system is improved.

Owner:XIDIAN UNIV

Embedded guide star processing system

ActiveCN109991900BBig amount of dataEasy to implementProgramme controlTelevision system detailsComputer hardwareEngineering

The embedded guide star processing system relates to an embedded guide star processing system for space targets, which solves the problem that the existing image acquisition and processing system is difficult to cope with the huge amount of real-time data, and the guide star is difficult, so that the main field of view cannot be aligned with the space for a long time. Target observation and other issues, including image acquisition module and guide star calculation module, the guide star calculation module adopts the guide star processing system with FPGA and DSP heterogeneous processor architecture, and the image acquisition module collects the sCMOS camera video signal in real time And stored in DDR3 SDRAM, and then the image data in DDR3 SDRAM is sent to the guide star calculation module; it provides powerful image processing and calculation analysis capabilities, can identify space targets, obtain their precise center of mass positions, and calculate the error The vector is converted into the actual amount of the telescope missing the target, which is fed back to the pointing control system of the astronomical telescope. The embedded guide star processing system improves the stability and accuracy of the guide star, achieving long-term observation of the target.

Owner:中国科学院国家天文台长春人造卫星观测站

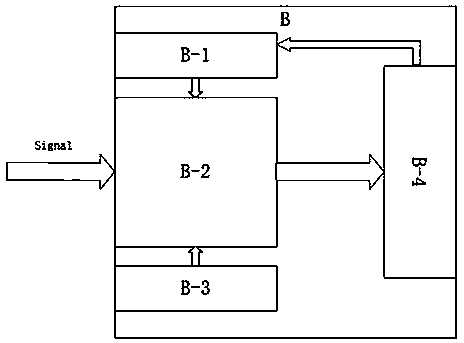

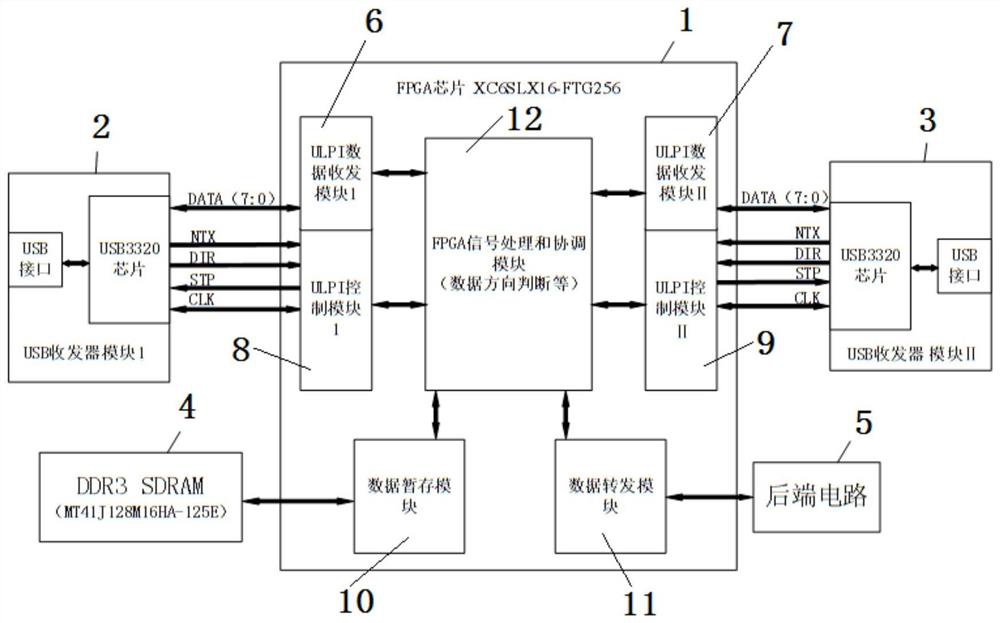

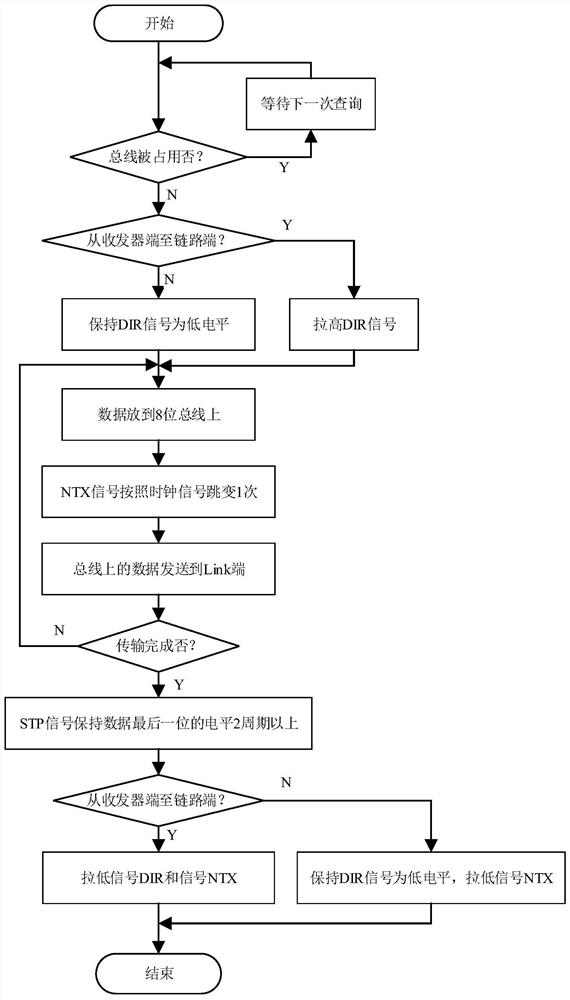

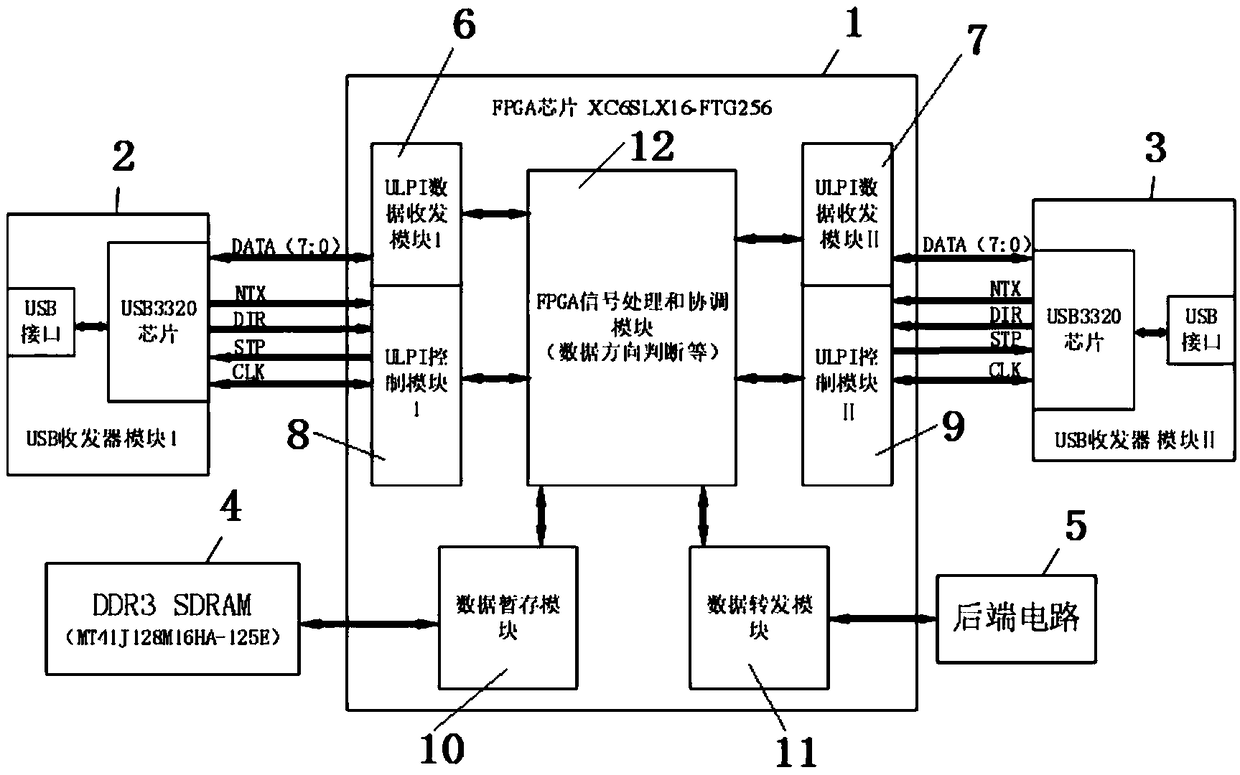

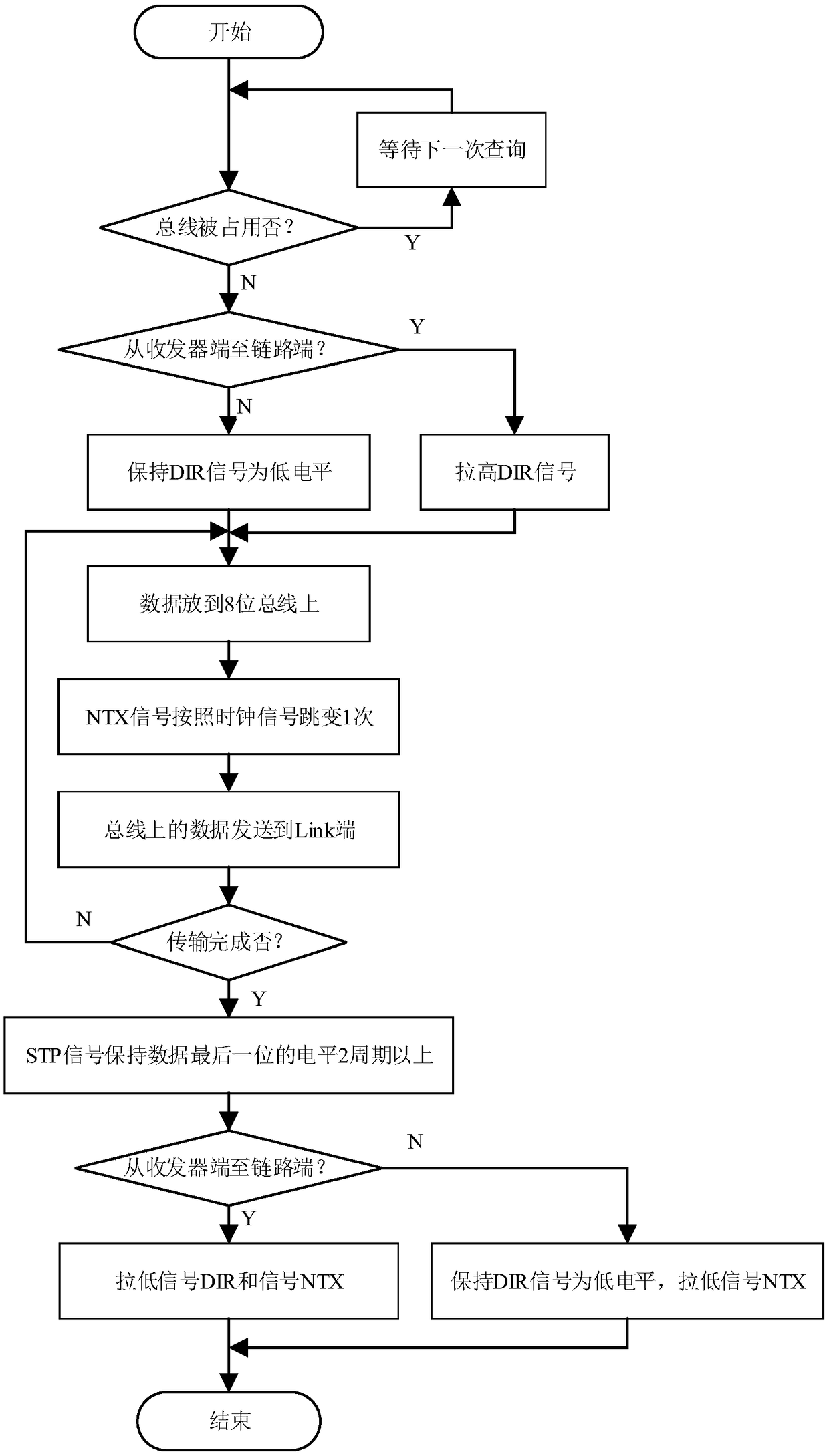

A FPGA-based usb data real-time monitoring system and method

ActiveCN109359082BRealize acquisitionLow costMultiple digital computer combinationsArchitecture with single central processing unitTransceiverStore and forward

The invention relates to an FPGA-based USB data real-time monitoring system and method, belonging to the technical field of electronics and communication. The present invention includes FPGA chip, USB transceiver module I, USB transceiver module II, DDR3 SDRAM memory; FPGA chip includes: ULPI data transceiver module I, ULPI data transceiver module II, ULPI control module I, ULPI control module II, data temporary memory module and FPGA signal processing and coordination module. In the present invention, the FPGA is used for relay, and the data on the USB bus can be unpacked, stored, and forwarded after being connected to the USB transmission line without a PC, so as to realize real-time monitoring and collection of non-invasive USB data from the data level. .

Owner:KUNMING UNIV OF SCI & TECH

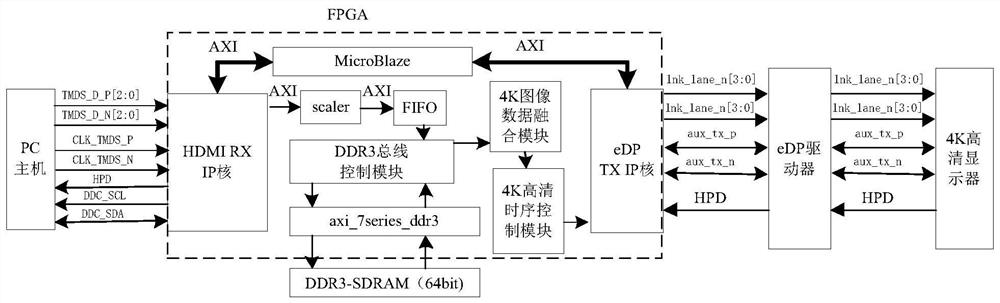

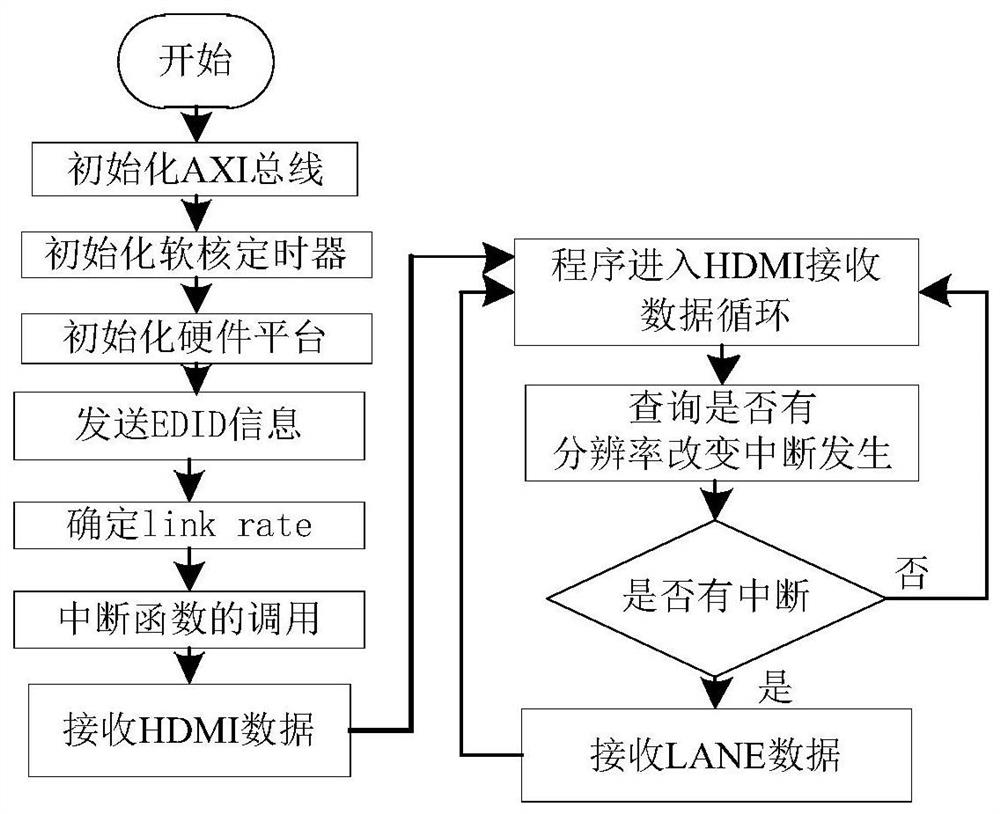

HDM-to-eDP interface conversion device and interface conversion method based on an FPGA

ActiveCN112714264AGuaranteed real-timeProcessing speedTelevision system detailsColor television detailsDisplay deviceEngineering

The invention discloses an HDM-to-eDP interface conversion device and interface conversion method based on an FPGA. An FPGA module in the device comprises an HDMI RX module, a MicroBlaze soft core module, a scaler scaling module, an FIFO module, a DDR3 bus control module, a DDR3 IP core module, a 4K image data fusion module, a 4K high-definition time sequence control module and an eDP TX module. The HDMI RX module receives a video image from the PC host; the HDMI RX module converts the HDMI video image into an RGB format; the scaler scaling module amplifies the resolution of the video image in the RGB format to 4K, and the resolution is stored by the FIFO module; when the number of the stored data of the FIFO module reaches a preset pixel point number, the currently stored pixel point is stored into the DDR3 SDRAM; the 4K image data fusion module reads data from the DDR3 SDRAM for preprocessing, then the data is converted into an eDP signal by the 4K high-definition sequential control module, and the eDP signal is sent to the high-definition display by the eDP TX hardware interface. According to the invention, the display speed of the 4K high-definition liquid crystal display is high.

Owner:CHANGSHA XIANGJI HAIDUN TECH CO LTD

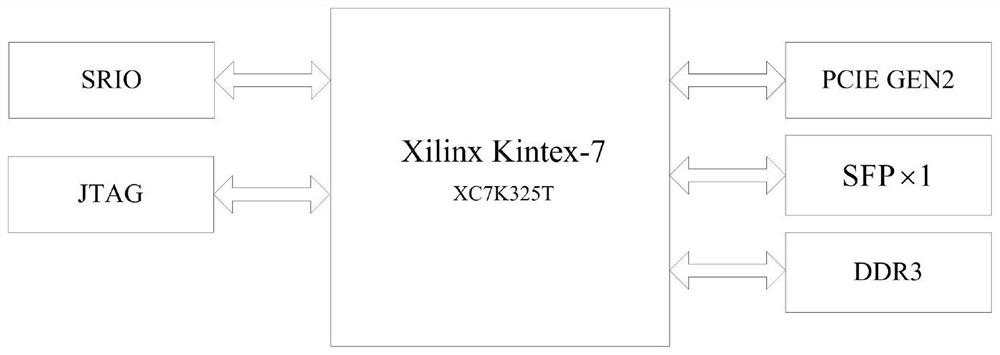

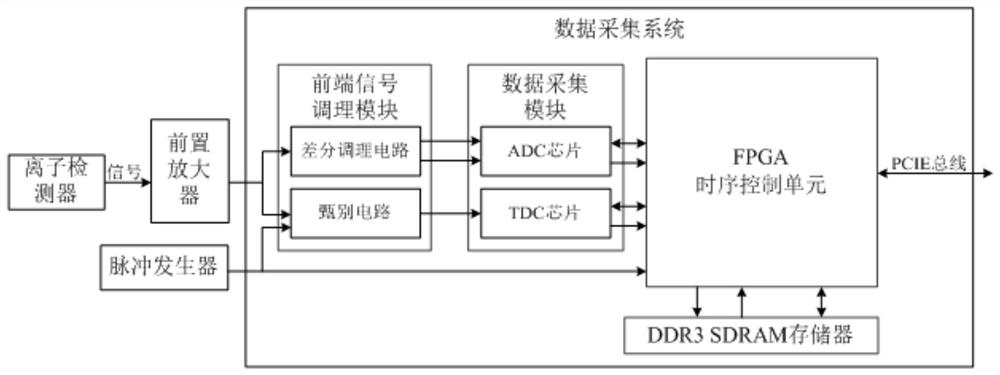

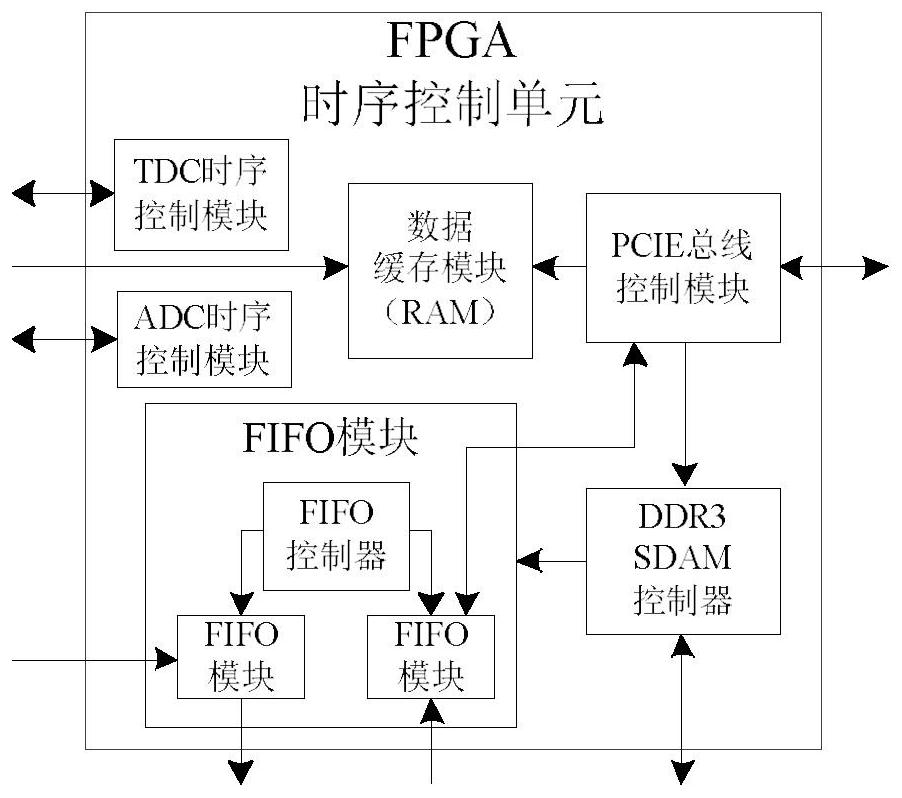

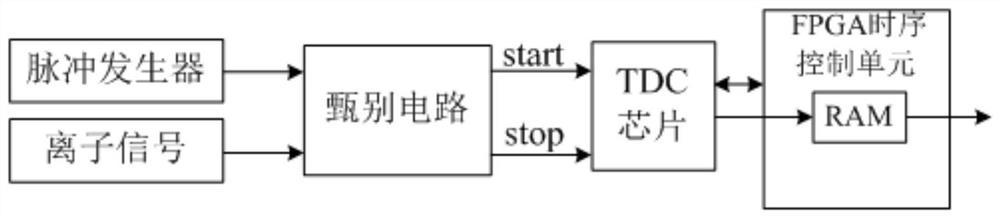

A Data Acquisition System Based on High Speed Analog-to-Digital Conversion and Time-to-Digital Conversion

ActiveCN108664425BAnalogue-digital convertersElectric digital data processingData acquisitionControl cell

The present invention is a data acquisition system based on high-speed analog-to-digital conversion and time-to-digital conversion technology, belonging to the field of electronic technology, including a front-end signal conditioning module, which includes a discrimination circuit and a differential conditioning circuit; including a TDC chip and an ADC chip respectively The data acquisition module that receives the signal processed by the discrimination circuit and the differential conditioning circuit; the FPGA timing control unit connected to the TDC chip and the ADC chip respectively, and the FPGA timing control unit reads the data of the TDC chip and the ADC chip, and communicates with the DDR3 SDRAM memory and PCIE Connected to the bus, connected to the computer through the PCIE bus; used to input the trigger signal to the discrimination circuit when the ion enters the time-of-flight mass analyzer, and input the trigger signal to the pulse generator of the FPGA timing control unit, and the FPGA timing control unit receives After the trigger signal is received, a control sequence is generated to enable the ADC chip and the TDC chip to collect at the same time. The system can obtain the data collected by the ADC and TDC at the same time, and take advantage of the advantages of ADC collection and TDC collection.

Owner:JILIN UNIV

A USB data real-time monitoring system and method based on FPGA

ActiveCN109359082ARealize acquisitionLow costMultiple digital computer combinationsArchitecture with single central processing unitTransceiverNon invasive

The invention relates to a USB data real-time monitoring system and method based on FPGA, and belongs to the technical field of electronics and communication. The invention comprises an FPGA chip, a USB transceiver module I, a USB transceiver module II and a DDR3 SDRAM memory. The FPGA chip includes a ULPI data transceiver module I, a ULPI data transceiver module II, a ULPI control module I, a ULPI control module II, a data temporary storage module and an FPGA signal processing and coordination module; As that FPGA of the invention is used as a relay, the data on the USB bus can be unpacked, stored and forwarded after the USB transmission line is accessed without a PC, so that the non-invasive USB data real-time monitor and collection from the data level can be realized.

Owner:KUNMING UNIV OF SCI & TECH