Patents

Literature

31 results about "DDR2 SDRAM" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Double Data Rate 2 Synchronous Dynamic Random-Access Memory, officially abbreviated as DDR2 SDRAM, is a double data rate synchronous dynamic random-access memory interface. It superseded the original DDR SDRAM specification, and is superseded by DDR3 SDRAM (launched in 2007). DDR2 DIMMs are neither forward compatible with DDR3 nor backward compatible with DDR.

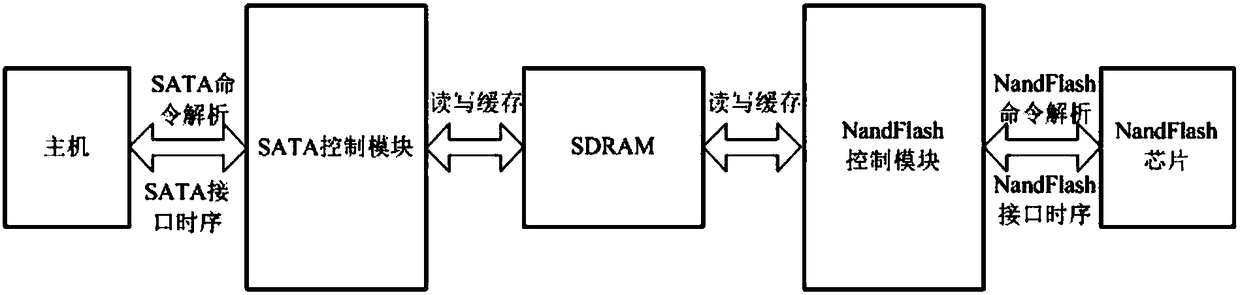

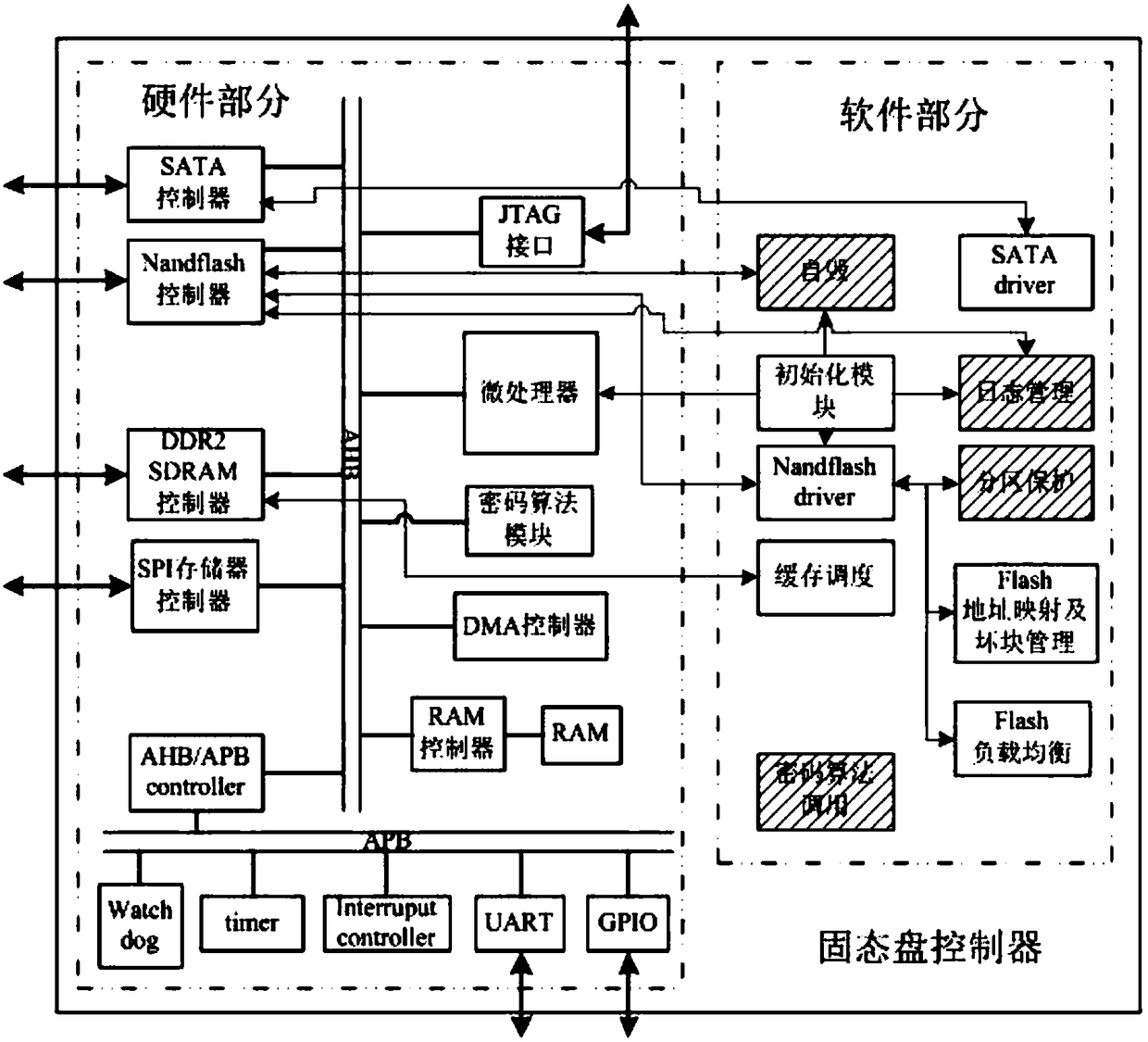

Storage array control method and device based on multiple channels of NandFlash memory

PendingCN108121672AIncrease capacityImprove data transfer rateEnergy efficient computingElectric digital data processingComputer moduleJoint Test Action Group

The invention provides a storage array control method and device based on multiple channels of a NandFlash memory. The device includes an embedded-type microprocessor, and the embedded-type microprocessor is connected with each external module through an in-chip high-speed intercommunication bus; the external modules include the SATA controller, the Nandflash controller, the DDR2 SDRAM controller,the JTAG debugging interface, the AHB / APB bridge, the code algorithm module, the DMA controller, the on-chip RAM controller and the SPI flash controller. The AHB / APB bridge connects the in-chip high-speed intercommunication bus with an in-chip low-power-consumption intercommunication bus, the in-chip low-power-consumption intercommunication bus is connected with an interrupt controller, a timer,a watchdog, a serial port and a GPIO, and therefore a complete on-chip system is constructed. The control method is designed on the basis of an assembly line framework and a fully-connected parallel framework, parallel running of the channels and an assembly line operation are achieved, the access bandwidth of a Flash interface is fully utilized, and the system performance is further improved.

Owner:HONGQIN (BEIJING) TECHNOLOGY CO LTD

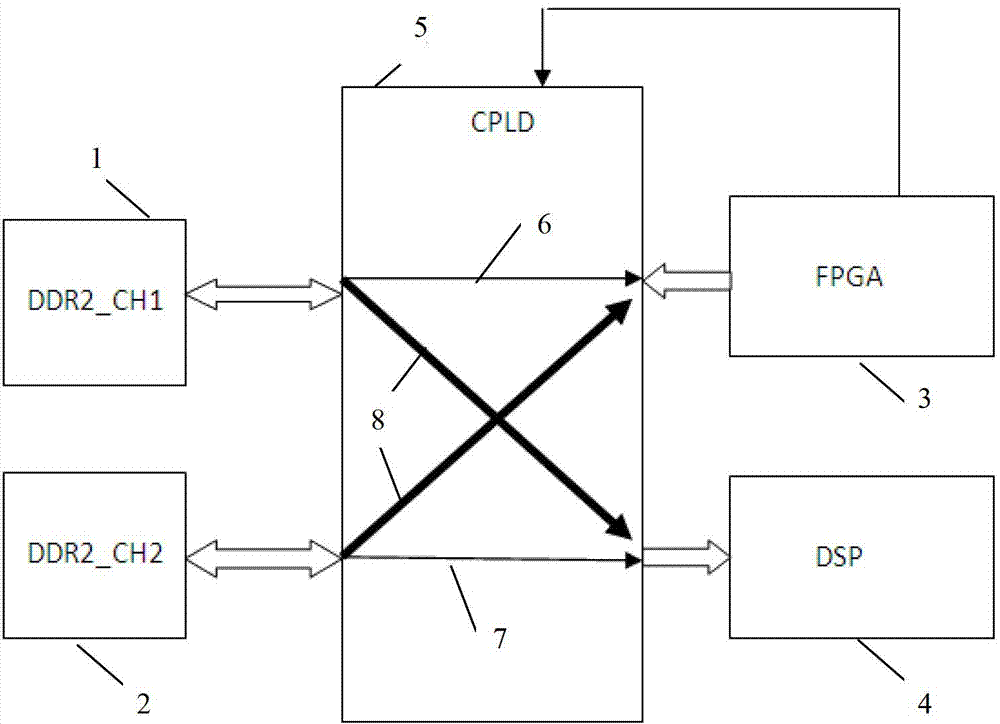

Field programmable gate array (FPGA) and digital signal processor (DSP) data transmission system based on Ping Pong mechanism

InactiveCN102968394AImplement alternate storageAchieving processing powerData conversionDigital signal processingDouble data rate

The invention provides a field programmable gate array (FPGA) and digital signal processor (DSP) data transmission system based on a Ping Pong mechanism. The FPGA and DSP data transmission system based on the Ping Pong mechanism comprises a two-channel selector switch, an FPGA, a DSP and two memories. The on-off state of the two-channel selector switch is controlled by the FPGA so as to realize the alternate operation of a first read / write channel and a second read / write channel, and therefore, alternate storage and read of data is realized; the first read / write channel is characterized in that cache current data of the FPGA are written into a first memory, and meanwhile, the data written in at the previous moment are read from a second memory by the DSP; the second read / write channel is characterized in that the cache current data of the FPGA are written into the second memory, and meanwhile, the data written in at the previous moment are read from the first memory by the DSP. The continuous data are alternately stored and read in turn between the two memories [double data rate 2 synchronous dynamic random access memory] (DDR2 SDRAM) through a Ping Pong way, and therefore, the waiting time is saved, and the data transmission efficiency is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

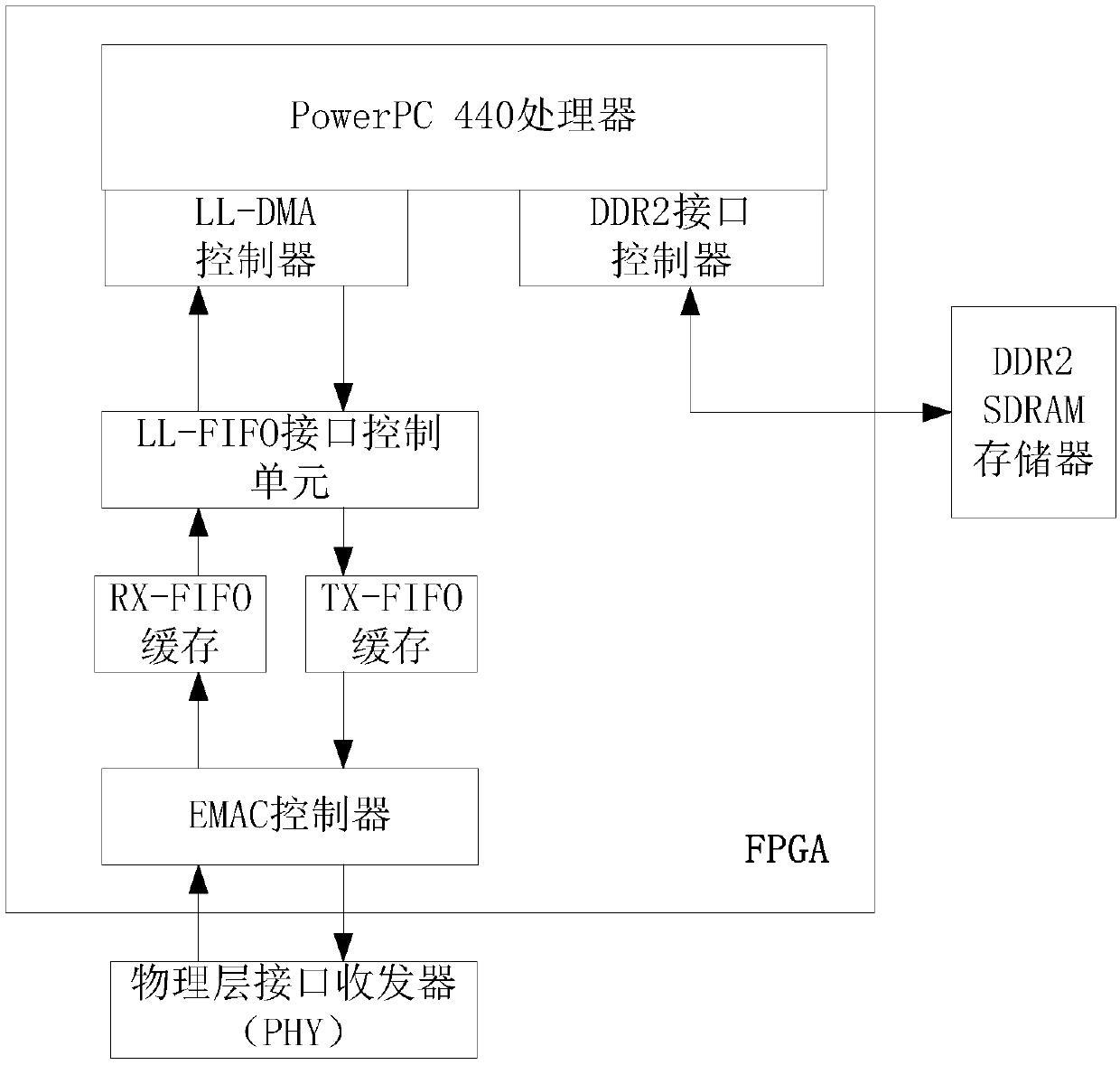

Gigabit Ethernet DMA data transmission design device based on FPGA

InactiveCN109634881AIncrease transfer rateReduce readback offload timeElectric digital data processingTransceiverNetwork link

The invention provides a gigabit Ethernet DMA data transmission design device based on FPGA. The device comprises the following steps: after an Ethernet medium access controller receives data from a physical layer interface transceiver, writing the data into a receiving FIFO (First In First Out) cache, sending an interrupt request to a processor by the receiving FIFO cache, and sending an LL-DMA by the processor; DMA controller generates descriptor instructions, LL-DMA controller reading RX-FIFO cached data, data is written into the DDR2 SDRAM memory through the DDR2 interface controller. According to the method, the processing delay caused by the fact that a CPU participates in data migration in a traditional mode is reduced; According to the invention, the transmission rate of the Ethernet link is improved, so that in the transmission process of the gigabit Ethernet network, the utilization efficiency of the network link reaches 80%, the read-back unloading time of the data recordingequipment is greatly reduced, and the work efficiency of task data analysis and information judgment by the troop external field is improved.

Owner:LUOYANG INST OF ELECTRO OPTICAL EQUIP OF AVIC

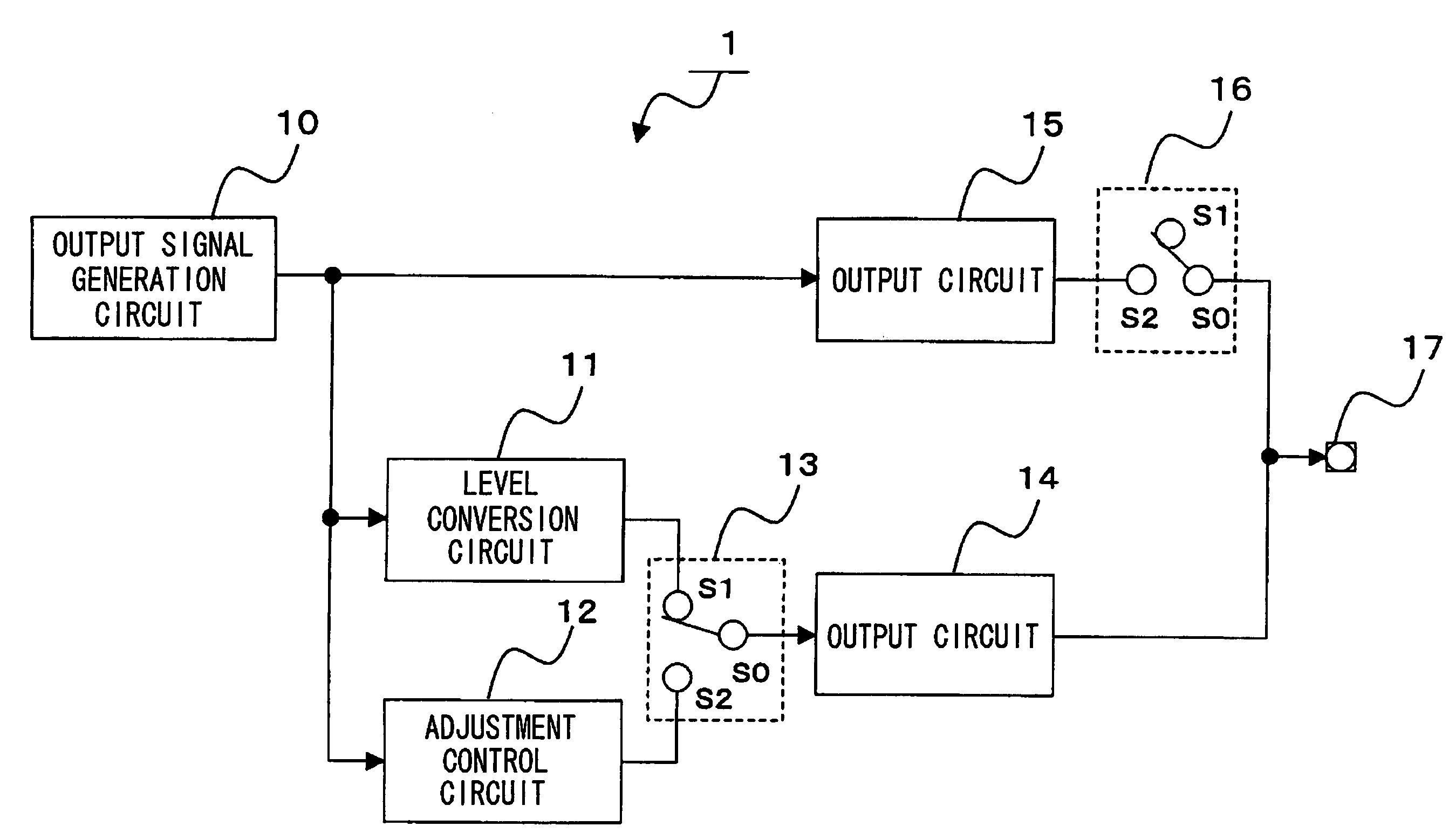

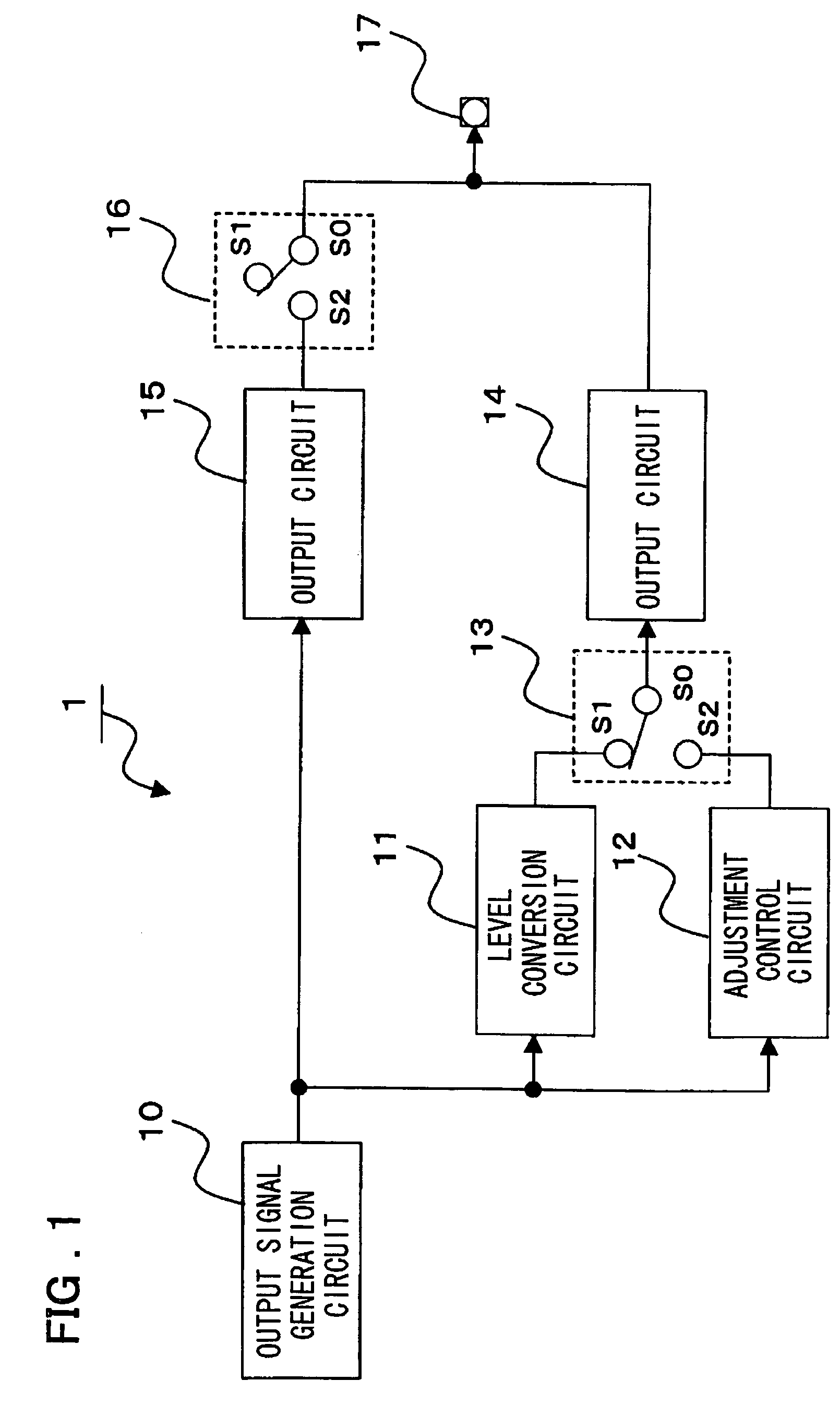

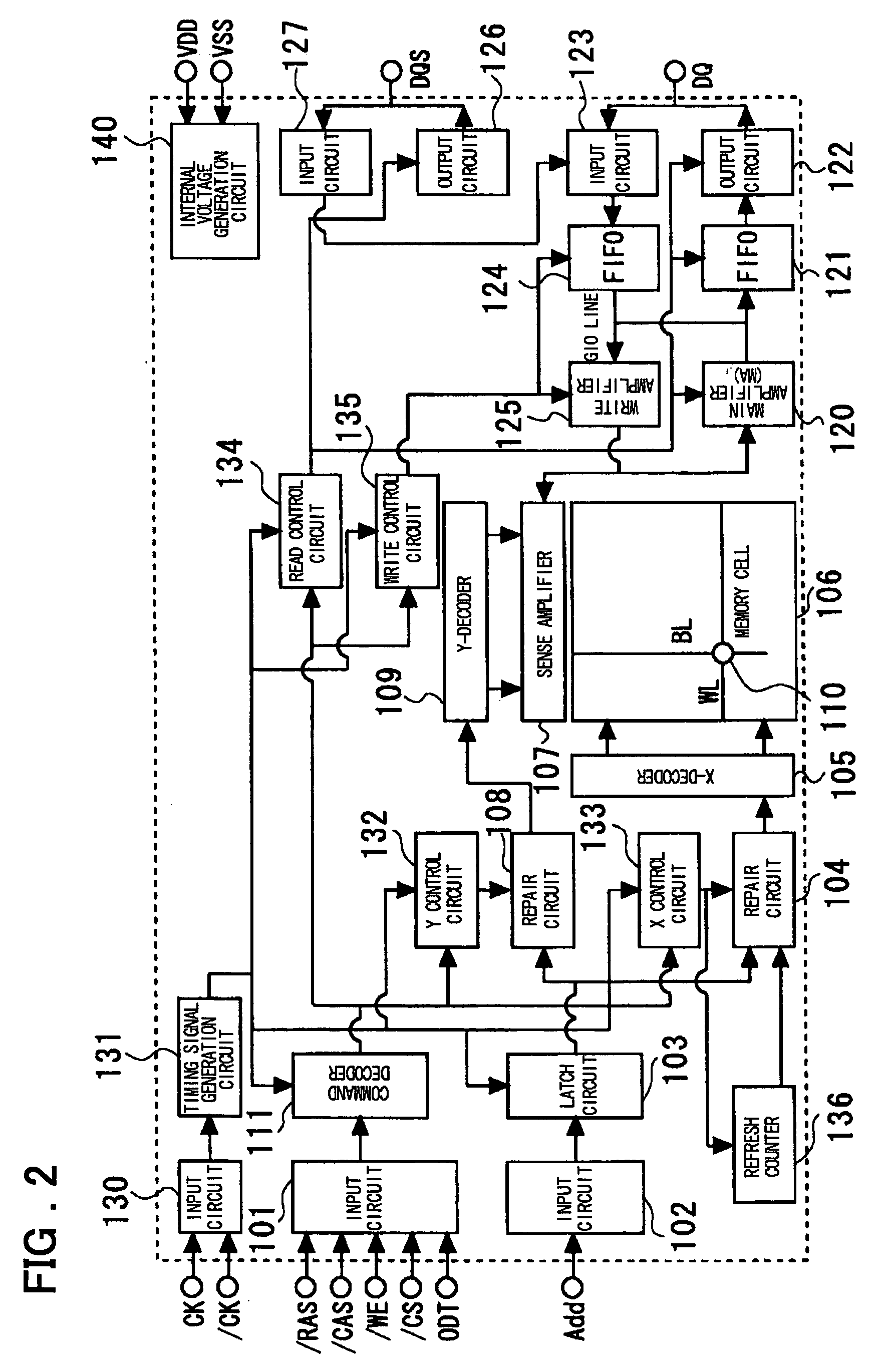

Semiconductor device

A high-density DDR-1 / DDR-2 compatible SDRAM chip with a reduced output circuit area is provided. When the SDRAM is a DDR1 SDRAM, an output signal output from an output circuit (14) is output to an output terminal (17) as a main output signal. When the SDRAM is a DDR2 SDRAM, an output signal output from an output circuit (15) is output to the output terminal (17) as the main output signal and, at the same time, the output signal output from the output circuit (14) is output as a sub-output signal to perform operation for adjusting the slew rate or the amount of output current of the main output signal or for adjusting the impedance of the output terminal as viewed from an external point.

Owner:LONGITUDE SEMICON S A R L

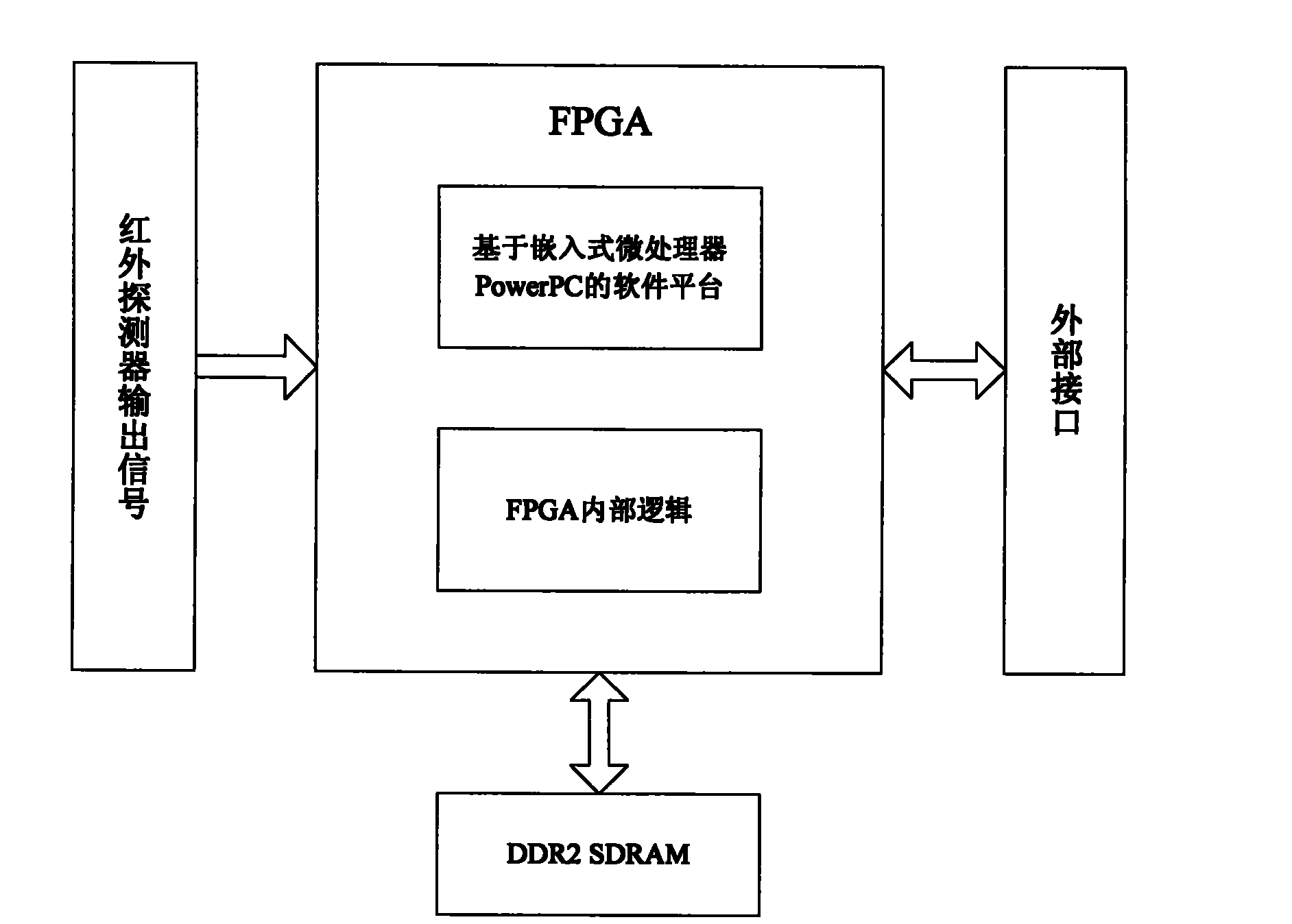

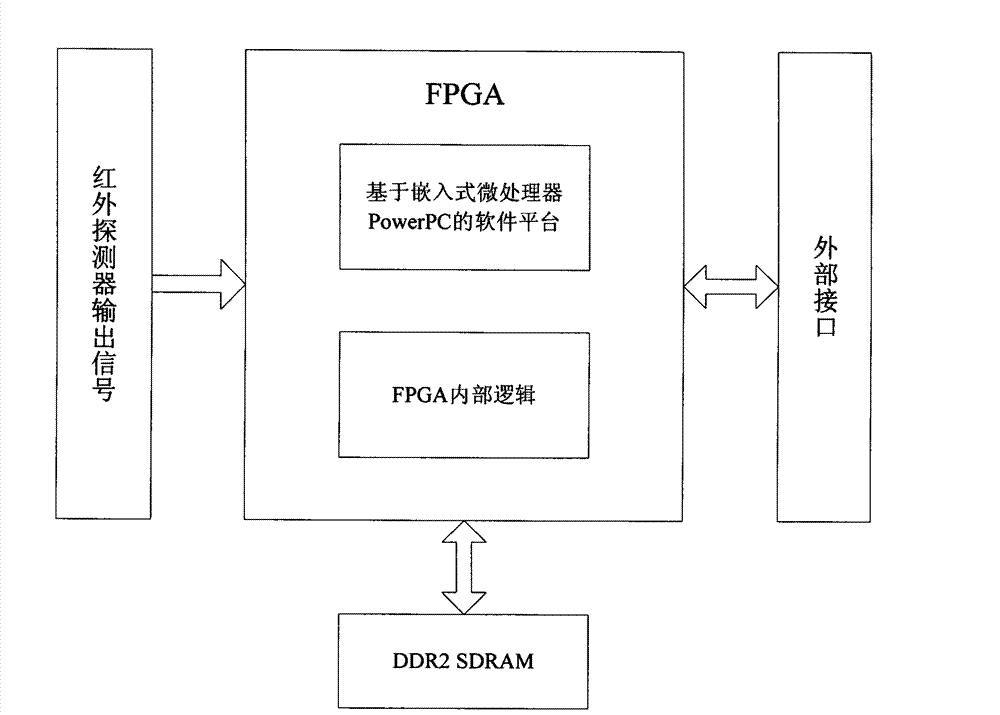

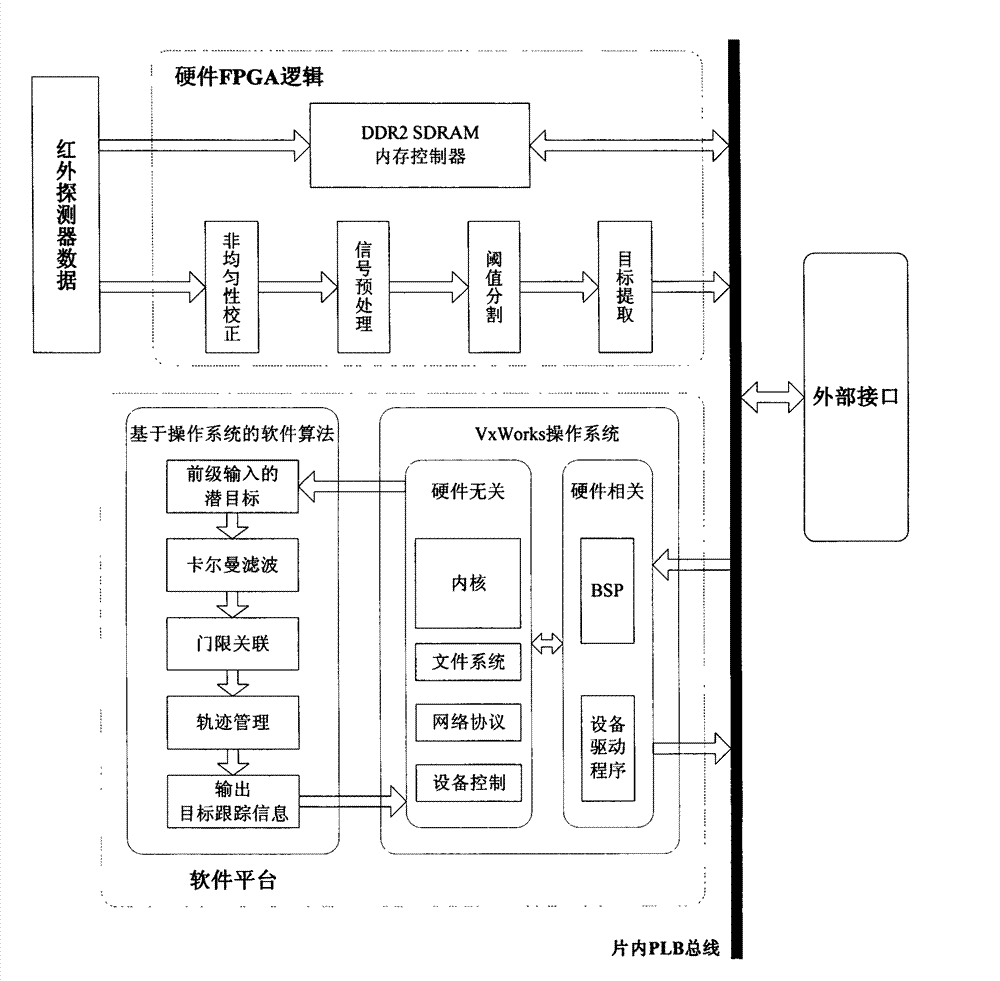

Embedded infrared real-time signal processing system

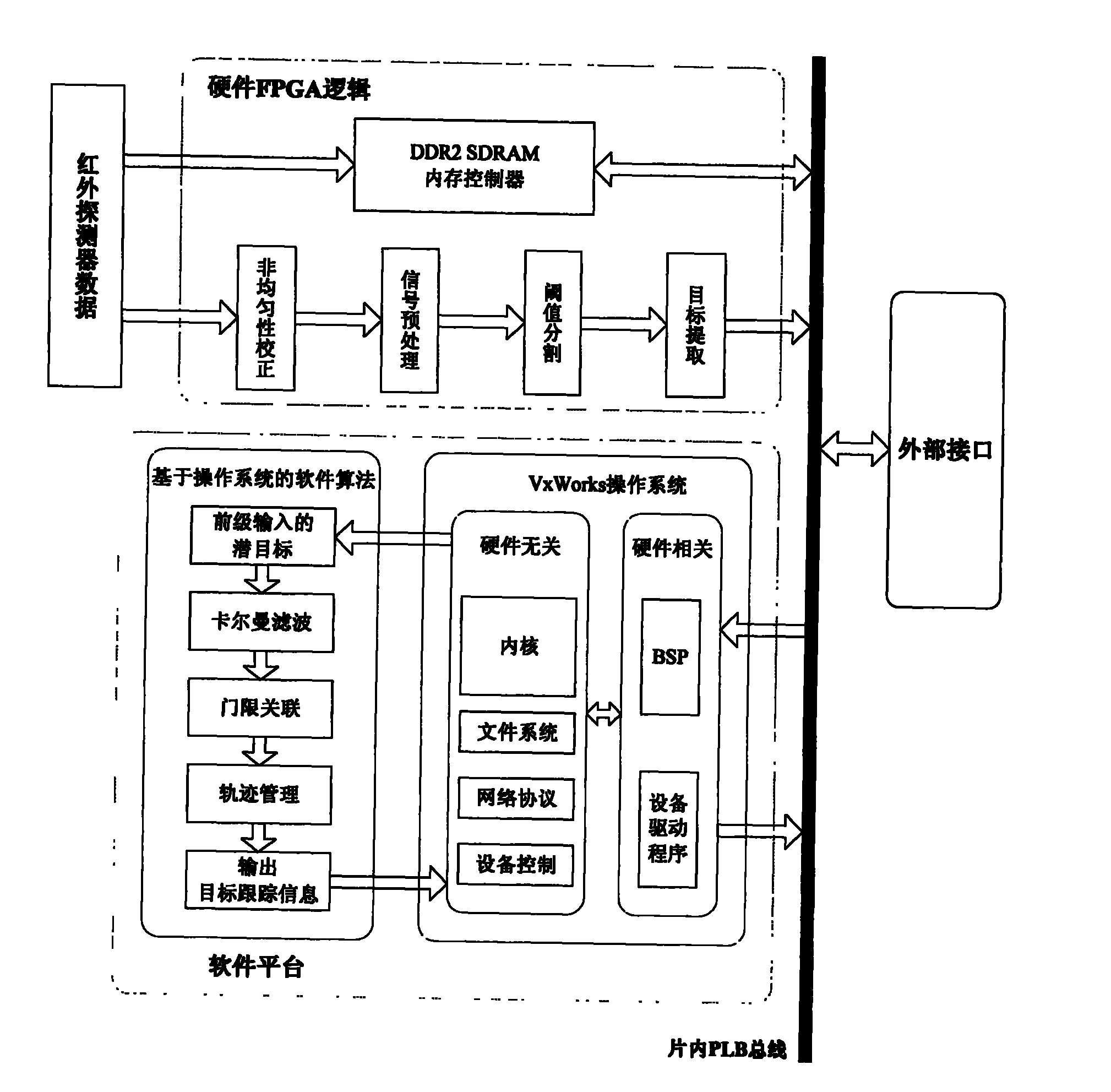

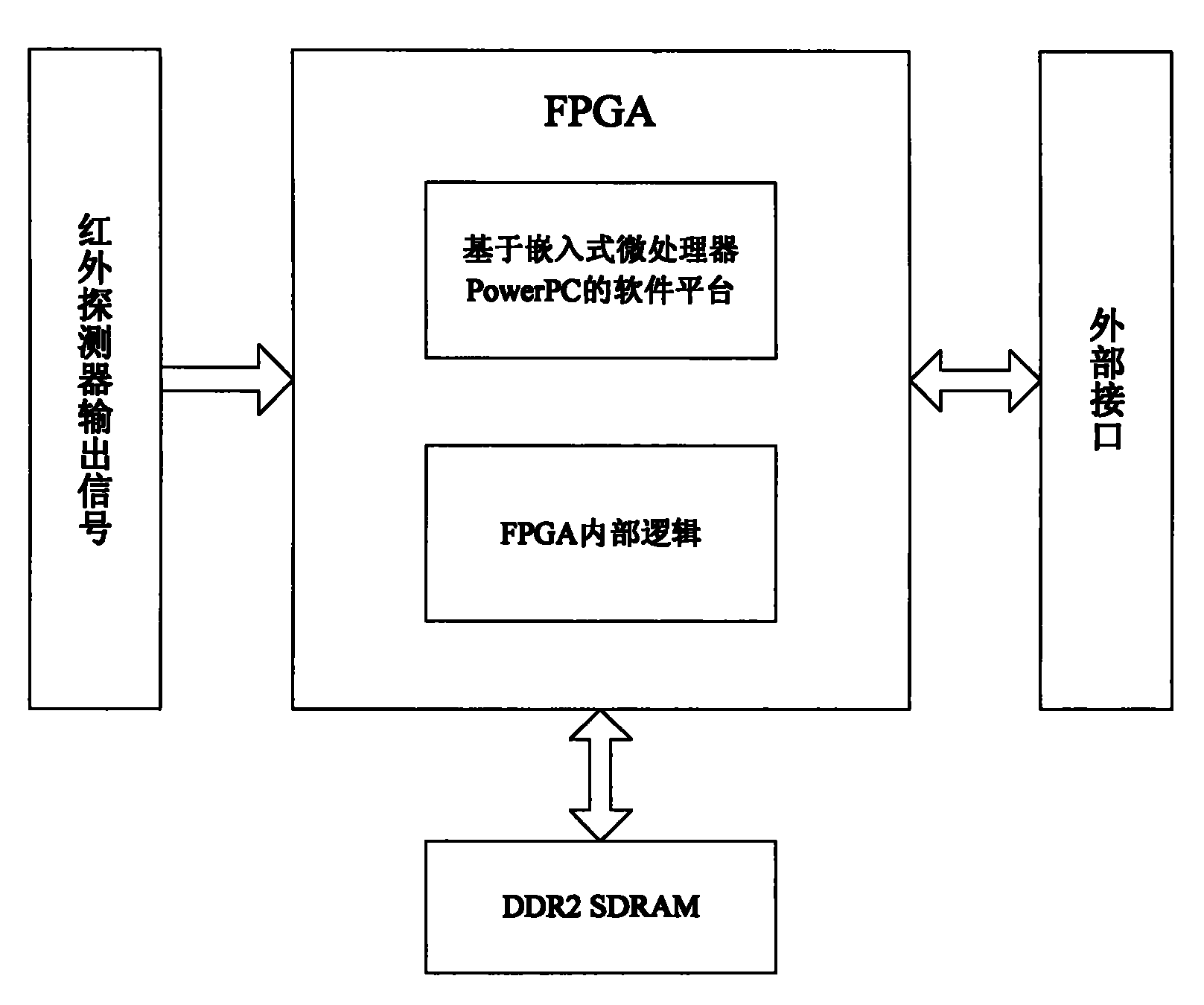

InactiveCN102156588AFlexible configurationImprove portabilityInput/output processes for data processingHardware structureDouble data rate

The invention discloses an embedded infrared real-time signal processing system, which is mainly used for an infrared detection system. The system mainly comprises an embedded signal processing board card, wherein an FPGA (Field Programmable Gate Array) with an embedded Power PC (Personal Computer) microprocessor is used as a core controller and is externally connected with a large-capacity DDR2 SDRAM (Double Data Rate 2 Synchronous Dynamic Random Access Memory) and embedded peripheral equipment. An embedded real-time operating system Vx Works based software platform is established on the Power PC microprocessor; and embedded infrared real-time signal processing can be realized by rationally selecting software and hardware of an infrared signal processing algorithm. The system has the main advantages that: a design scheme of the embedded system is adopted; a hardware structure of the embedded Power PC microprocessor in the FPGA and the embedded real-time operating system Vx Works based software platform are used; the entire infrared signal processing system is integrated on one board card; and the entire system is provided with various external interfaces, has high real-time property and a small size and is convenient to carry.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

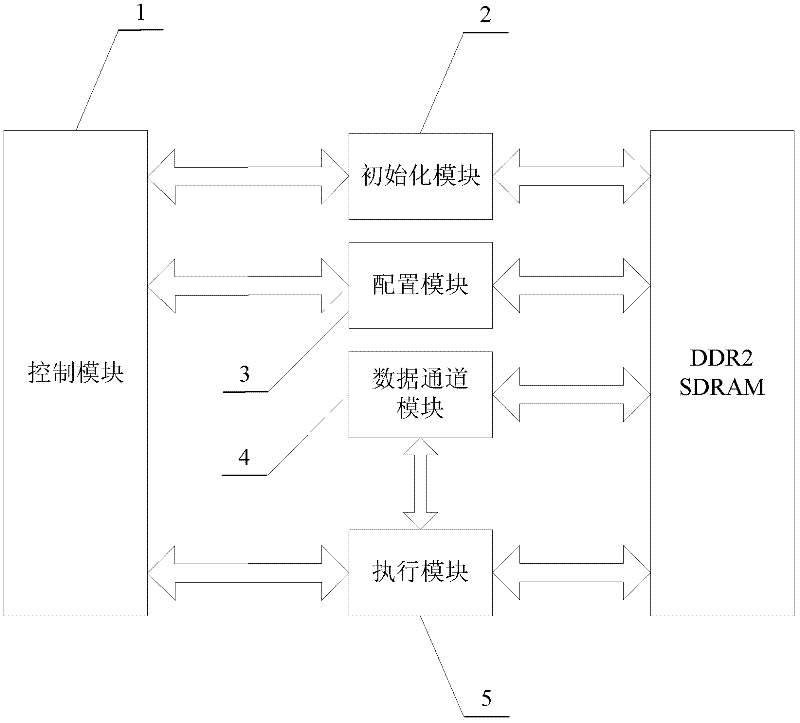

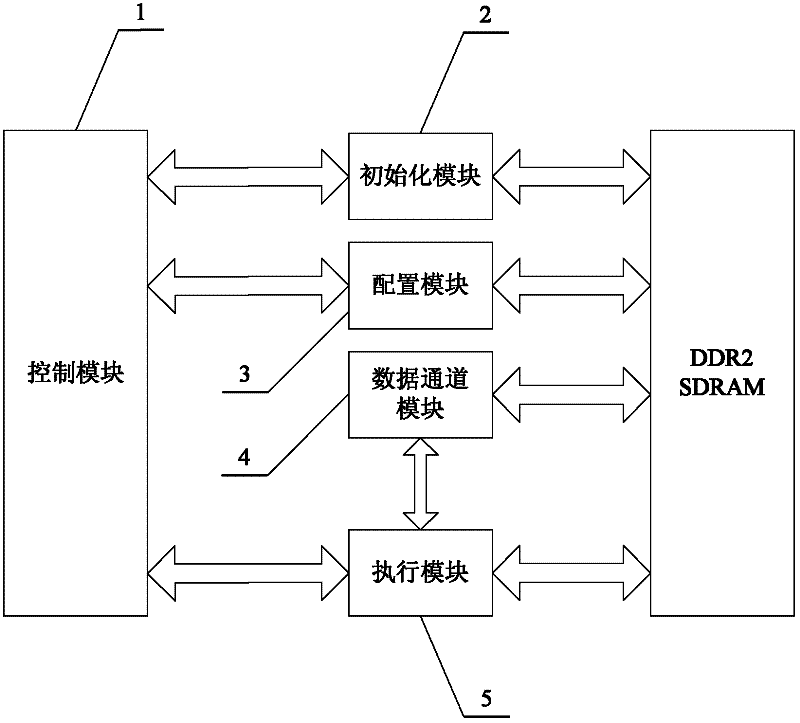

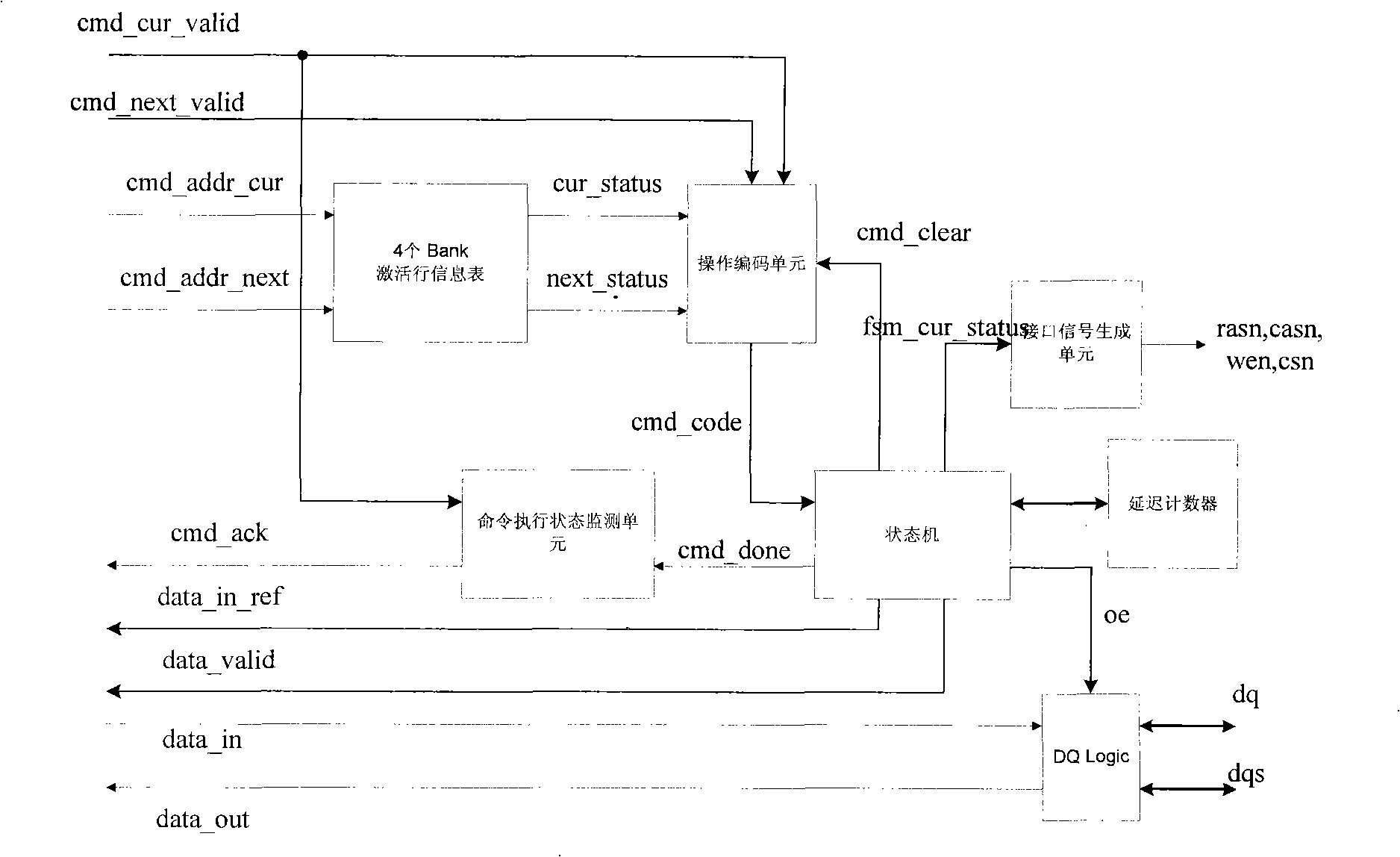

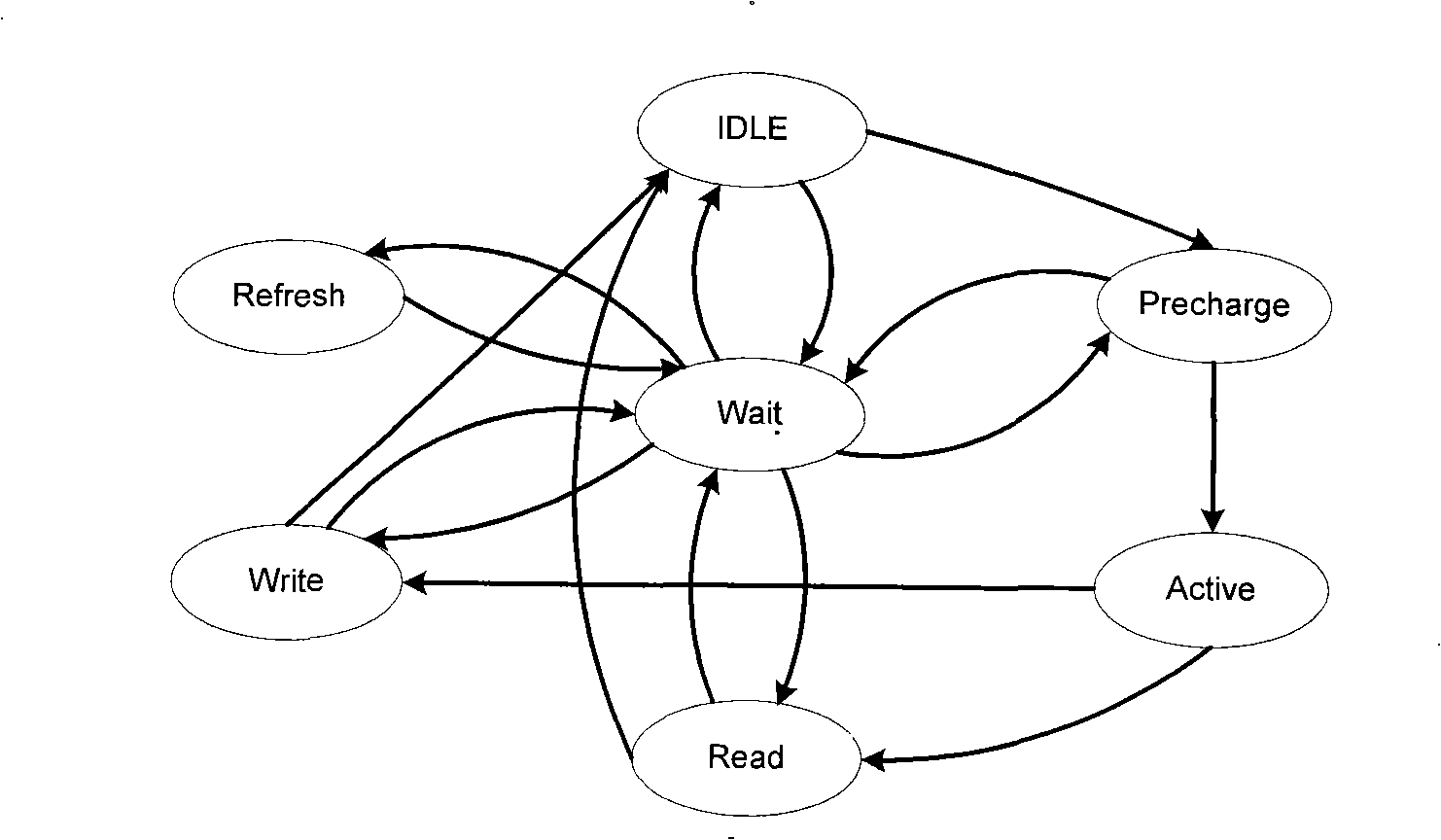

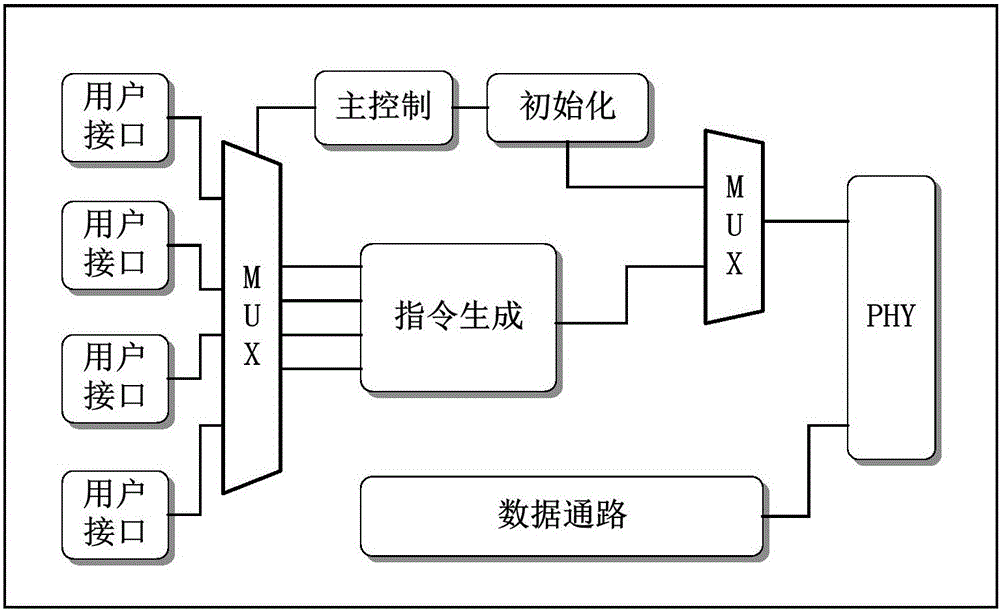

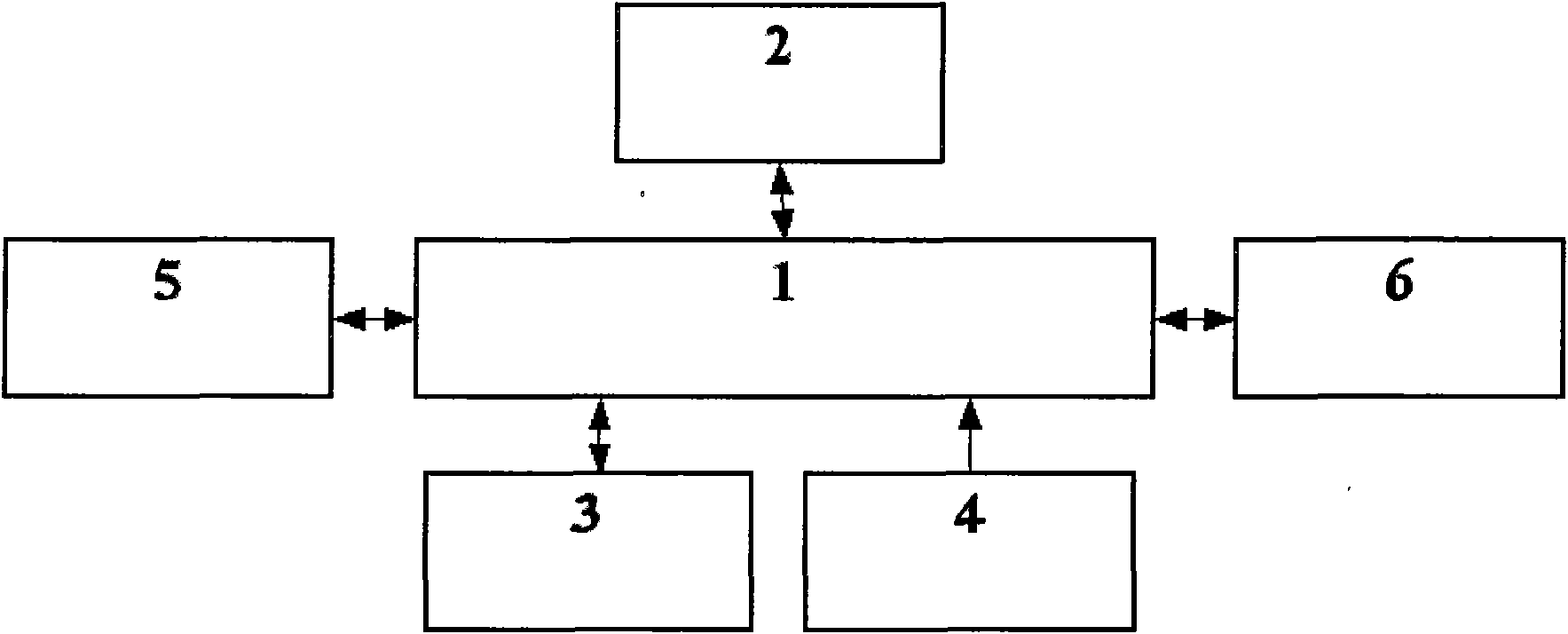

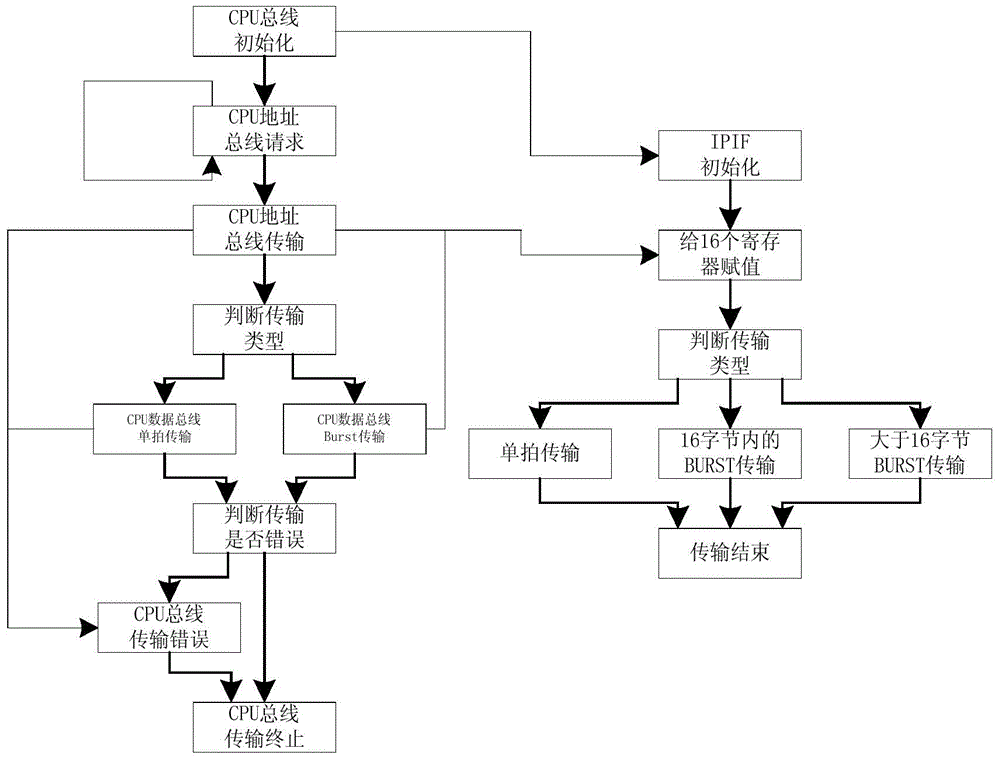

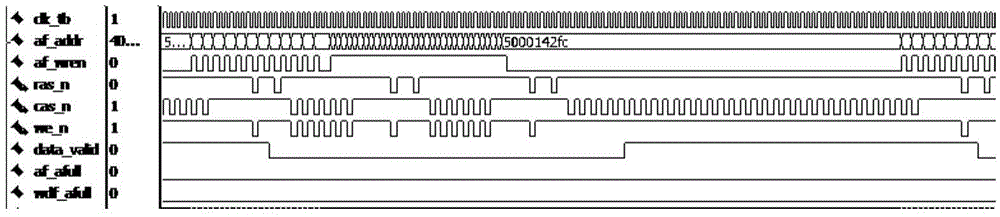

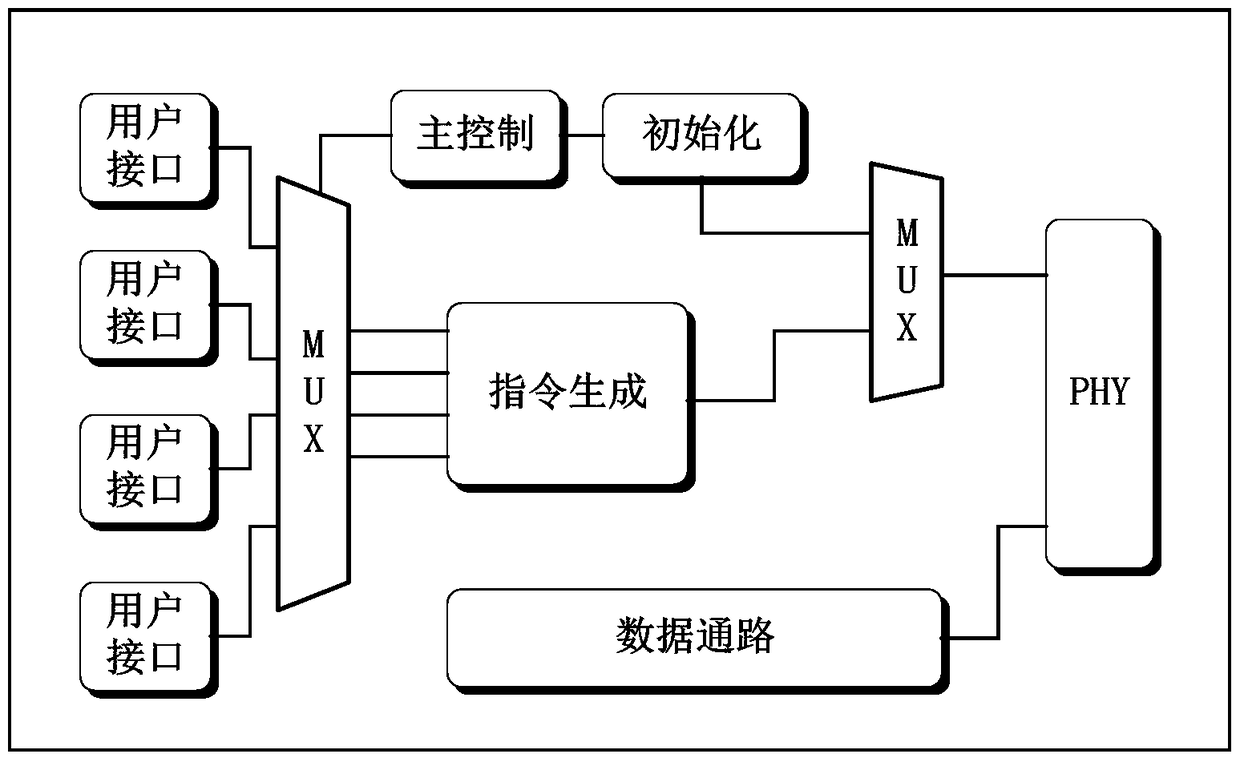

DDR (Double Data Rate) 2 SDRAM (Synchronous Dynamic Random Access Memory) controller

The invention provides a DDR (Double Data Rate) 2 SDRAM (Synchronous Dynamic Random Access Memory) controller. The controller comprises a control module, an initialization module, a configuration module, a data channel module and an execution module, wherein the control module is used for sending a control signal, receiving a feedback of the control signal, sending a sequence instruction, determining the conversion of operation states and providing a state indication signal for a system; the initialization module is used for initializing the DDR2 SDRAM controller and a DDR2 SDRAM and setting a register; the configuration module is used for configuring, controlling and indicating states of the DDR2 SDRAM controller and the DDR2 SDRAM; the data channel module is used for modulating and demodulating reading-writing data and providing data for the DDR2 SDRAM and a host computer port; and the execution module is used for receiving the sequence instruction and decoding an address carried in the sequence instruction into a sector address, a row address and a column address, judging the type of the current operation according to an instruction signal and selecting a corresponding channel to access. The DDR2 SDRAM controller hides a complex sequential operation and can be matched with various DDR2 SDRAM controllers.

Owner:上海世纪鼎利教育科技有限公司

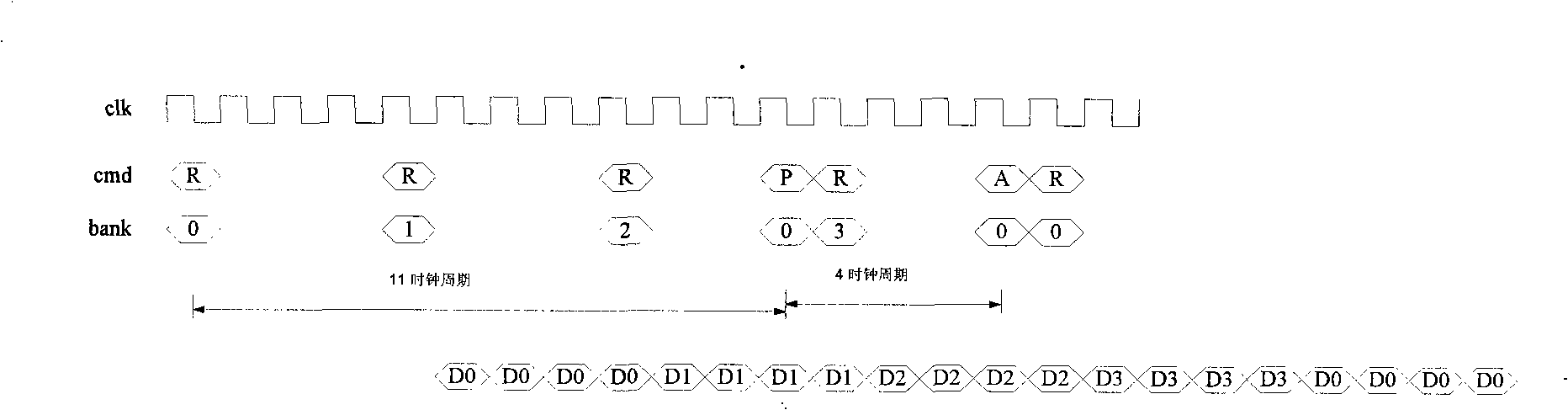

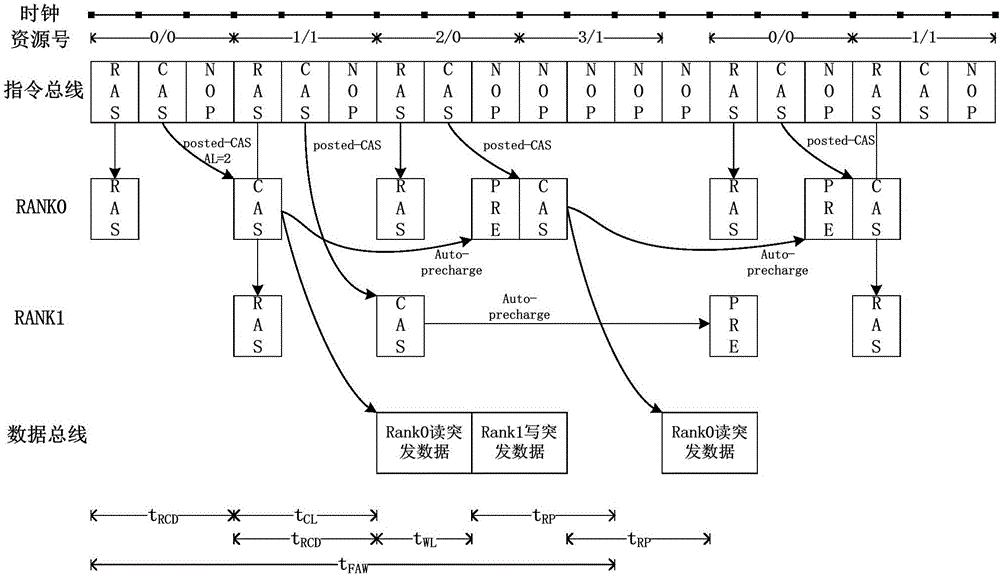

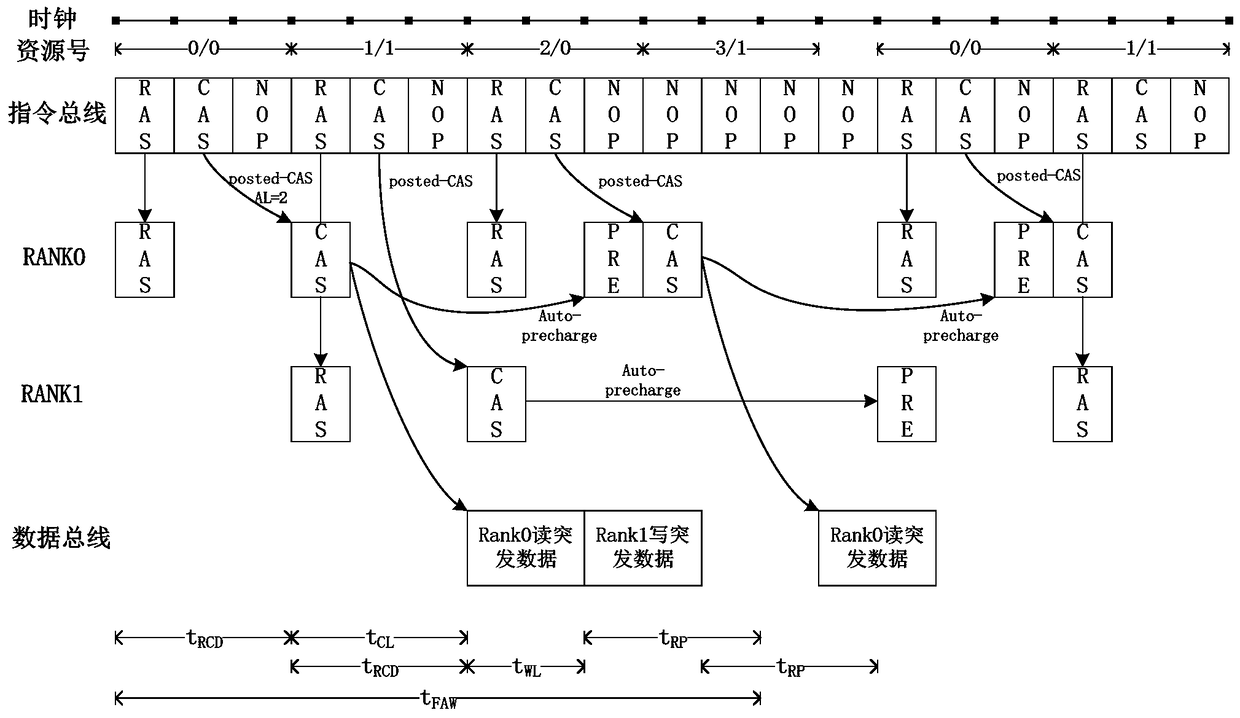

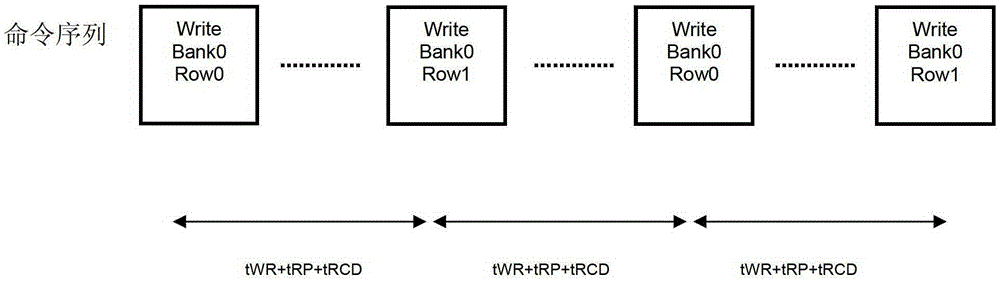

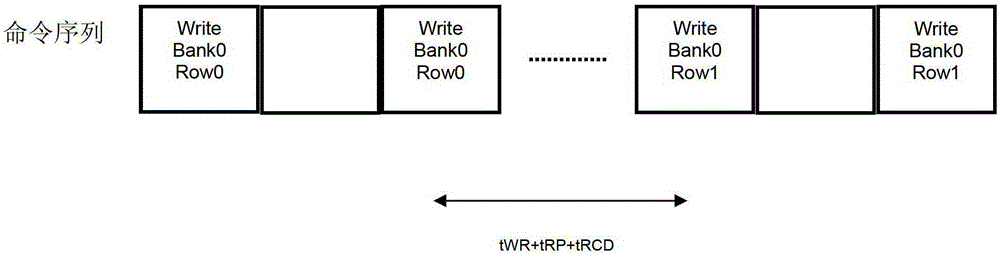

Design method of DDR2 SDRAM controller of high bandwidth utilization

InactiveCN101340365AOvercome the shortfall in bandwidth utilizationImprove overall utilizationData switching networksHigh bandwidthEngineering

The invention relates to a method for designing a controller in network data exchange equipment. The invention aims at providing a method that can improve the utilization rate of the bus under the condition that the burst-length is 8, and the method is characterized by low cost, high bandwidth and large storage. The technical proposal is: a method for designing DDR2 SDRAM controller with high bandwidth utilization rate comprises: (1) Bank rotation, Bank is switched after each Burst operation, under the premise of trying to keep high utilization rate of the data bus, the interval of adjacent twice visits of each Bank is enlarged; (2) Precharge operation is brought forward: if the next operation needs Precharge and then Active, and the next operation does not conflict with the operation, the Precharge operation is executed before the operation. The burst-length adopted by data is 8.

Owner:HANGZHOU RUINA SCI & TECH

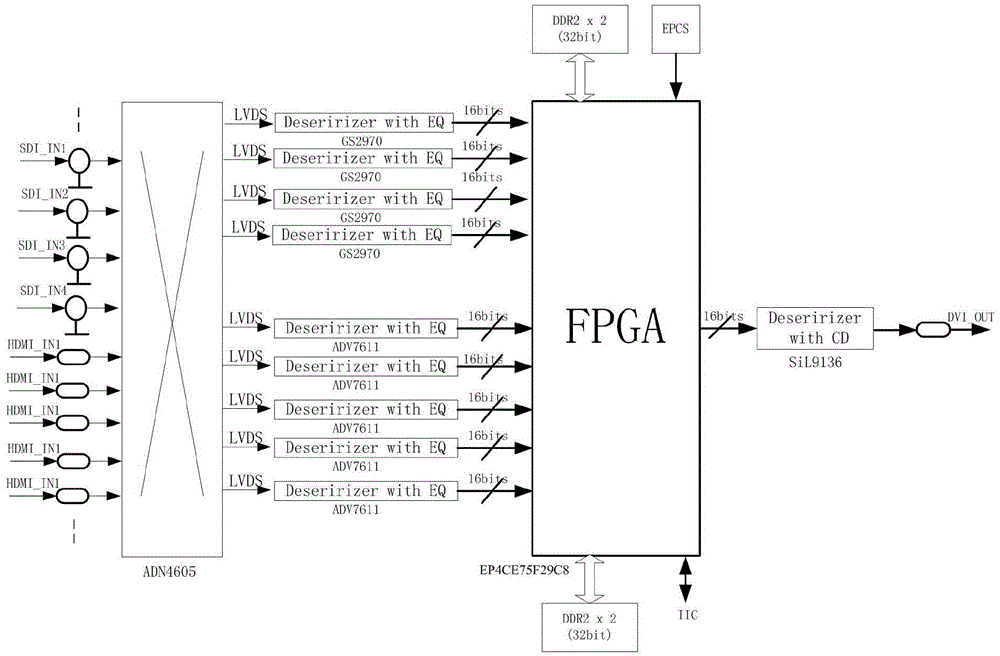

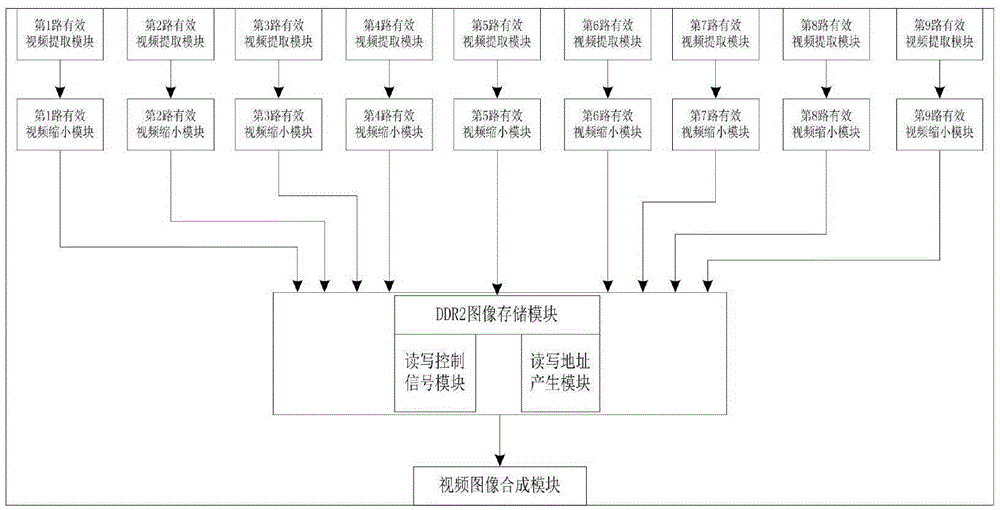

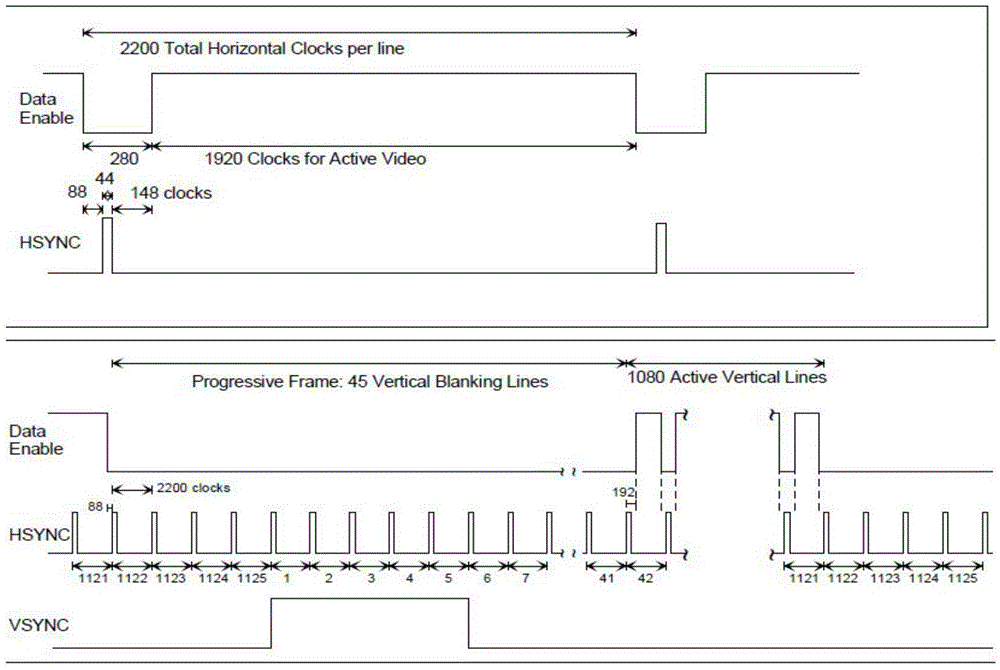

Solving method for multi-picture division cracked screen display of high-definition video

InactiveCN105430296ASolve the problem of split screen displayTelevision system detailsColor television detailsHDMIHigh-definition video

The invention discloses a solving method for multi-picture division cracked screen display of a high-definition video. The solving method adopts an SDI interface circuit, an HDMI interface circuit, a matrix chip, an SDI signal decoding circuit, an HDMI signal decoding circuit, an FPGA and a configuration circuit thereof, a DDR2 SDRAM data storage circuit and an HDMI signal coding circuit, wherein after the matrix chip receives SDI / HDMI signals from the SDI interface circuit and the HDMI interface circuit, the SDI signal decoding circuit and the HDMI signal decoding circuit decode the signals and convert into parallel digital signals; and then the parallel digital signals enter the FPGA and the configuration circuit thereof to extract, store and compound nine-channel video signals, and the processed data is converted into HDMI video signals by the HDMI signal coding circuit. The solving method provided by the invention can effectively solve the problem about multi-picture division cracked screen display of the high-definition video, and delay during display can be controlled within a frame by using the method.

Owner:深圳市捷视飞通科技股份有限公司

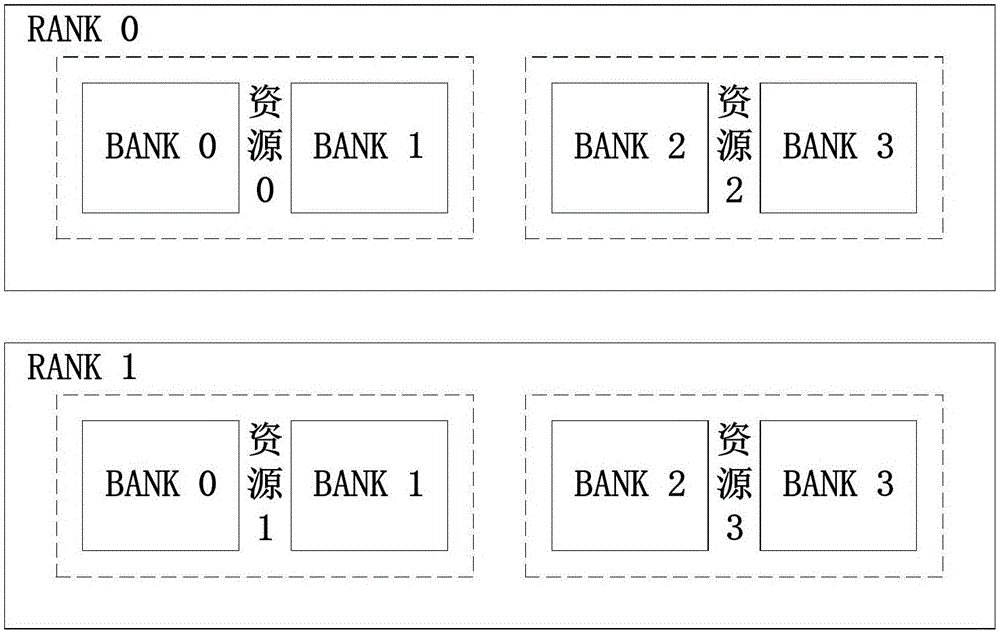

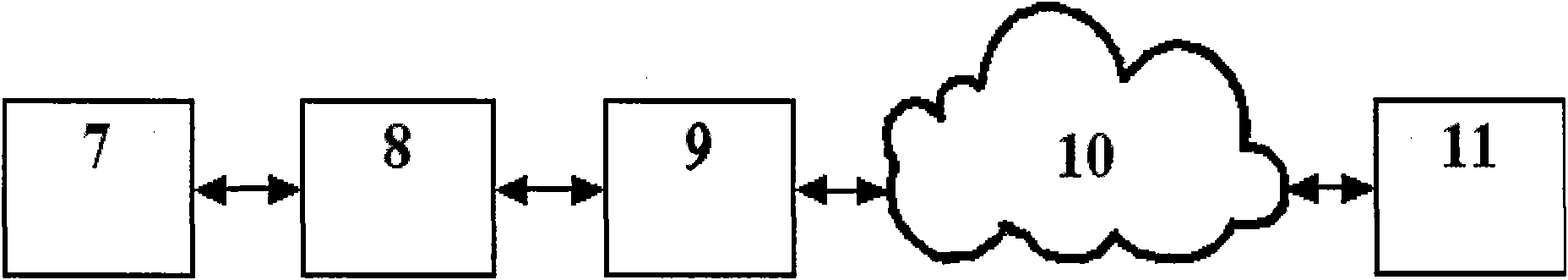

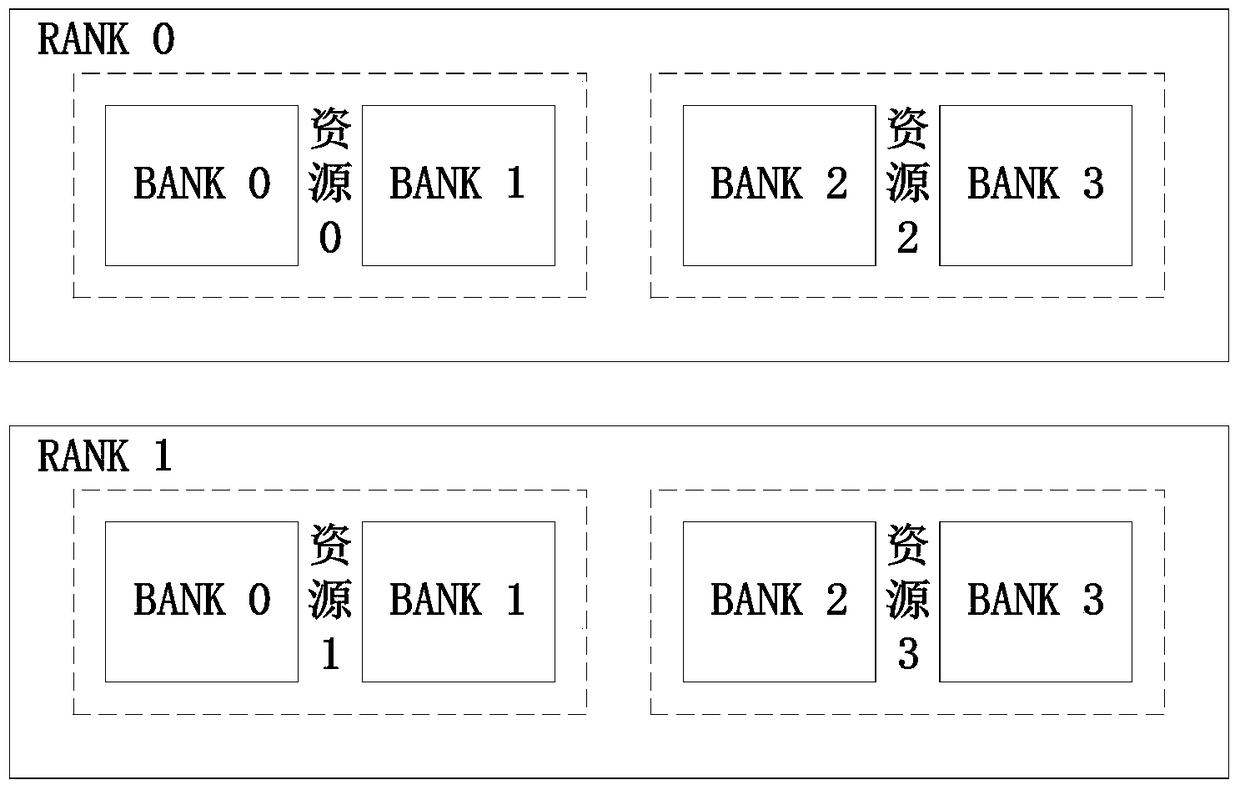

DDR2-SDRAM controller and low latency optimization method therefor

ActiveCN105045722AWill not violate the timing of the operationAvoid address dependenciesMemory adressing/allocation/relocationExternal storageLatency (engineering)

The invention discloses a DDR2-SDRAM controller used for a high-performance RF automatic testing platform, and a corresponding low latency optimization method. The DDR2-SDRAM controller is characterized in that firstly, an external storage module is not considered as a single resource; however, a storage space of a storage is divided into a plurality of independent logic resources according to rank and bank structures of a DRAM module; each resource belongs to a task with a fetching requirement, based on which, corresponding arbitration manner and instruction sequence are designed; secondly, a refreshing mechanism is improved and one refreshing period is arranged at the tail of 60 fetching instruction periods by the controller; an appointed rank in a storage array is refreshed through rank accessing to break up refreshing time into parts, so that the influence on access latency by the conflict of the fetching requirement and a refreshing request are reduced; and finally, the maximum fetching latency performance of each task of the system can be more greatly improved.

Owner:SOUTHEAST UNIV

Embedded video server based on ARM framework and DSP framework

InactiveCN101651814AImprove reliabilityReduce volumeTwo-way working systemsDsp architectureOperational system

The invention discloses an embedded video server based on an ARM framework and a DSP framework, belonging to the technical field of network video. The embedded video server comprises an ARM9 microprocessor, a TI C6000 DSP chip, a DDR2 SDRAM memory, a Flash memory, an SATA hard disk and a high-speed Ethernet controller, and is characterized in that the ARM9 microprocessor is respectively connectedwith the TI C6000 DSP chip, the DDR2 SDRAM memory, the Flash memory, the SATA hard disk and the high-speed Ethernet controller, and is responsible for operating an operation system and a user program.The invention provides an embedded video server which features reasonable design, high cost performance and good effect, and can be widely used in the following monitoring occasions, such as coal mines, hospitals, schools, road traffic, subdistricts and wine shops and the like; the invention constructs a remote monitoring system, and can prevent the wiring work in traditional monitoring solutions, thus realizing plug and play and reducing the complexity of network configuration.

Owner:SHANDONG UNIV

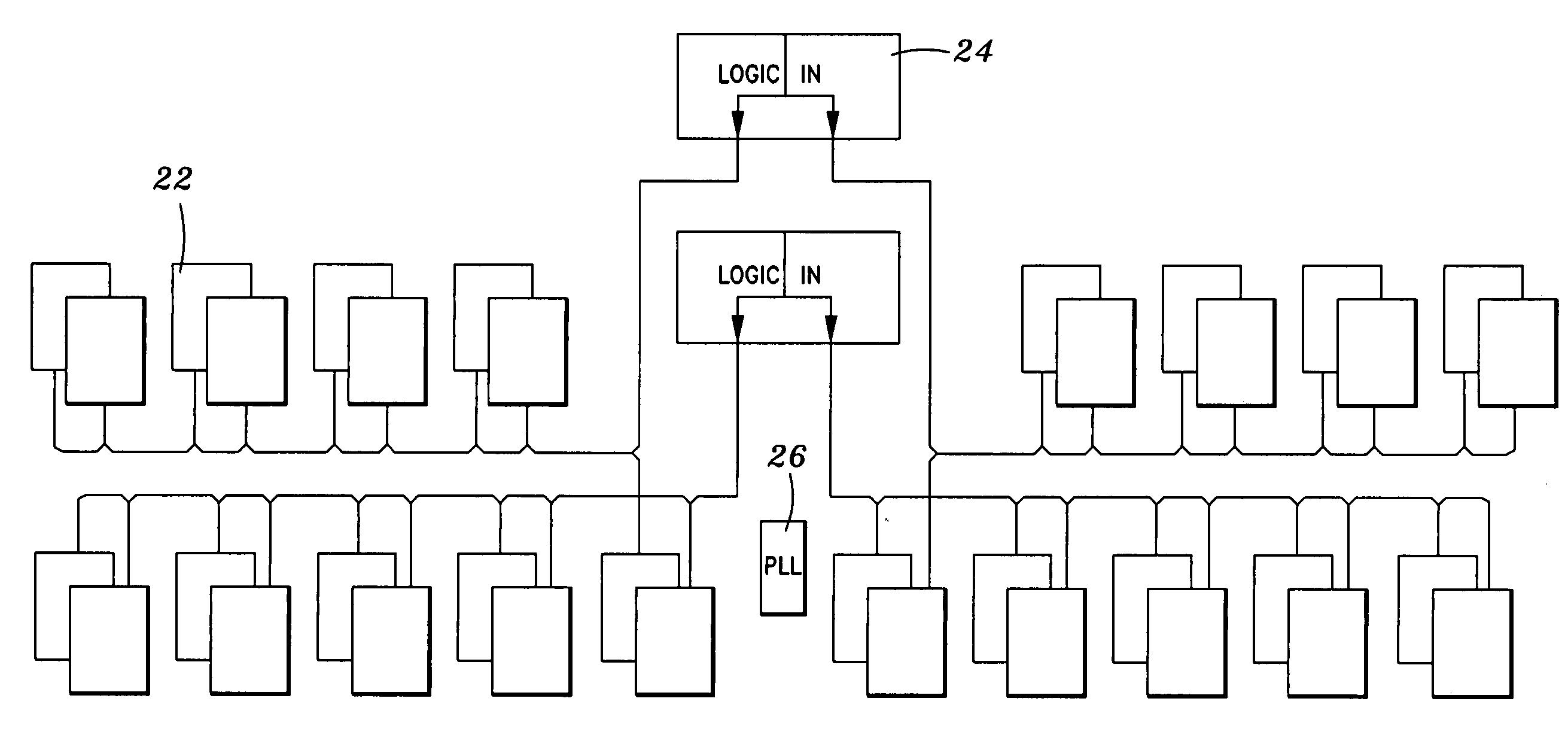

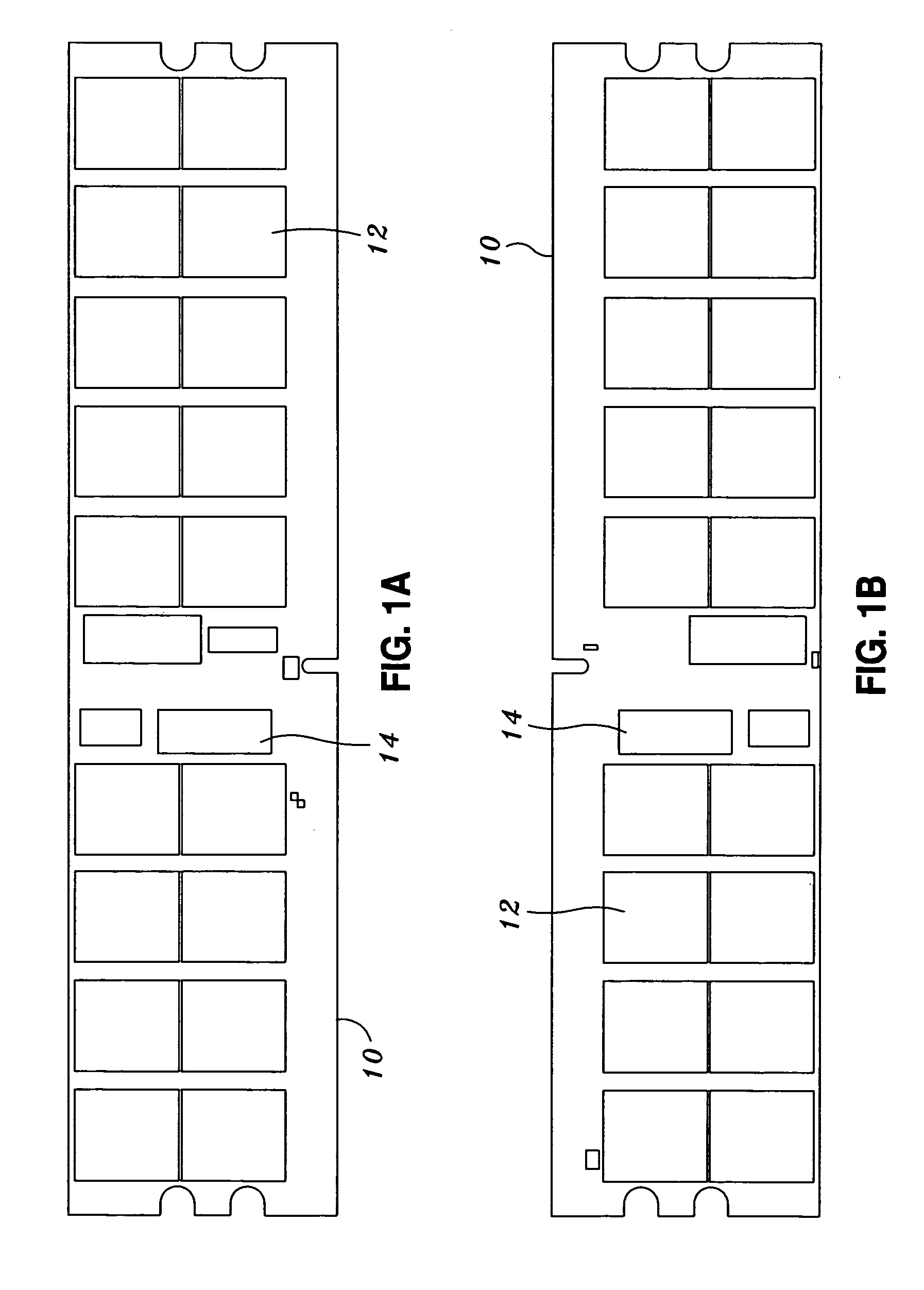

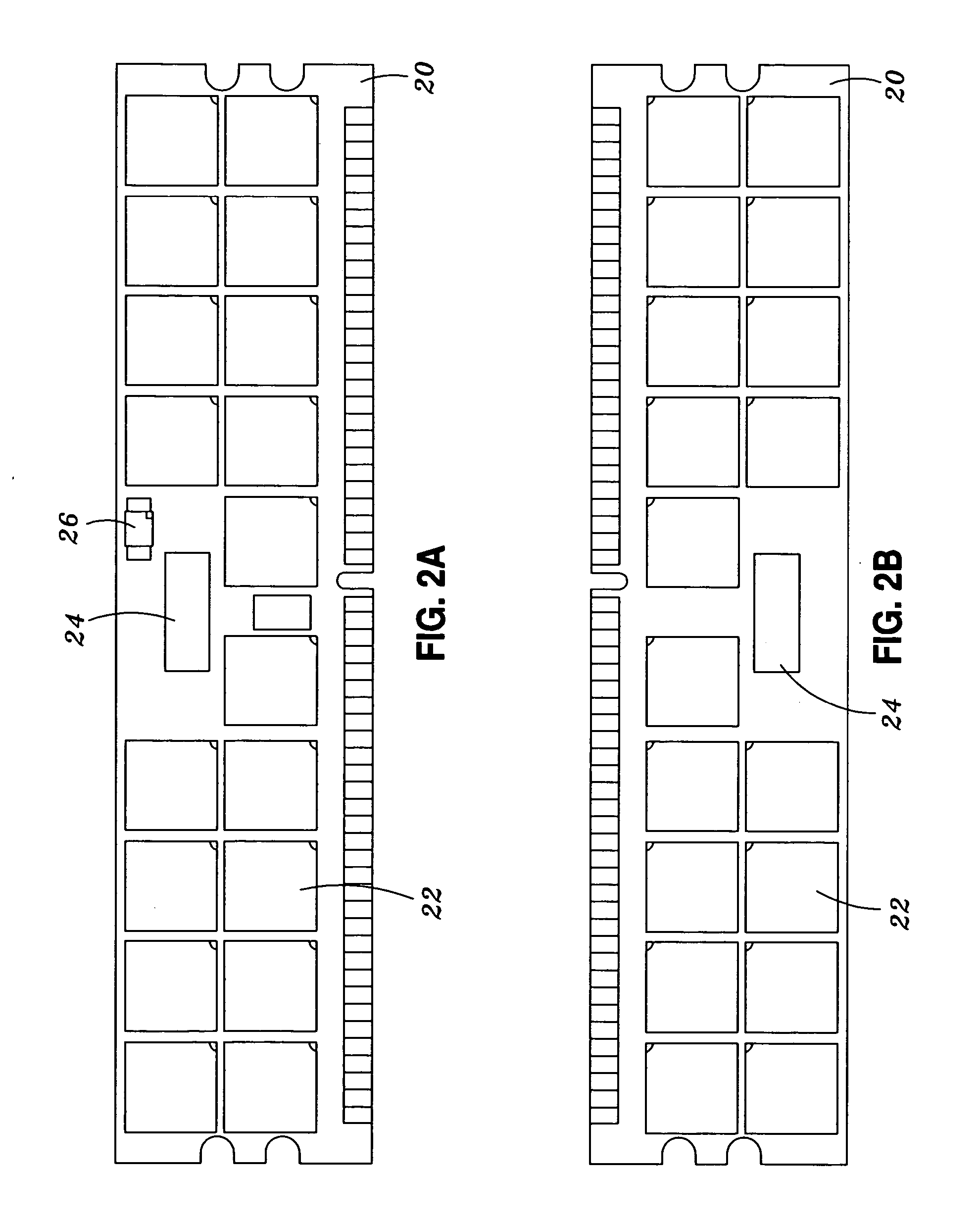

DDR2 SDRAM memory module

InactiveUS20060136658A1Reduce time skewExtension of timeStatic storageMemory systemsMemory chipDDR2 SDRAM

A DDR2 SDRAM memory module having memory chips arranged bilaterally symmetrical on the module. A register chip is arranged on each of two faces of the memory module, with each register chip coupled to half of the memory chips.

Owner:HGST TECH SANTA ANA

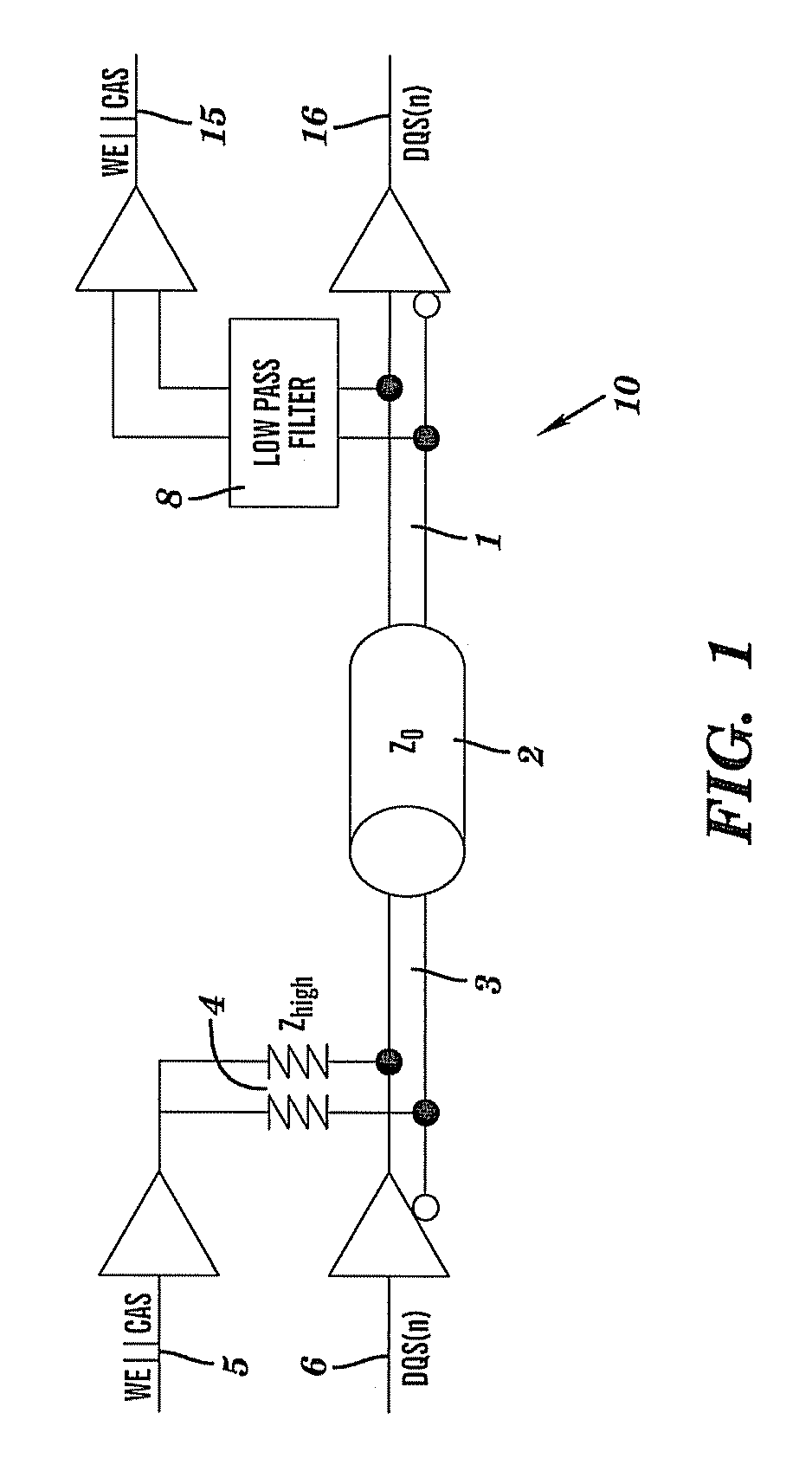

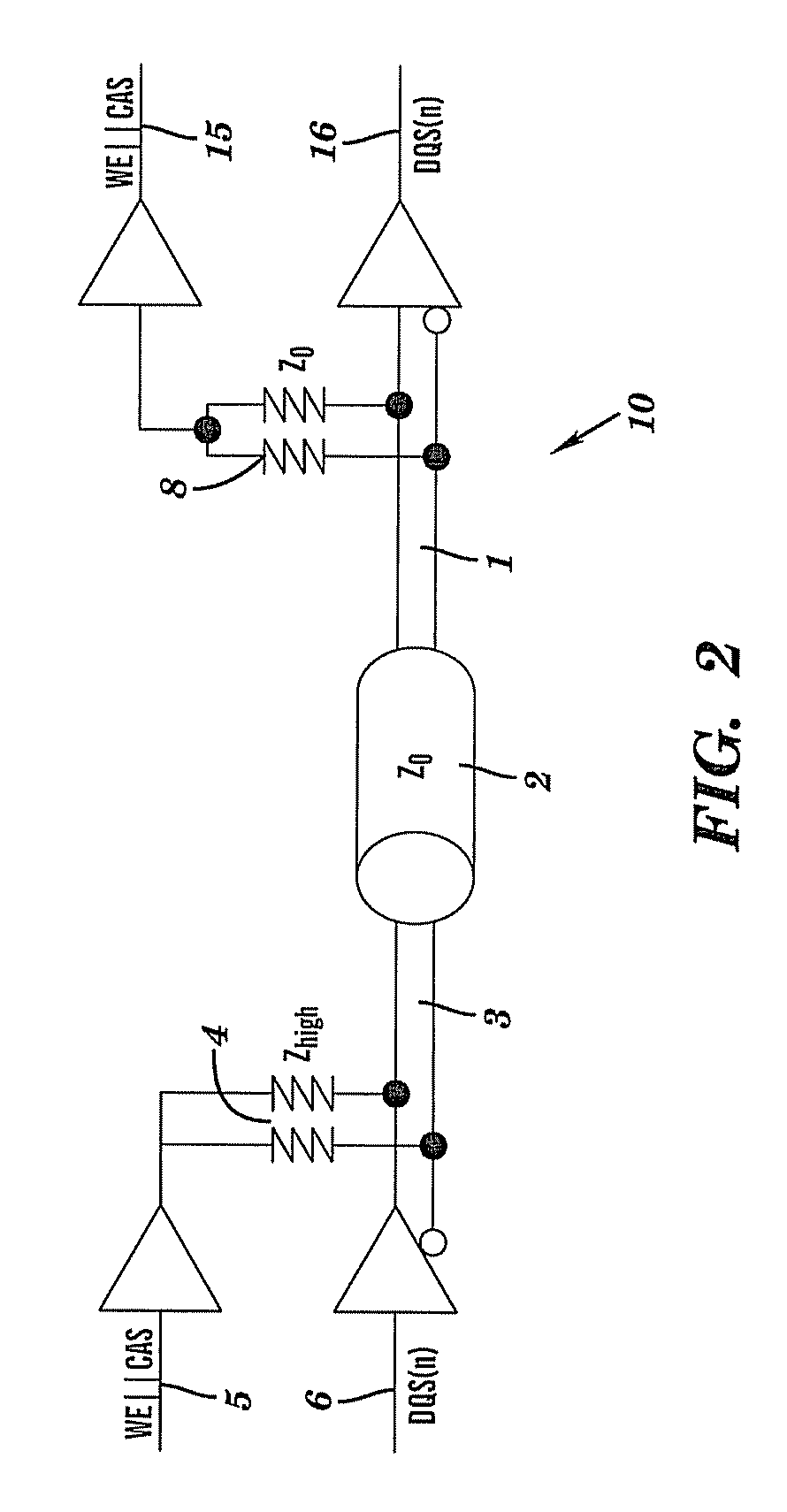

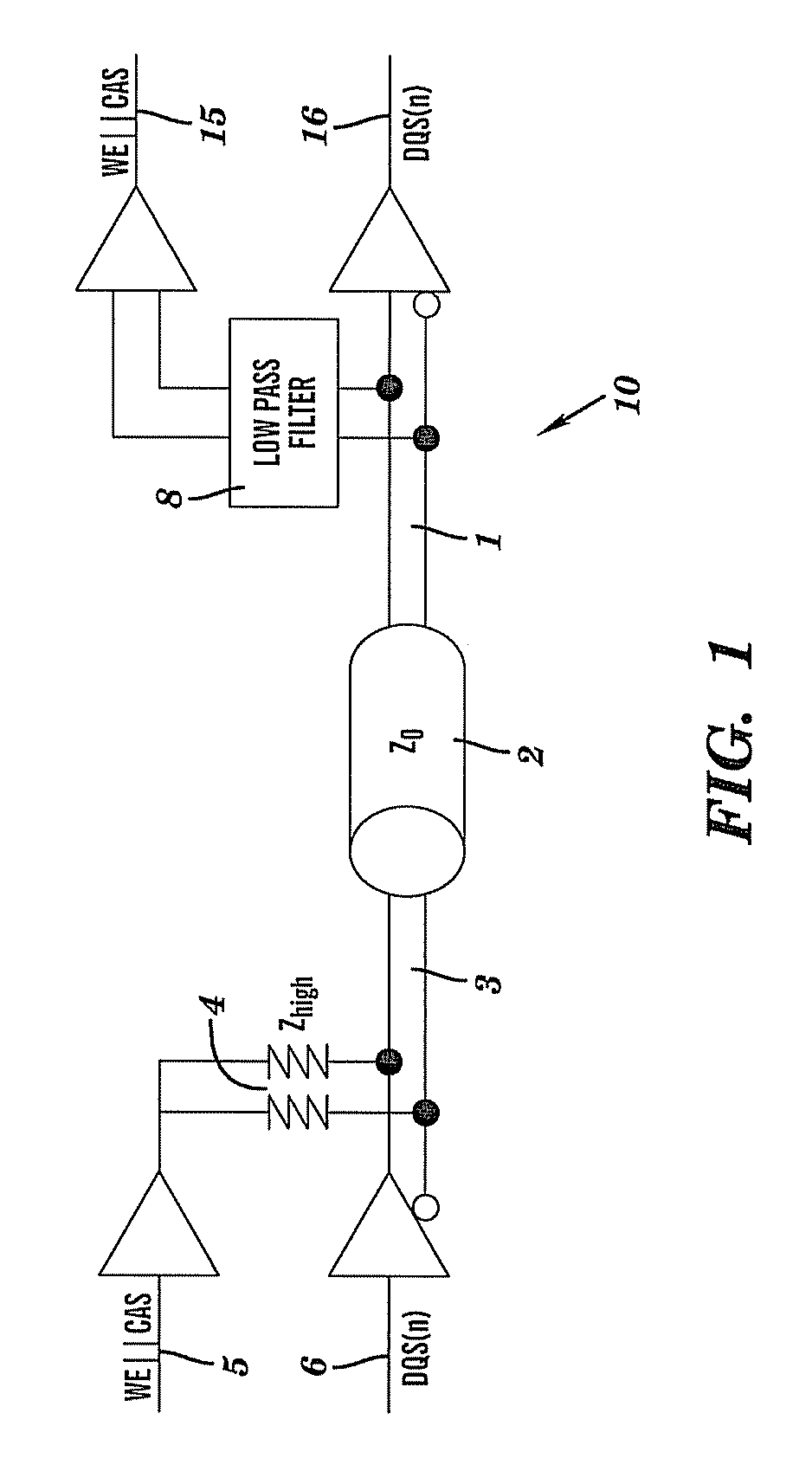

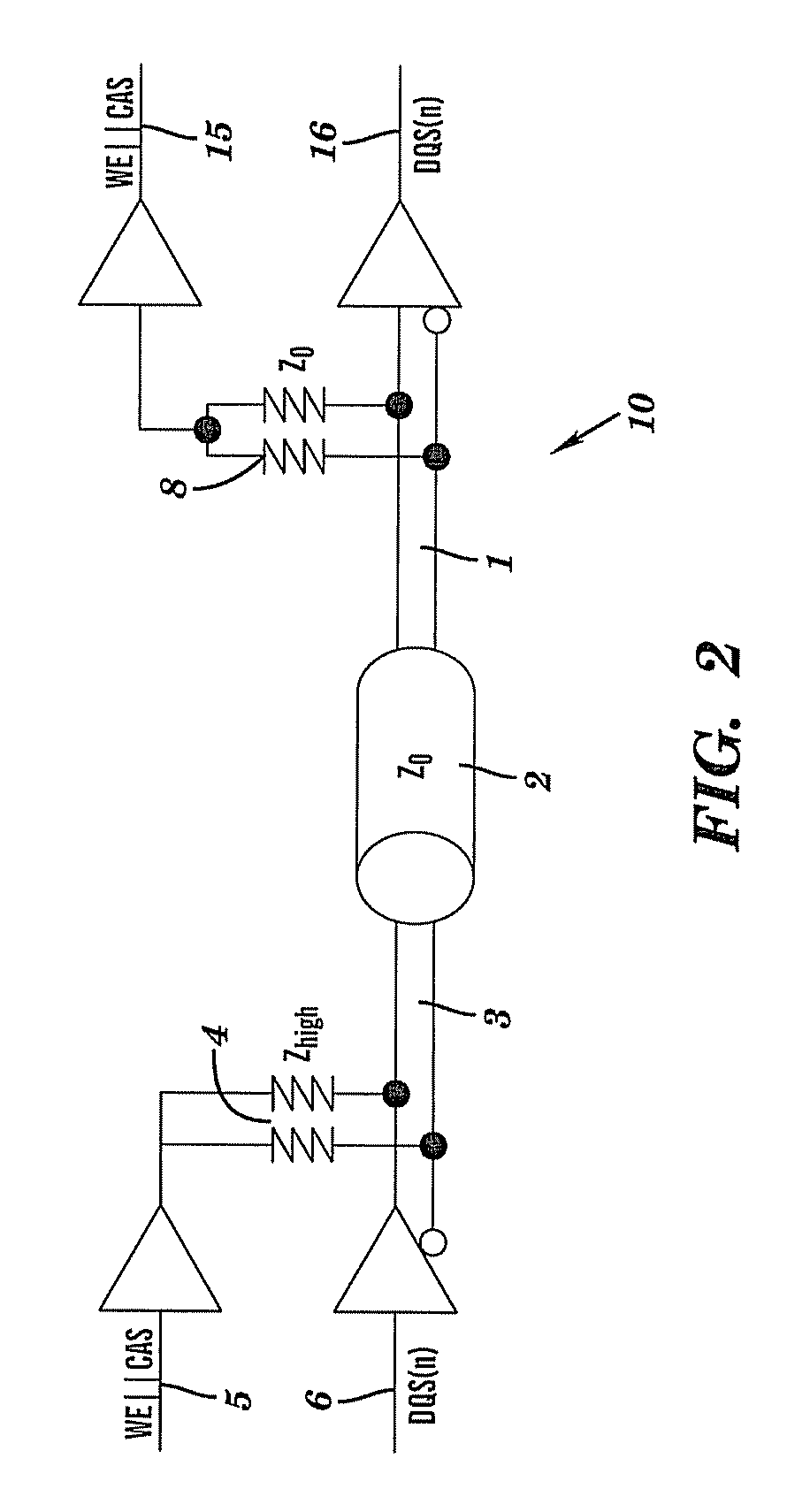

Using common mode differential data signals of ddr2 sdram for control signal transmission

A double-data-rate two synchronous dynamic random access (DDR2) memory circuit includes a low-speed input path and a high-speed input path coupled thereto by an input coupling and forming a common input, the common input coupled to a memory core, the memory core having a common output wherein a high-speed output path and a low-speed output path are coupled together by an output coupling and further coupled to the common output of the memory core.

Owner:META PLATFORMS INC

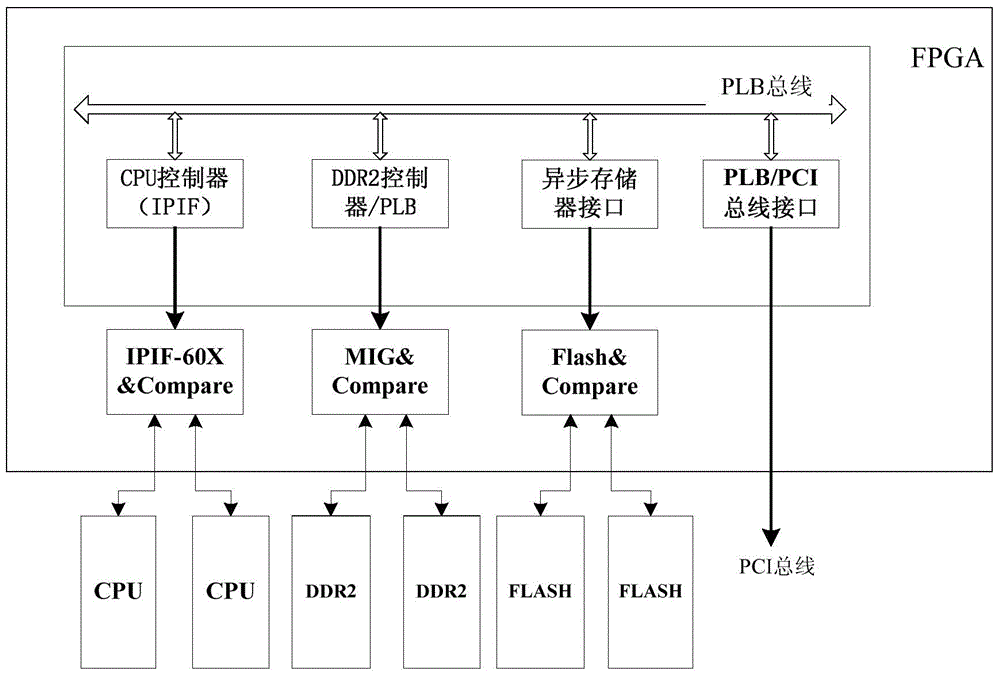

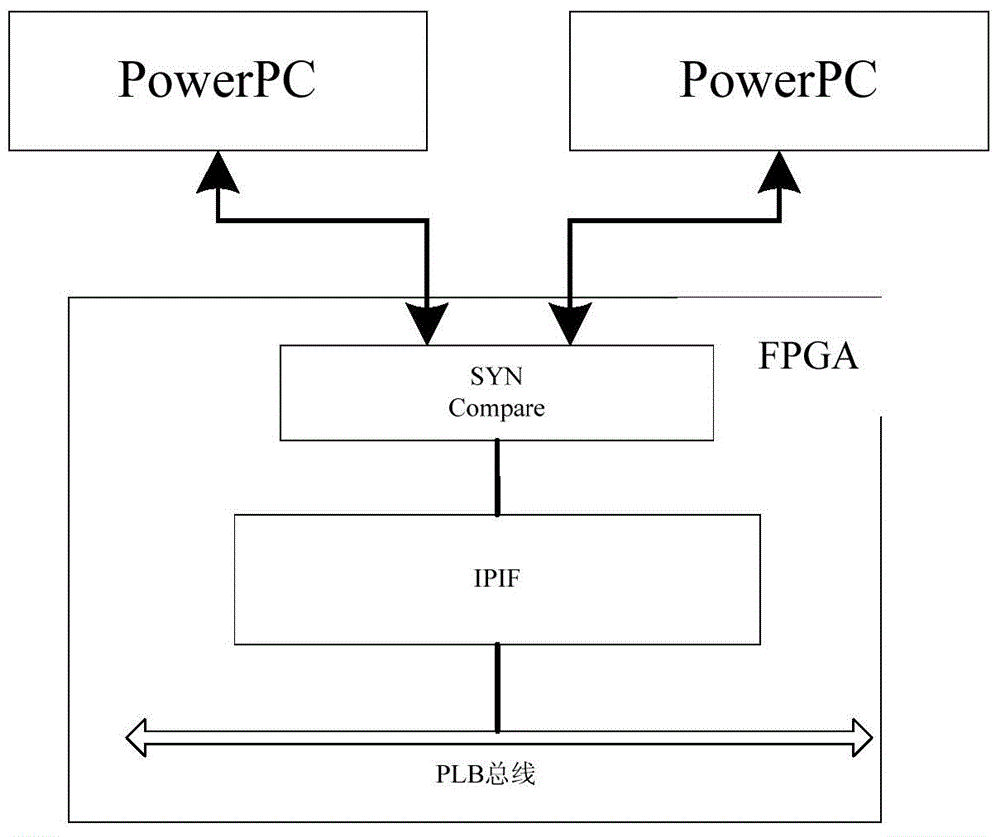

Loosely-coupled Lockstep processor system

ActiveCN104484299AImprove integrityRealize the operationReliability/availability analysisFpga implementationsHigh probability

The invention provides a loosely-coupled Lockstep processor system which comprises a processor with a 60x bus interface, a processor bus interface, a PLB, a DDR2 SDRAM storage interface and an asynchronous bus peripheral interface. The processor bus interface realizes timing conversion between the PLB and a 60X bus, the PLB is realized by an FPGA (field programmable gate array), the DDR2 SDRAM storage interface and an MIG interface in the FPGA realize access, of the PLB, to a synchronously-coupled DDR2, and the asynchronous bus peripheral interface accesses a coupled peripheral through the PLB. The bus synchronous comparing Lockstep processor system can realize realtime high-probability fault detection and isolation of a computer, DMA operation and slave equipment operation of the system can be guaranteed, the loosely-coupled Lockstep processor system has the advantages of expandability, convenience in realization and the like, and high reliability in data processing of the computer can be guaranteed.

Owner:AVIC NO 631 RES INST

Adaptive Novel Memory Matching Data Strobe Method

InactiveCN102298974AAvoid effectivenessAvoid environmental problemsStatic storageDDR2 SDRAMPhase point

The present invention relates to data storage technology. The present invention solves the problem that the existing same system is easy to cause memory overflow and collapse when using new memory and / or new memory from different manufacturers in different temperature environments, and provides a self-adaptive new memory matching data strobe pulse The method, and its technical solution can be summarized as: detecting the high-order and low-order DQS / DQ phase points of each DDR SDRAM at each initialization to obtain an effective point, and then selecting the intermediate value to preset as an environmental parameter. The invention has the beneficial effects of stable operation and is suitable for systems using DDR2 SDRAM and / or DDR3 SDRAM.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

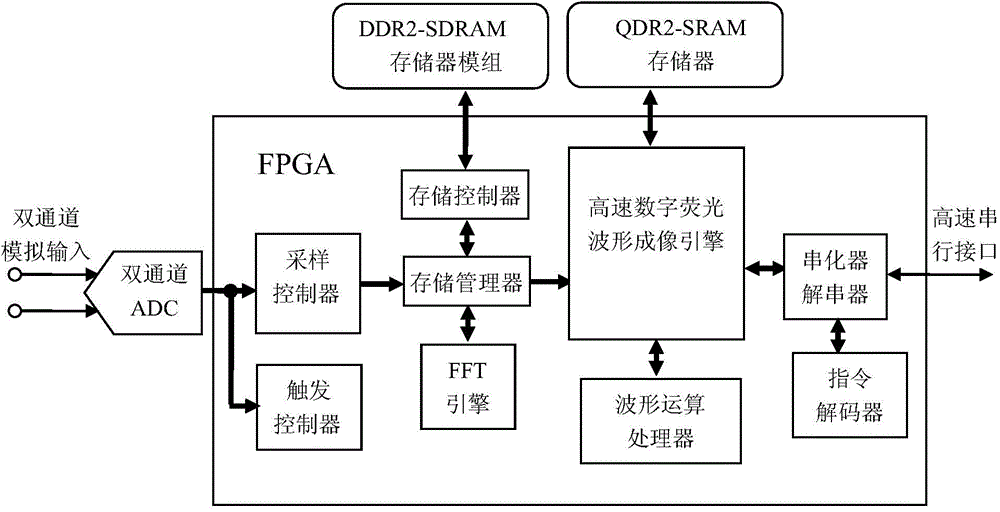

Oscilloscope sampling and imaging system

The invention belongs to the field of signal processing, and particularly relates to oscilloscope sampling and imaging module technology. An oscilloscope sampling and imaging system comprises the components of a double-channel ADC, a DDR2-SDRAM memory module, a QDR2-SRAM memory and an FPGA. The double-channel ADC, the DDR2-SDRAM memory module and the QDR2-SRAM memory are connected with the FPGA, wherein the double-channel ADC receives and simulates frontend signal input and converts the input signal to a digital signal. The FPGA realizes all signal processing operations from digital signal input to waveform imaging transmission. Through sampling signal data, a complicated signal is wholly captured and analyzed in higher precision and waveform visualizing of the data is performed, thereby displaying signal amplitude, time and frequency of the amplitude along with time on a screen, and effectively reducing loss rate.

Owner:JIANGSU LVYANG ELECTRONICS INSTR GROUP

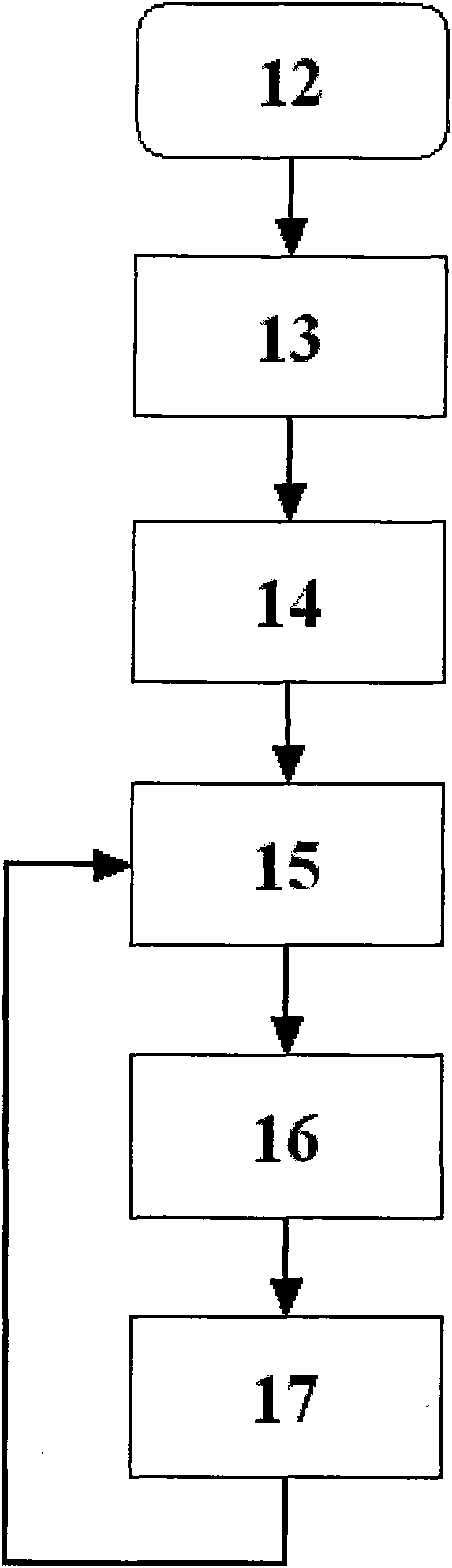

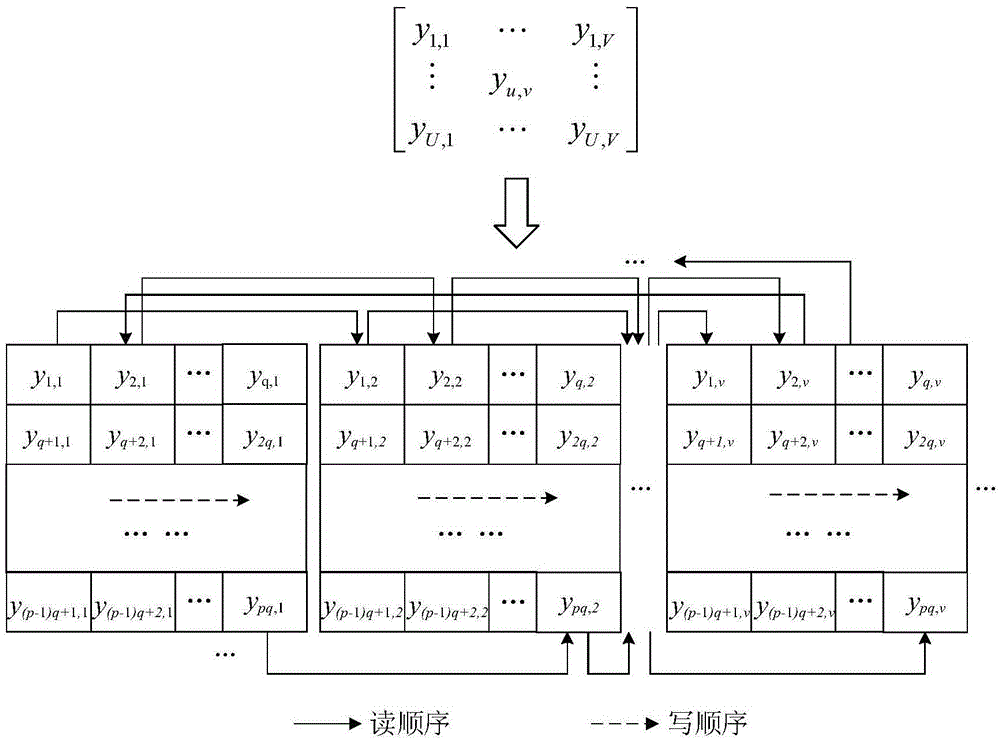

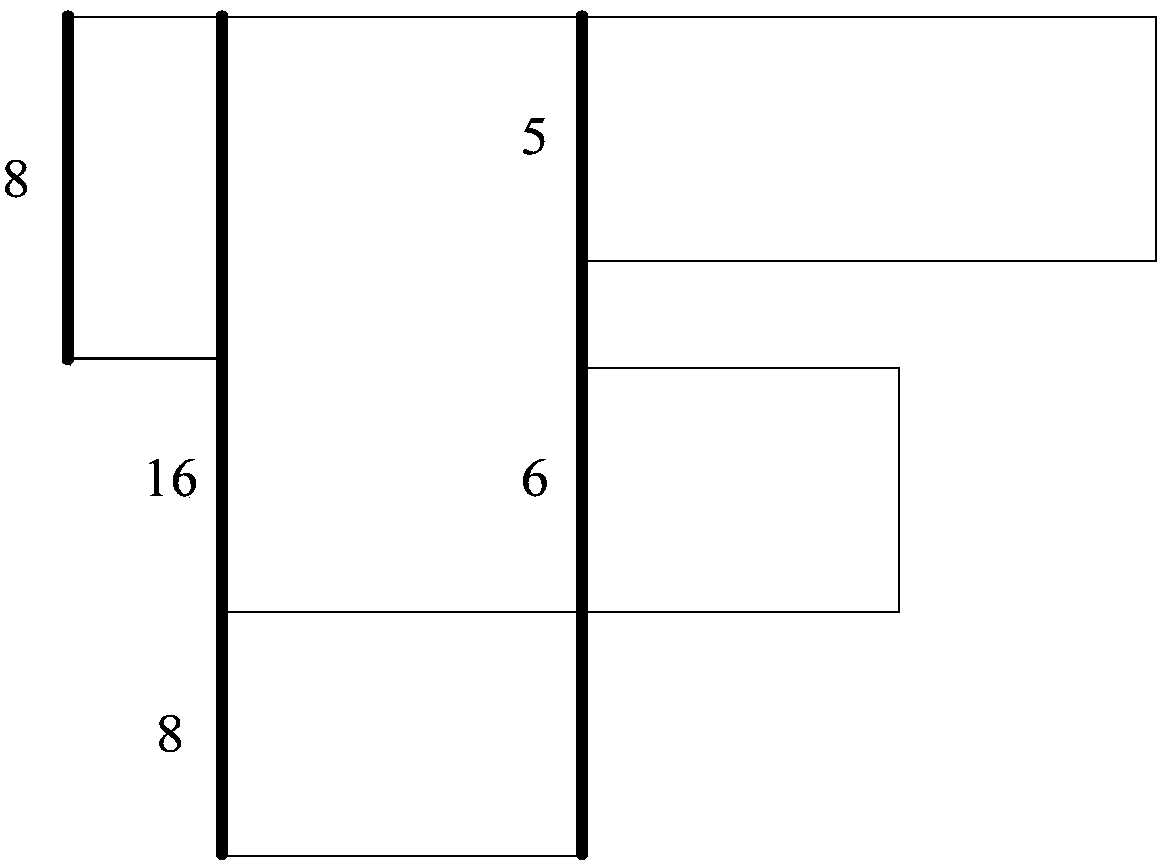

DDR2 SDRAM-based short cycle storage method

InactiveCN105528305APersistent accessImprove access speedMemory architecture accessing/allocationMemory adressing/allocation/relocationDouble data rateMemory interface

The present invention discloses a method for short cycle data storage based on a DDR2 SDRAM (Double Data Rate 2 SDRAM, the second generation double data rate synchronous dynamic random access memory, DDR2 for short). The method comprises the steps of determining a read-write short cycle and read-write operation execution times in the short cycle according to the storage rate requirement and DDR2 model; designing a few-row-multiple-column storage structure according to a read-write scheme and DDR2 storage space; and controlling the DDR2 to alternatively perform the read-write operation in the short cycle by a user through an MIG (Memory Interface Generator). The problem that in the prior art, continuous in and out of data are restricted by a storage method that read-write operation is individually executed for a long time is solved, and data access efficiency is improved when the DDR2 processes data under the condition that read-write sequences are not consistent.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

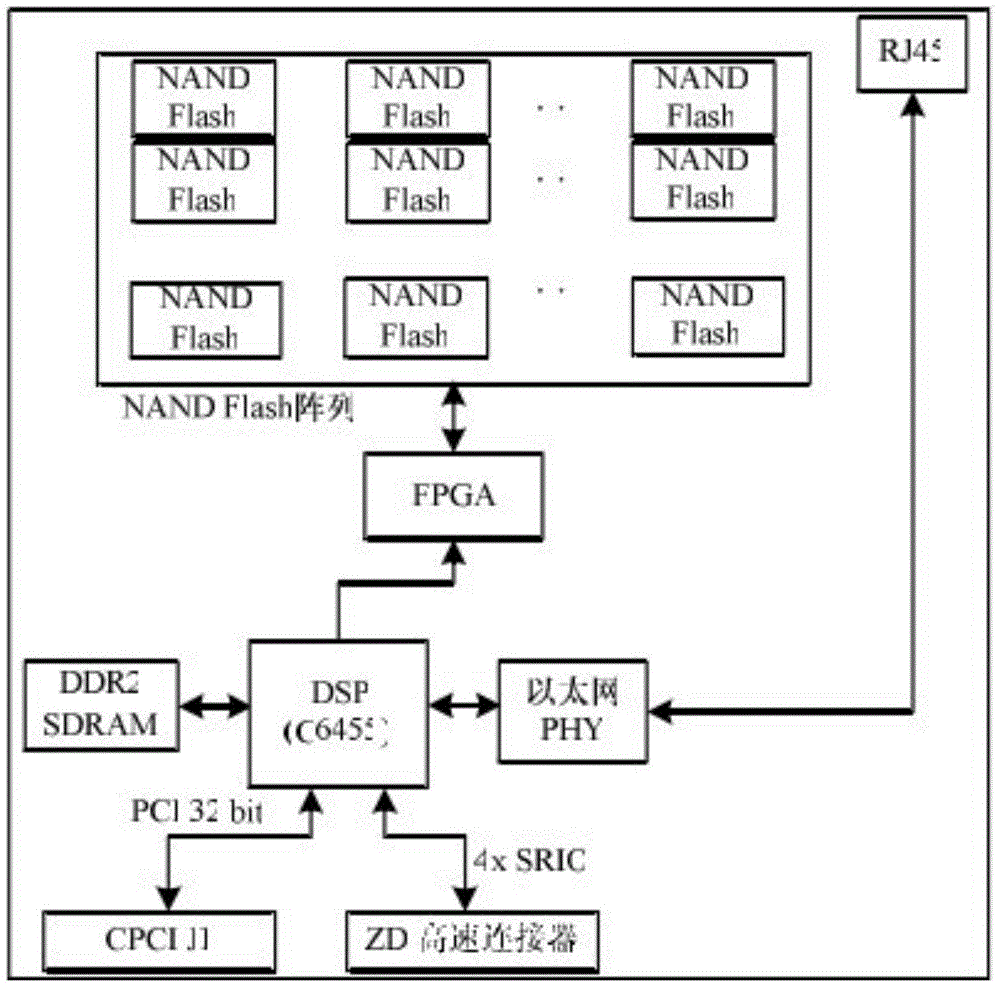

High-speed massive data storage system

InactiveCN105630400AIncrease storage bandwidthImprove scalabilityInput/output to record carriersDigital signal processingDDR2 SDRAM

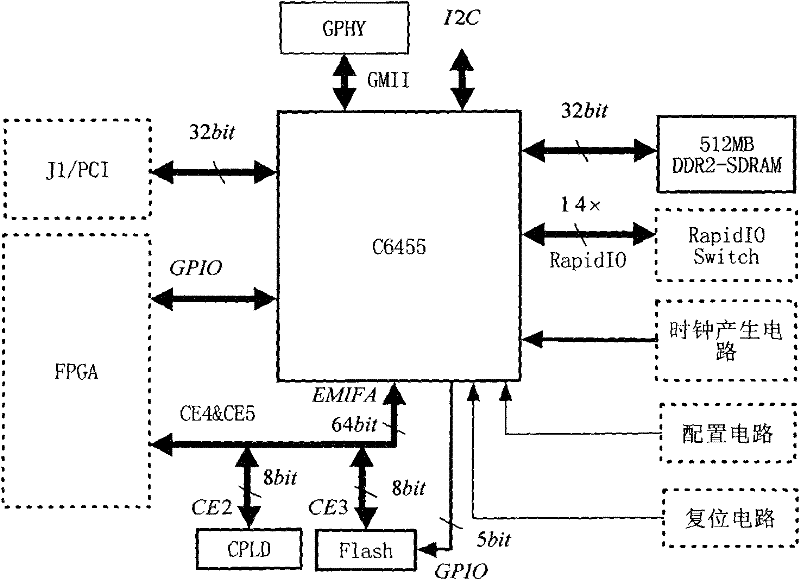

The invention belongs to the field of digital signal processing, and discloses a high-speed massive data storage system. The system comprises an NAND Flash array, an FPGA, a DSP, an Ethernet PHY, a DDR2 SARAM, a CPCI J1 and a ZD high-speed connector, wherein the FPGA is electrically connected with each of the NAND Flash array and the DSP; the DSP communicates with each of the Ethernet PHY, the DDR2 SDRAM, the CPCI J1 and the ZD high-speed connector; the NAND Flash array adopts a spatial parallel and time parallel method to broaden the storage bandwidth; the DSP provides a standard high-speed interface for the DDR2 SDRAM and is connected with the FPGA through an EMIF bus; and the DSP receives an instruction from an external master control end and transmits the instruction to the FPGA. The system disclosed in the invention has favorable system expansibility and universality.

Owner:JIANGSU LVYANG ELECTRONICS INSTR GROUP

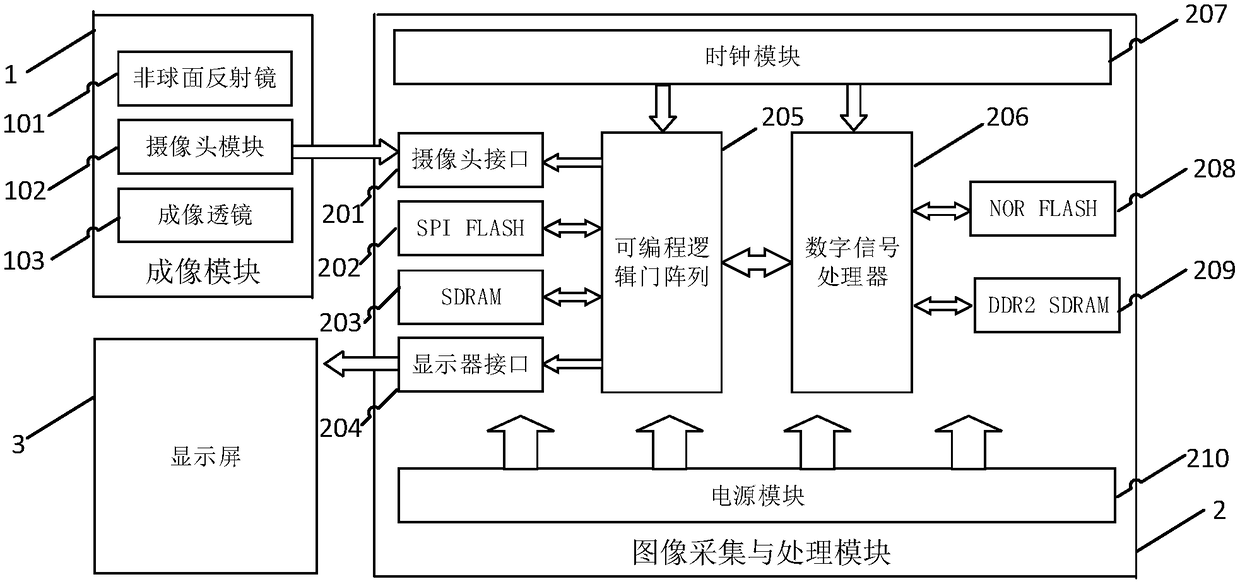

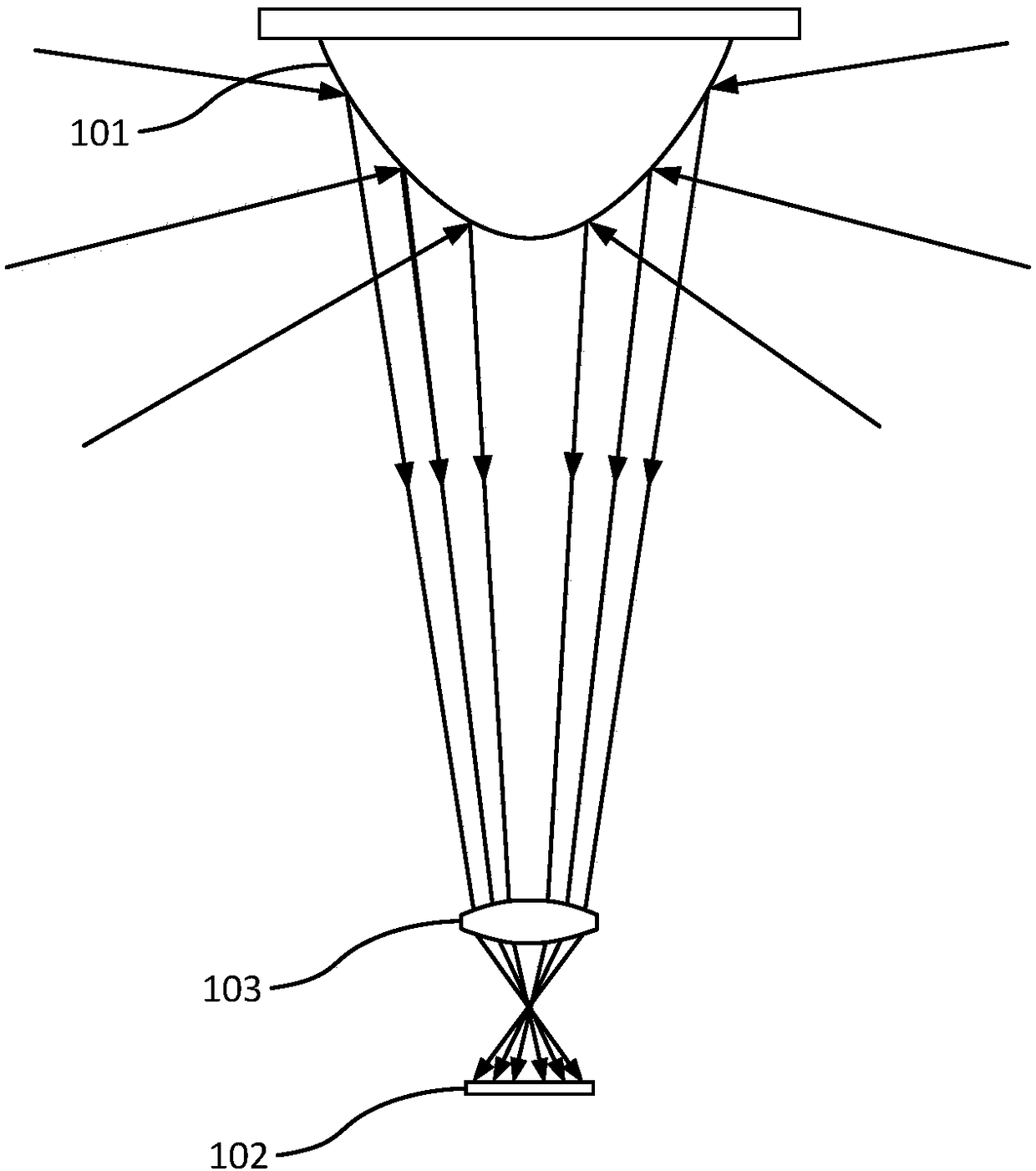

High-definition panoramic video image collecting and processing system

PendingCN108093179AAcquisition speed is fastImprove processing speedTelevision system detailsColor television detailsImaging lensLogic gate

The invention discloses a high-definition panoramic video image collecting and processing system. The system comprises an imaging module, an image collecting and processing module and a display screen; the imaging module comprises an aspherical mirror, a camera module and an imaging lens, and the image collecting and processing module comprises a camera interface, an SPI-FLASH, an SDRAM, a displayer interface, a programmable logic gate array, a data signal processor, a clock module, an NOR-FLASH, a DDR2-SDRAM and a power module; the imaging module is electrically connected to the image collecting and processing module, and the image collecting and processing module is electrically connected to the display screen. In the high-definition panoramic video image collecting and processing system, real-time high-definition panoramic video image collection with the horizontal angle of 360 degrees and the vertical angle of 80 degrees can be achieved only by a single camera, and a collected annular image can be spread into a normal image convenient to observe by human eyes in real time and displayed.

Owner:CHANGCHUN UNIV OF SCI & TECH

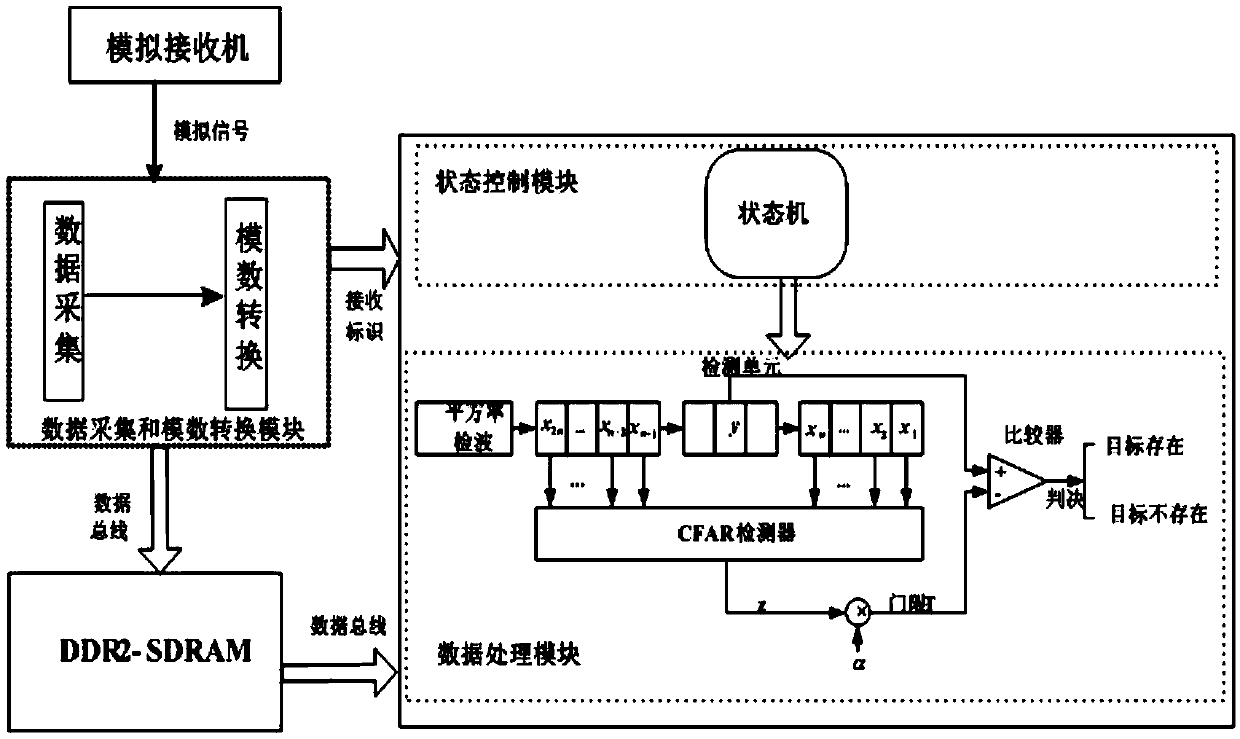

fpga-based system on chip and its object detection method

ActiveCN106291500BShorten operation timeReduce computational complexityWave based measurement systemsComplete dataChinese characters

Owner:XIDIAN UNIV +1

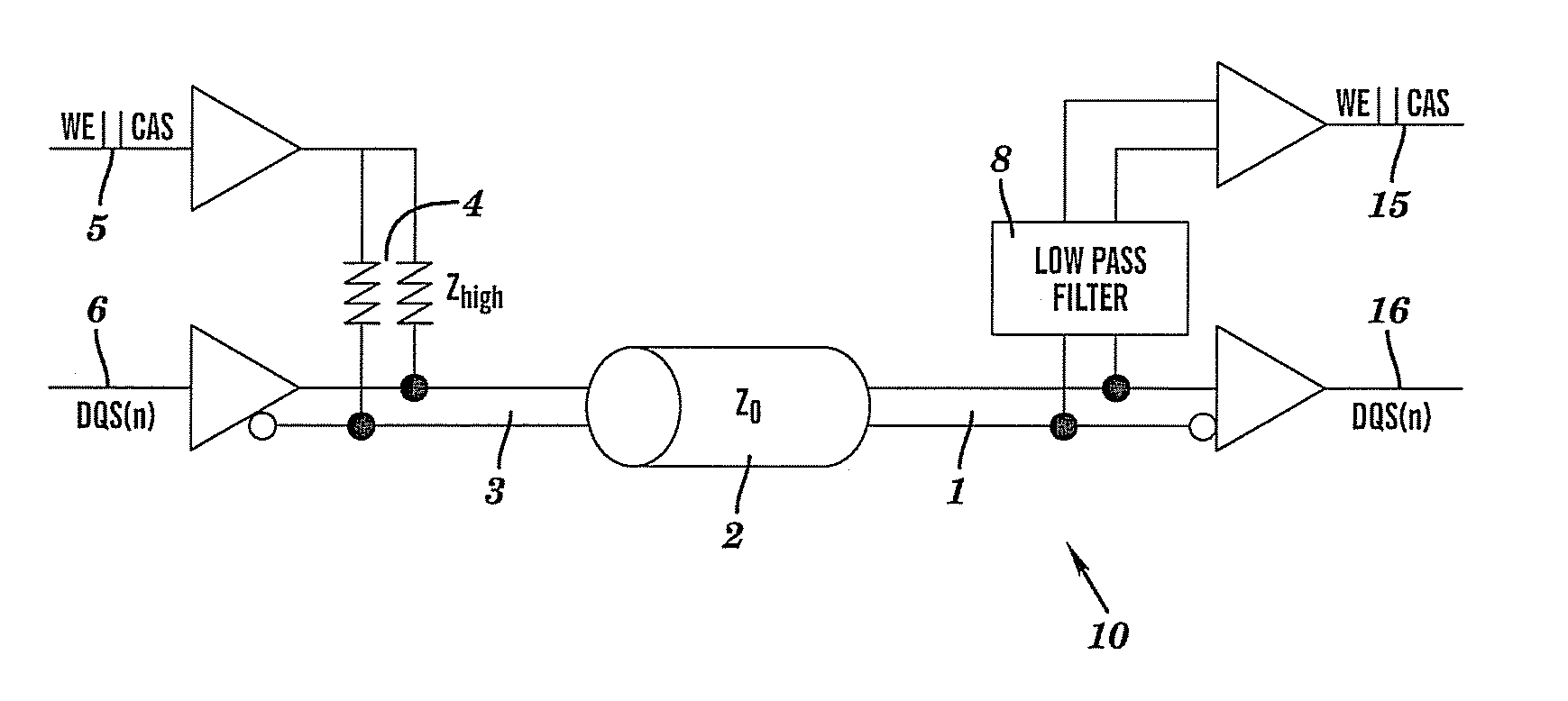

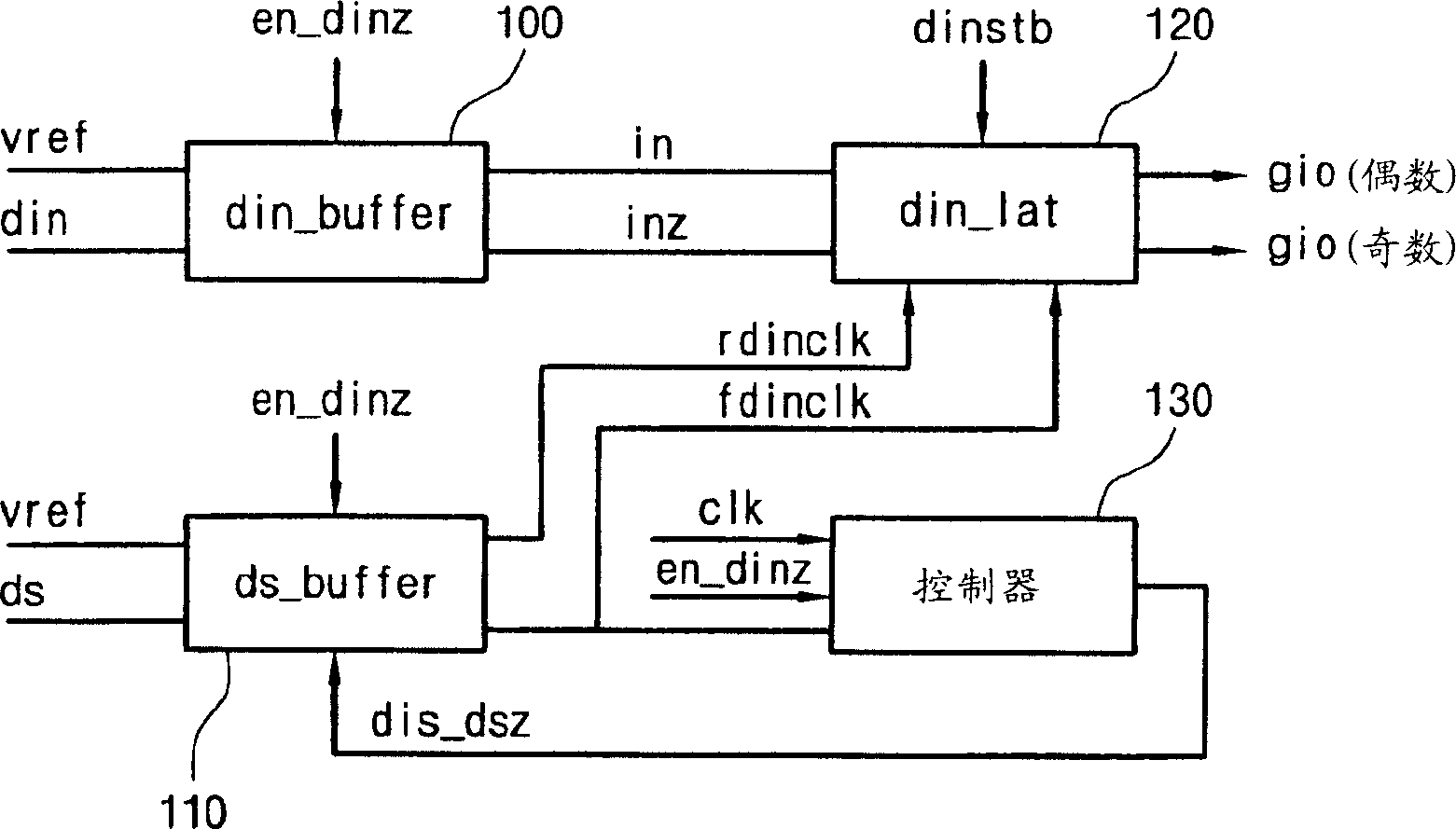

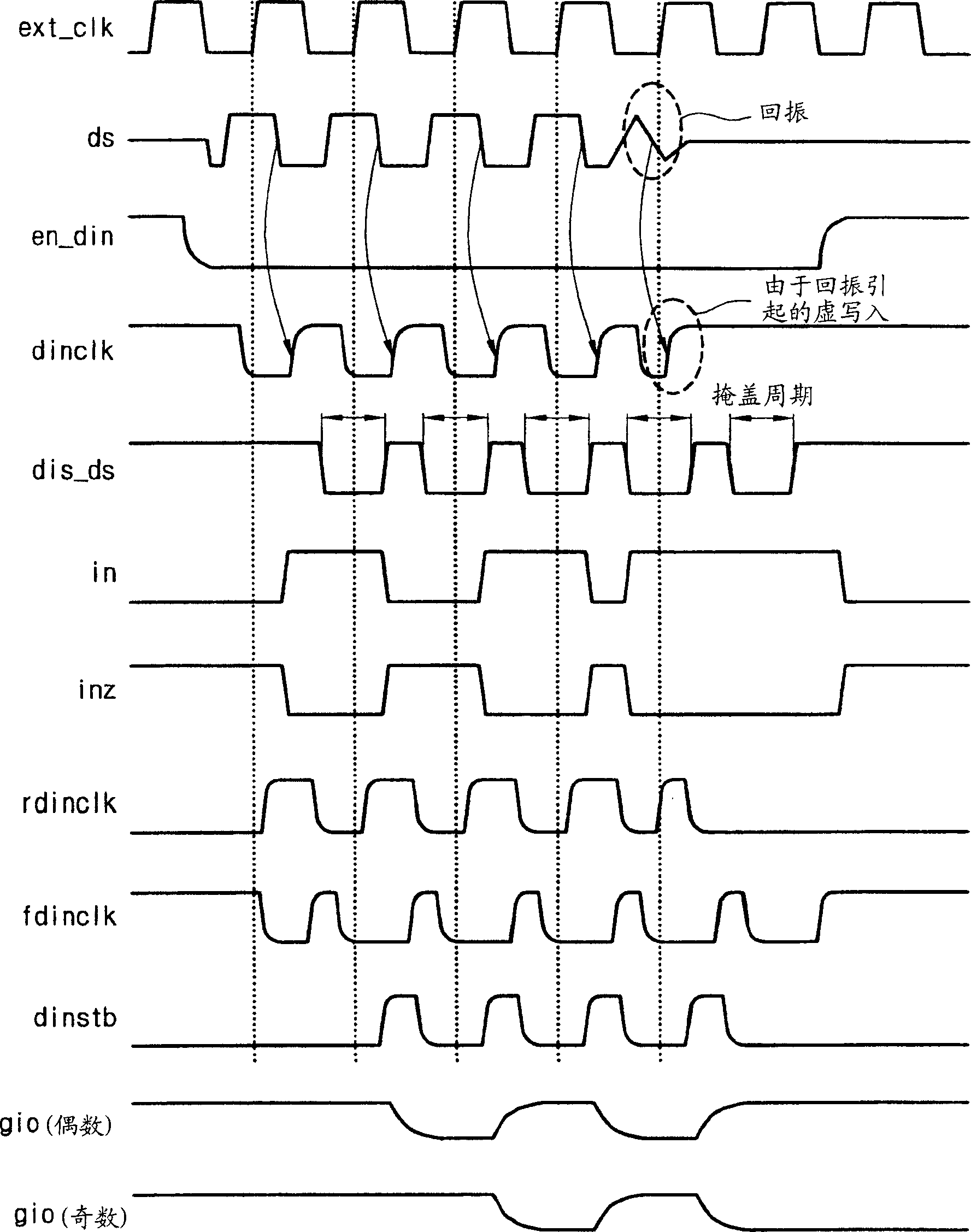

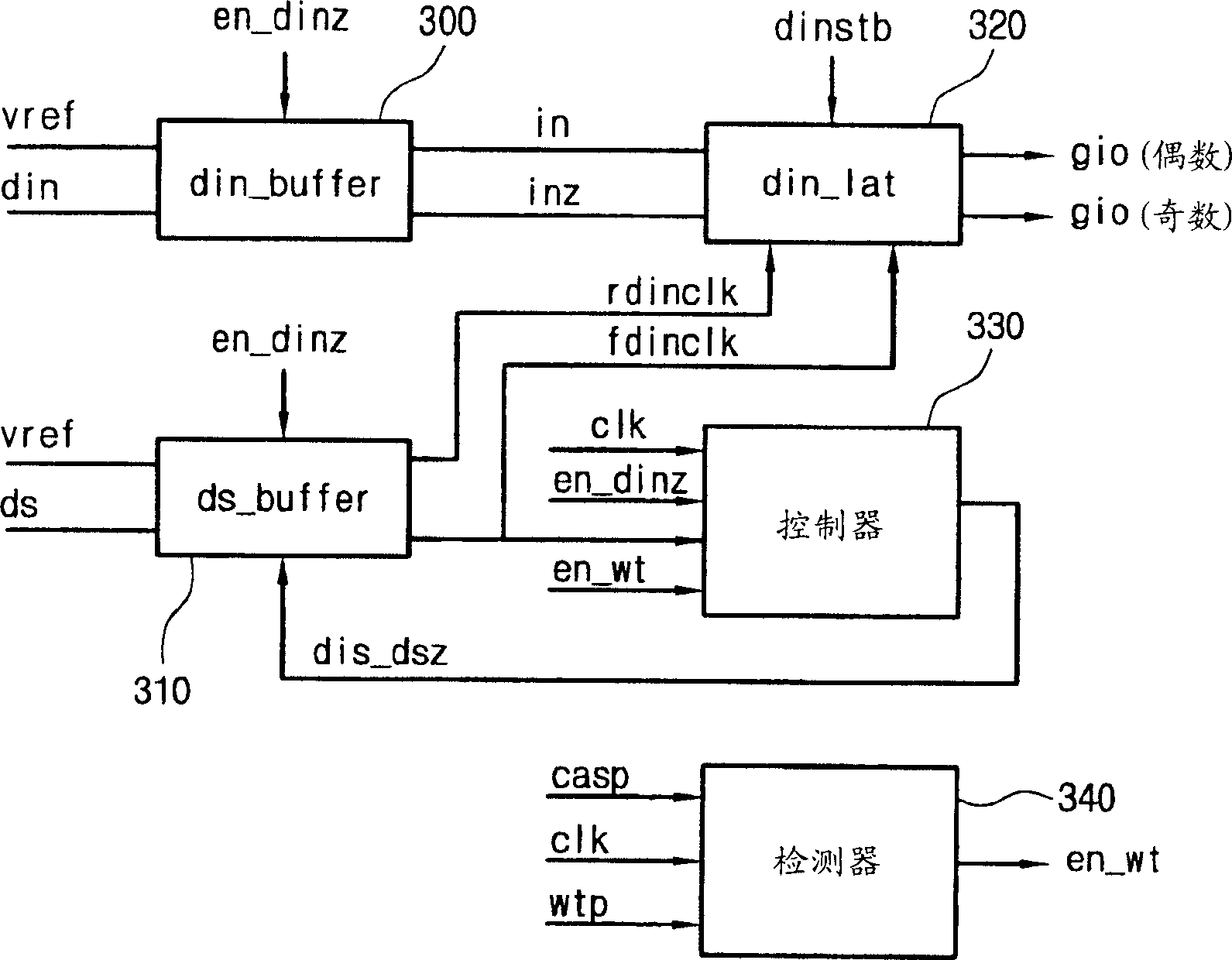

Data pass control device for masking write ringing in ddr sdram and method thereof

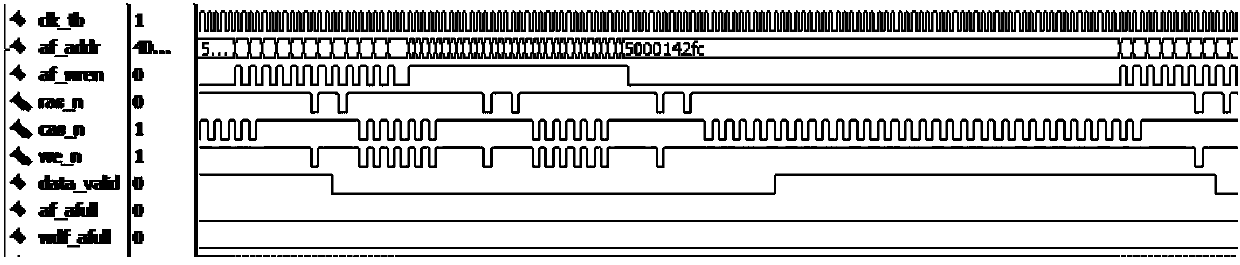

The present invention relates to a data pass control device for masking a ringing of a data strobe that occurs when a write operation in a DDR SDRAM is completed. The data pass control device for masking the write ringing in the DDR SDRAM can be advantageously used for masking only a section with the ringing problem during the write operation, so that any unnecessary operations during the write operation can be eliminated and a more stable write operation can be realized by eliminating a write fail.

Owner:SK HYNIX INC

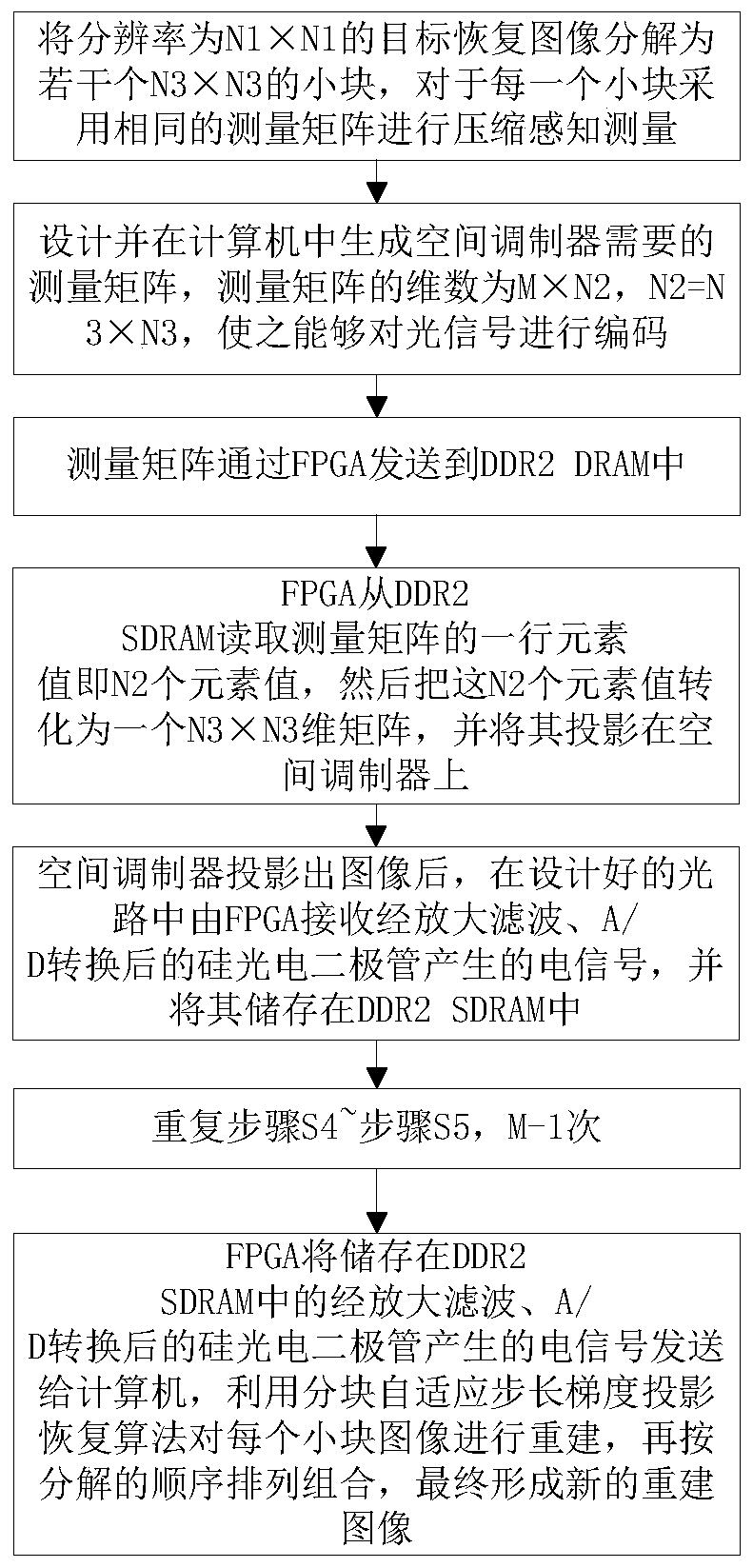

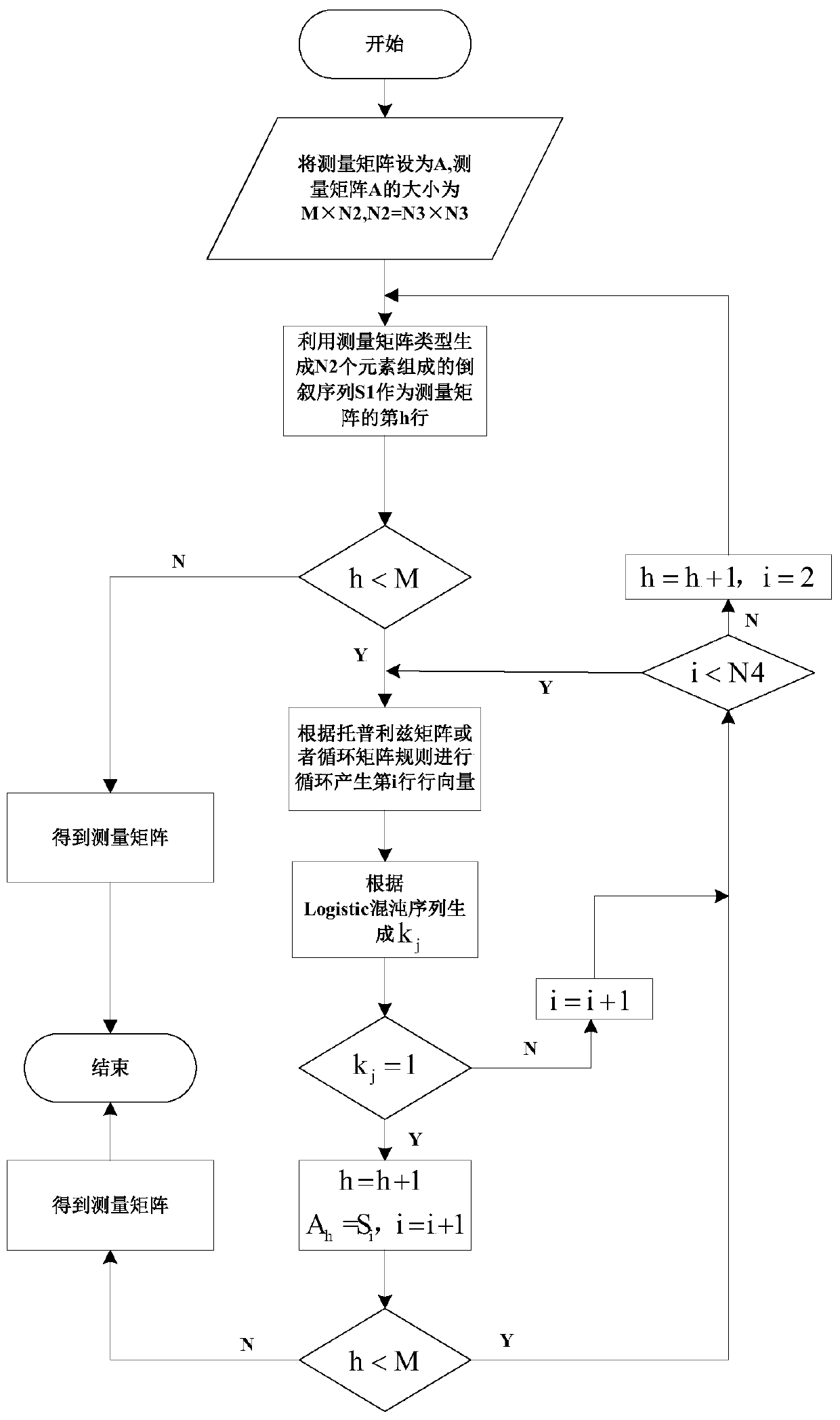

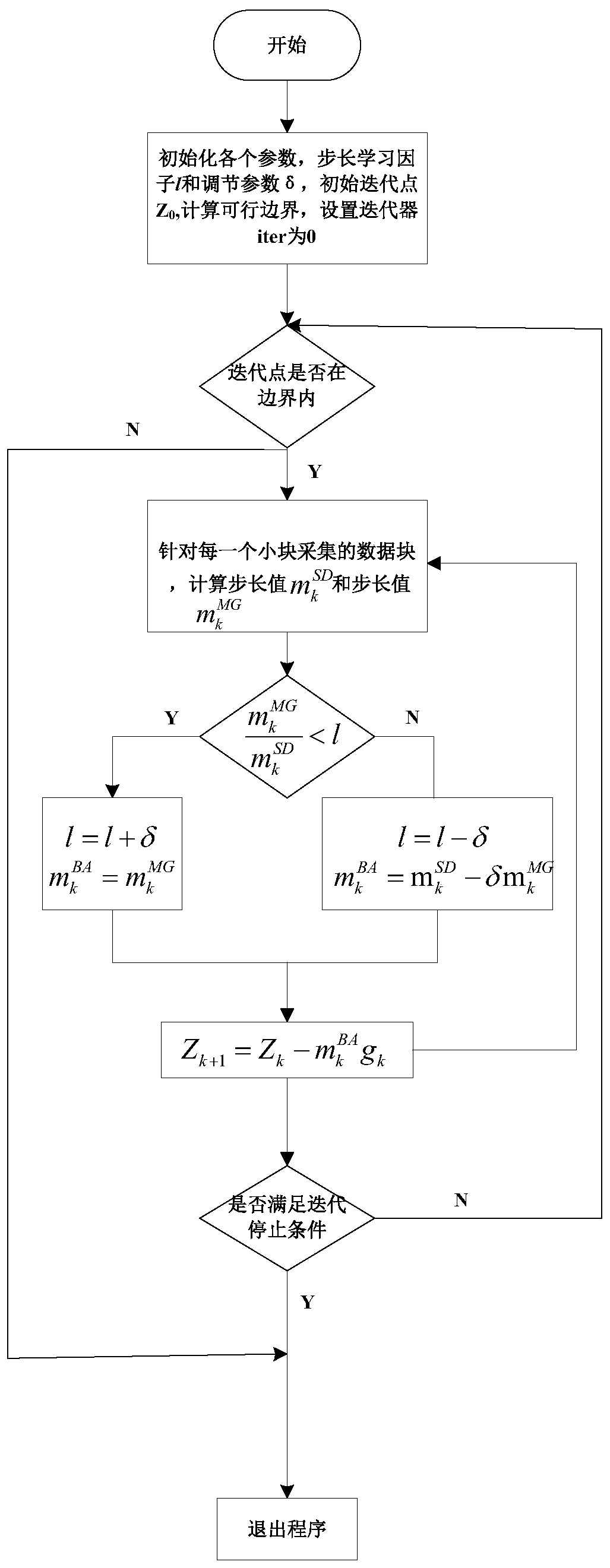

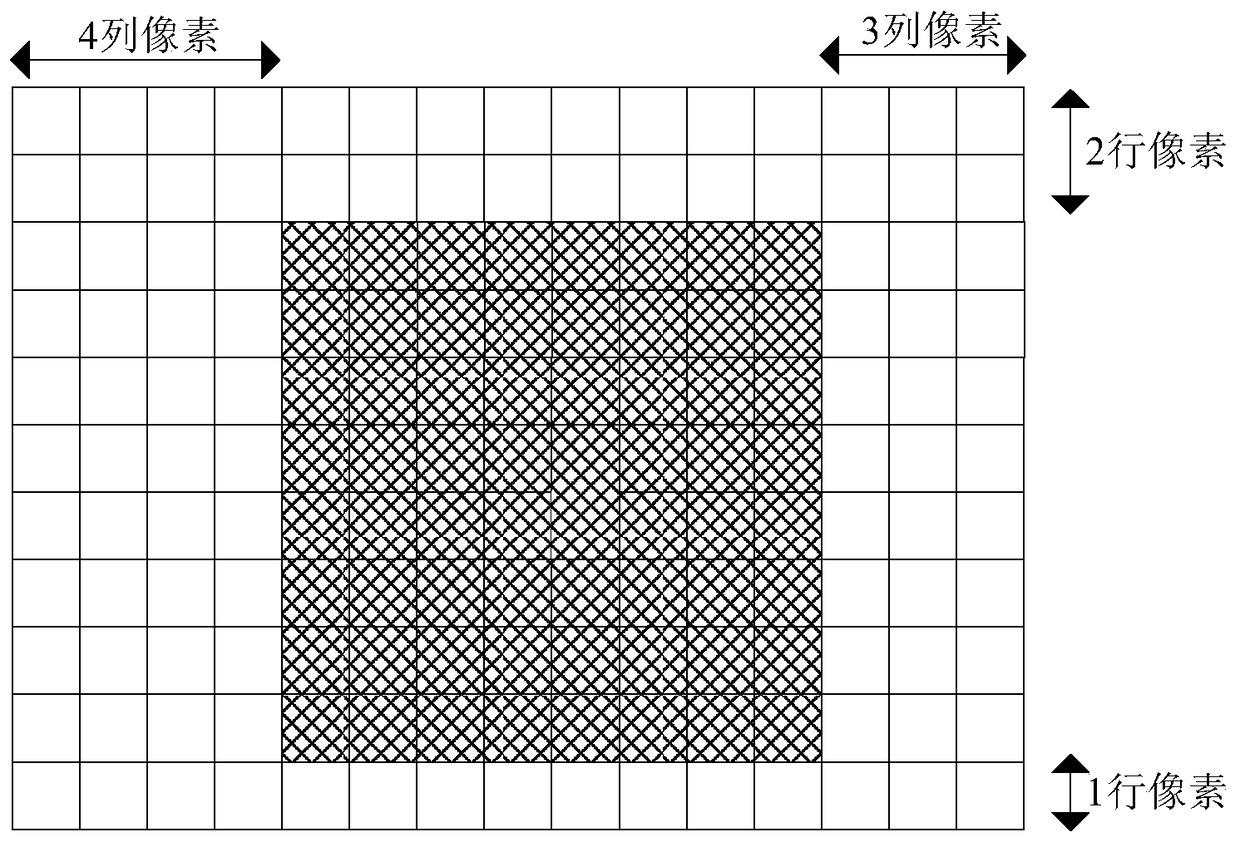

Color single-pixel imaging method and system based on random circulant matrix

ActiveCN108833919BLow costBreak dependenciesPicture reproducers using projection devicesDigital video signal modificationBeam splitterEngineering

The invention discloses a color single-pixel imaging method and system based on a random cyclic matrix. The imaging system includes DDR2 SDRAM installed on the Discovery 4100 development board, on-board FPGA, spatial modulator, signal acquisition and processing module, The signal recovery and reconstruction module, the optical path composed of lenses and beam splitters. This invention uses the measurement matrix to control the spatial modulator to encode the optical signal, adopts the method of "sampling while compressing" to process the data, and combines the advantages of fast decomposition rate and good real-time performance of the spectroscope to form a set of color single-pixel imaging The system solves the problems of signal transmission and storage caused by massive data in traditional imaging equipment. It uses the block adaptive step gradient projection recovery algorithm to greatly improve the image quality, and its resolution can reach 256*256.

Owner:NORTHEASTERN UNIV LIAONING

A Short Period Storage Method Based on ddr2 SDRAM

InactiveCN105528305BPersistent accessImprove access speedMemory architecture accessing/allocationMemory adressing/allocation/relocationDouble data rateMemory interface

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

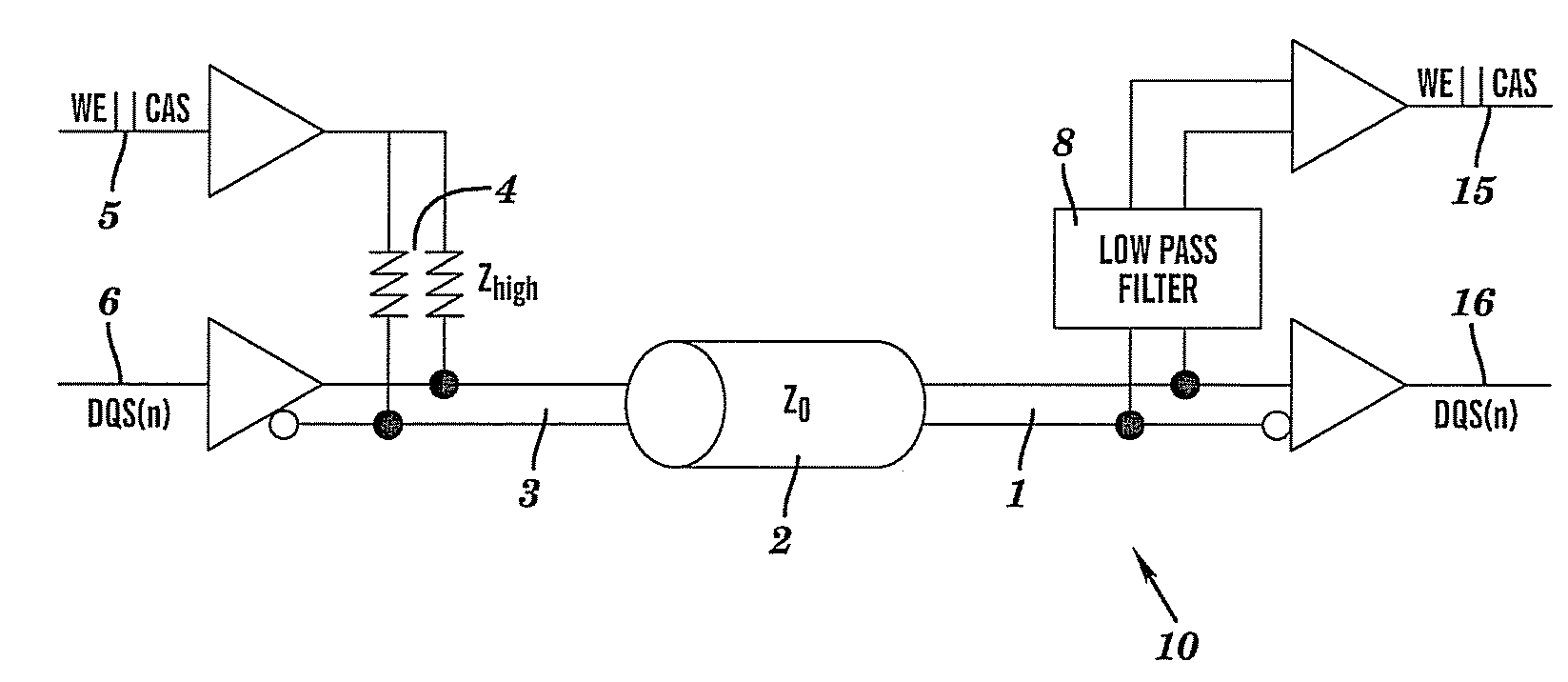

Using common mode differential data signals of DDR2 SDRAM for control signal transmission

A double-data-rate two synchronous dynamic random access (DDR2) memory circuit includes a low-speed input path and a high-speed input path coupled thereto by an input coupling and forming a common input, the common input coupled to a memory core, the memory core having a common output wherein a high-speed output path and a low-speed output path are coupled together by an output coupling and further coupled to the common output of the memory core.

Owner:META PLATFORMS INC

A ddr2-sdram controller and its low-latency optimization method

ActiveCN105045722BAvoid address dependenciesReduce the impact of memory access latencyMemory adressing/allocation/relocationRefresh cycleExternal storage

The invention discloses a DDR2-SDRAM controller and a corresponding low-delay optimization method for a high-performance RF automatic test platform. The DDR2-SDRAM controller is characterized in that, first, it does not regard the external storage module as a single resources, but according to the rank and bank structure of the DRAM module, the memory storage space is divided into several independent logical resources, each resource is private to a task with memory access requirements, and on this basis, the present invention designs corresponding Arbitration method and instruction sequence. The second is that it improves the refresh mechanism. The controller arranges a refresh cycle at the end of 60 memory access instruction cycles, and refreshes the specified row in the storage array through row access, which reduces the refresh time to zero and reduces memory access requests. The impact of conflicting with refresh requests on memory access latency. Ultimately, the maximum memory access latency performance of each task in the system is greatly improved.

Owner:SOUTHEAST UNIV

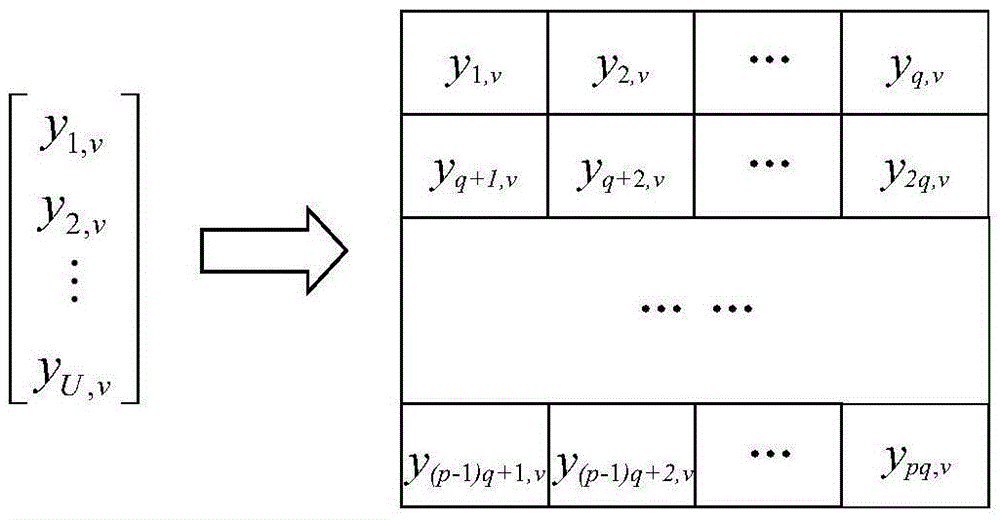

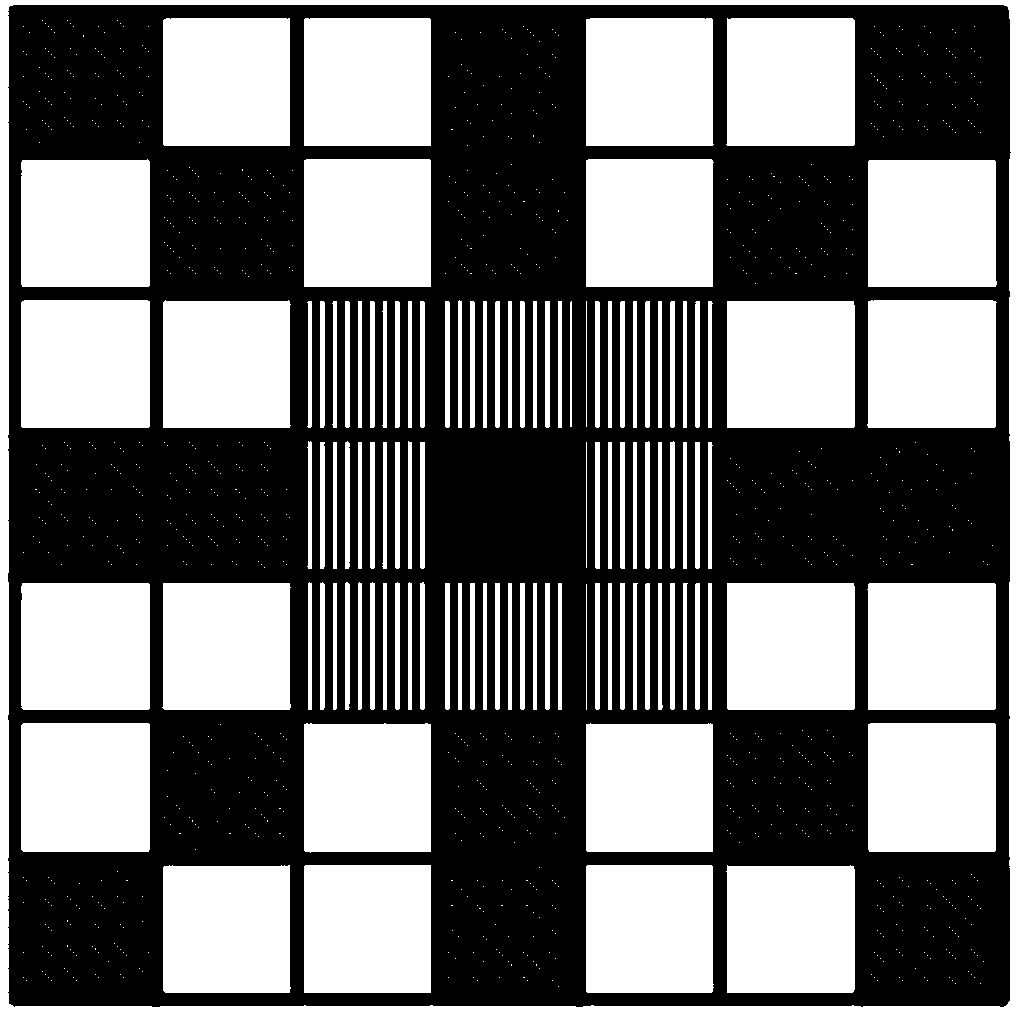

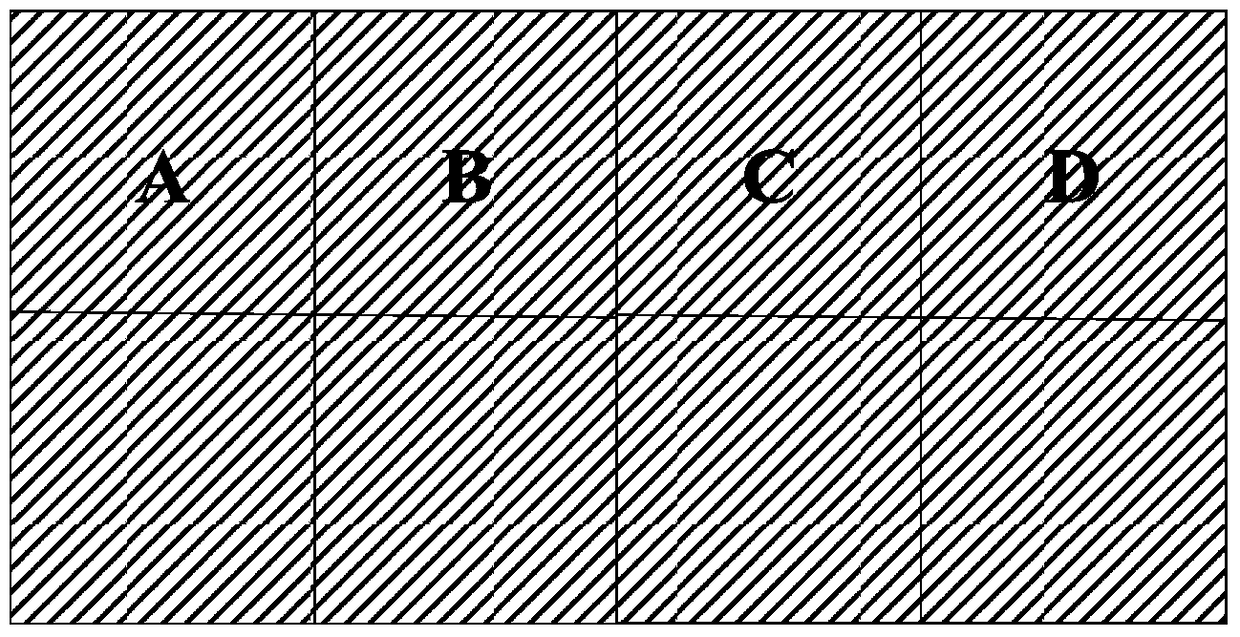

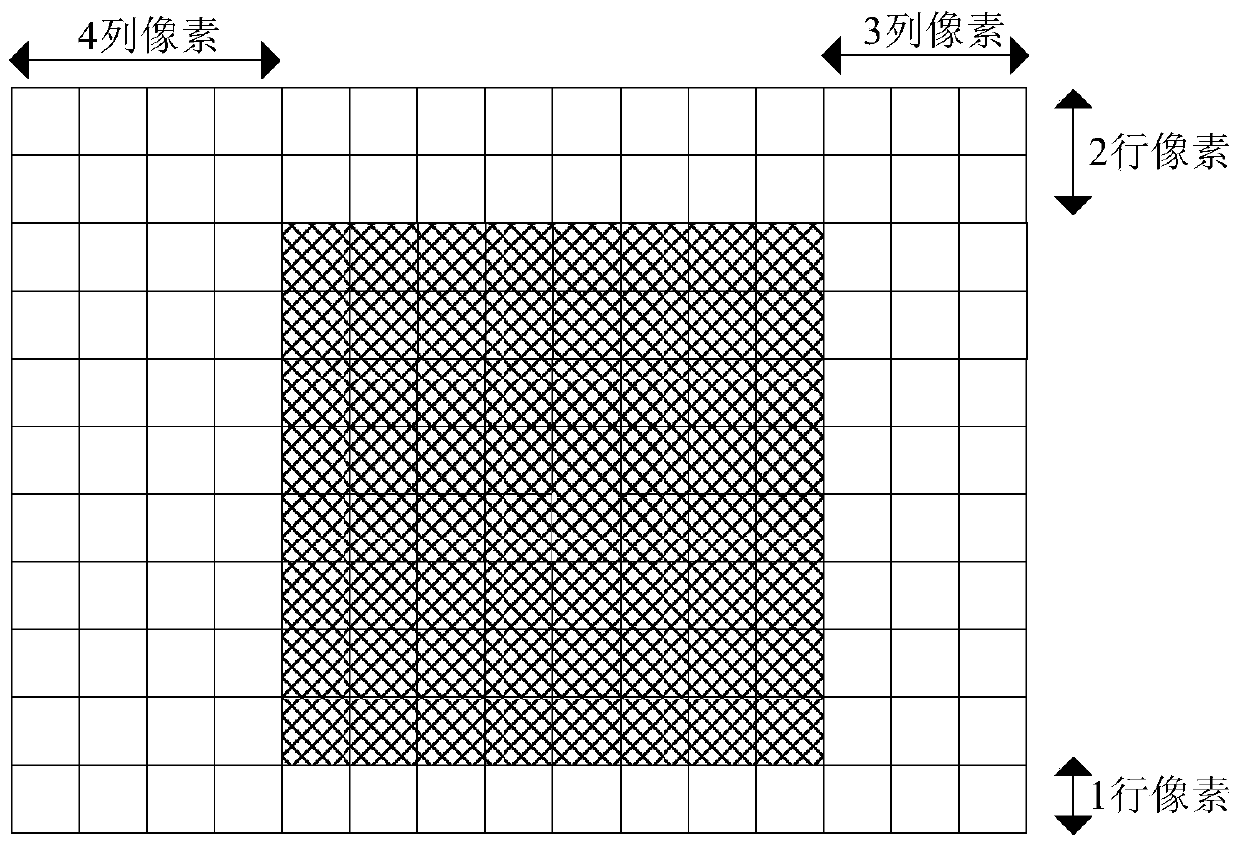

Data reading method for fine motion estimation based on Jiugongge

ActiveCN105516725BShorten read timeAvoid frequent visitsDigital video signal modificationHigh-definition videoDDR2 SDRAM

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

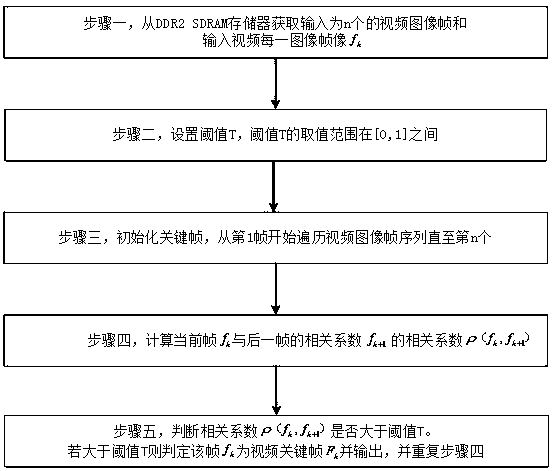

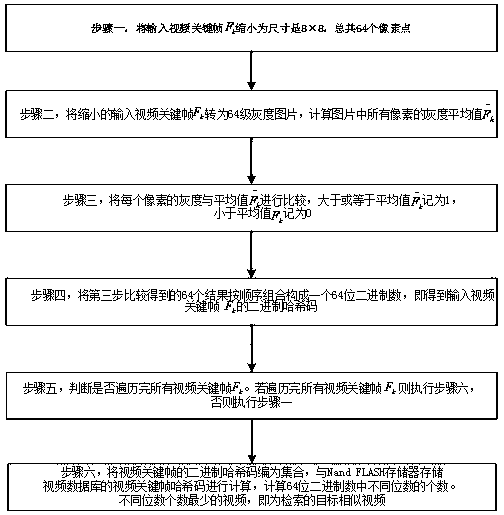

Similar video retrieval system based on frame correlation coefficient and perceptual hash

ActiveCN111078941AQuick extractionEfficient extractionDigital data information retrievalSpecial data processing applicationsVideo retrievalVideo storage

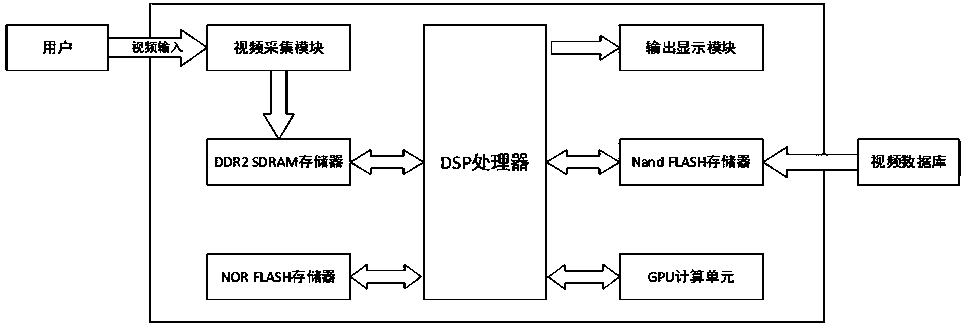

The invention relates to a similar video retrieval system based on a frame correlation coefficient and perceptual hash; a video acquisition module is connected with the DSP processor through the DDR2SDRAM memory, a video database is connected with the DSP processor through the Nand FLASH memory, and the DSP processor is connected with the NOR FLASH memory, the GPU computing unit and the output display module. The video acquisition module is used for receiving a video input by a user; the DDR2 SDRAM memory is used for caching the acquired video image frames and carrying out data conversion onthe video image frames; the NOR FLASH memory is used for storing the feature information extraction algorithm module and the matching retrieval algorithm module; the DSP processor is responsible for algorithm execution, the GPU computing unit is used for increasing the algorithm computing speed, the Nand FLASH memory is used for storing video feature information of a video database, and the outputdisplay module is used for displaying a matching retrieval result. According to the invention, the feature information of the input video can be rapidly extracted, the target similar video is retrieved, and the problems that a traditional manual retrieval mode consumes time and labor, the system precision is not high and the hardware degree is low are solved.

Owner:FUZHOU UNIV

Sudoku based fine motion estimation data reading method

ActiveCN105516725AShorten read timeAvoid frequent visitsDigital video signal modificationHigh-definition videoDDR2 SDRAM

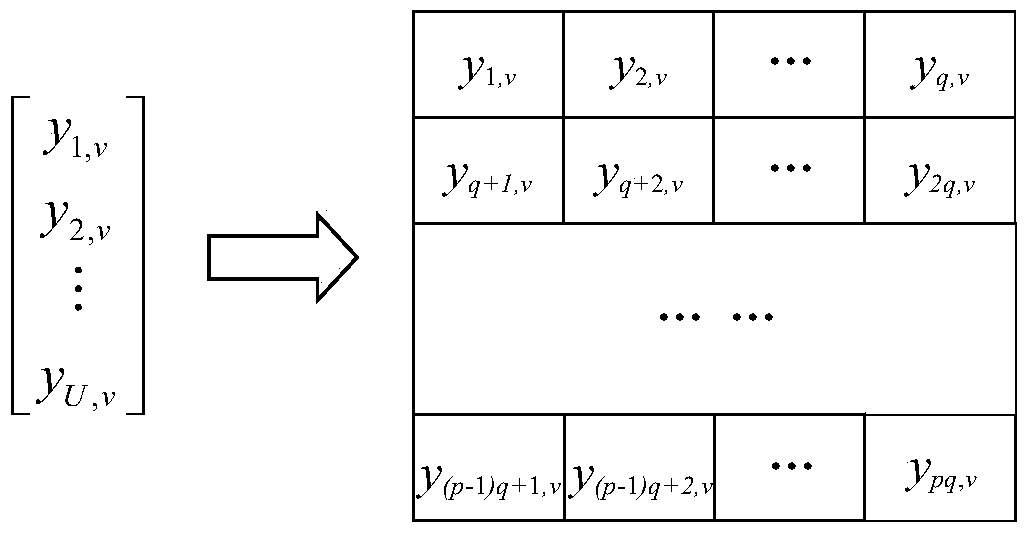

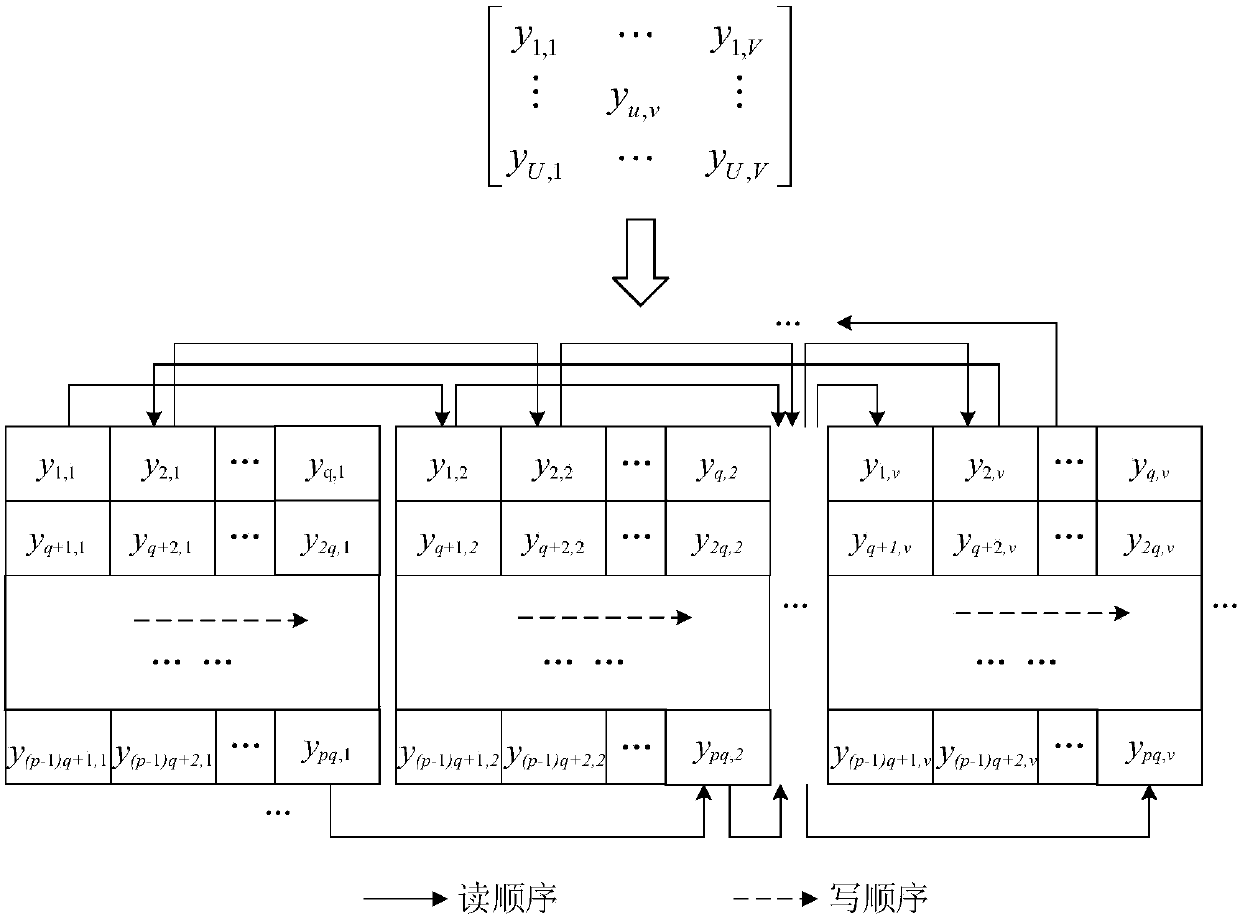

The invention relates to a Sudoku based fine motion estimation data reading method. When an H.264 high-definition video coding core carries out fine motion estimation, data in a search box are great in size and disordered, and relatively multiple cross-row operations are required, so the reading-writing efficiency is low, and a plenty of time is taken for writing the data into an off-chip DDR2 SDRAM. According to the invention, a macro-block reading method for visiting according to a fixed sequence is provided. As the visiting speed of fine motion is increased by adopting a method in which a Sudoku form is adopted for buffer-on-chip of data, an address prejudgment method, a redundancy data early termination method and the like, data of fine motion estimation can be taken back rapidly and exactly, and the speed required by high-definition real-time coding is realized.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

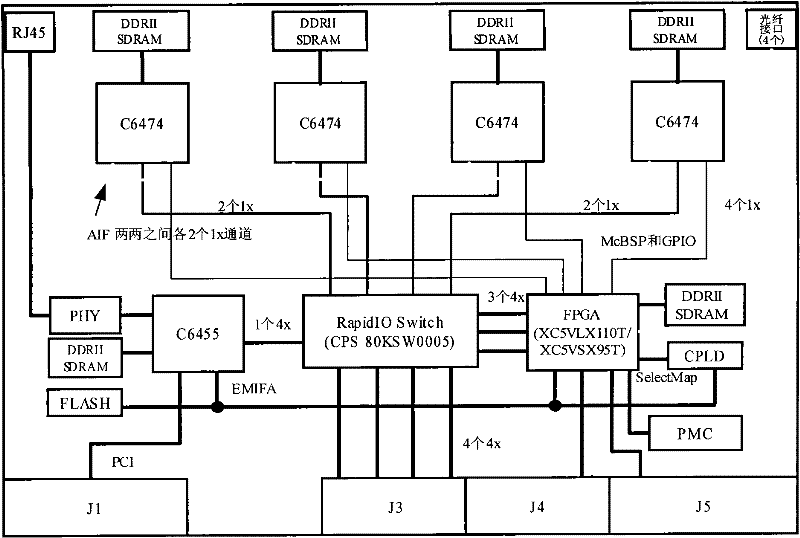

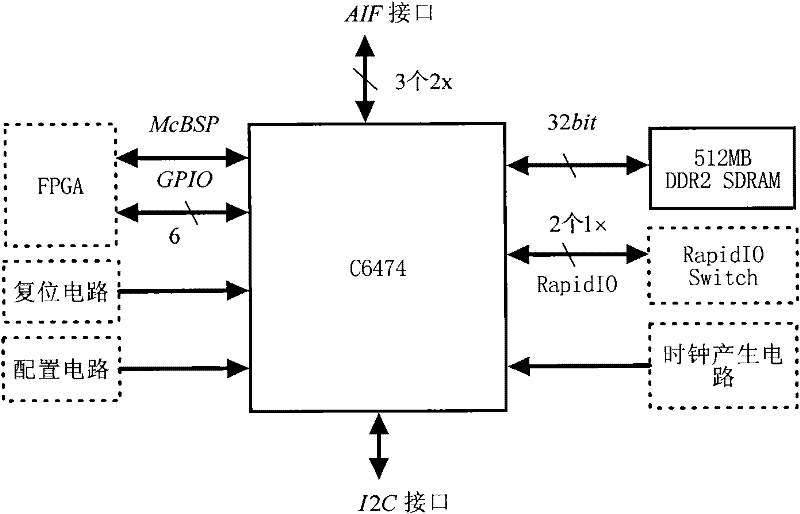

Switchboard based extensible DSPEED-DSP (Digital Signal Processor)_Q6474 signal processing board

InactiveCN101969378BLarge cache capacityEasy to manageData switching detailsInterface protocolBoard processor

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

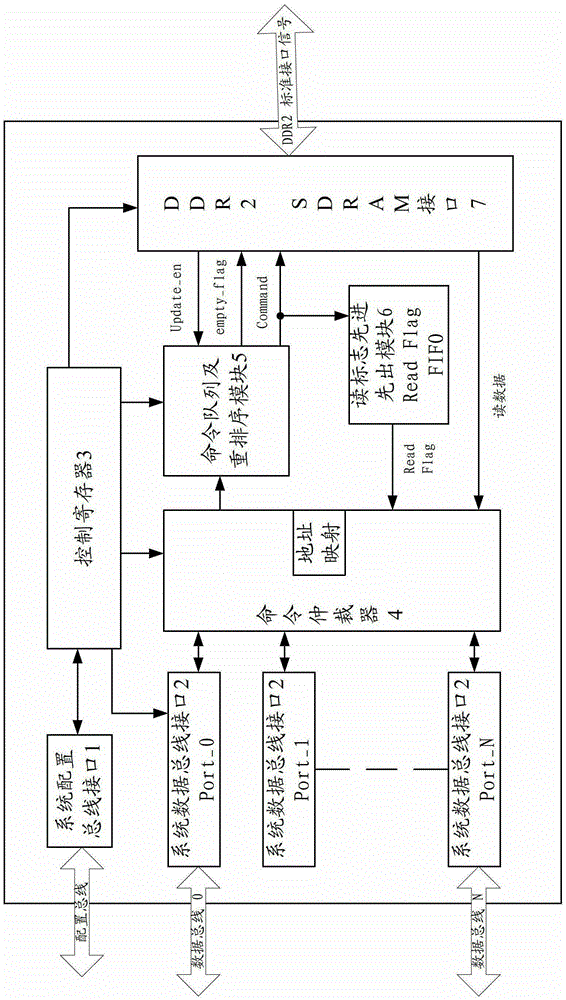

ddr2 SDRAM controller

ActiveCN103092785BIncrease profitRealize data transmissionElectric digital data processingDouble data rateInterface protocol

The invention relates to a double data rate (DDR) 2 synchronous dynamic random access memory (SDRAM) controller. Due to the fact that the DDR2SDRAM controller follows a DDR2SDRAM interface protocol, data transmission between the DDR2SDRAM controller and an outside DDR2SDRAM is achieved. The DDR2SDRAM controller comprises a DDR2SDRAM interface, a system data bus interface, an order arbiter and a command queuing and reordering module, wherein the DDR2SDRAM interface achieves various signals a DDR2SDRAM interface protocol definition; the system data bus interface achieves an interface function of the sides of system data buses and can be copied to meet requirements of the connection of a plurality of data buses; the order arbiter aims at requests of the plurality of data buses and enables only one route of data bus to visit the outside DDR2SDRAM within the same time; the command queuing and reordering module receives a reading / writing request command which is output by the order arbiter, the reading / writing request command is reordered according to relevancy of an address, and thereby the use ratio of the DDR2SDRAM interface is improved.

Owner:OMNIVISION TECH (SHANGHAI) CO LTD

Embedded infrared real-time signal processing system

InactiveCN102156588BFlexible configurationImprove portabilityInput/output processes for data processingHardware structureDouble data rate

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI