Field programmable gate array (FPGA) and digital signal processor (DSP) data transmission system based on Ping Pong mechanism

A technology of data transmission system and ping-pong mechanism, which is applied in data conversion, electrical digital data processing, instruments, etc., can solve problems such as low efficiency and difficulty in adapting to high-speed data transmission requirements, so as to improve system performance, save waiting time, and improve data quality. The effect of transmission efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The specific embodiments of the present invention will be further described below with reference to the drawings and examples.

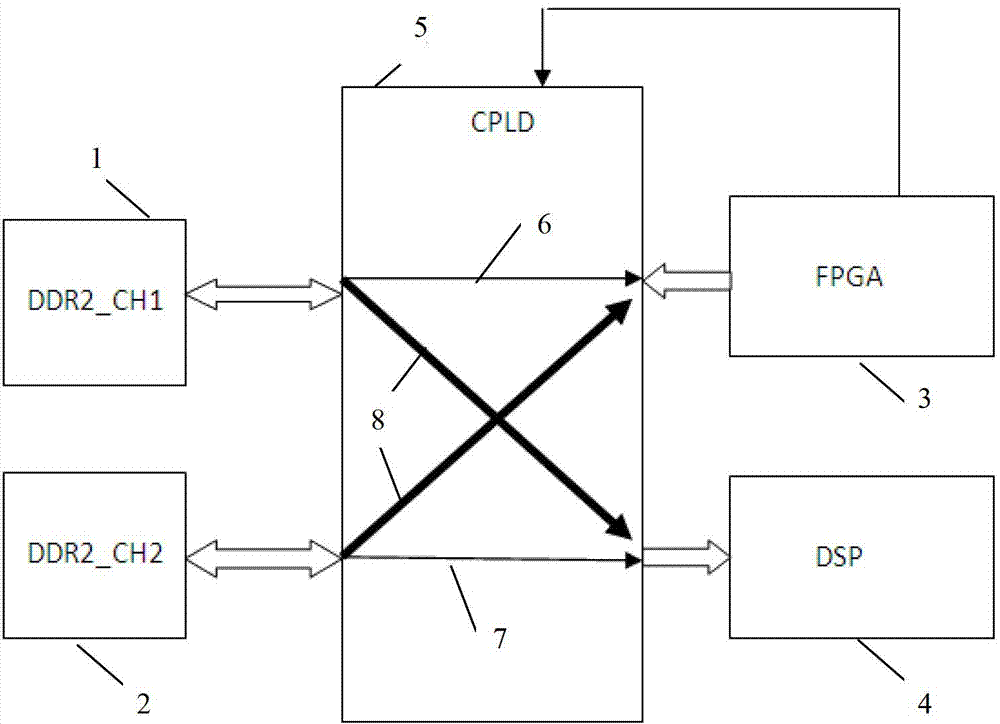

[0015] The FPGA and DSP data transmission system based on the ping-pong mechanism of the present invention includes a dual-channel switch, FPGA, DSP and two memories. In this example, the dual-channel switch is implemented using CPLD, and the memory uses the second-generation double-rate synchronous dynamic random access memory DDR2 SDRAM.

[0016] in figure 1 In the design of dual-channel DDR2 SDRAM, the ping-pong mechanism is adopted. That is, when FPGA 3 writes data to one DDR2 SDRAM 1, DSP 4 reads data from another DDR2 SDRAM 2. Then CPLD 5 controls the switching of the control rights of DDR2 SDRAM 1 and 2 between FPGA 3 and DSP 4. Since DDR2 SDRAM 1 and 2 are single-port devices (only one set of buses), the switching device CPLD is used as a switch between two DDR2 SDRAM 1 and 2 to achieve the "multiplexing" function.

[0017] DDR2_CH1 and D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More