Patents

Literature

38results about How to "Reduce time skew" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

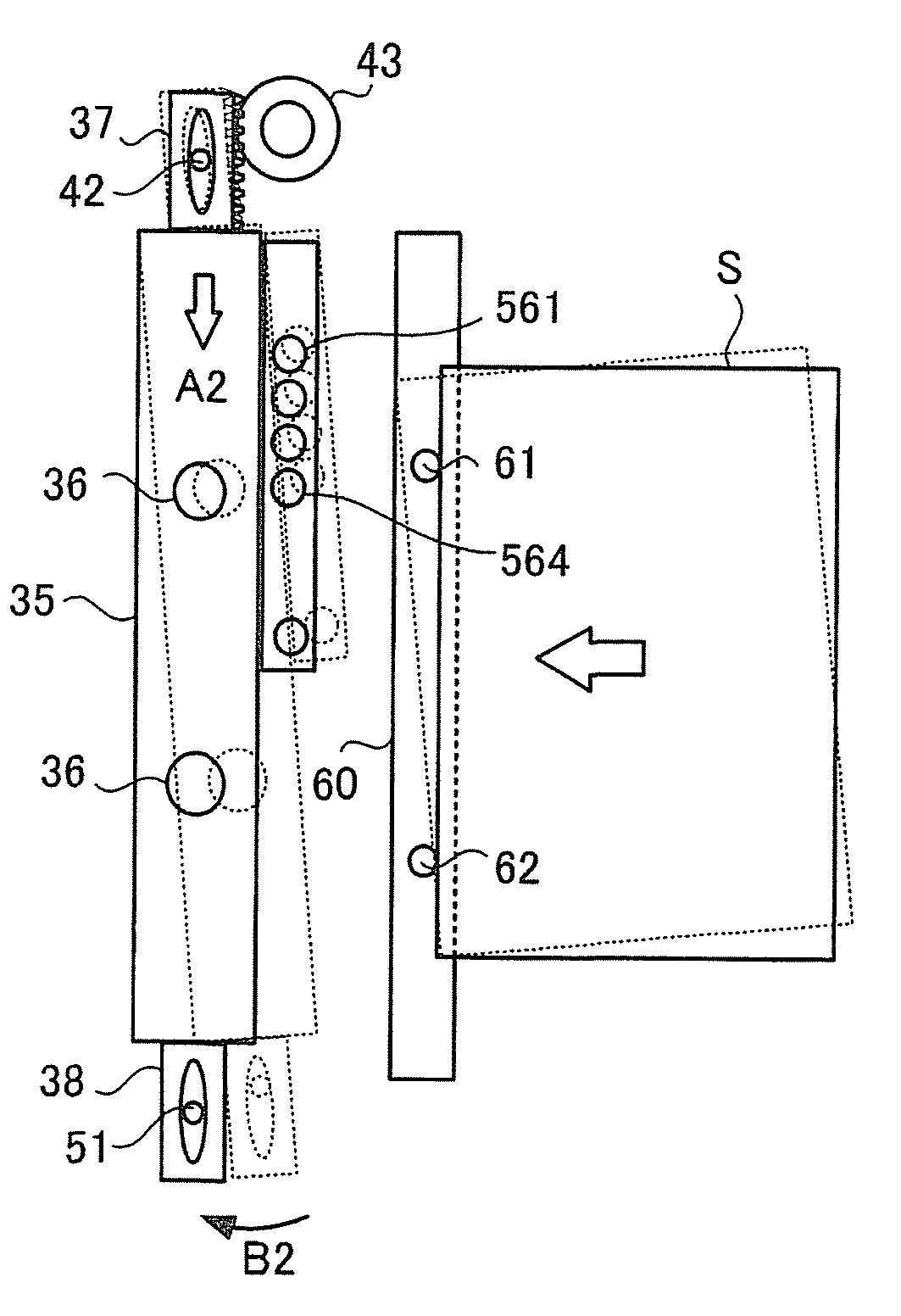

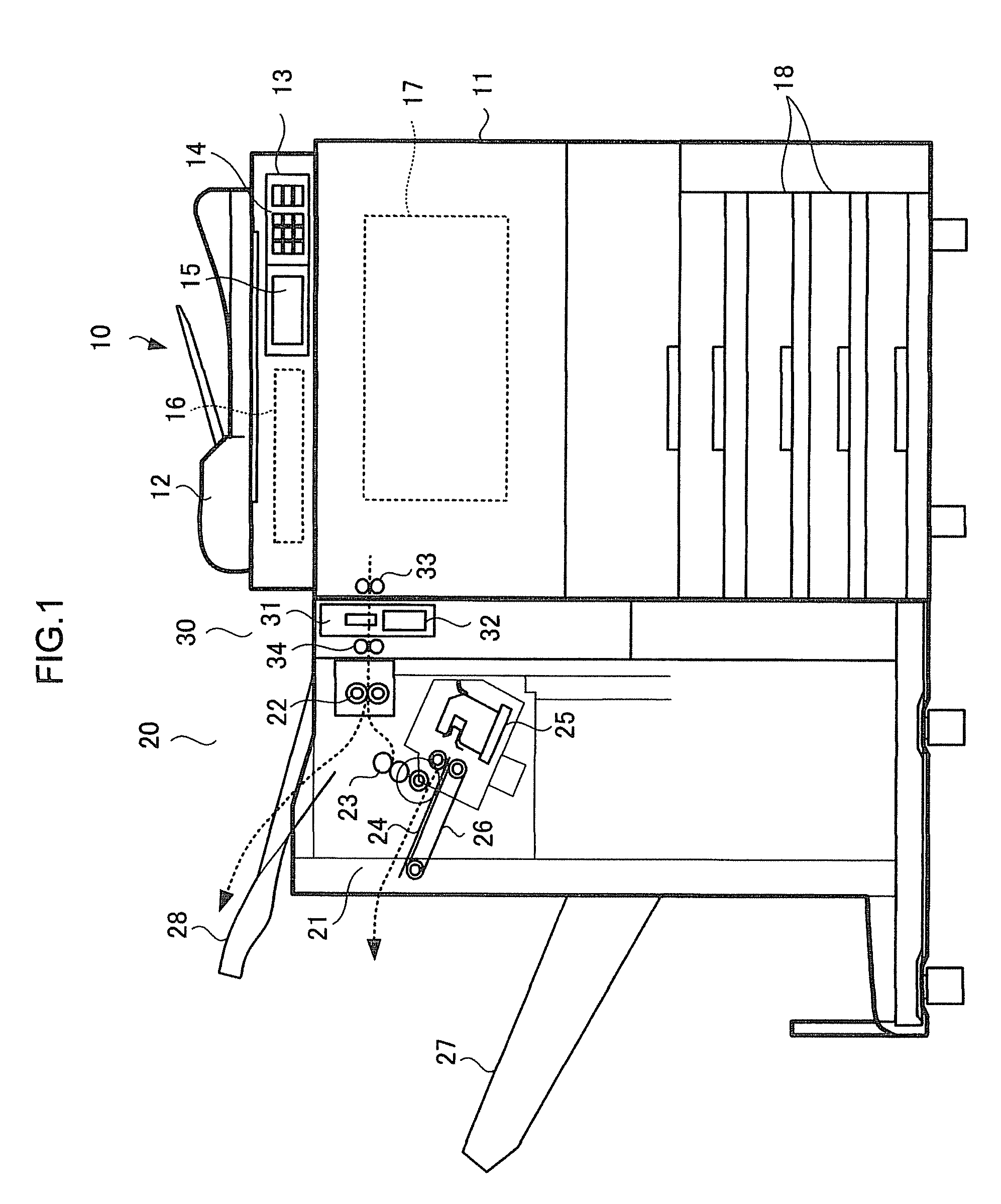

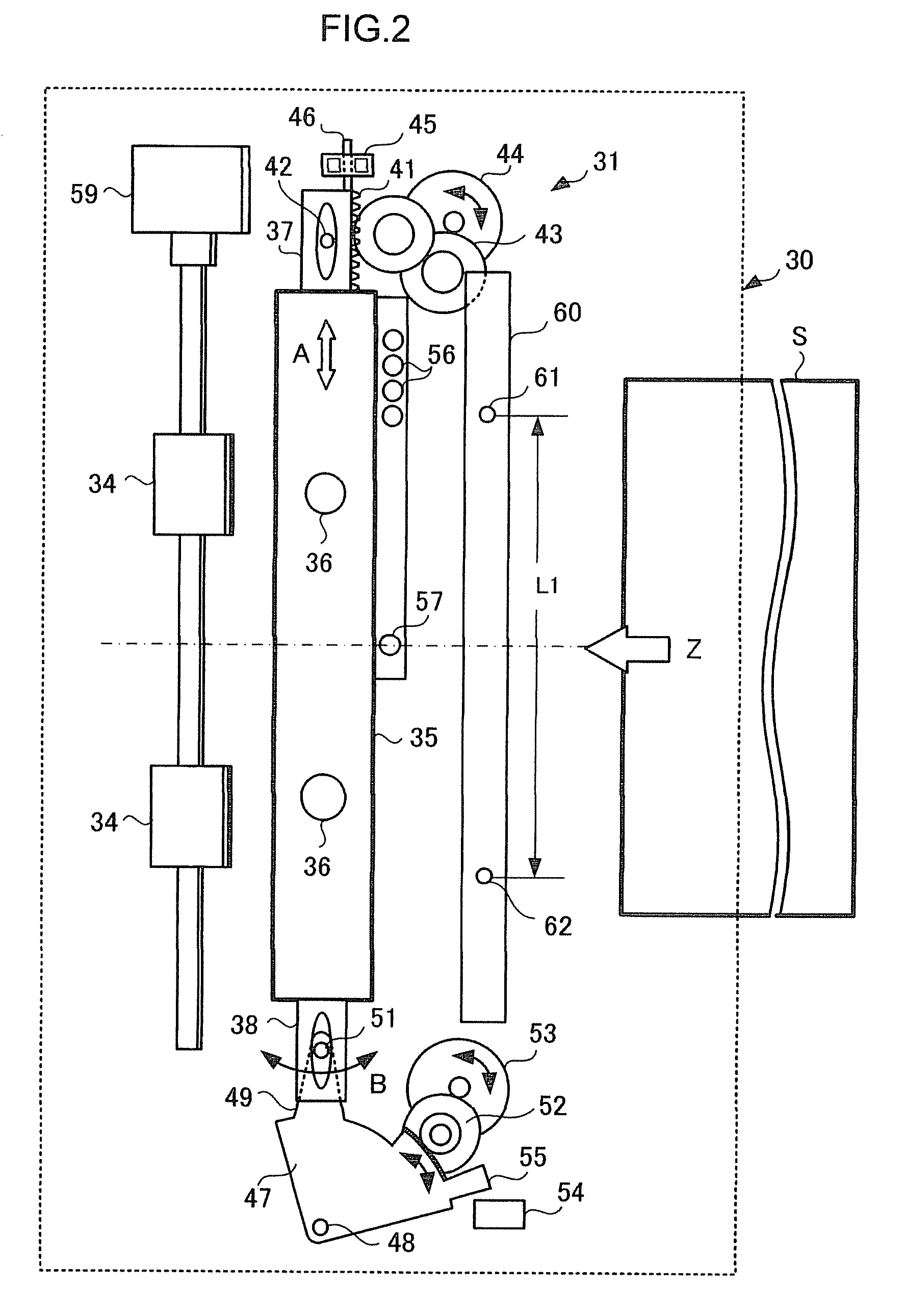

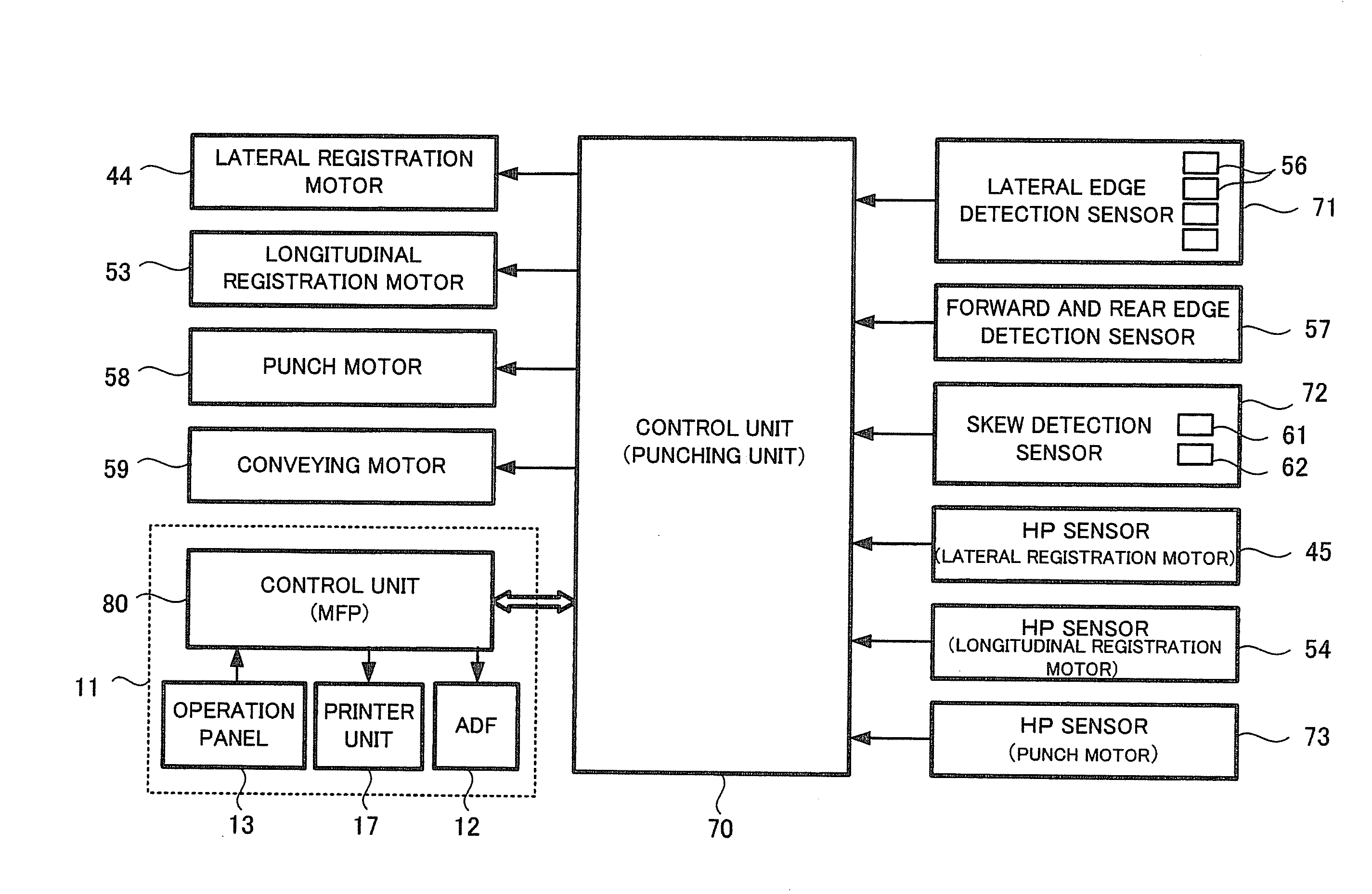

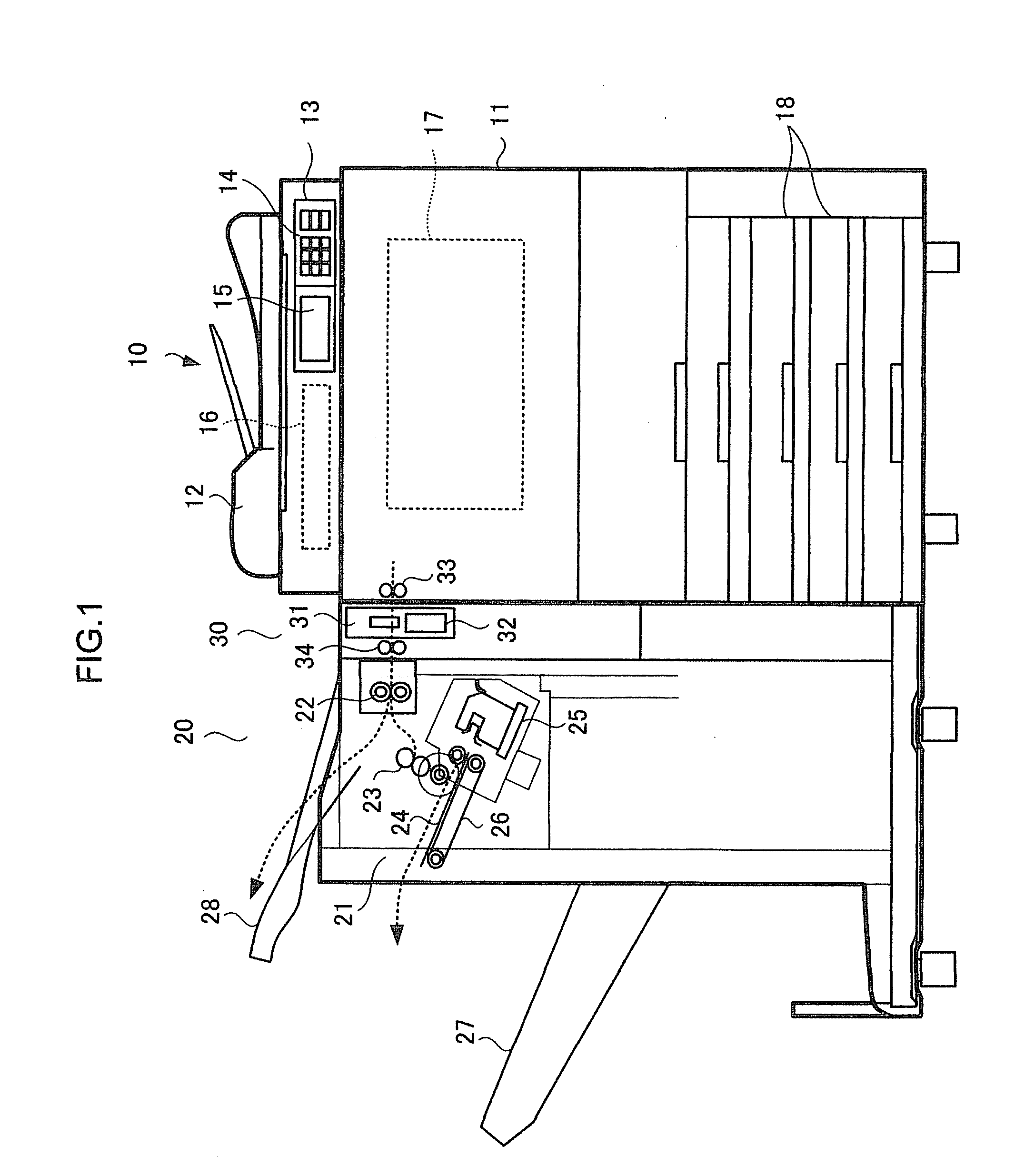

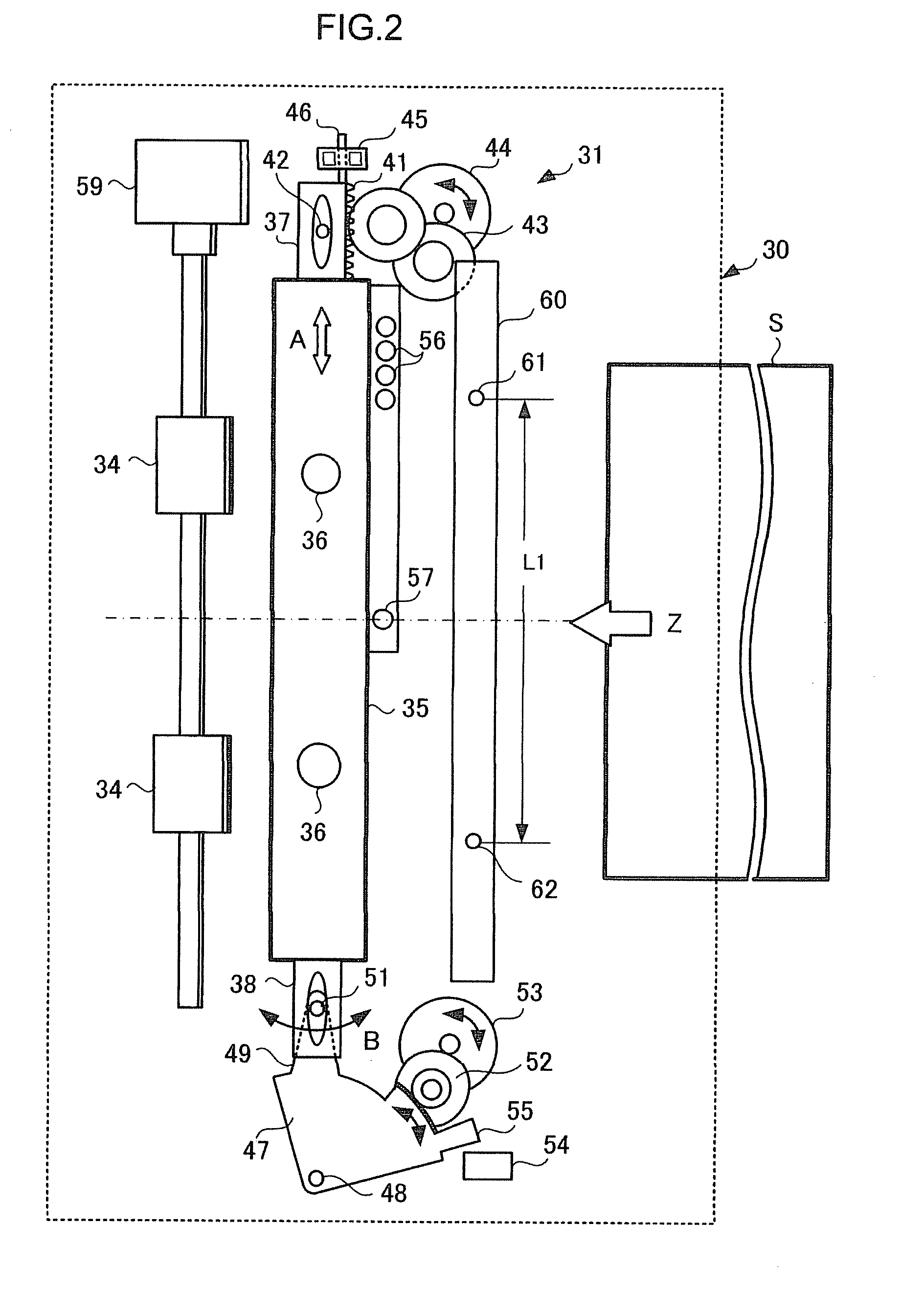

Sheet processing apparatus and sheet processing method

ActiveUS7578498B2Accurately carry-outReduce time skewFunction indicatorsElectrographic process apparatusControl theoryControl unit

A sheet processing apparatus includes a hole punching section arranged downstream from a skew detecting unit and orthogonally to a conveying path of a sheet, and a control unit configured to change the tilt angle of the hole punching section in accordance with each of the quantity of skew at the forward edge and the quantity of skew at the rear edge of the sheet, carry out skew correction at the forward edge within a first correction range w1, and carry out skew correction at the rear edge within a second correction range w2 (where w1>w2≧w1 / 2). The control unit carries out skew correction at the forward edge within the correction range w2, in the case where the detected quantity of skew at the forward edge is a tilt angle exceeding the correction range w2, and then carries out skew correction at the rear edge in accordance with the difference between the quantity of skew at the forward edge after the correction and the quantity of skew at the rear edge.

Owner:KK TOSHIBA +1

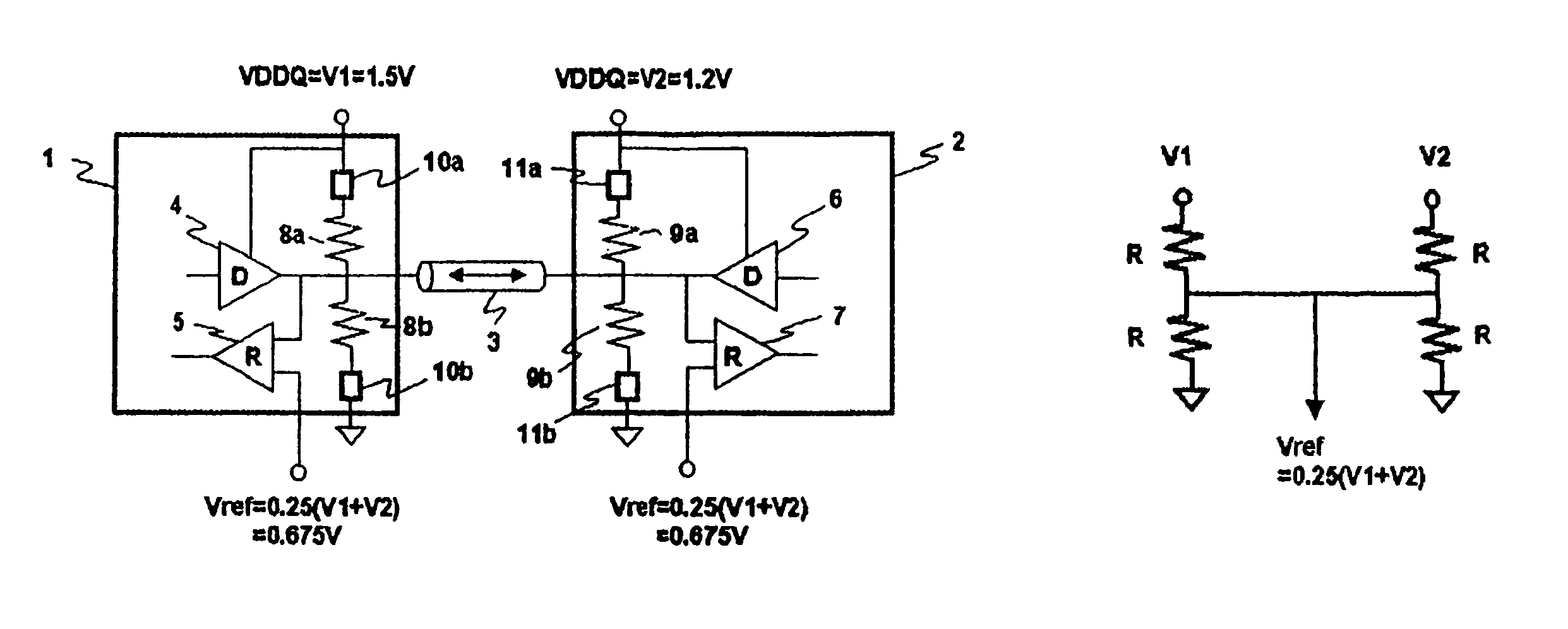

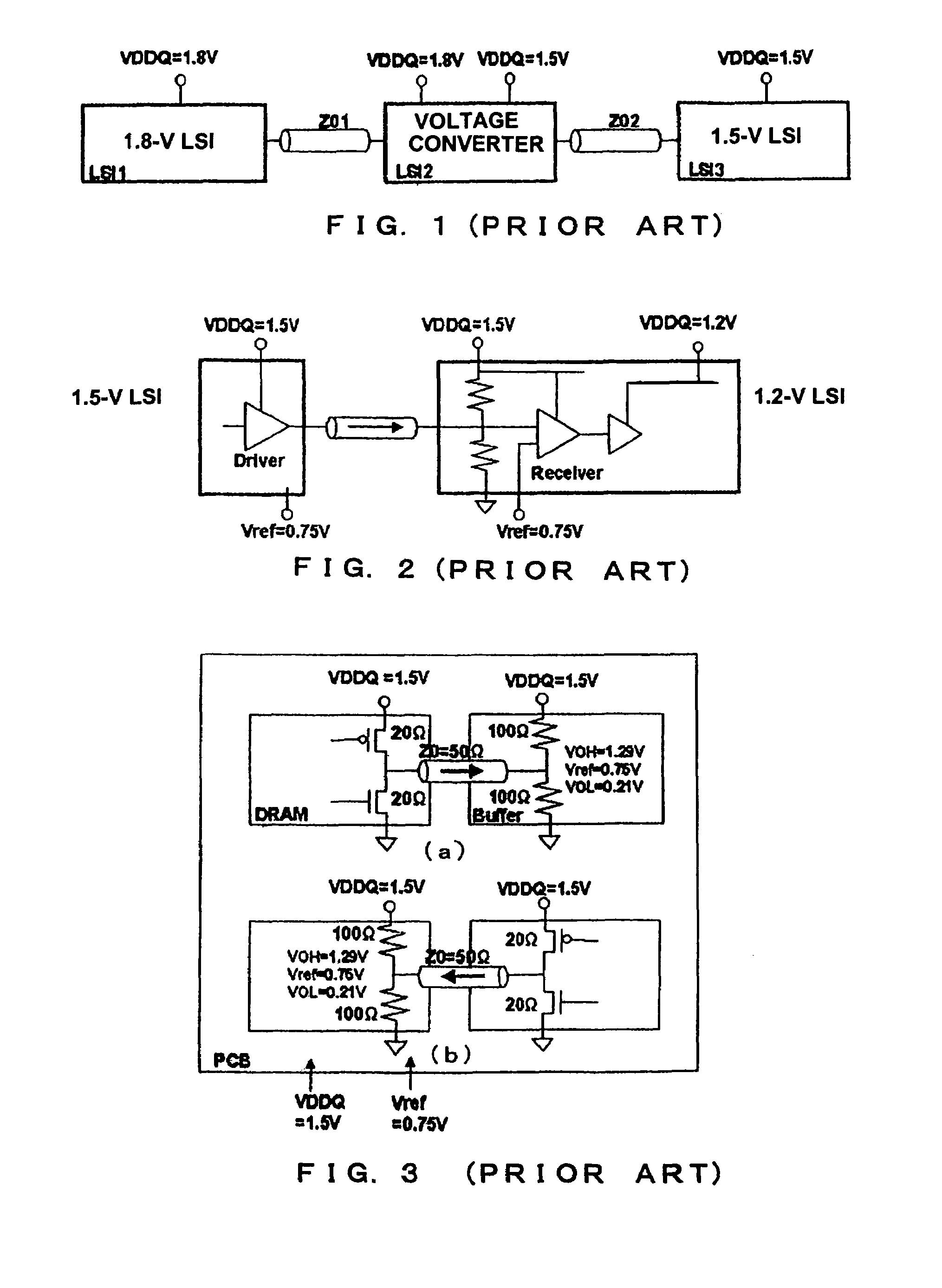

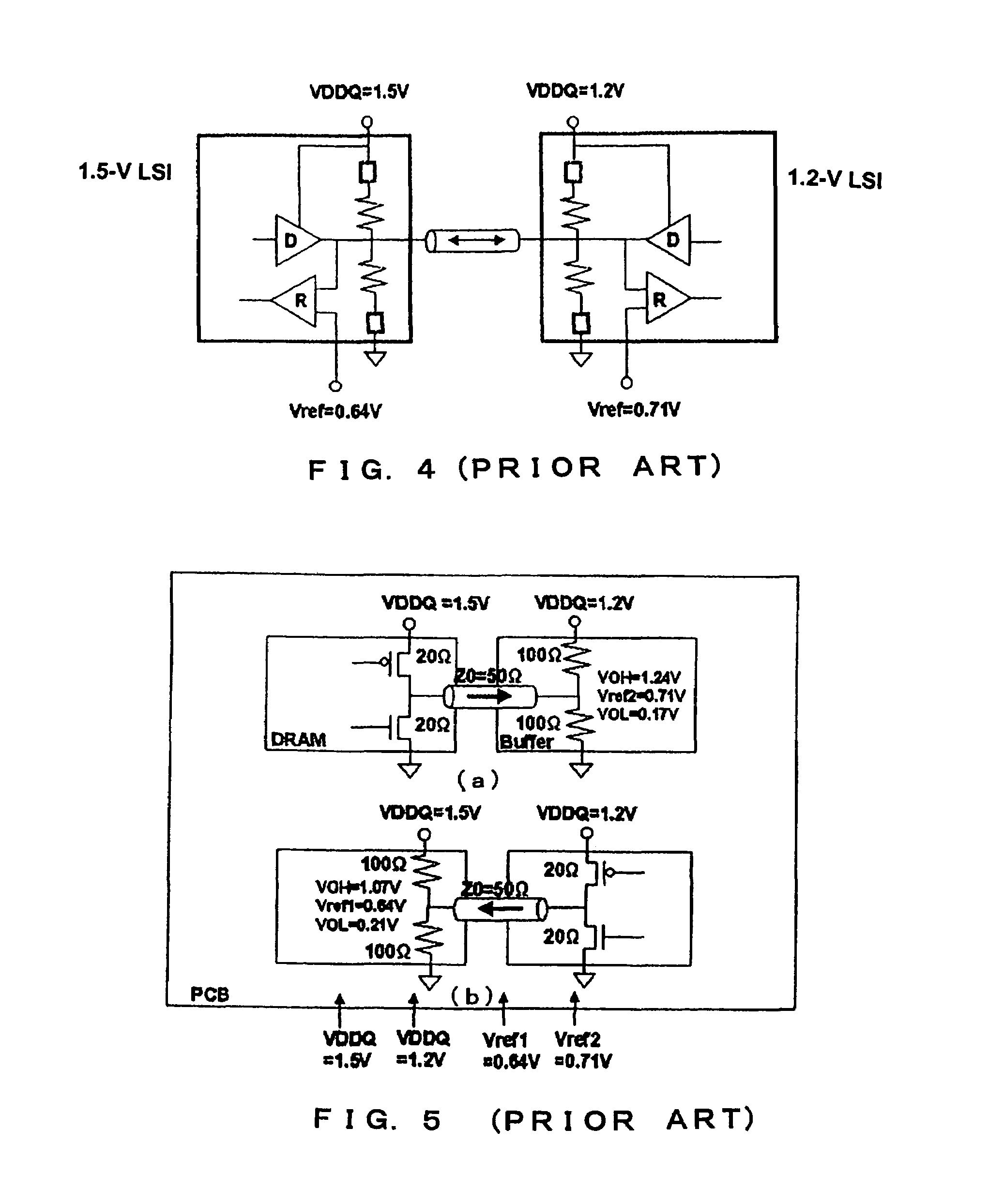

Signal transmitting system

InactiveUS6985009B2Suppresses timing skewLow costReliability increasing modificationsElectronic switchingElectrical resistance and conductancePush pull

Semiconductor integrated circuit devices that operate under different power supply voltages are directly interconnected by a bidirectional bus which is a transmission line. A driver is of a push-pull type and a reception side is CTT-terminated. If a terminating resistor is in conformity with the characteristic impedance of the transmission line, the on resistance of the driver is equal to or lower than the characteristic impedance. If the on resistance of the driver is in conformity with the characteristic impedance of the transmission line, the value of the terminating resistor is equal to or lower than the characteristic impedance of the transmission line. If the reception side is VTT-terminated, the value of the VTT is ½ of a lower one of power supply voltages that are supplied to the respective semiconductor integrated circuit devices. The value of the terminating resistor is in conformity with the characteristic impedance of the transmission line. The semiconductor integrated circuit devices use a common reference voltage for determining the signal voltage.

Owner:LONGITUDE SEMICON S A R L

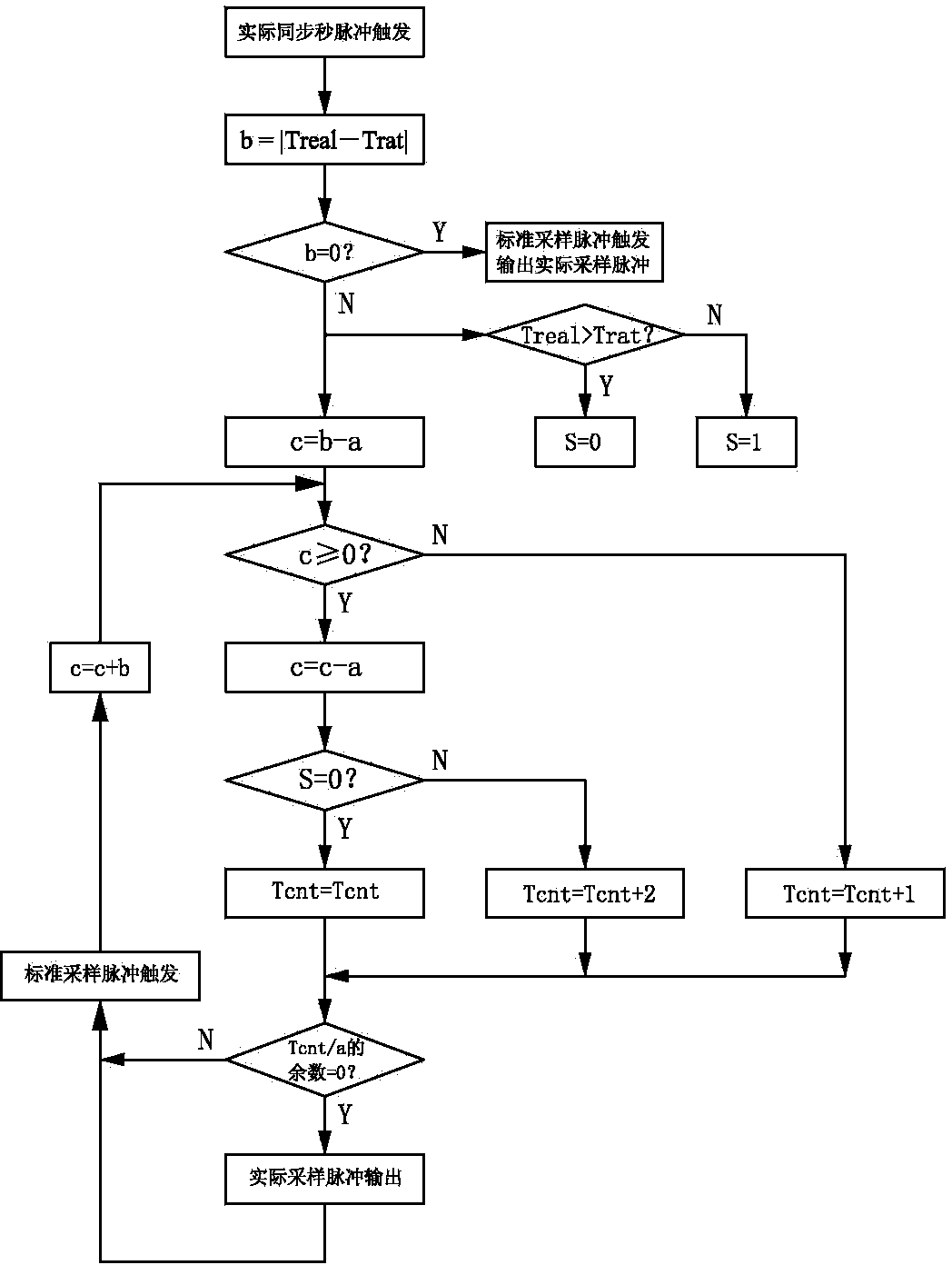

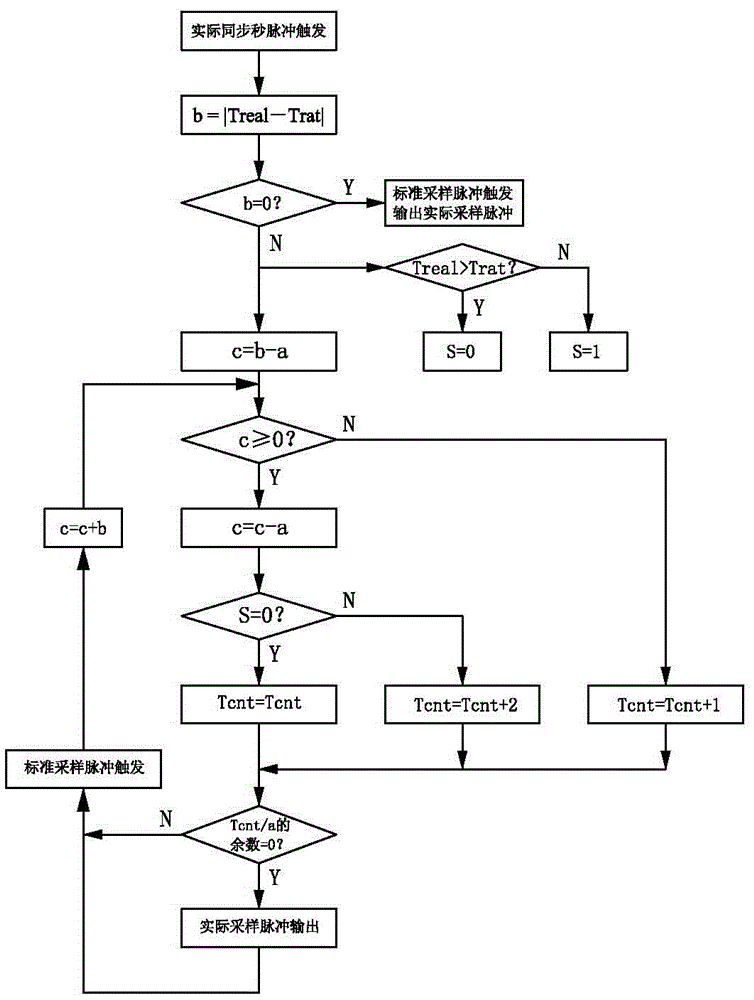

Method for adopting high-accuracy pulse per second frequency multiplication to produce sampling pulse based on FPGA

ActiveCN103941622AReduce time skewHigh speedProgramme controlComputer controlElectric power systemDependability

The invention discloses a method for adopting high-accuracy pulse per second frequency multiplication to produce sampling pulses based on an FPGA in the technical field of electric power system measurement and control and aims at solving the technical problem that sampling pulses provided by an oscillator in the prior art enable the sampling accuracy to be low. In the method, an actual synchronous pulse per second counting value is compared with an ideal synchronous pulse per second counting value, deviations and sampling frequencies are subjected to accumulation calculation, the correction situation of a pulse counter is judged according to an accumulation calculation result, accordingly total deviations of actual synchronous pulses per second are averagely distributed in actual sampling pulses, sampling pulse errors are remarkably decreased, and reliable and stable sampling pulse signals are provided for analog-digital signal acquisition. In addition, the method is simple and easy to operate, occupied FPGA chip resources are decreased, and the running speed and reliability of the FPGA are improved.

Owner:STATE GRID CORP OF CHINA +4

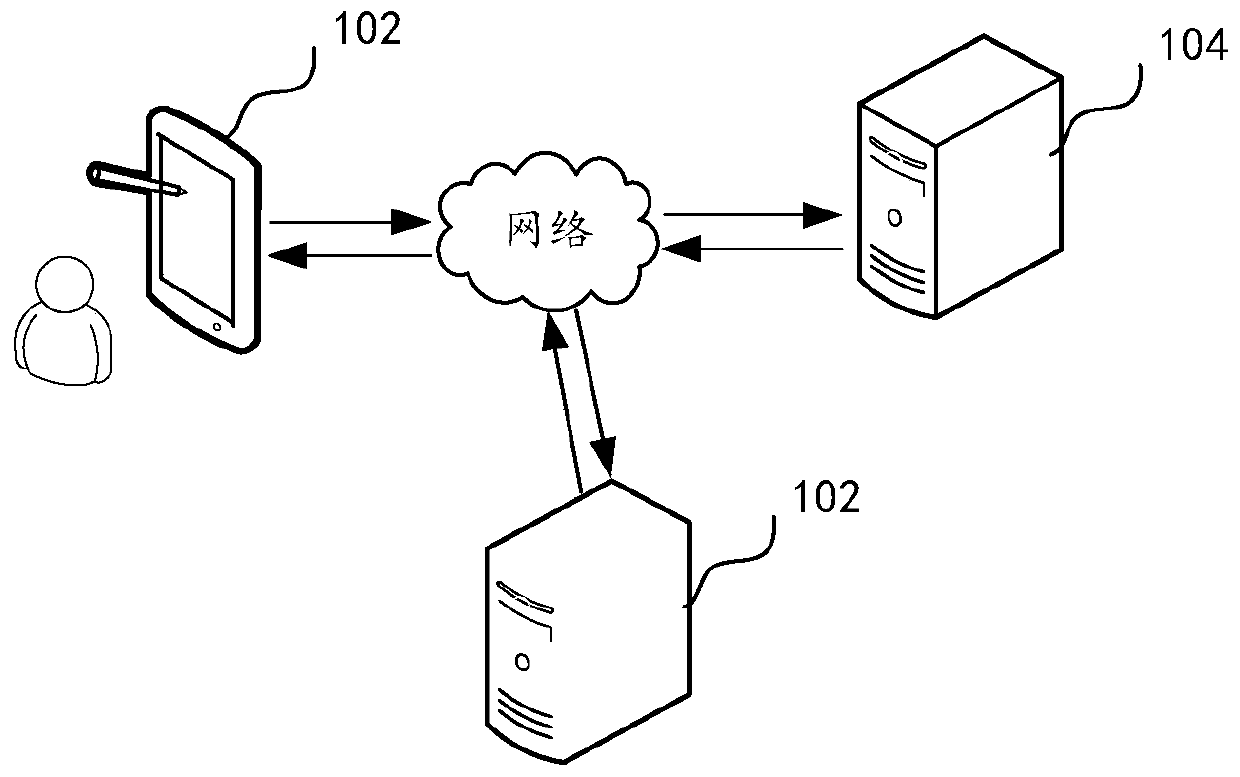

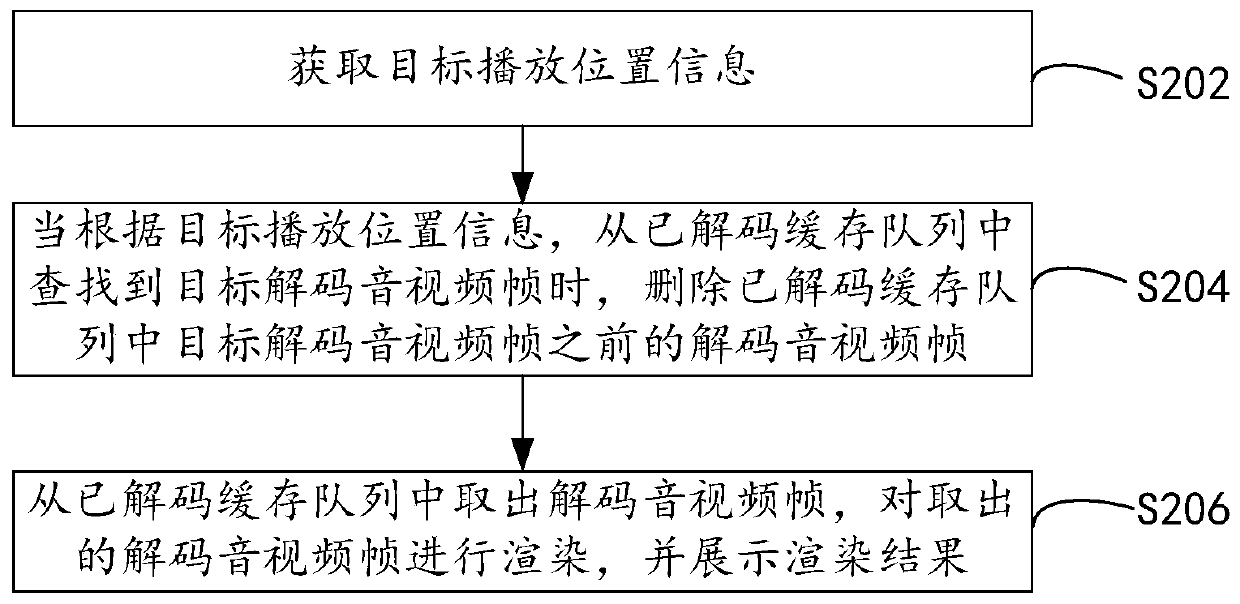

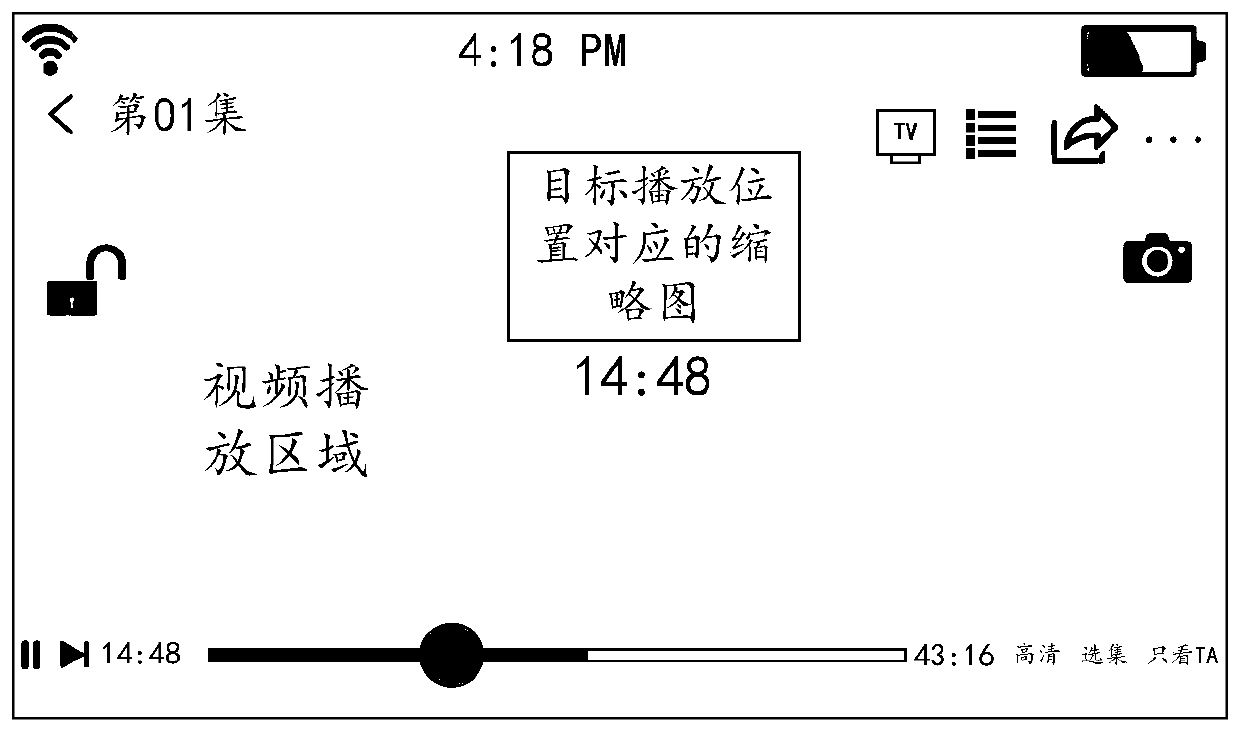

Audio and video playing method and device, computer equipment and storage medium

ActiveCN110418186AReduce time skewSelective content distributionTime deviationComputer graphics (images)

The invention relates to an audio and video playing method and device, a computer device and a storage medium. The method comprises the steps of obtaining target playing position information; when a target decoded audio and video frame is found from a decoded cache queue according to the target playing position information, deleting the decoded audio and video frame before the target decoded audioand video frame in the decoded cache queue; and taking out the decoded audio and video frames in the decoded cache queue, rendering the taken-out decoded audio and video frames, and displaying a rendering result. Since rendering playing can be started from the position of the target decoded audio and video frame corresponding to the target playing position information in the decoded cache queue,the time deviation between the actual playing position and the target playing position can be reduced.

Owner:TENCENT TECH (SHENZHEN) CO LTD

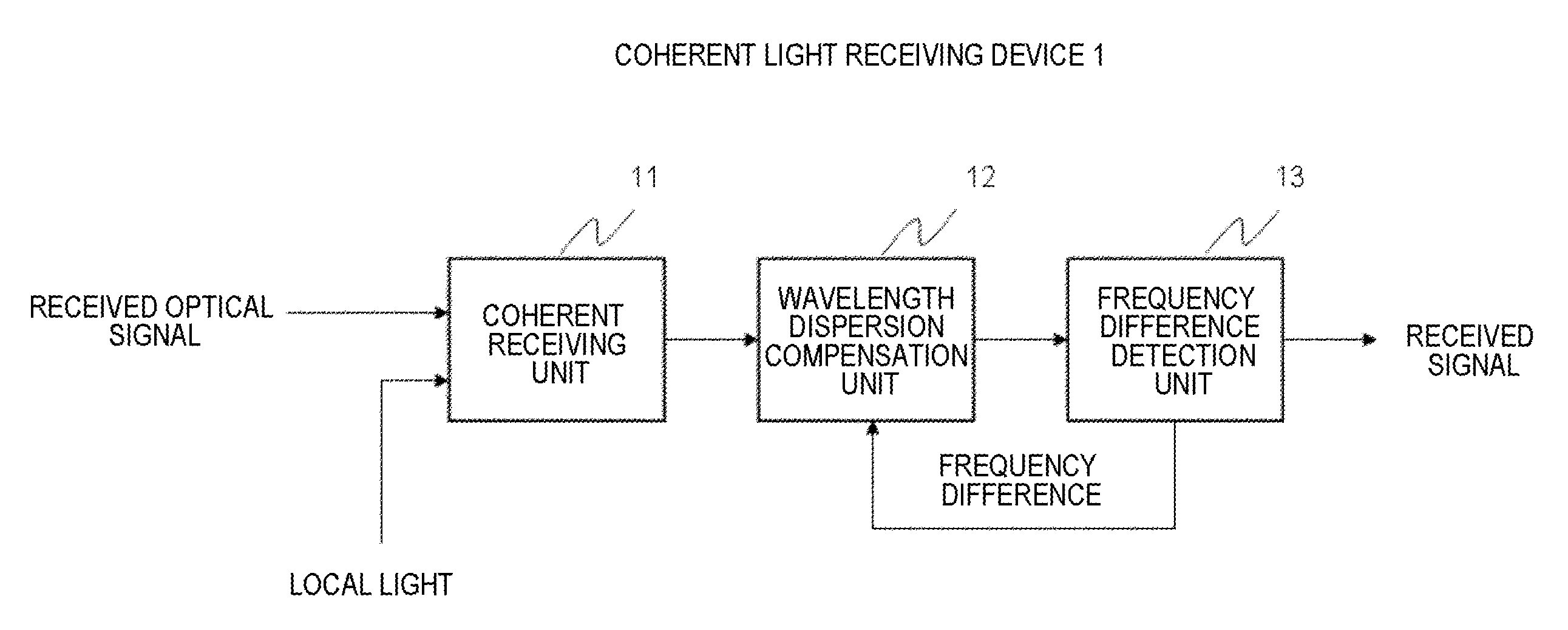

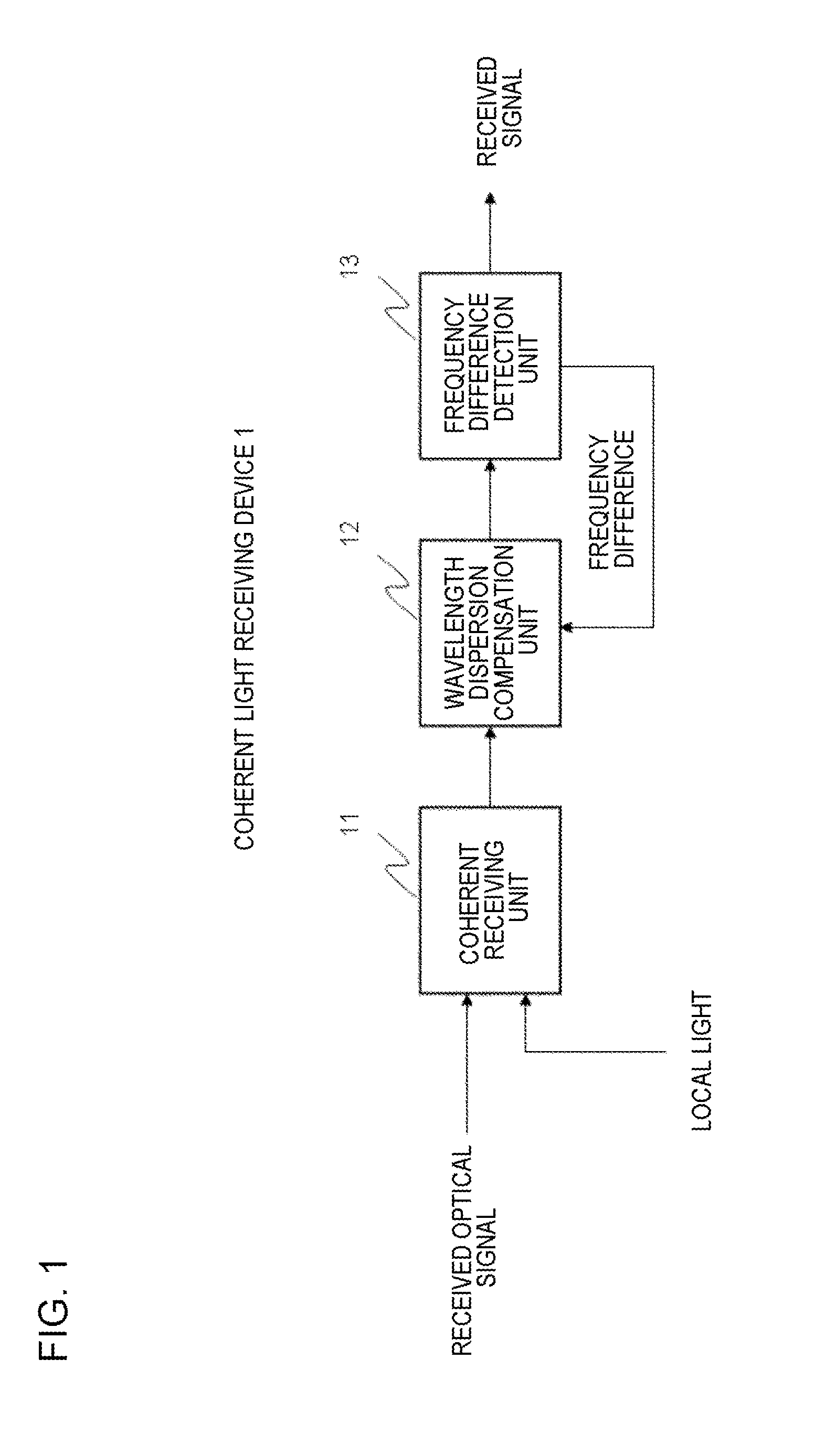

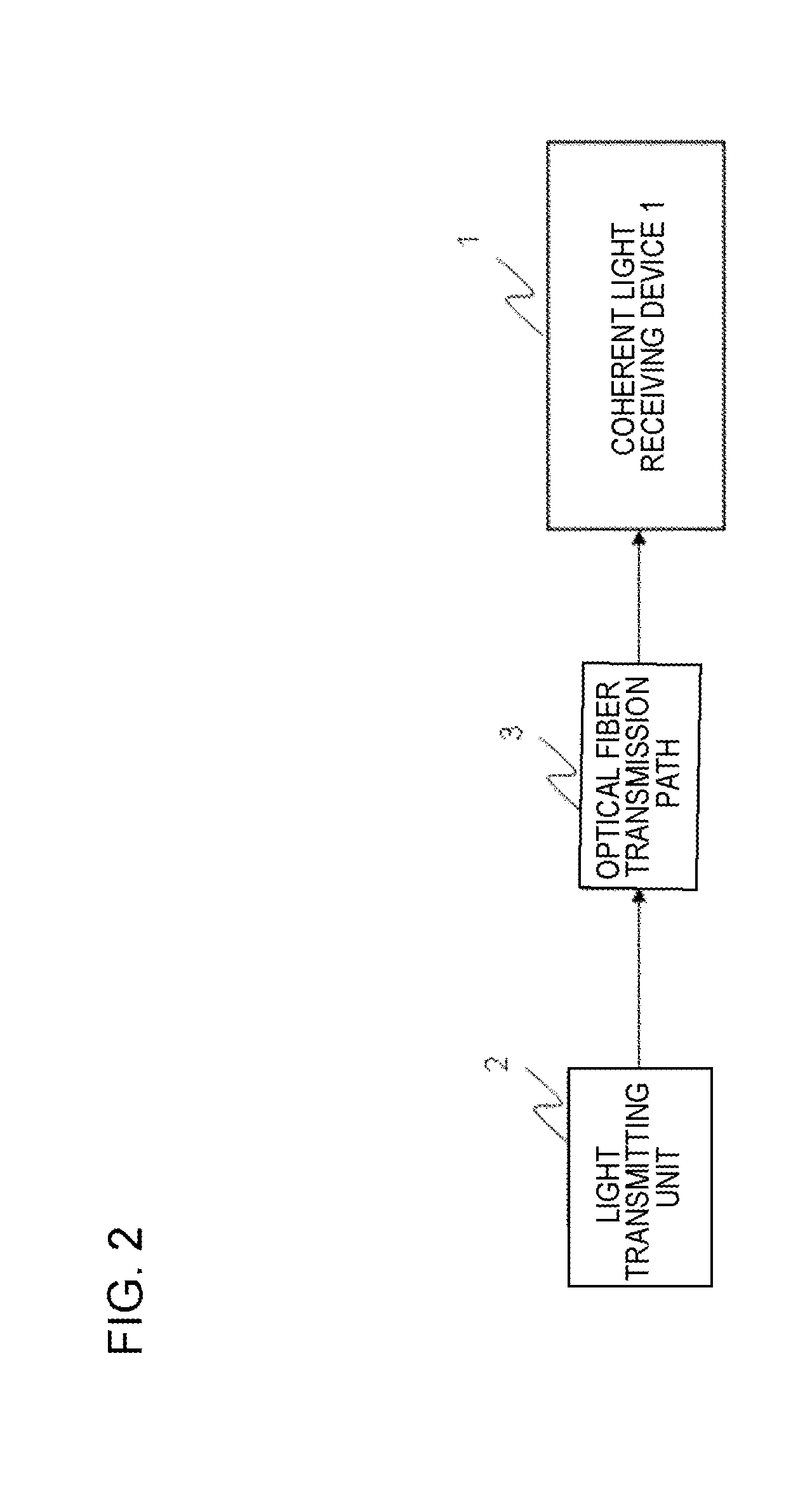

Coherent light receiving device, system, and method

InactiveUS20130216240A1Reduce time skewShorten the timeElectromagnetic receiversLength waveWaveform distortion

A coherent light receiving device includes a coherent receiving unit which mixes a received optical signal with local light and performs optical coherent detection to output a digital signal, a wavelength dispersion compensation unit which compensates for waveform distortion in the digital signal and outputs a digital signal after compensation, and a frequency difference detection unit which detects the frequency difference between the received optical signal and local light and notifies the wavelength dispersion compensation unit of the frequency difference, wherein the wavelength dispersion compensation unit performs compensation using a transfer function which is based on the frequency difference notified from the frequency difference detection unit and represents waveform distortion due to wavelength dispersion.

Owner:NEC CORP

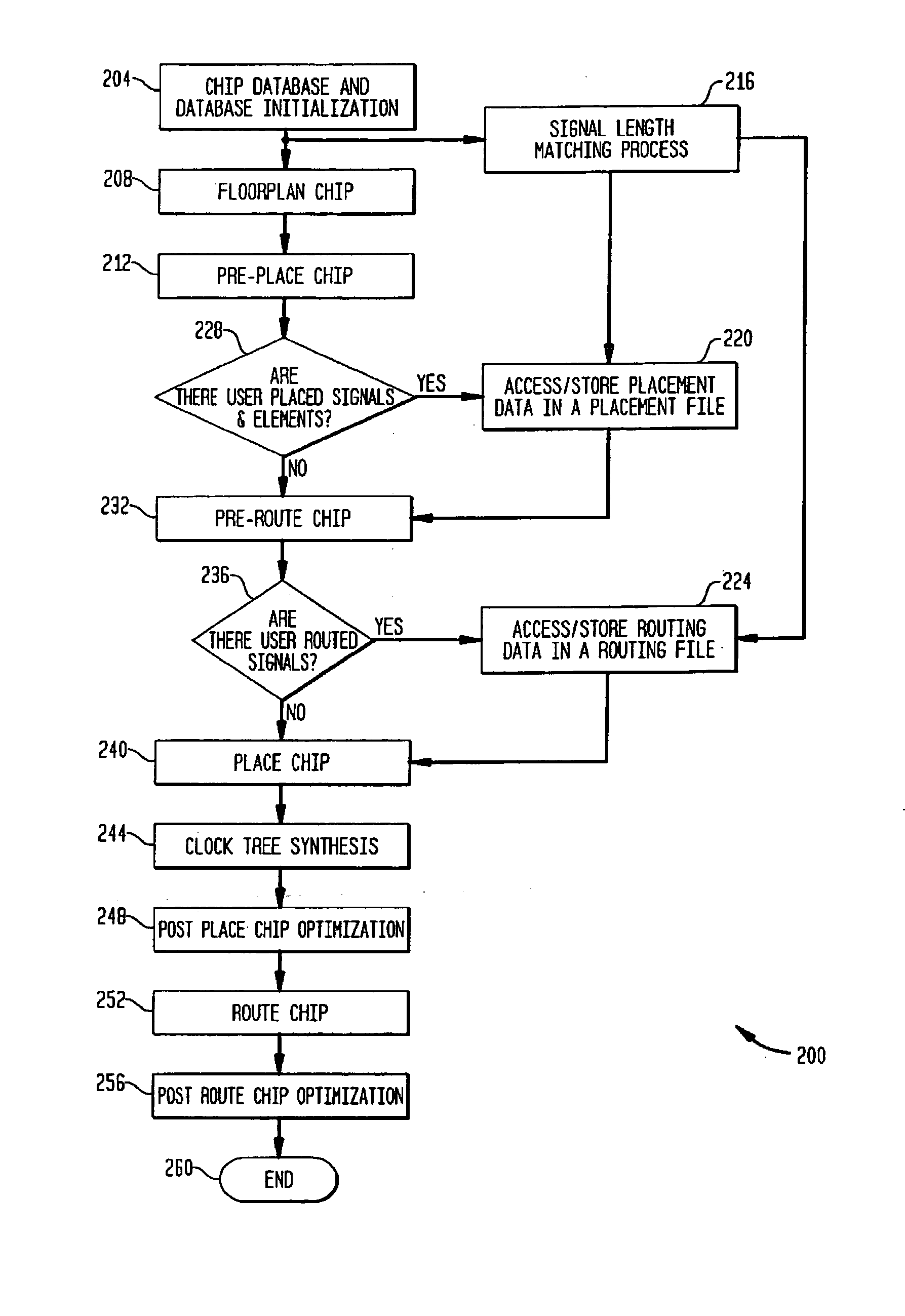

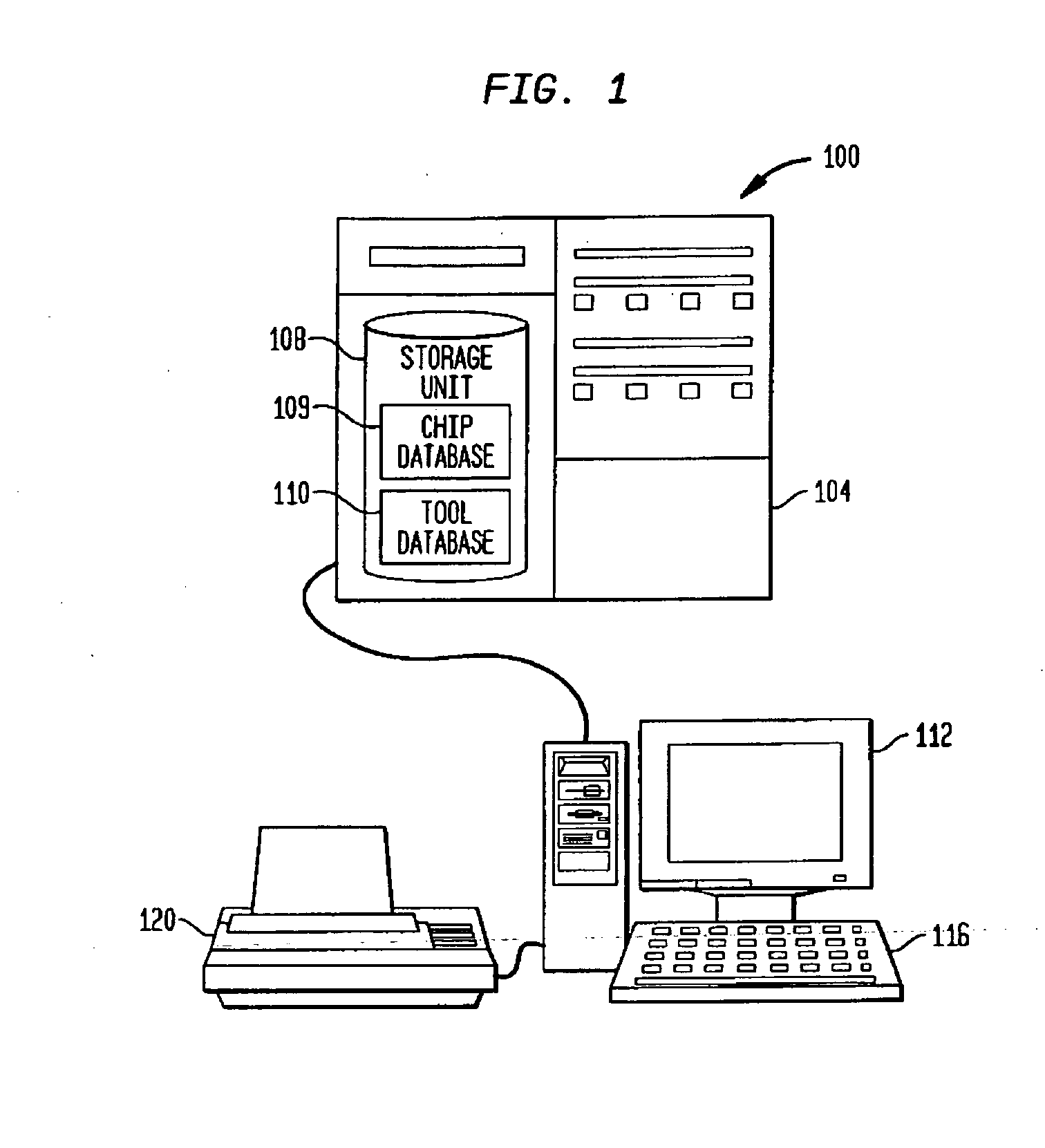

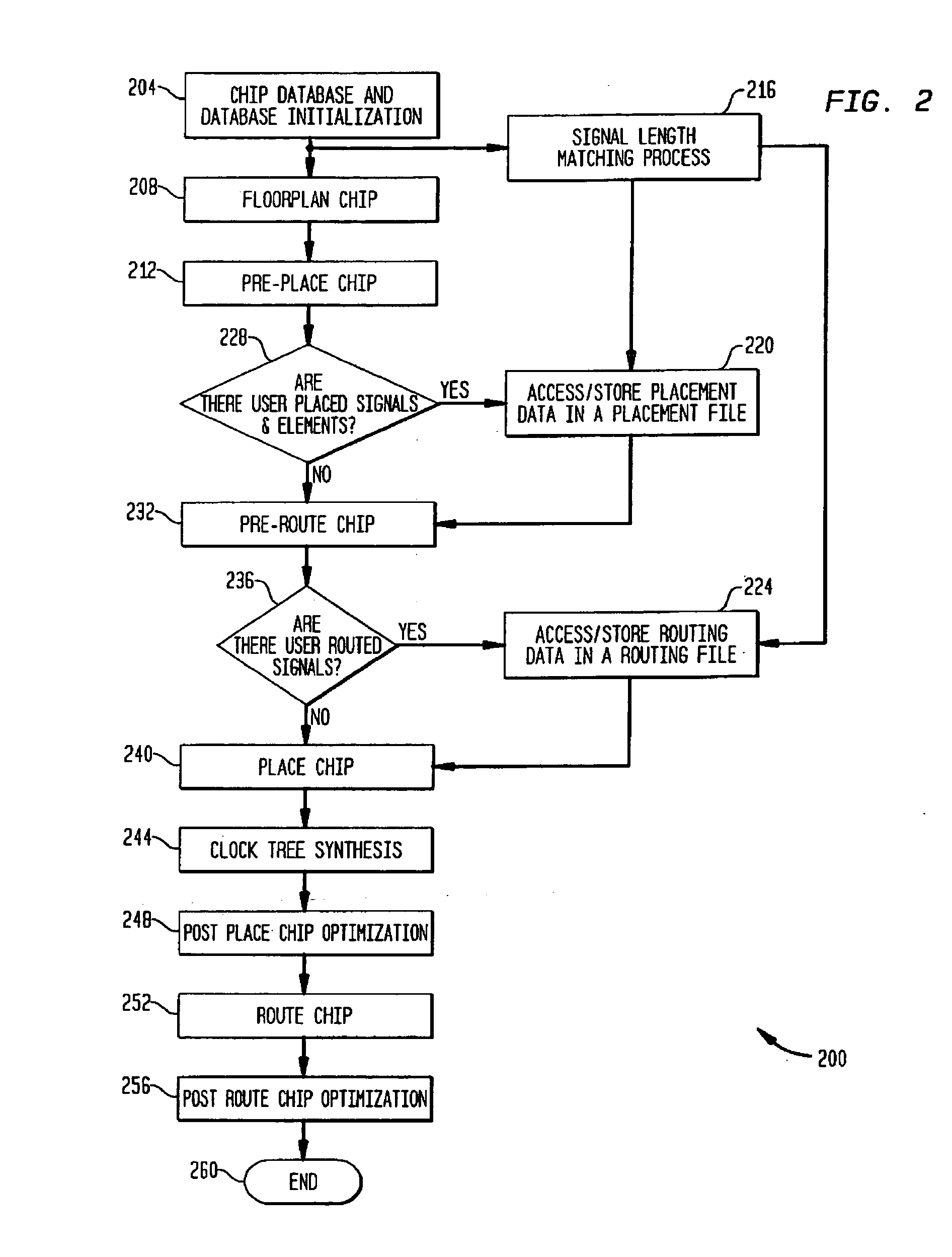

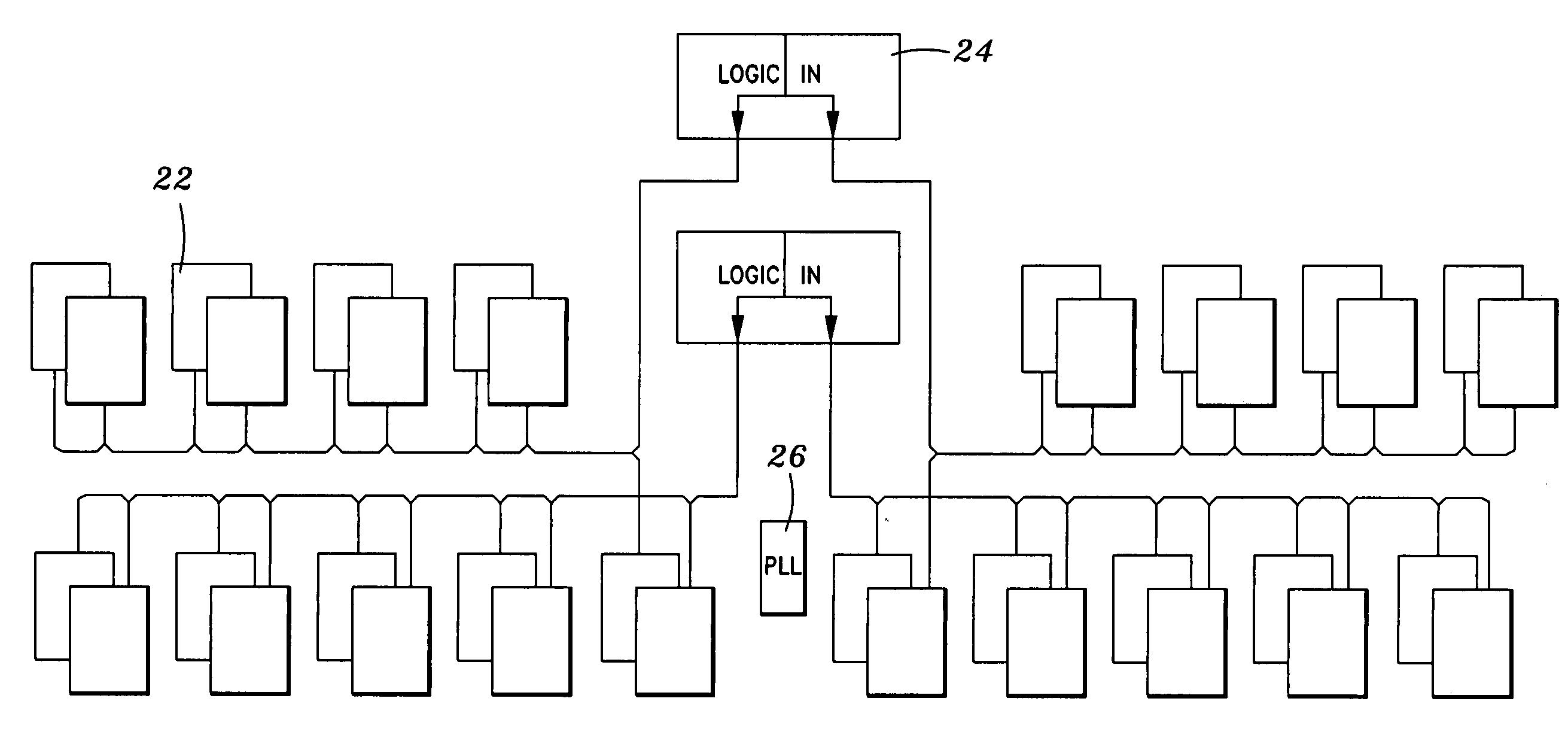

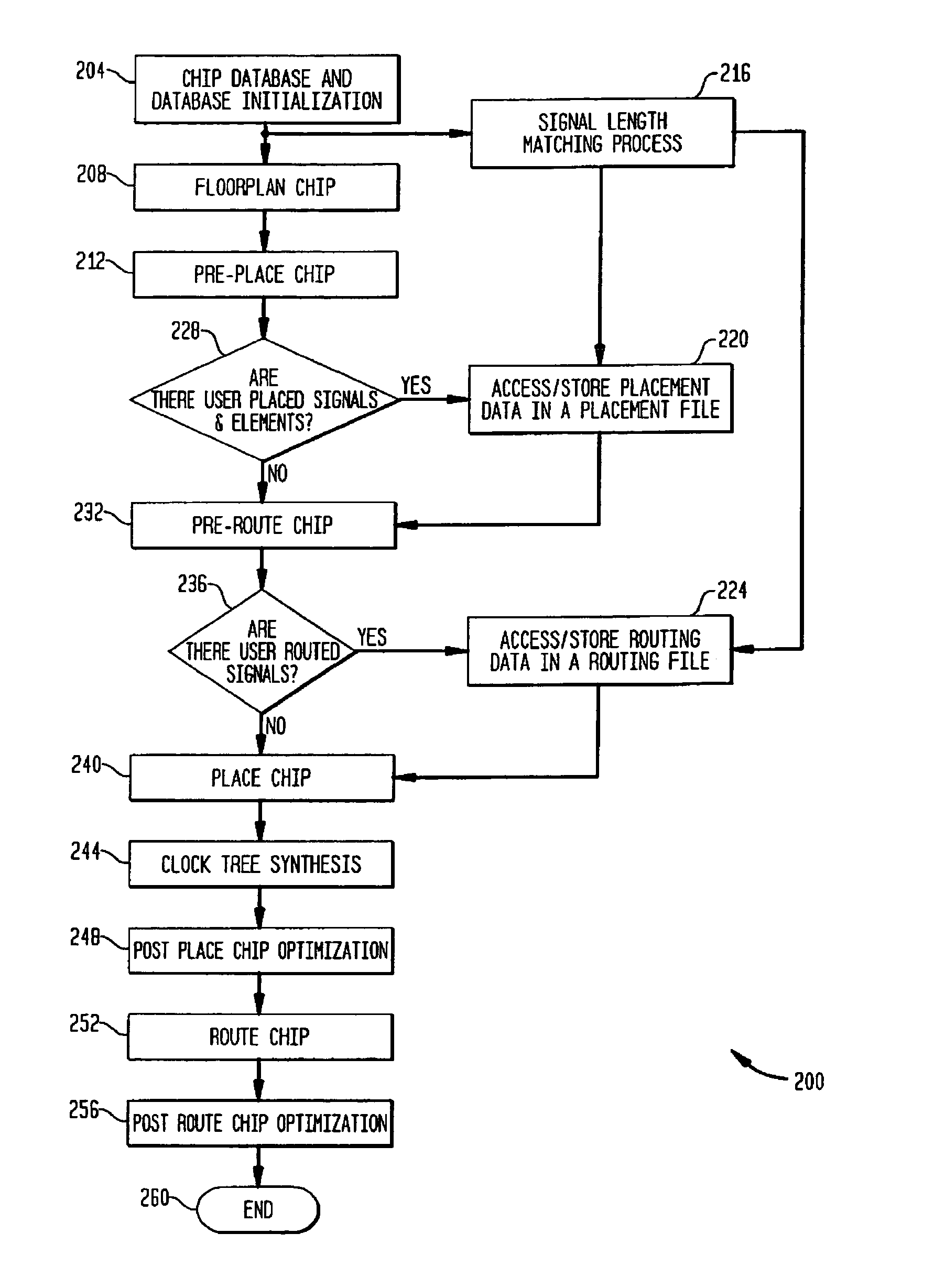

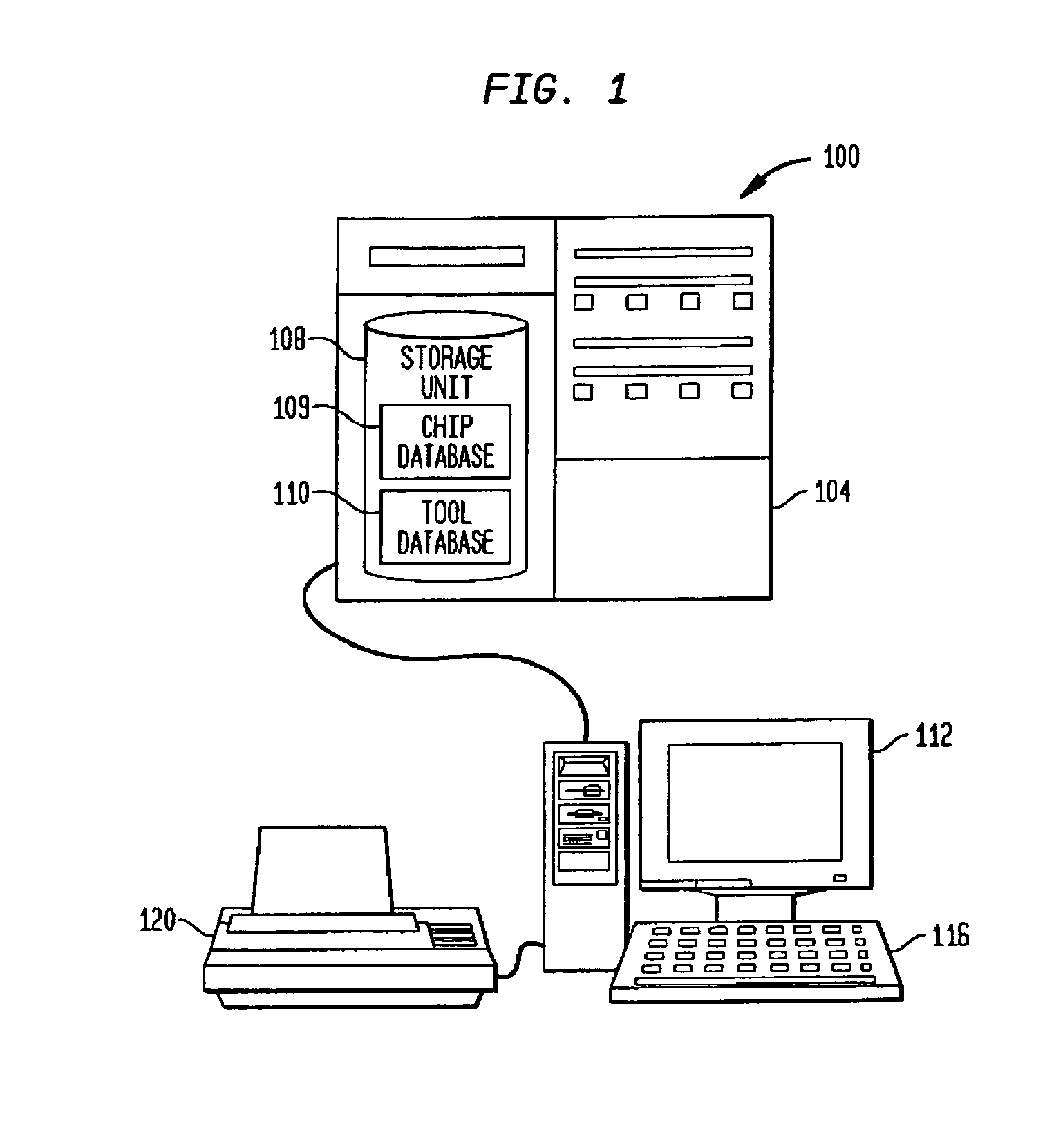

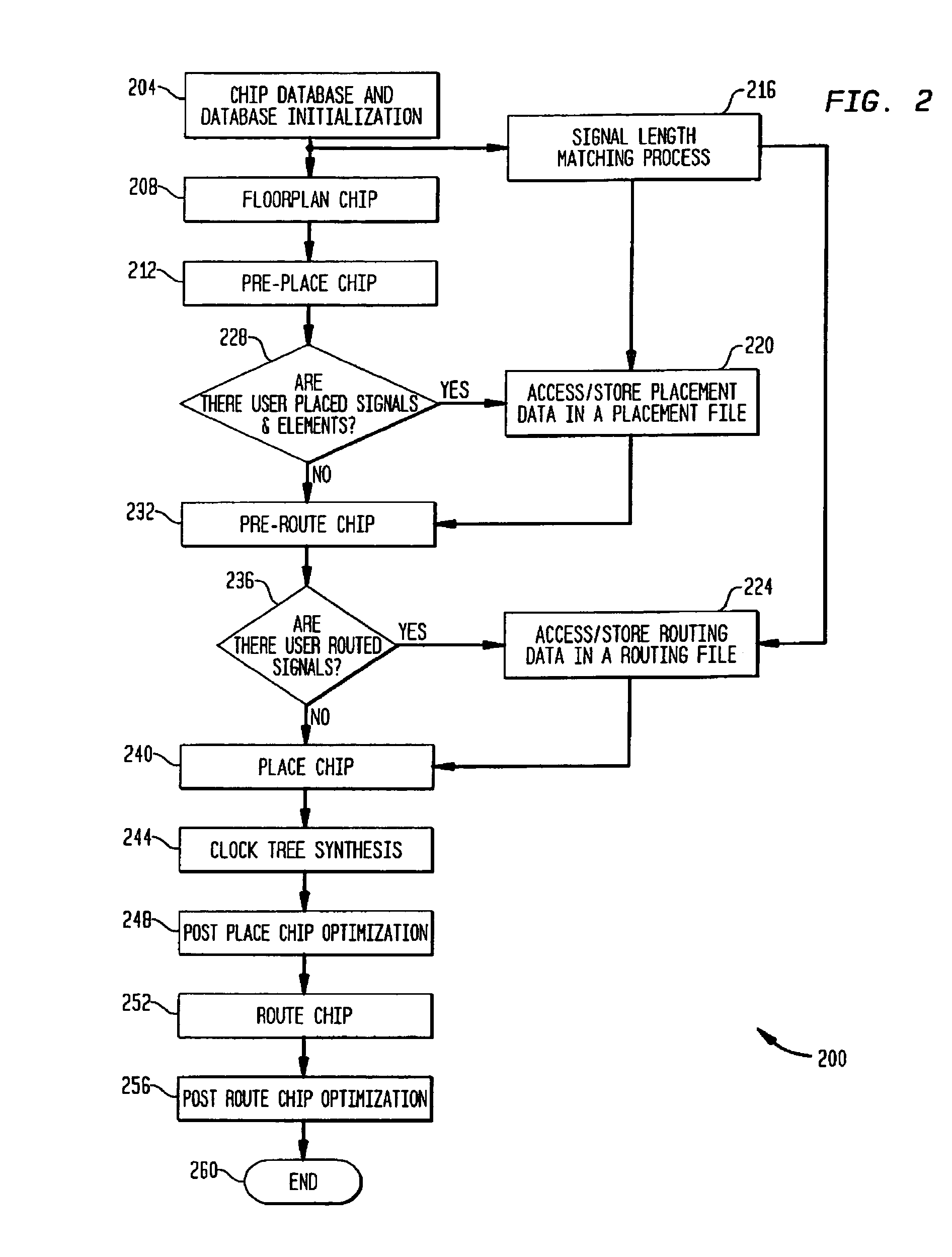

Methods and apparatus for reducing timing skew

InactiveUS20070220466A1Reduce distanceReduce time skewCAD circuit designSoftware simulation/interpretation/emulationElectrical and Electronics engineeringEngineering

Reducing timing skew begins with identifying signals that are to have a reduced timing skew. These identified signals are then routed to reduce the layout distance of each signal path. Among these identified signals, a longest signal path is found and the signal paths of the remaining identified signals are lengthened. The lengthening is done to each of the remaining identified signal paths to each have a length substantially equal to the longest signal path whereby the timing skew between the identified signals is reduced. A signal length matching process may be stored as a program in a computer-readable medium with the program operable on a computer system tailored for providing chip placement and routing processes.

Owner:BELL SEMICON LLC

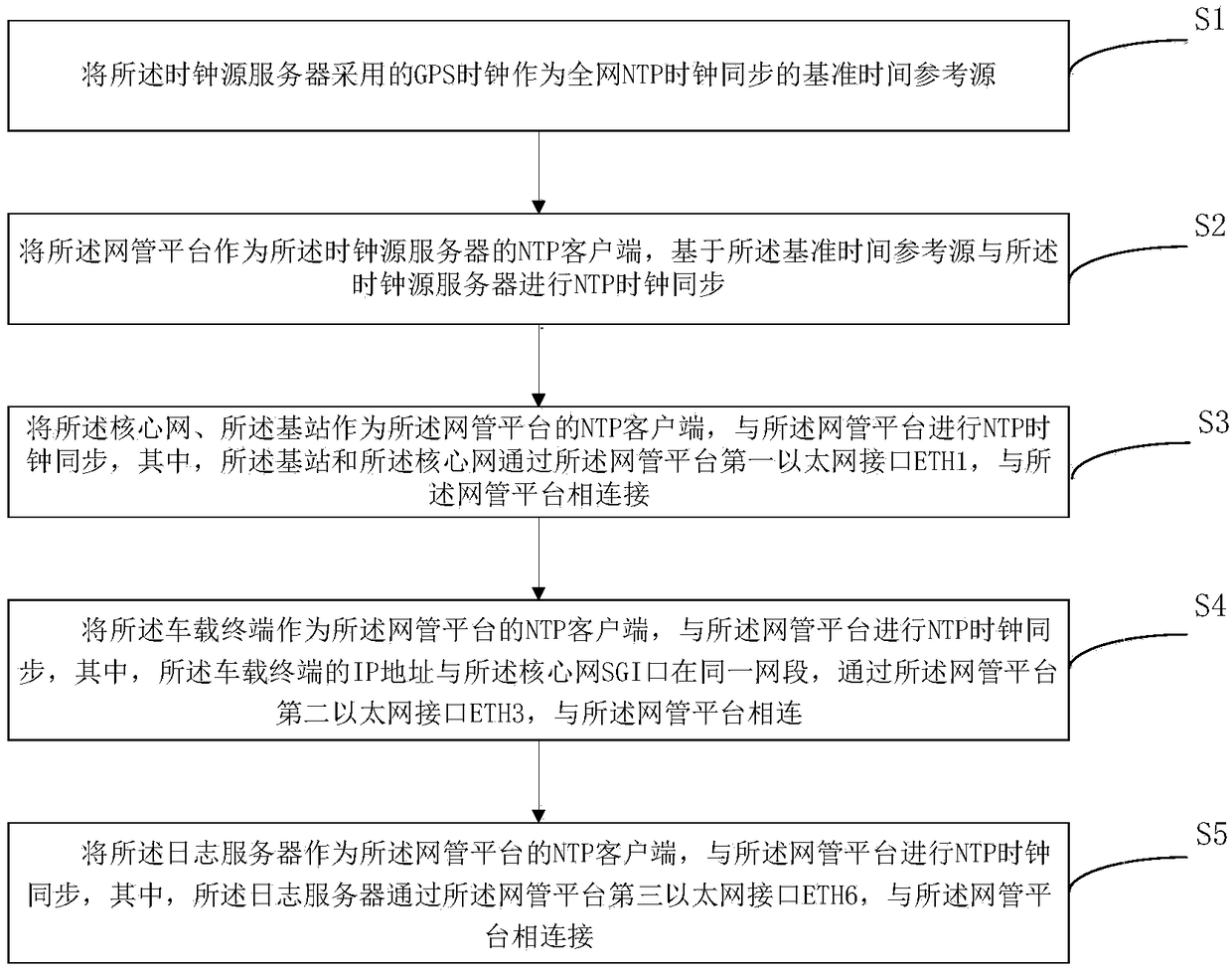

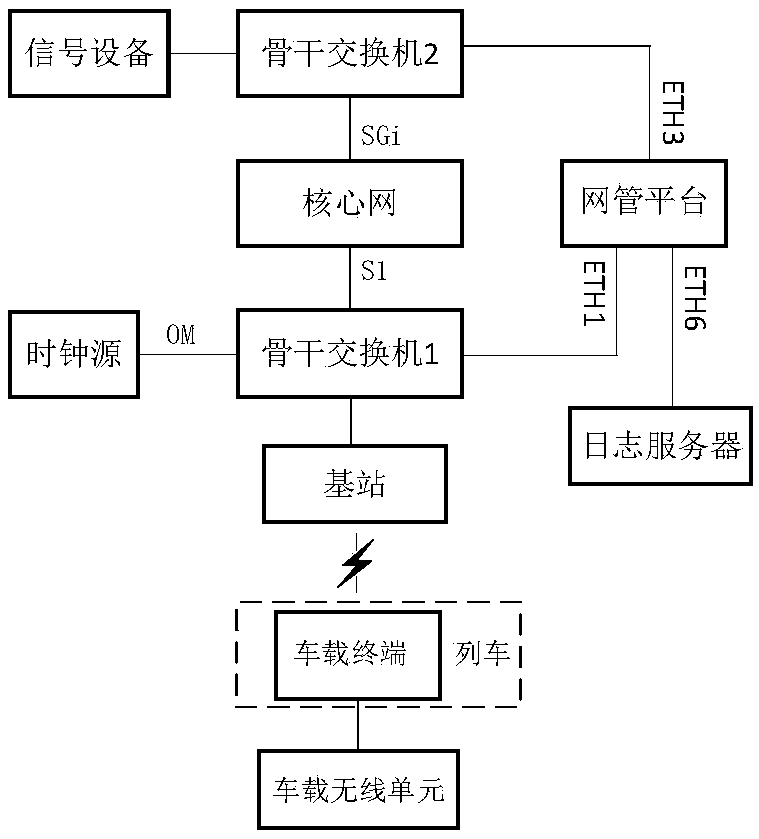

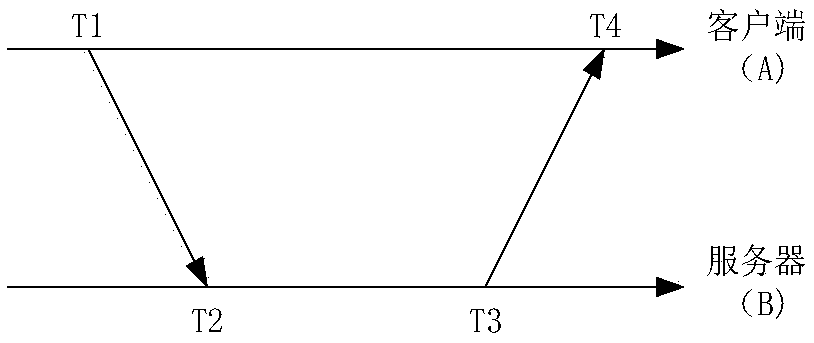

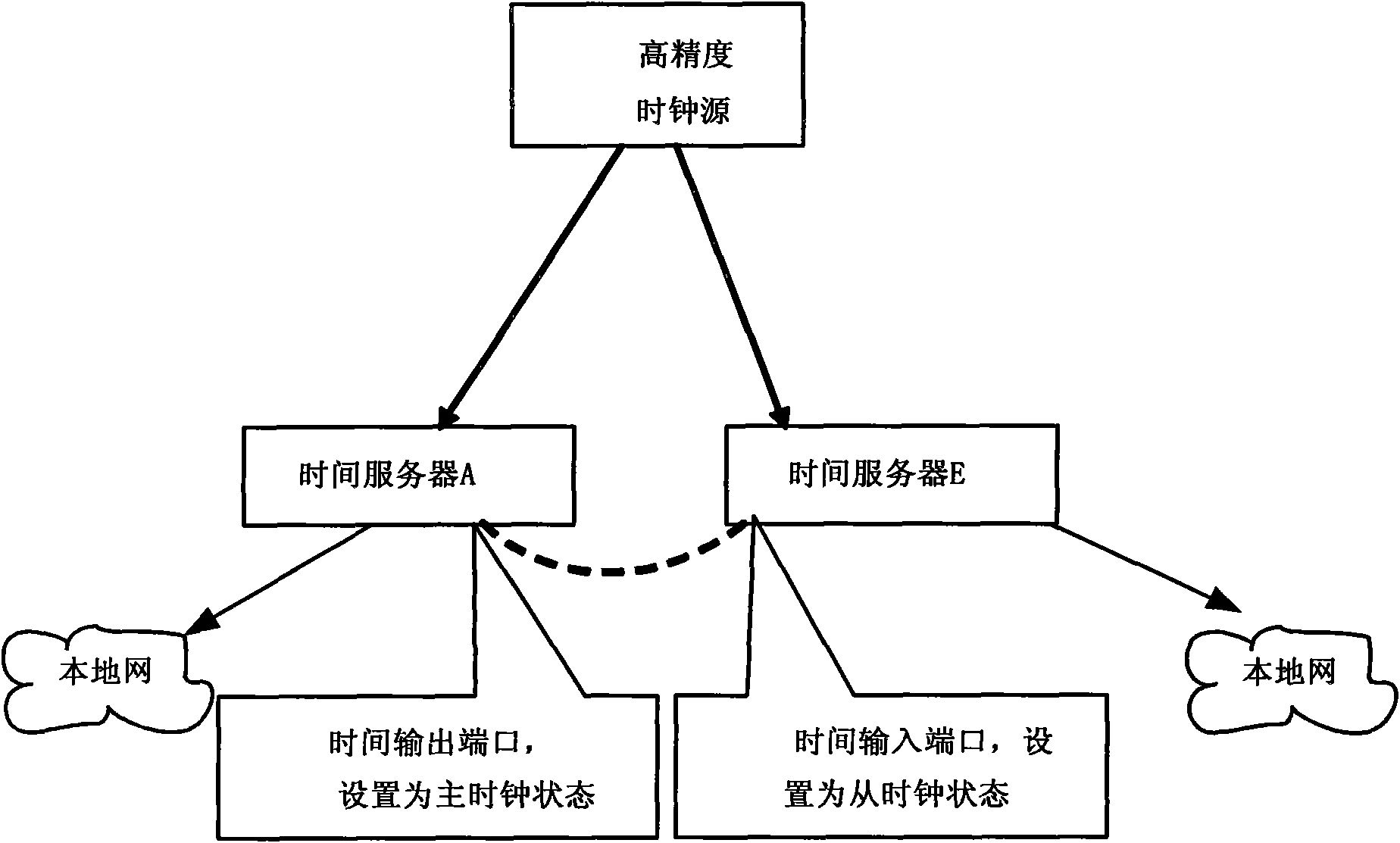

Whole-network clock synchronization method and a device applied to an LTE rail transit network

ActiveCN109257133AAchieve synchronizationReduce time skewSynchronisation arrangementTime-division multiplexNetwork clockNetwork management

The invention provides a whole network clock synchronization method and a whole network clock synchronization device applied to an LTE rail traffic network. The method comprises the following steps: aGPS clock adopted by a clock source server is used as a reference time reference source of the whole network NTP clock synchronization. The NTP client uses the network management platform as the clock source server, and synchronizes the NTP clock with the clock source server based on the reference time reference source. The core network, base station and log server are used as the NTP client of the network management platform to synchronize the NTP clock with the network management platform, and the vehicle terminal is used as the NTP client of the network management platform to synchronize the NTP clock with the network management platform. The method of the invention realizes the technical effect of clock synchronization of the whole rail transit network.

Owner:WUHAN HONGXIN TECH DEV CO LTD

Sheet processing apparatus and sheet processing method

ActiveUS20080309006A1Accurately carry-outReduce time skewFunction indicatorsElectrographic process apparatusEngineeringControl theory

A sheet processing apparatus includes a hole punching section arranged downstream from a skew detecting unit and orthogonally to a conveying path of a sheet, and a control unit configured to change the tilt angle of the hole punching section in accordance with each of the quantity of skew at the forward edge and the quantity of skew at the rear edge of the sheet, carry out skew correction at the forward edge within a first correction range w1, and carry out skew correction at the rear edge within a second correction range w2 (where w1>w2≧w1 / 2). The control unit carries out skew correction at the forward edge within the correction range w2, in the case where the detected quantity of skew at the forward edge is a tilt angle exceeding the correction range w2, and then carries out skew correction at the rear edge in accordance with the difference between the quantity of skew at the forward edge after the correction and the quantity of skew at the rear edge.

Owner:KK TOSHIBA +1

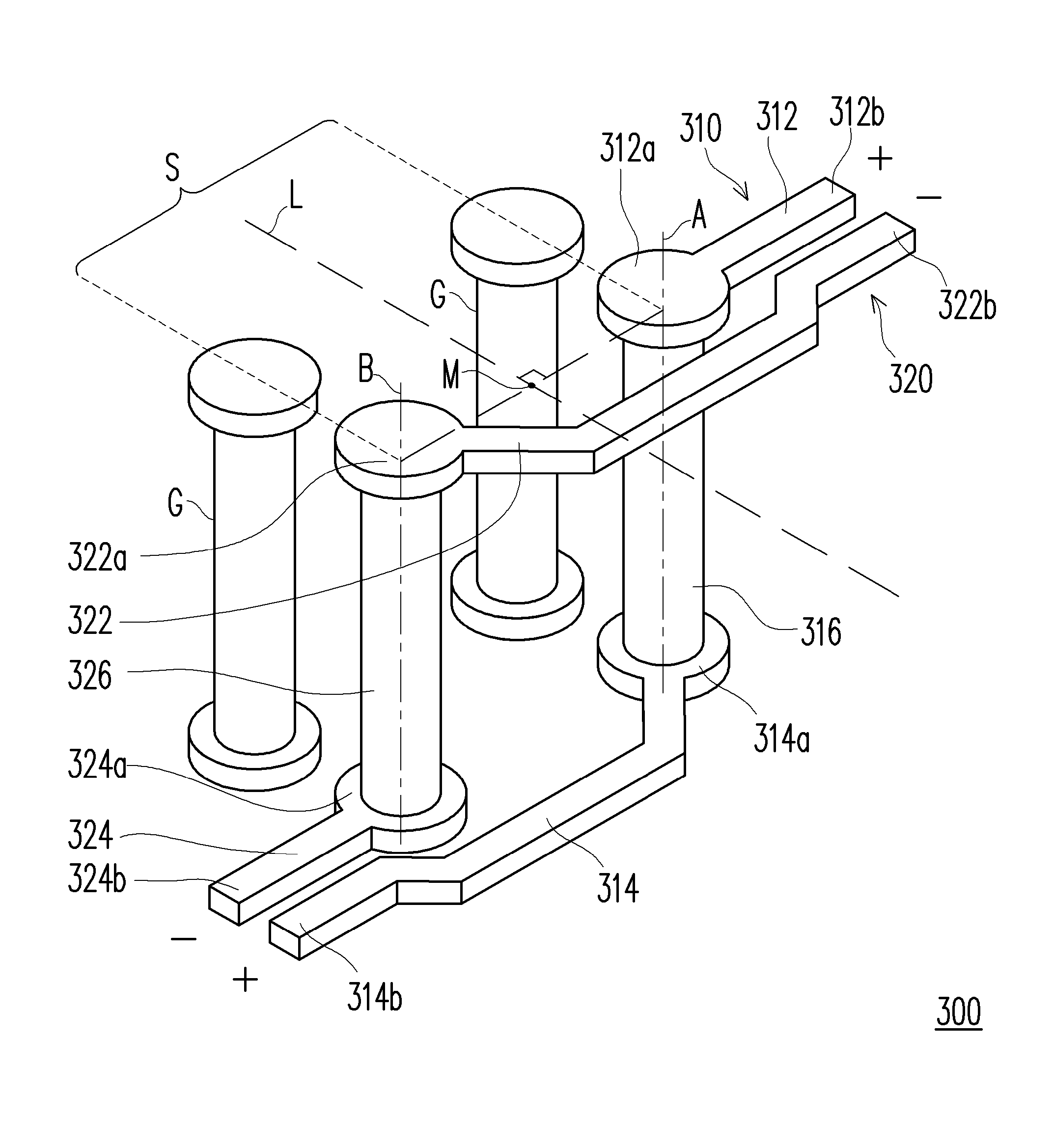

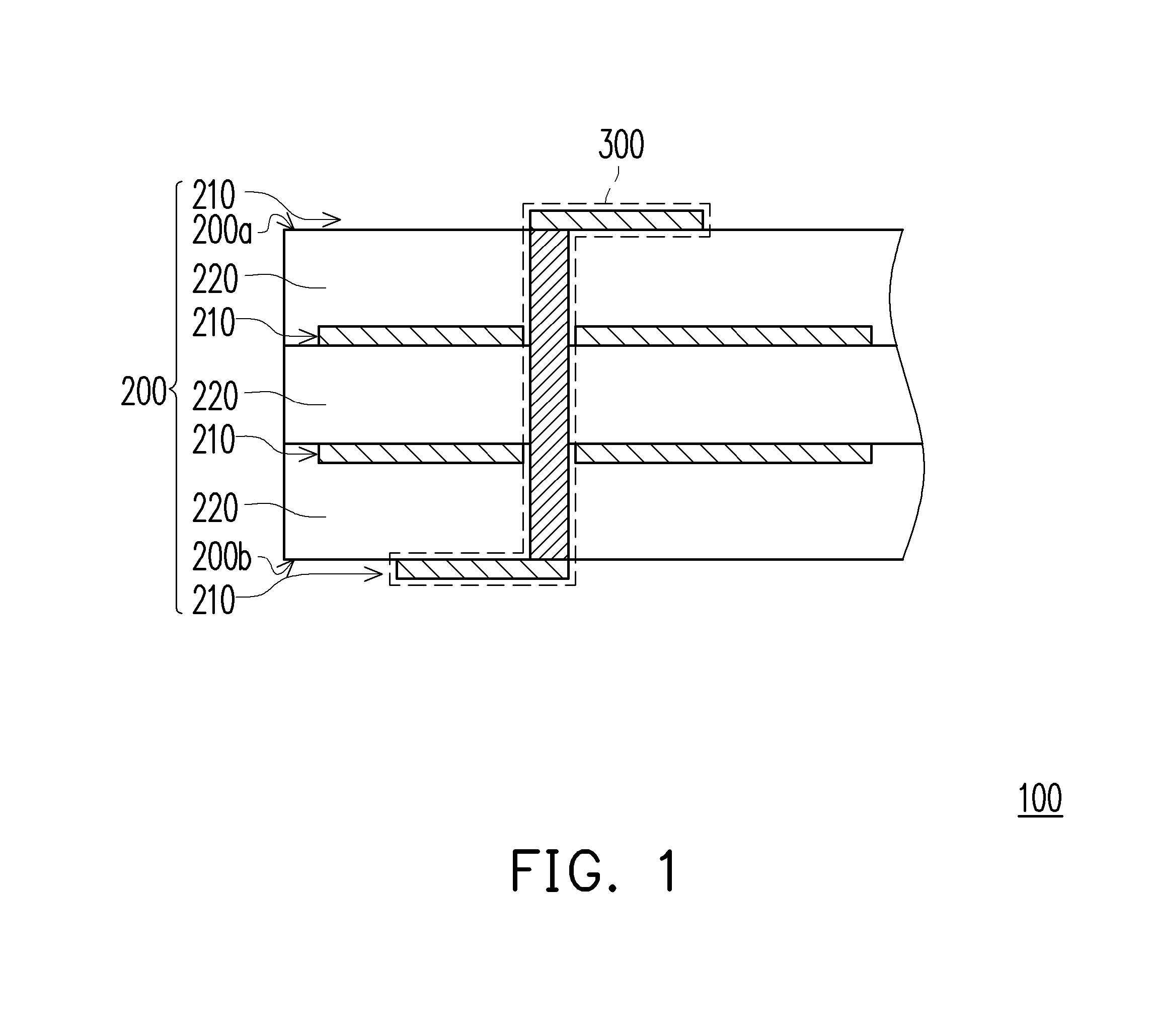

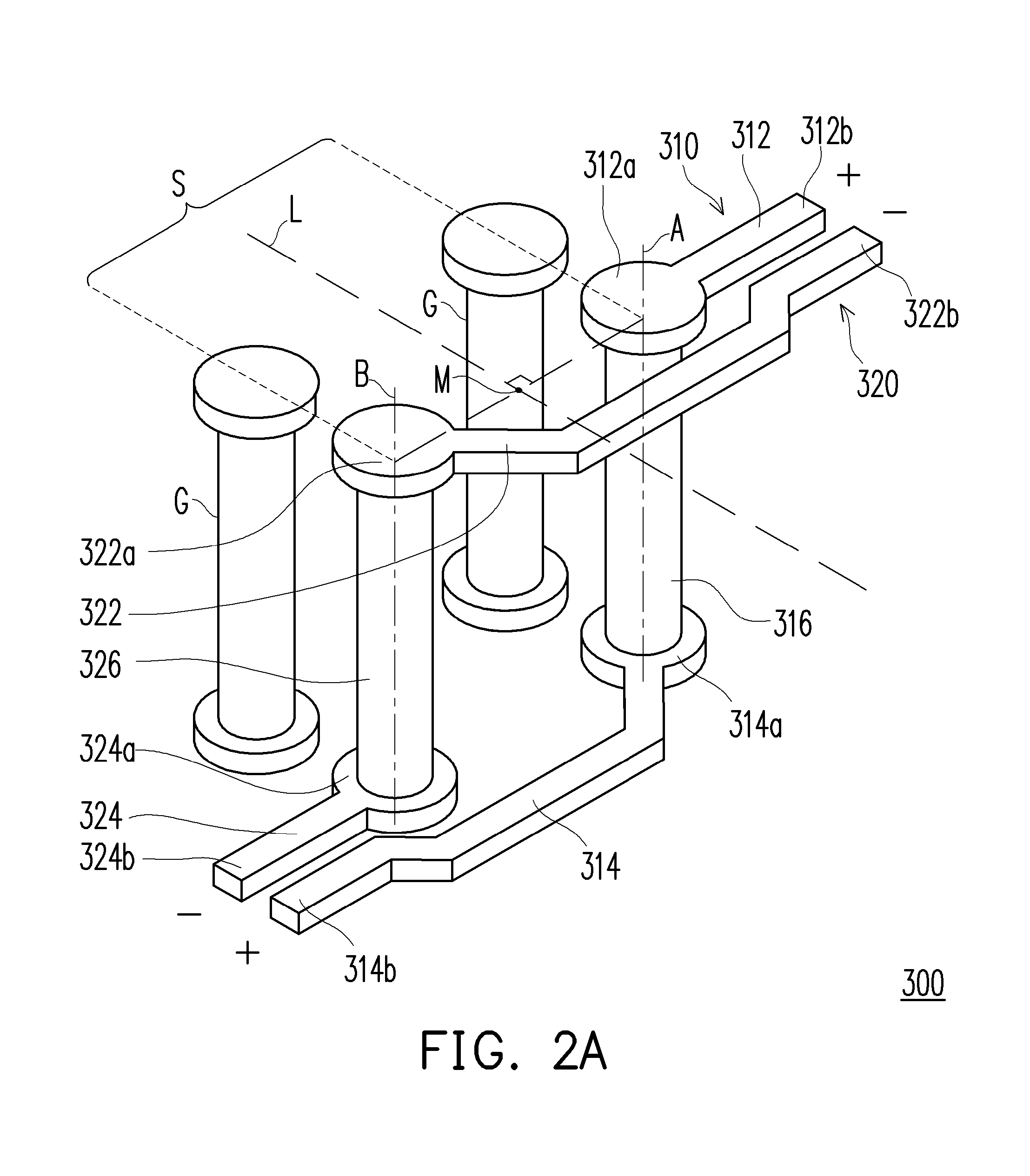

Differential signal pair transmission structure, wiring board and electronic module

ActiveUS8552308B2Reduce time skewPrinted electric component incorporationPrinted circuit aspectsElectronic modulesEngineering

A differential signal pair transmission structure adapted to a wiring board and including a first signal path and a second signal path is provided. The first signal path includes a first upper trace, a first lower trace and a first conductive through via. The second signal path includes a second upper trace, a second lower trace and a second conductive through via. A portion of the first signal path and a portion of the second signal path overlaps in the normal projection onto the upper or lower surface of the wiring board. Normal projections of the first and the second signal path projecting onto the upper surface of the wiring board are substantially symmetric with respect to a line which is perpendicular to a segment connecting normal projections of axes of the first and the second through via onto the upper surface and passes through the midpoint of the segment.

Owner:VIA LABS INC

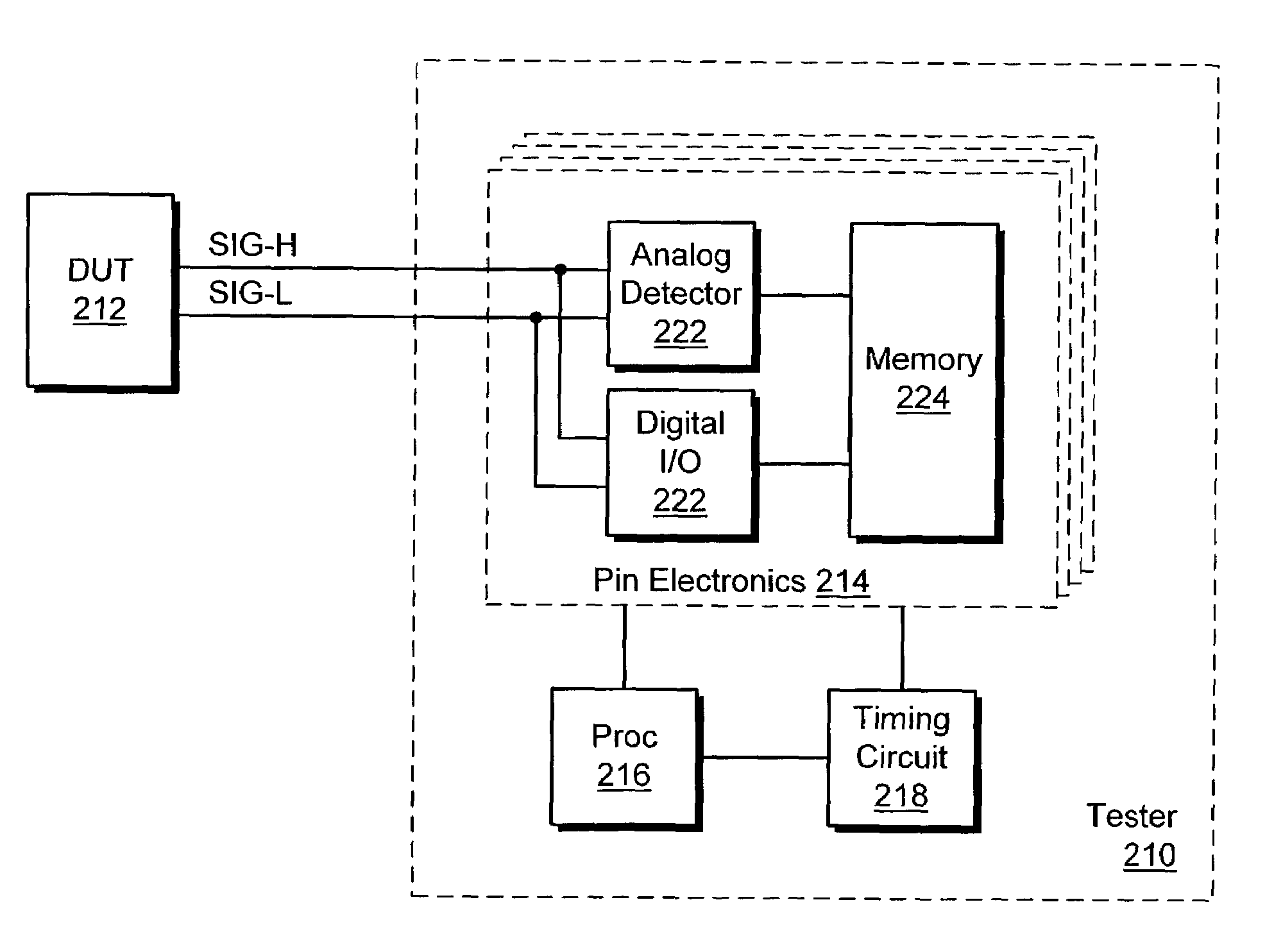

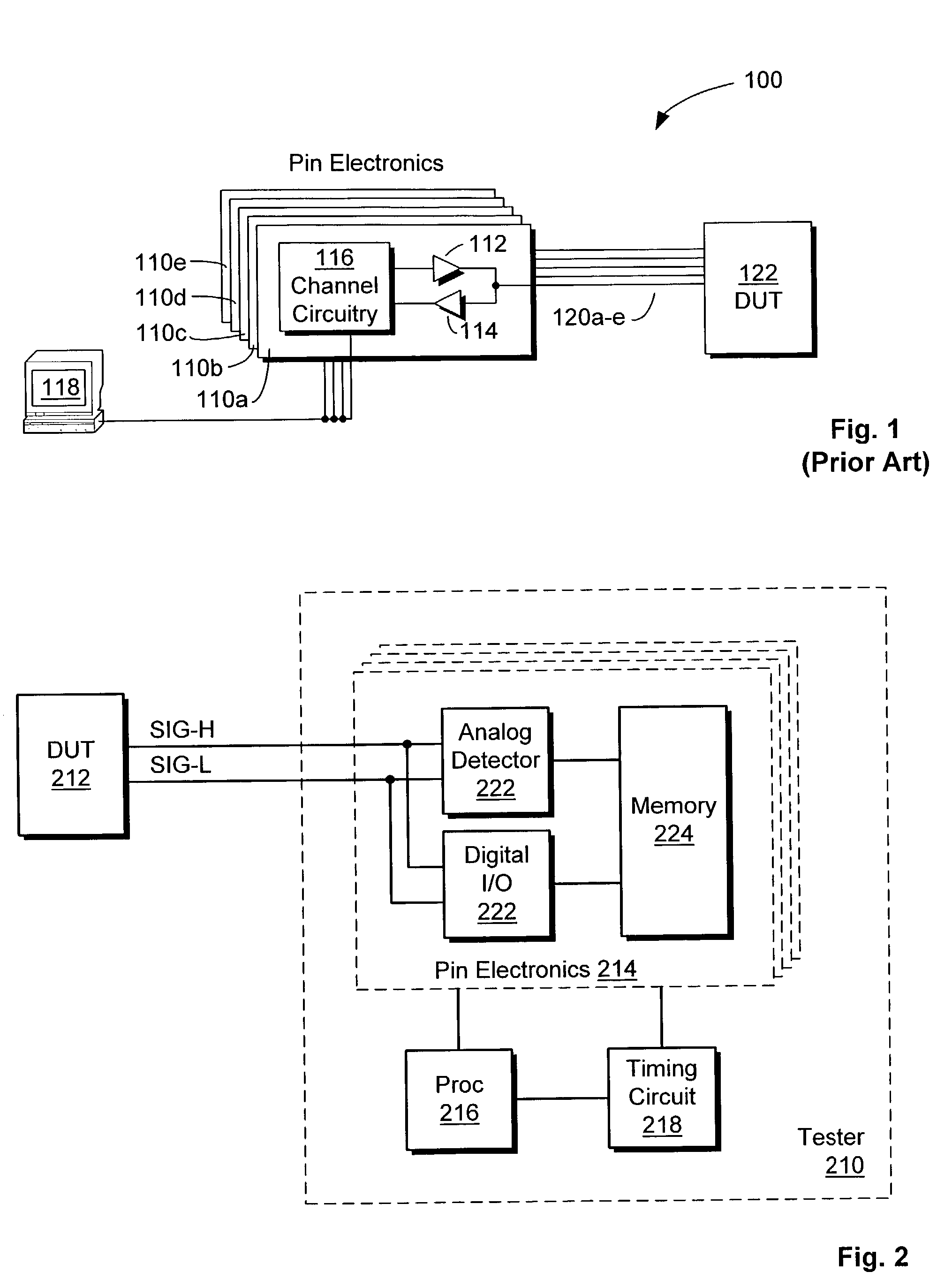

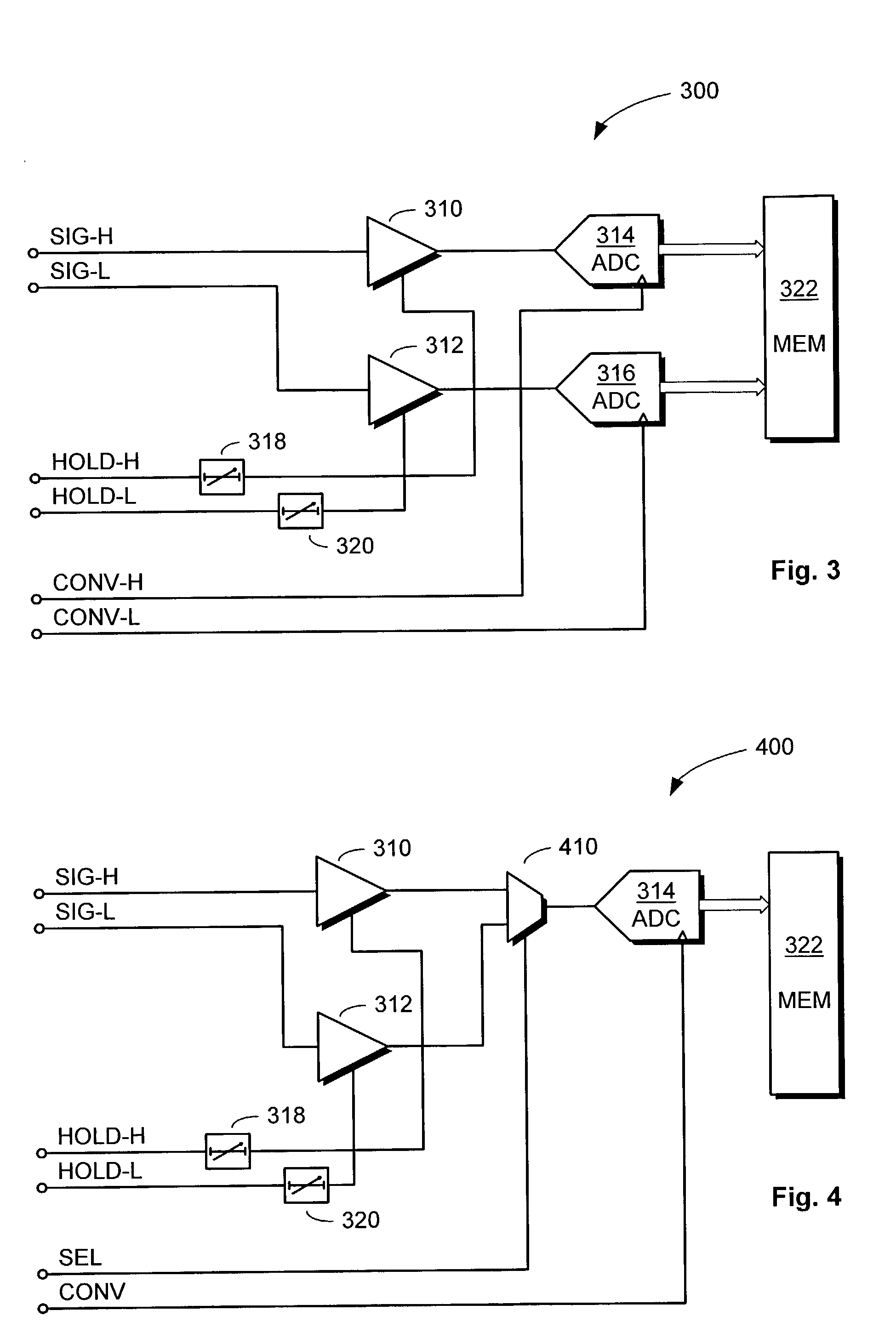

Deskewed differential detector employing analog-to-digital converter

InactiveUS6981192B2Reduce time skewDigital circuit testingError detection/correctionAutomatic test equipmentDigital down converter

A pin electronics circuit for automatic test equipment includes first and second sampling circuits for sampling first and second legs of a differential signal produced by a DUT (Device Under Test). Timing signals activate the first and second sampling circuits to sample the legs of the differential signal at precisely defined instants of time to produce first and second collections of samples. To deskew the legs of a differential signal with respect to each other, corresponding features within the first and second collections are identified and a difference is taken between them. The differential skew can then be applied to correct measurements of differential signals.

Owner:TERADYNE

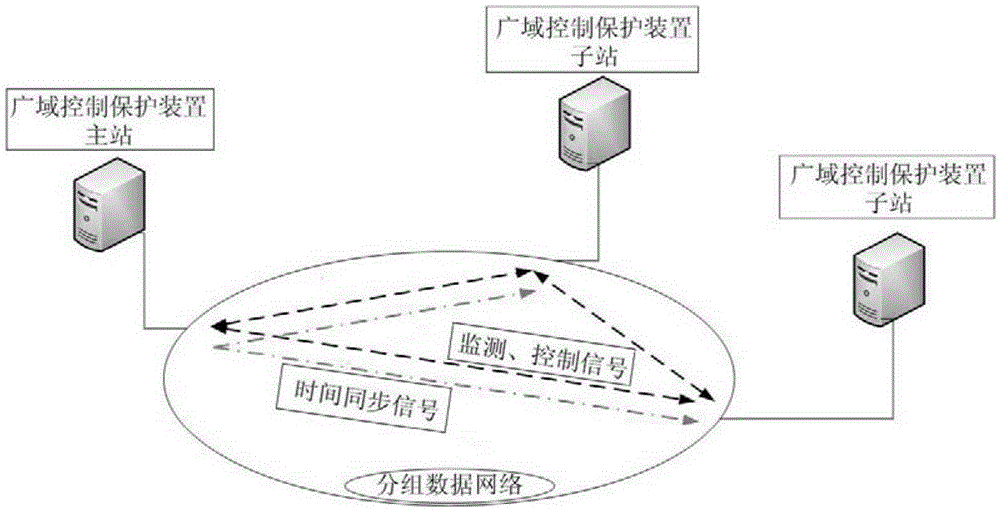

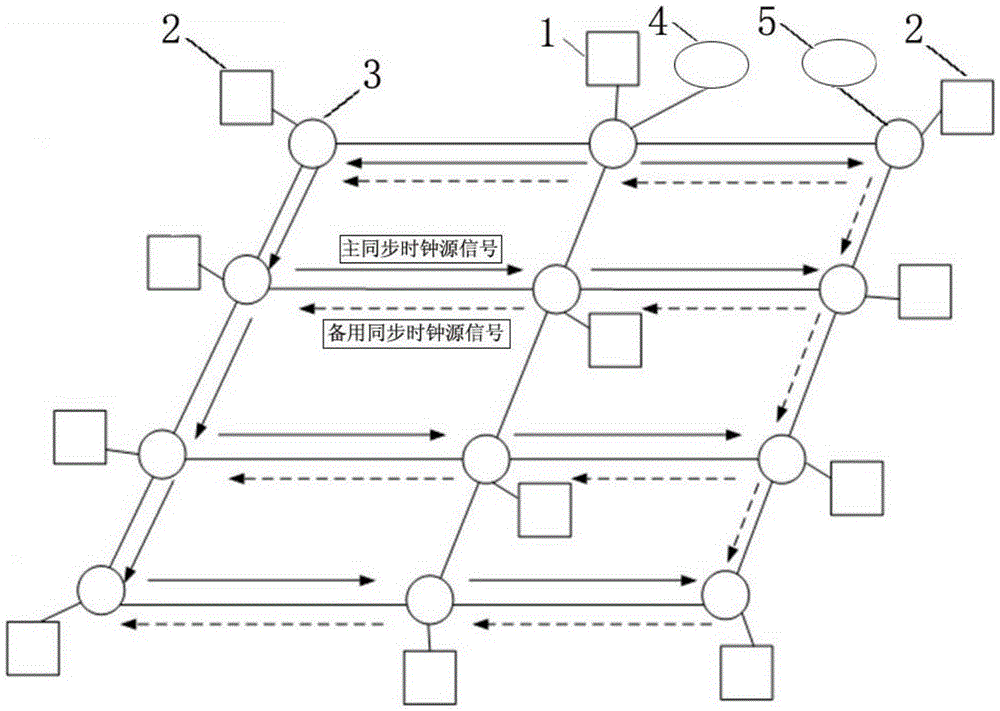

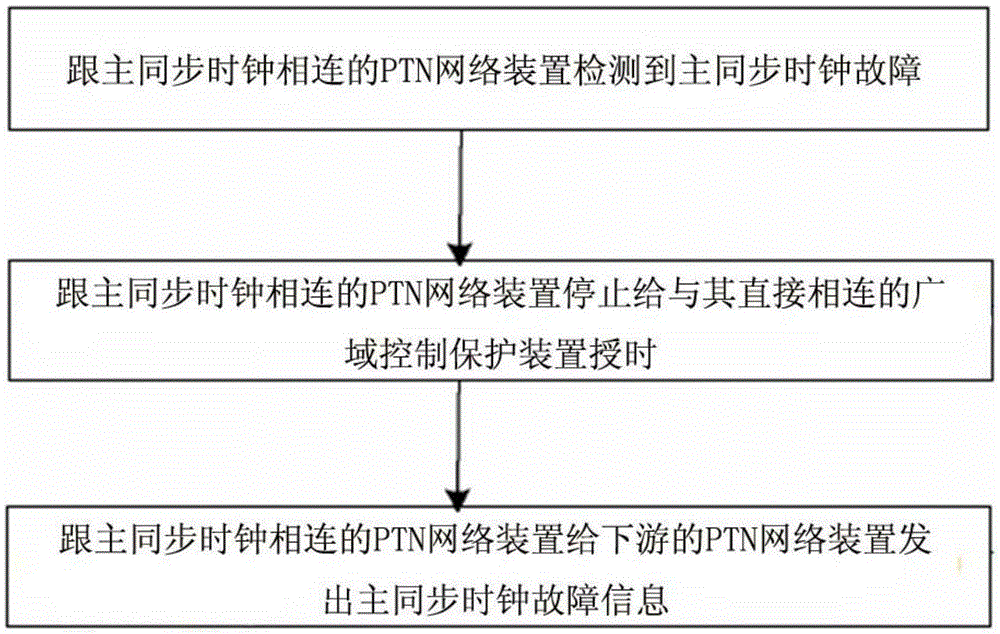

Method and system for switching main and standby synchronous clocks under BC (Basic Control) mode of PTN (Packet Transport Network) synchronous network of wide area protection system

InactiveCN105245306AAvoid misuseHigh time accuracyTime-division multiplexTransmission protocolWide area

The invention provides a method and a system for switching main and standby synchronous clocks under a BC (Basic Control) mode of a PTN (Packet Transport Network) synchronous network of a wide area protection system. Wide area control protection devices of various substations are connected through a PTN network device and interstation time synchronization is realized by adopting a BC synchronizing function of a transmission IEEE1588V2 protocol; when the main synchronous clock has a fault, a time service interface of each wide area control protection device is cut off, and the standby synchronous clock is fast tracked in this time; and after time precision of the standby synchronous clock is determined, switching completion information is sent to all PTN network devices to realize time service of each wide area control protection device again. The method and the system have the characteristics of fast fault switching speed, high accuracy, good signal transmission quality and low time deviation ratio of each wide area control protection device in a fault process of the synchronous clock.

Owner:CHINA SOUTHERN POWER GRID COMPANY +1

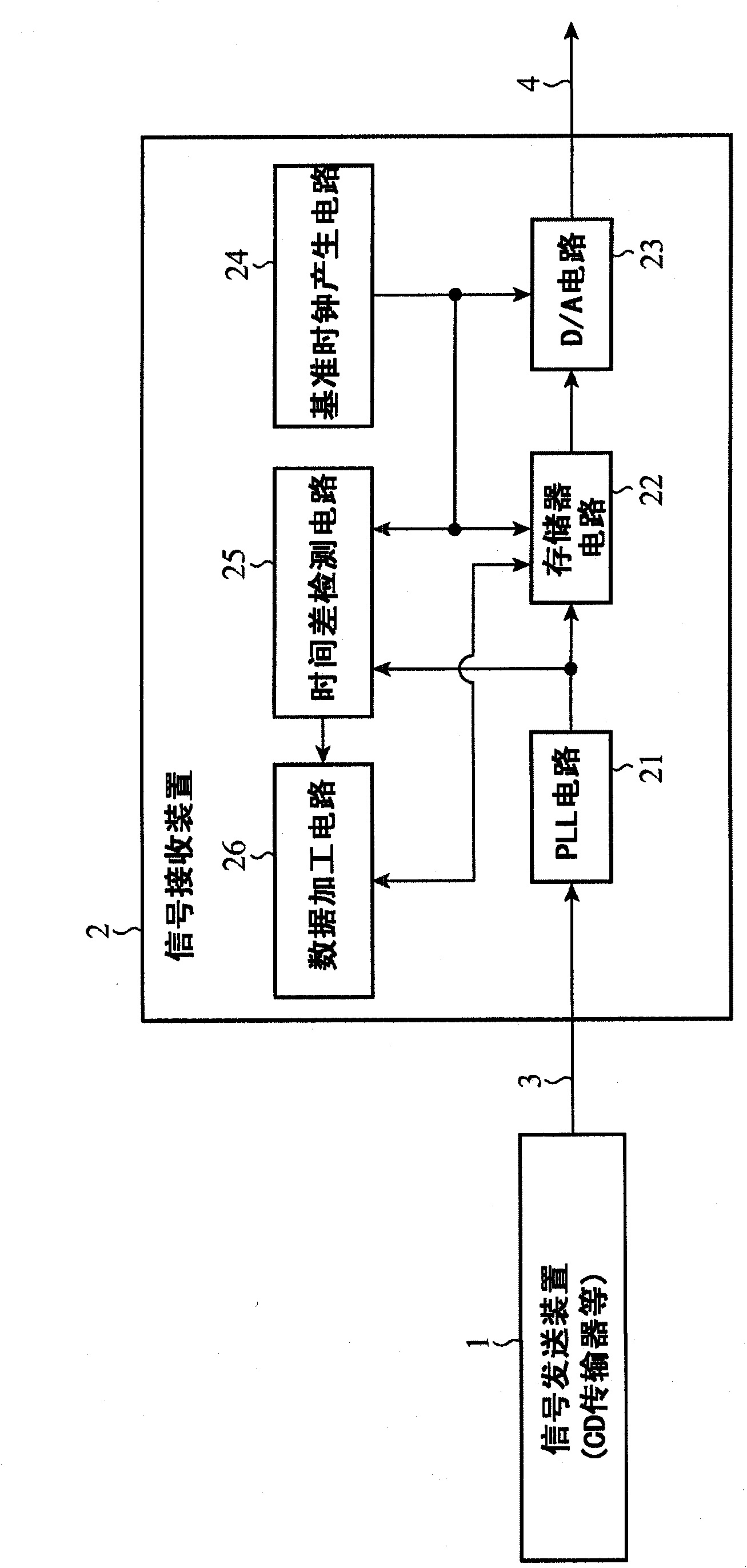

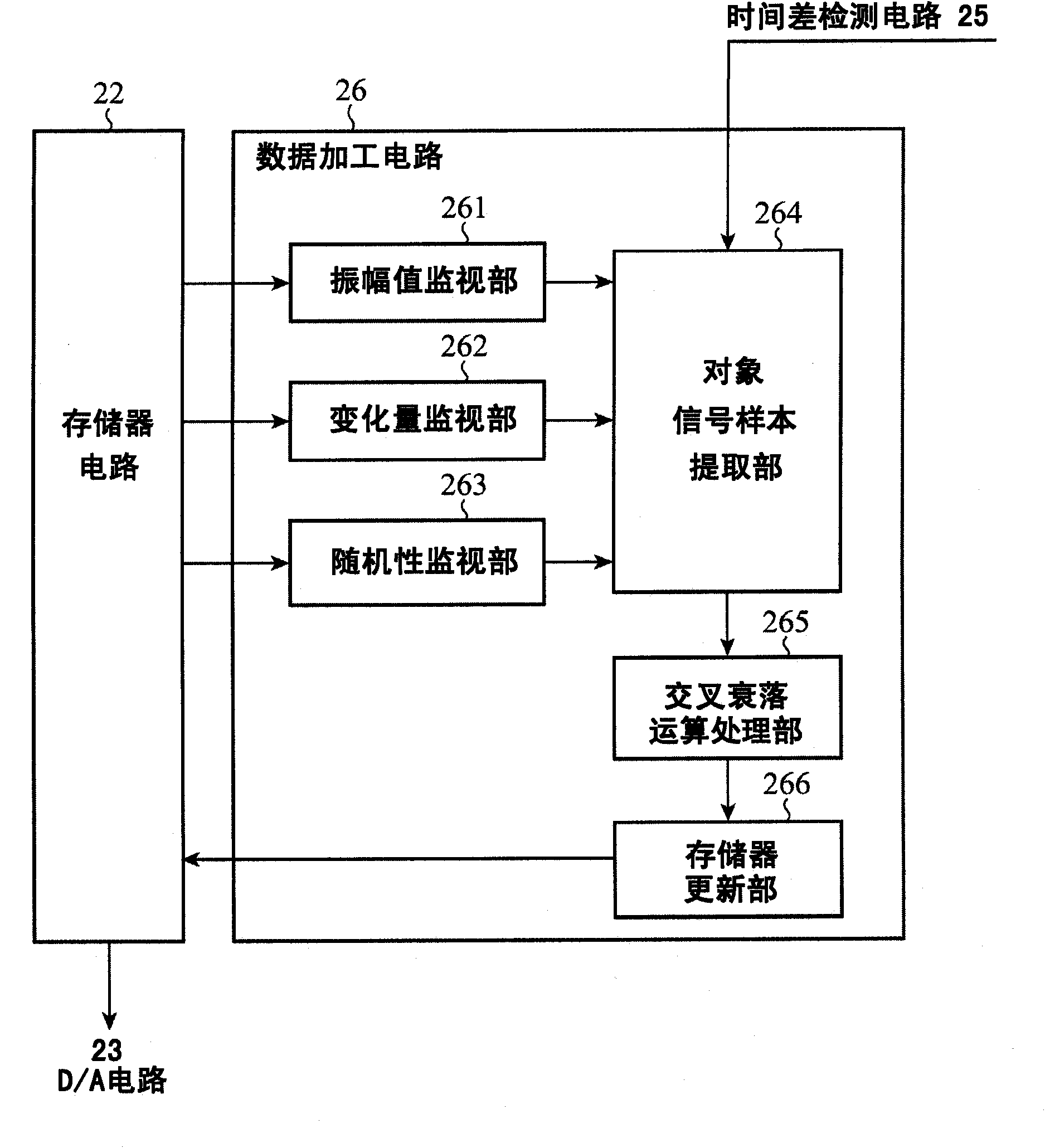

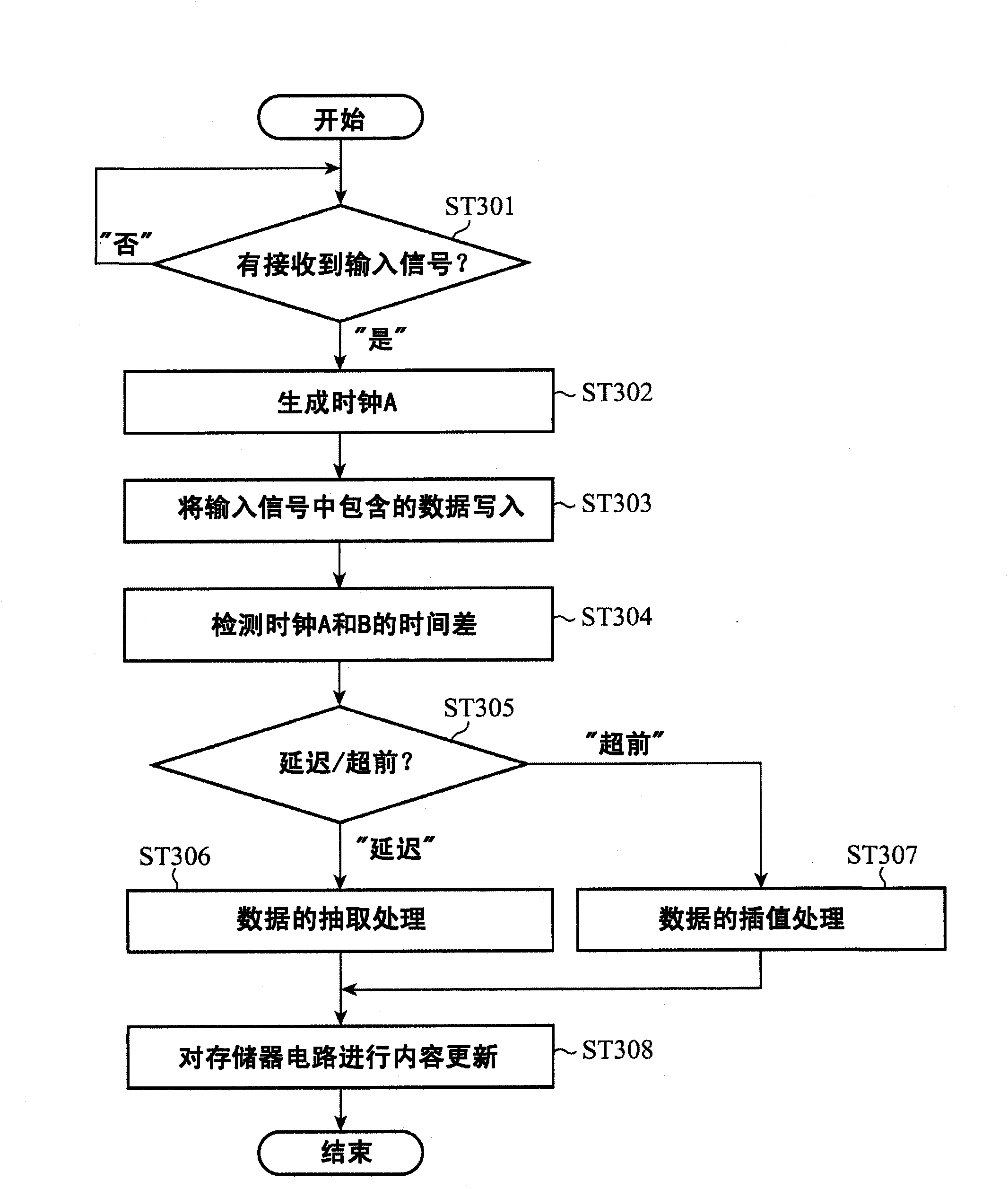

Signal reception device and signal transmission system

InactiveCN102113049AReduce time skewReduce jitterTelevision system detailsModification of read/write signalsMemory circuitsComputer science

A signal reception device (2) includes a memory circuit (22). Data contained in a digital input signal transmitted from a signal transmission device (1) is written by using a clock separated / generated from the received digital input signal by using a PLL circuit (21) and read by using a reference clock of crystal accuracy from a reference clock generation circuit (24). Here, a difference between the clock and the reference clock is detected so as to correct the difference to reproduce the digital input signal. If the signal reception device (2) delays as compared to the signal transmission device (1), the data contained in the digital input signal is thinned. If the signal reception device (2) advances as compared to the signal transmission device (1), a signal generated from the preceding and the following digital input signals is interpolated.

Owner:MITSUBISHI ELECTRIC CORP

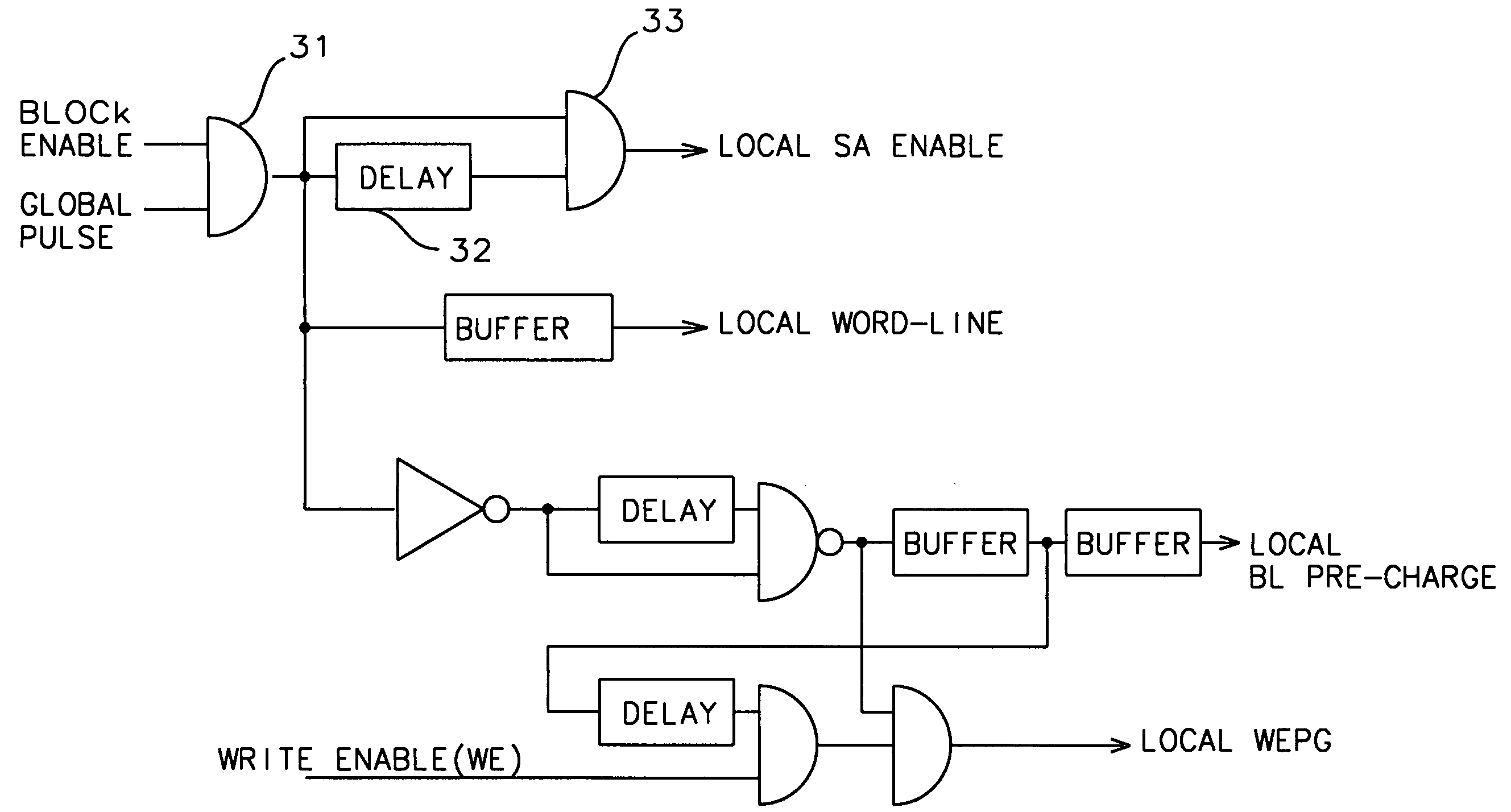

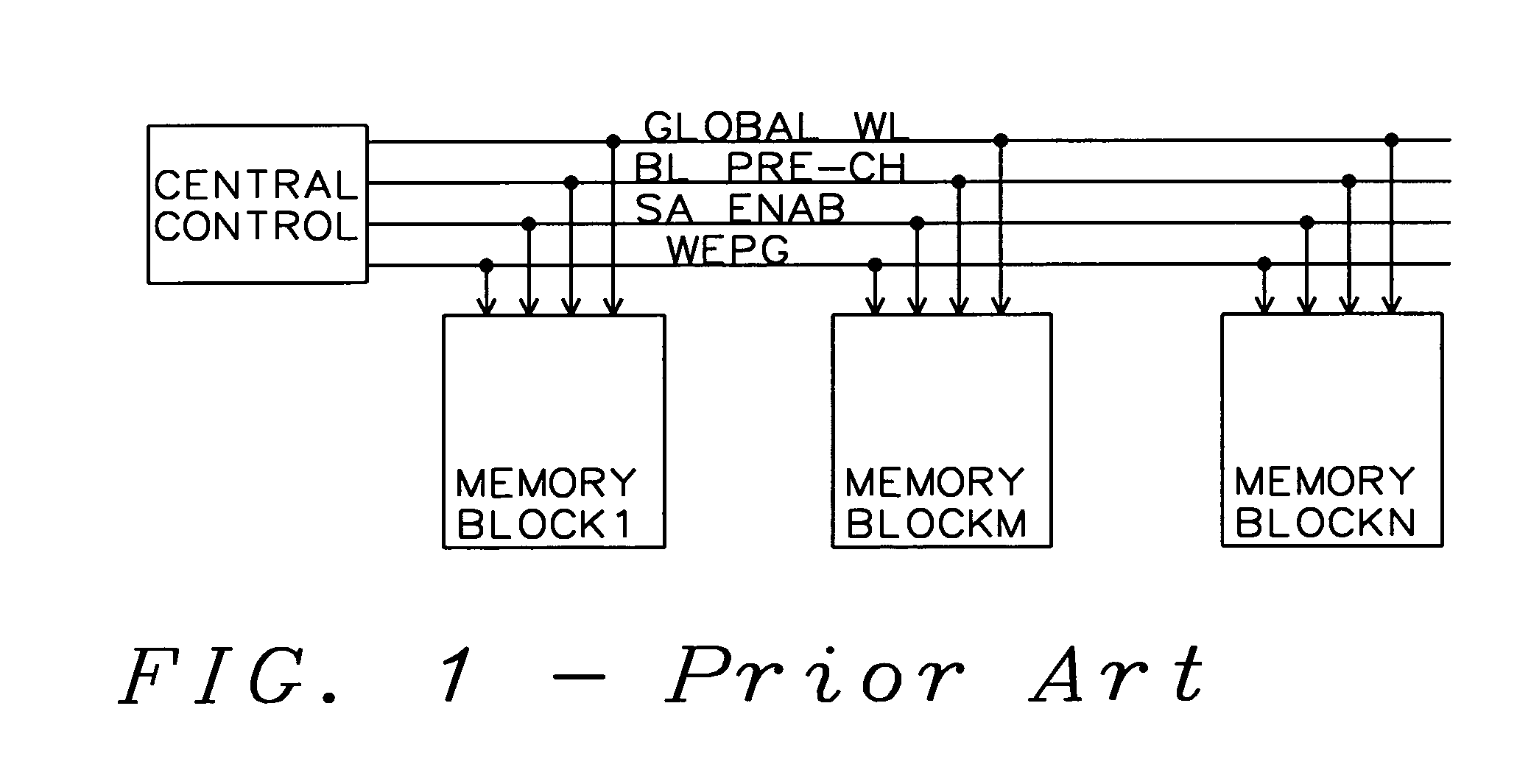

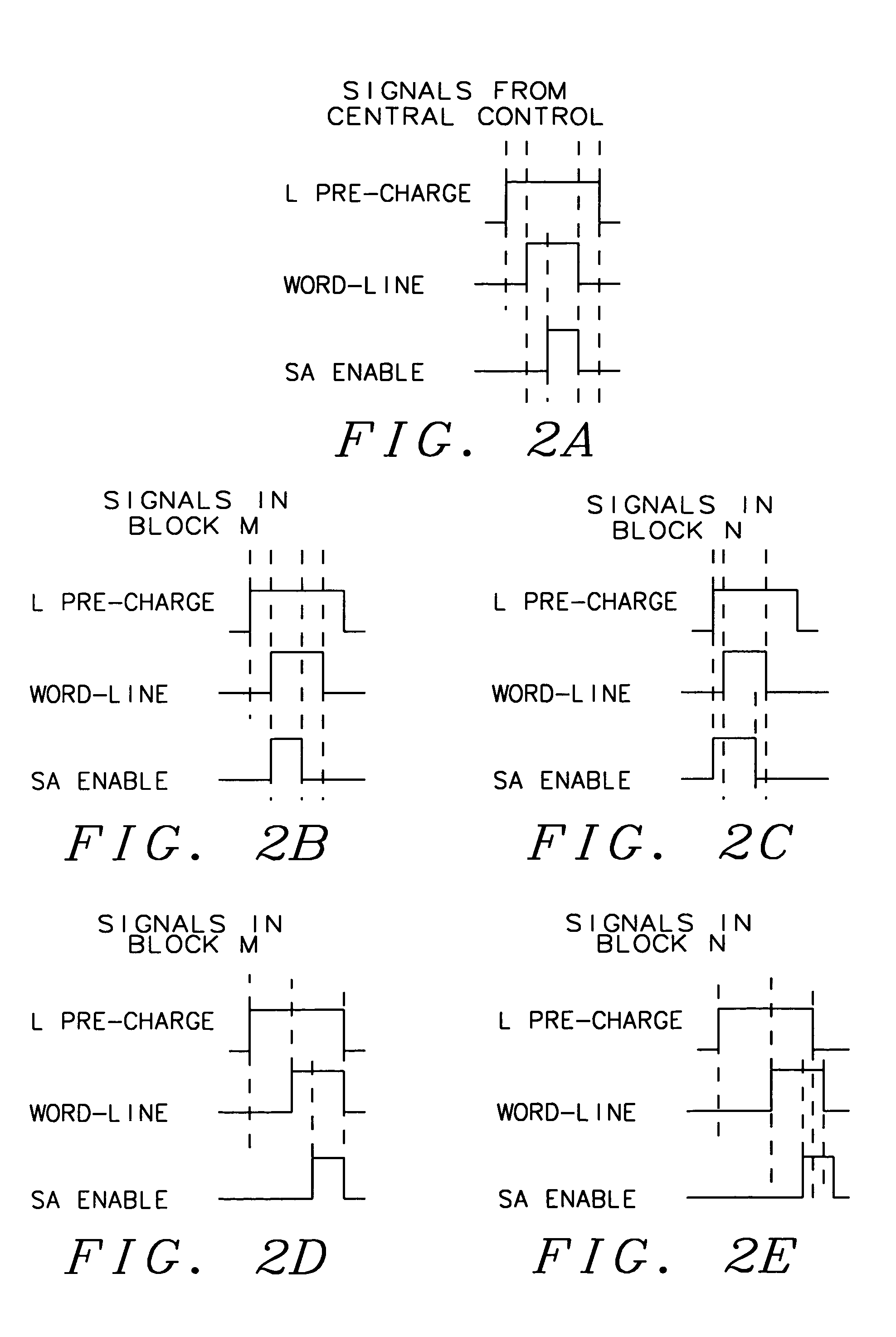

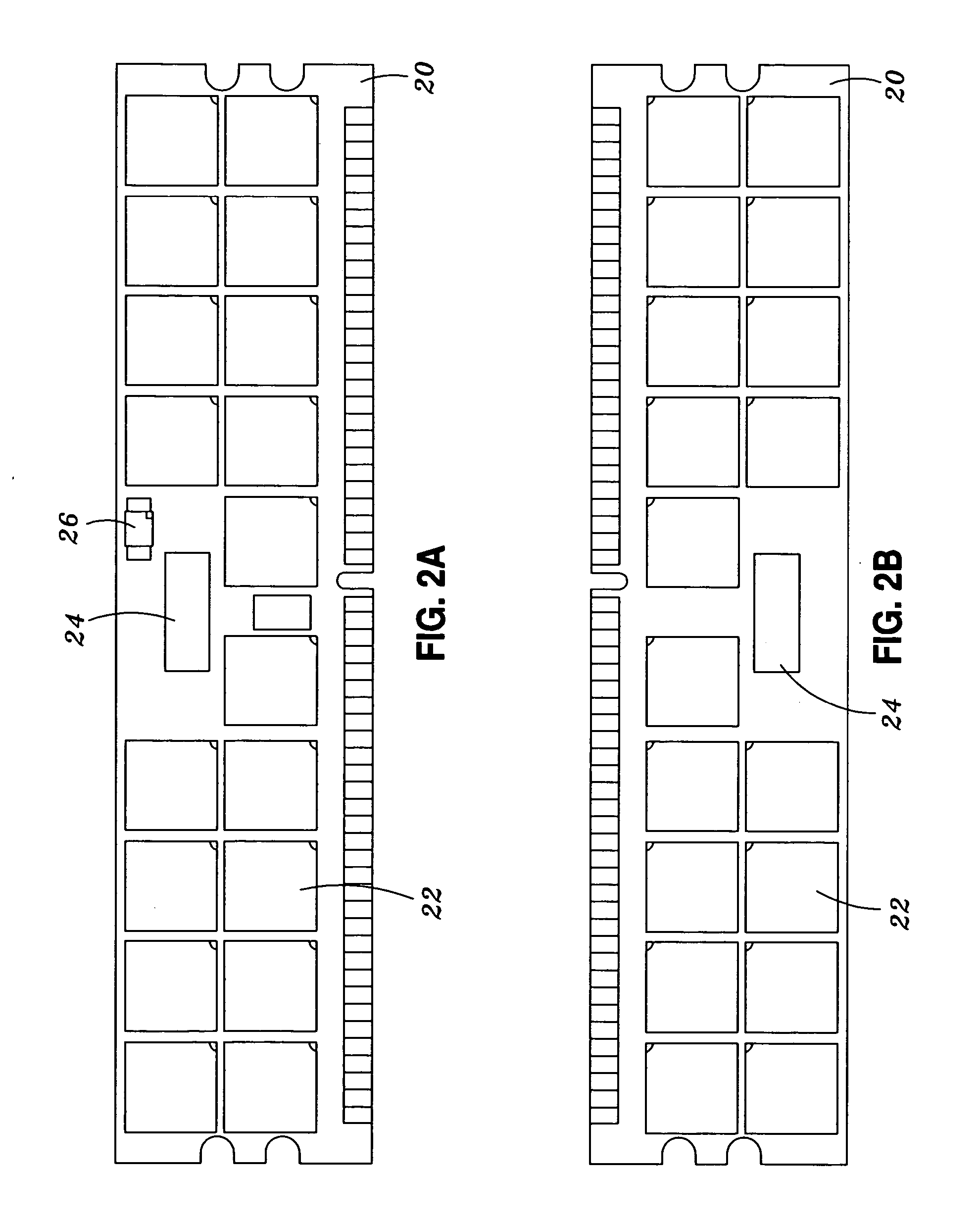

Skew free control of a multi-block SRAM

InactiveUS7356656B1Reduce time skewShorten the timeDigital storageMemory systemsTiming marginComputer architecture

A multi-block SRAM memory system is described where a single global clock pulse is distributed to each memory block from the central control. At each SRAM memory block a local signal generator uses the globally distributed clock pulse to generate the required memory control pulse signals. By generating the memory control pulses locally, instead of distributing these from the central control the variations in skew are greatly reduced. Thus the required timing relationship between memory control signals can be achieved with smaller timing margins. This allows higher speed memory cycle and more reliable memory operation.

Owner:TAIWAN SEMICON MFG CO LTD

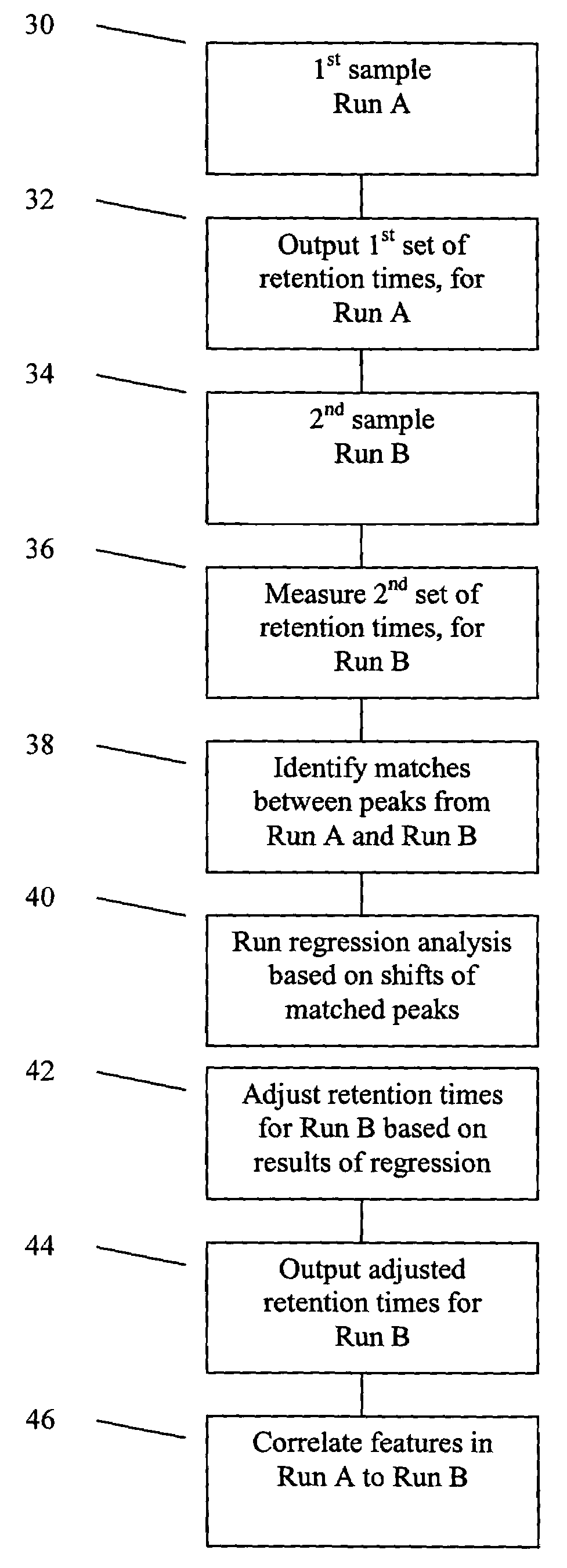

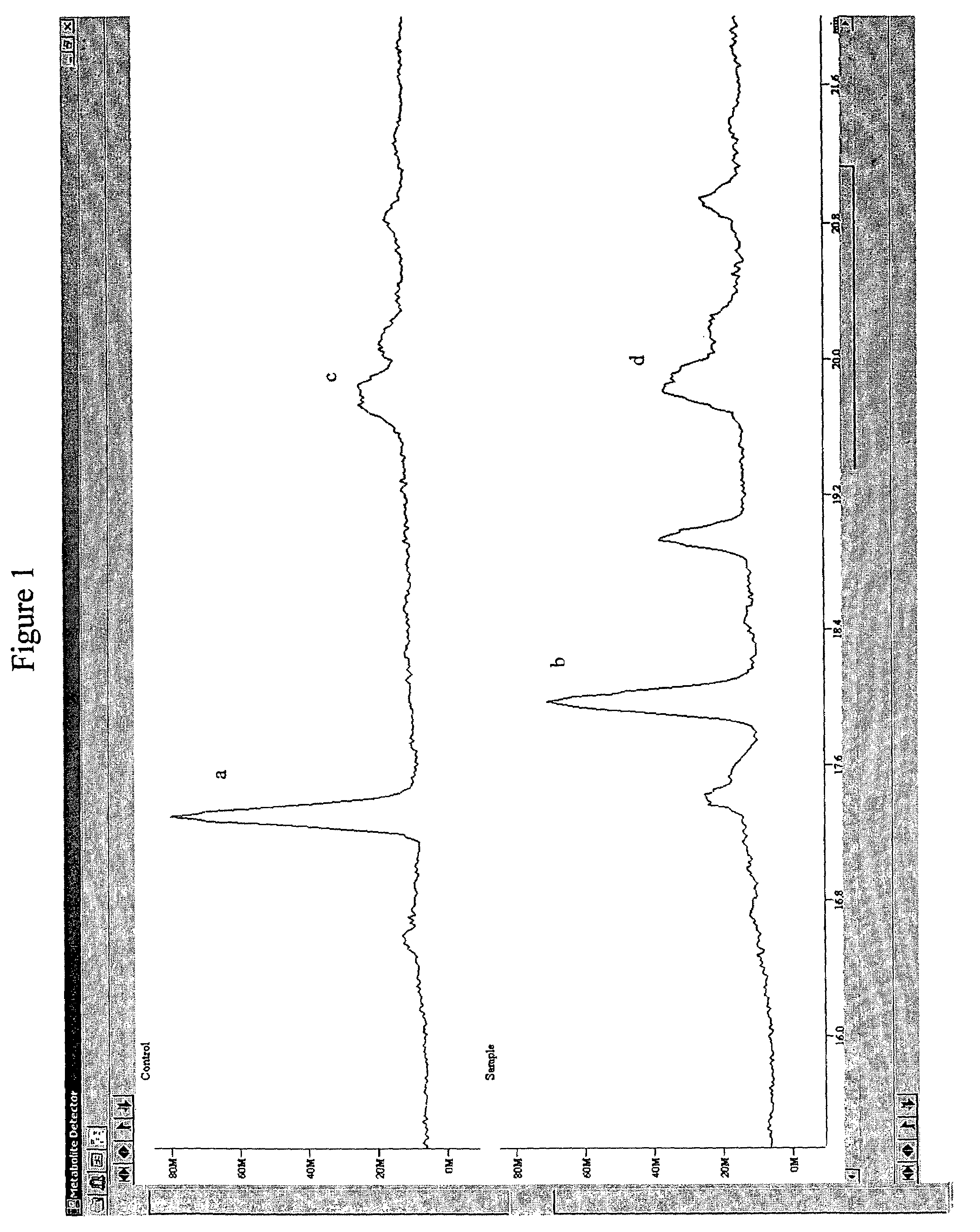

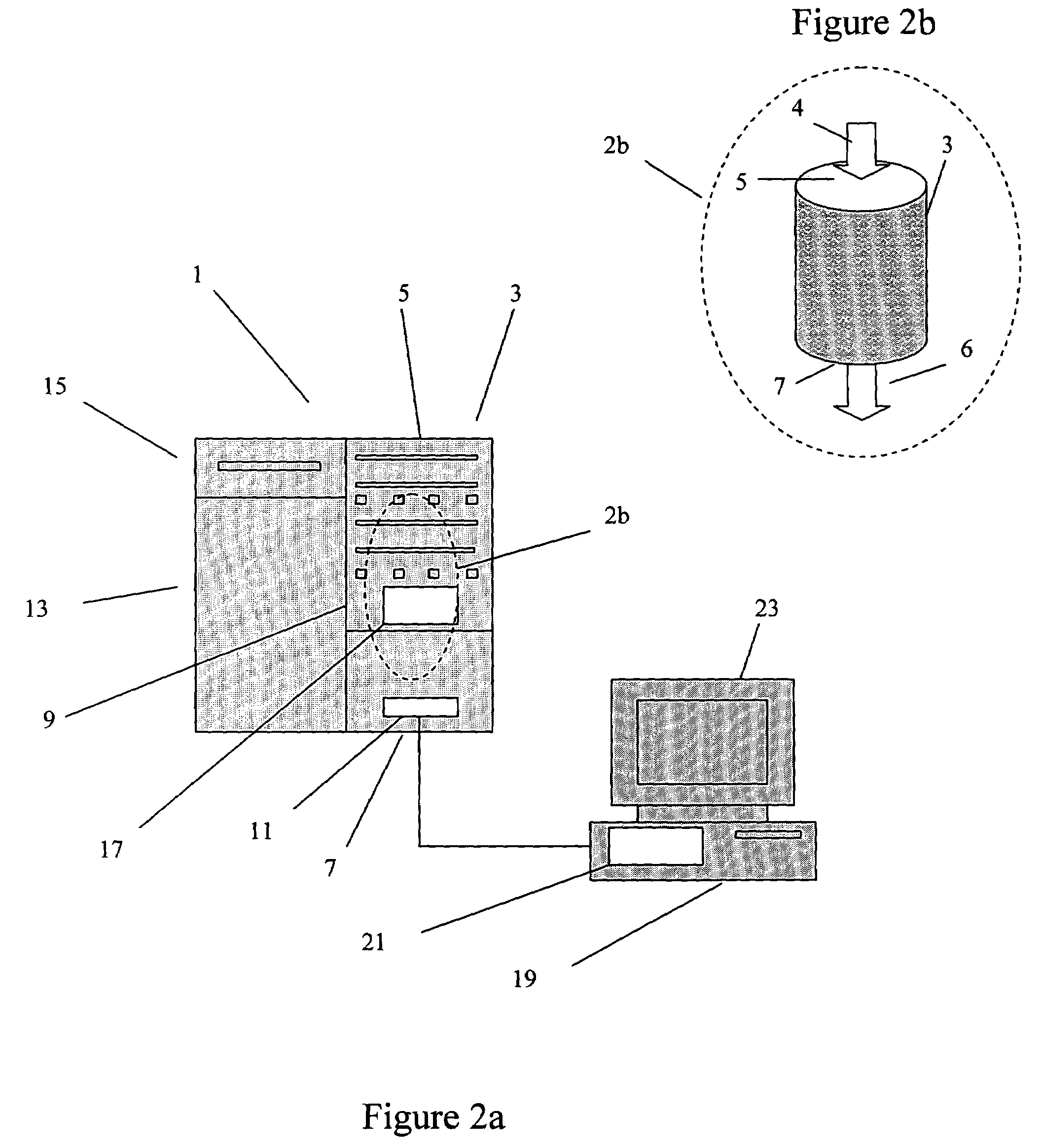

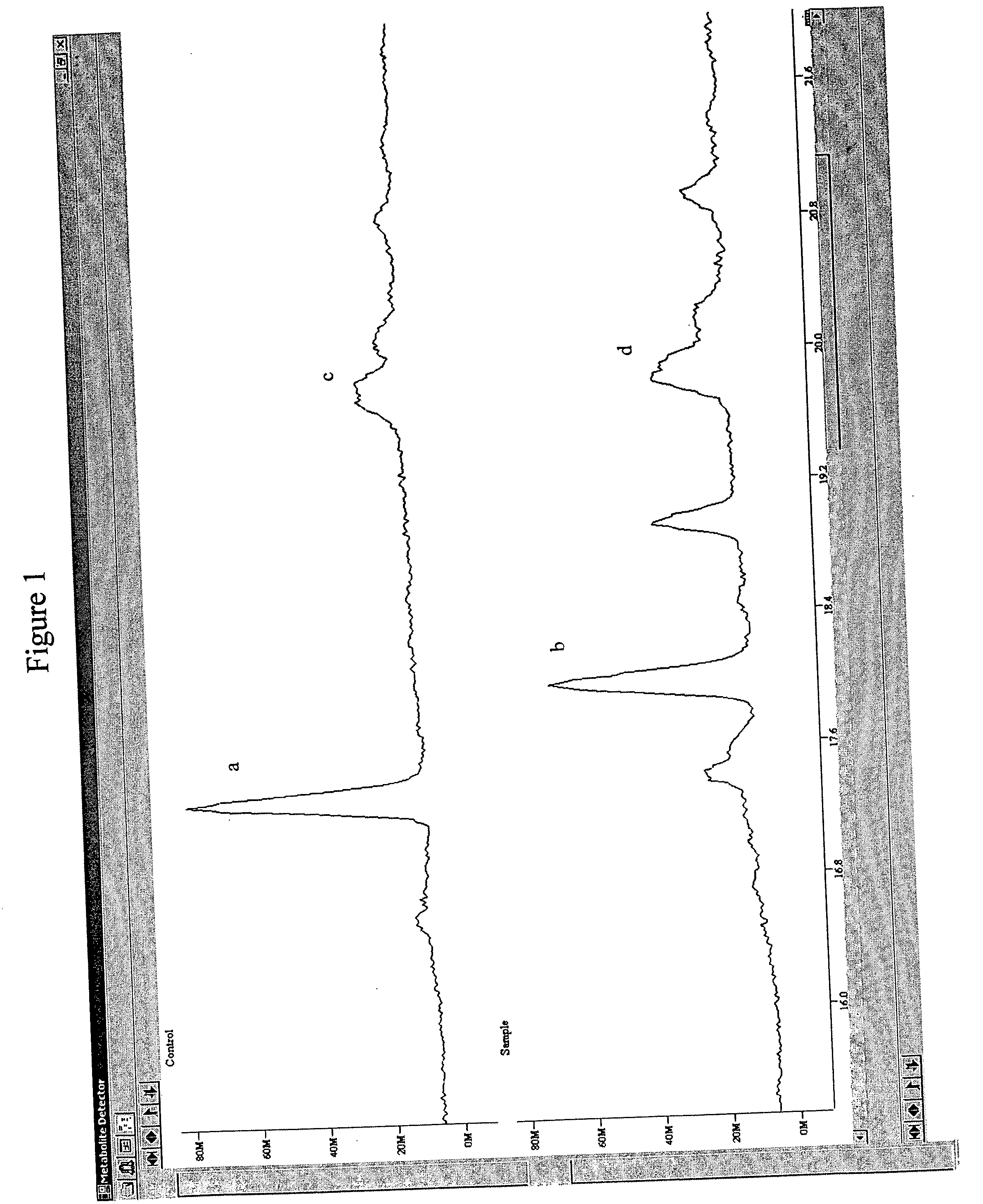

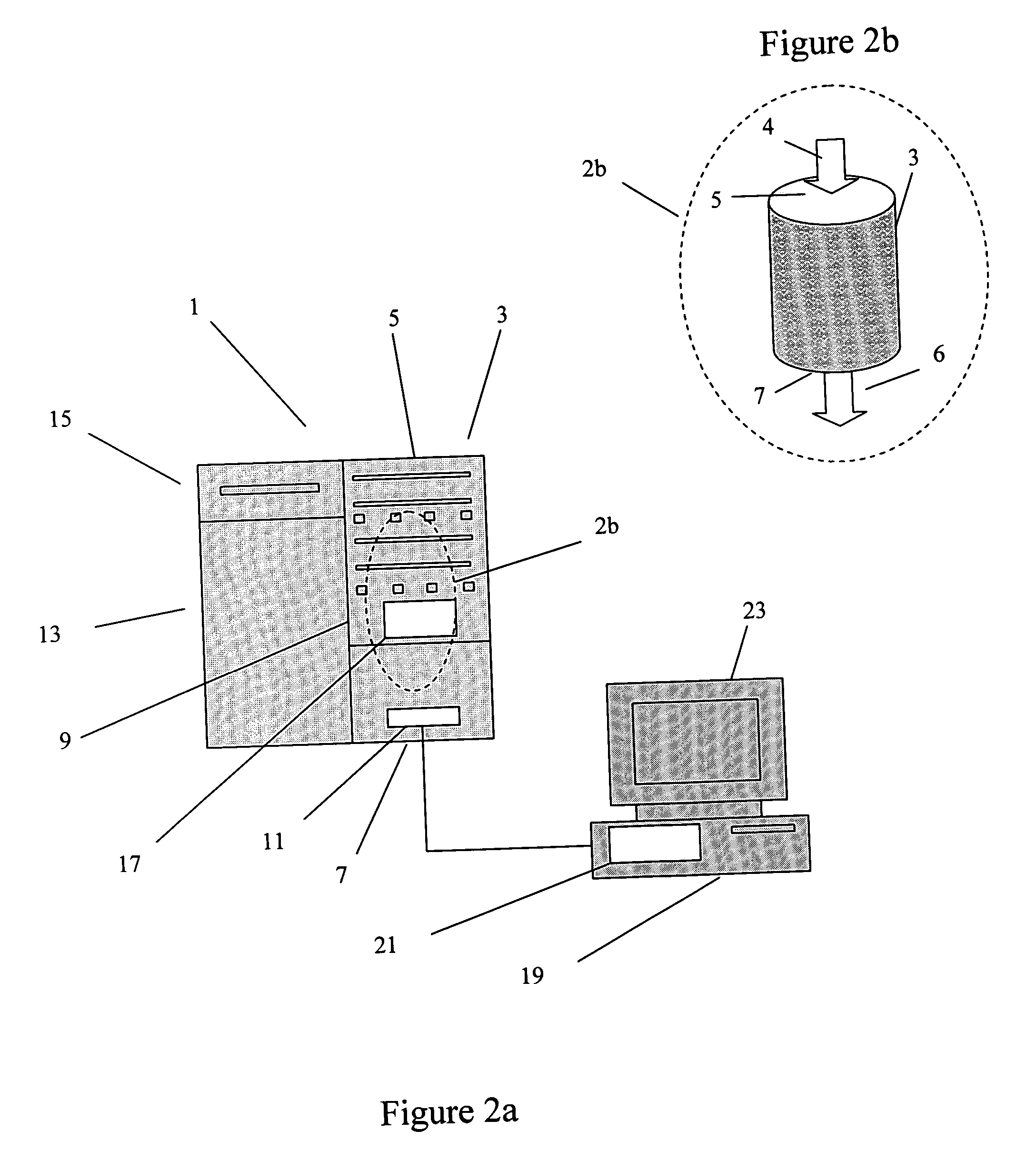

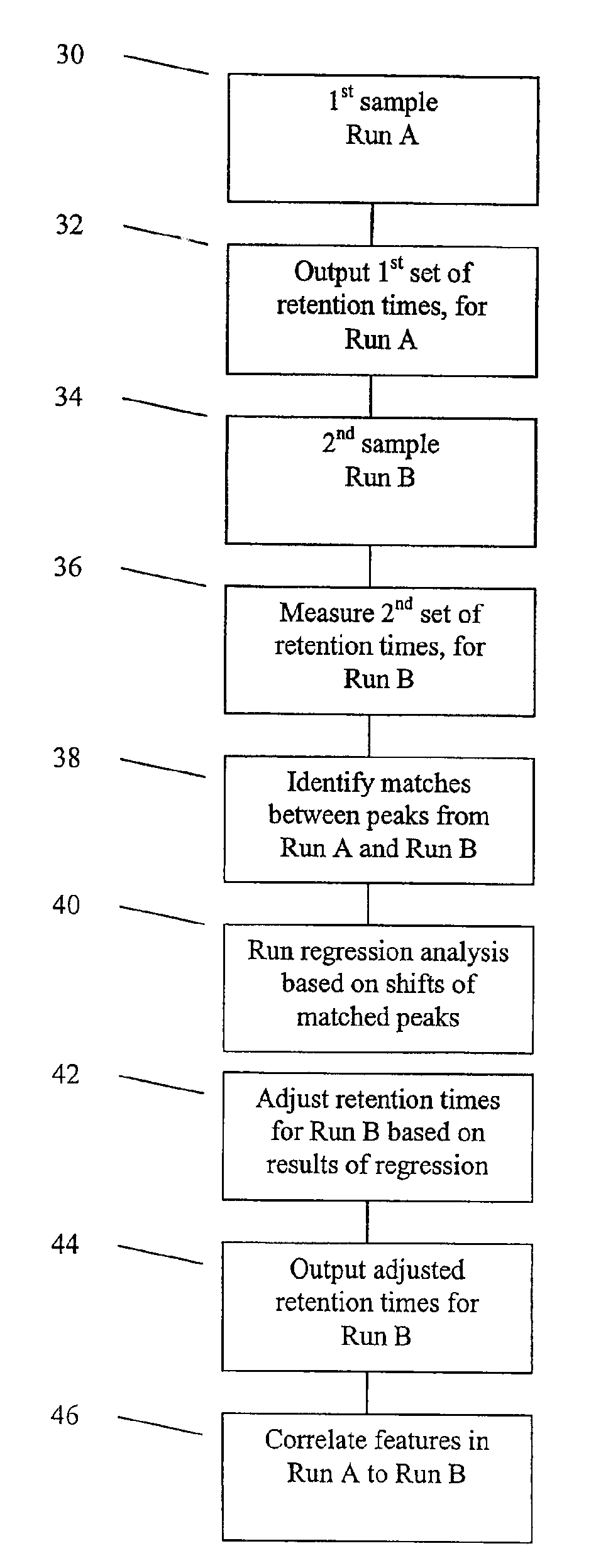

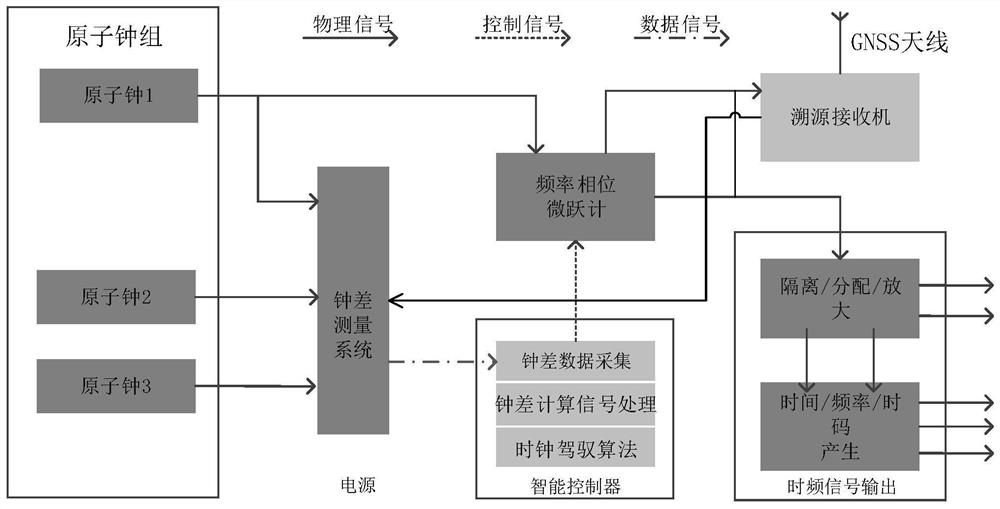

System and method for feature alignment

ActiveUS7635433B2Accurate comparisonReduce probabilityIon-exchange process apparatusComponent separationComputer scienceSeparation column

In a system and method for feature alignment in chromatographic systems, the system runs a first sample through a first separation column. The system determines a first set of features for the first sample run. The system runs a second sample through a second separation column and detects a second set of features for the second sample run. The system estimates a systematic shift in features between the first sample run through the first separation column and the second sample run through the second separation column. The system adjusts the second set of features detected for the second sample run through the second separation column based on the estimated systematic shift to obtain a third set of adjusted features.

Owner:AGILENT TECH INC

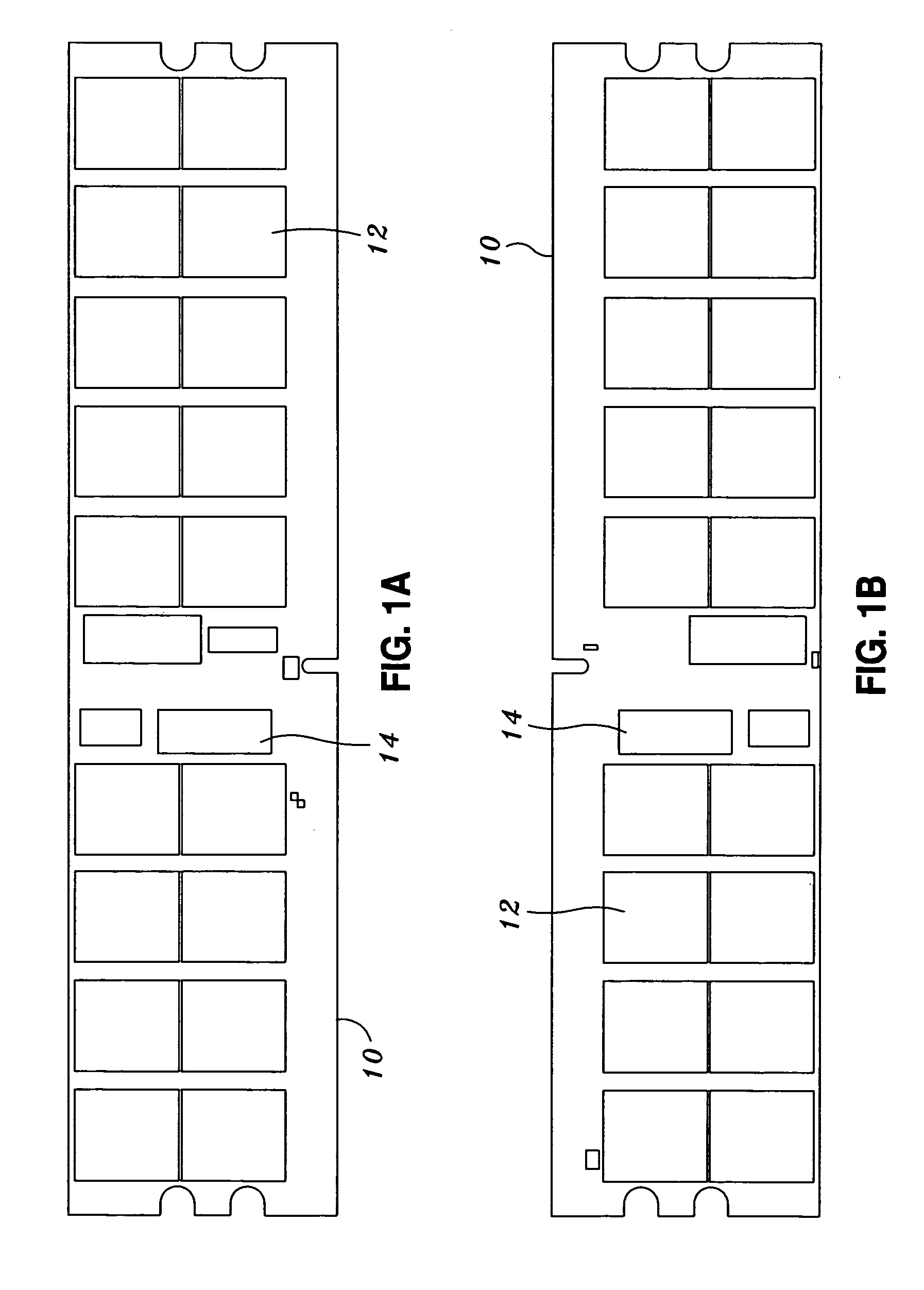

DDR2 SDRAM memory module

InactiveUS20060136658A1Reduce time skewExtension of timeStatic storageMemory systemsMemory chipDDR2 SDRAM

A DDR2 SDRAM memory module having memory chips arranged bilaterally symmetrical on the module. A register chip is arranged on each of two faces of the memory module, with each register chip coupled to half of the memory chips.

Owner:HGST TECH SANTA ANA

Methods and apparatus for reducing timing skew

InactiveUS7509609B2Reduce distanceReduce time skewCAD circuit designSoftware simulation/interpretation/emulationComputerized systemEngineering

Reducing timing skew begins with identifying signals that are to have a reduced timing skew. These identified signals are then routed to reduce the layout distance of each signal path. Among these identified signals, a longest signal path is found and the signal paths of the remaining identified signals are lengthened. The lengthening is done to each of the remaining identified signal paths to each have a length substantially equal to the longest signal path whereby the timing skew between the identified signals is reduced. A signal length matching process may be stored as a program in a computer-readable medium with the program operable on a computer system tailored for providing chip placement and routing processes.

Owner:BELL SEMICON LLC

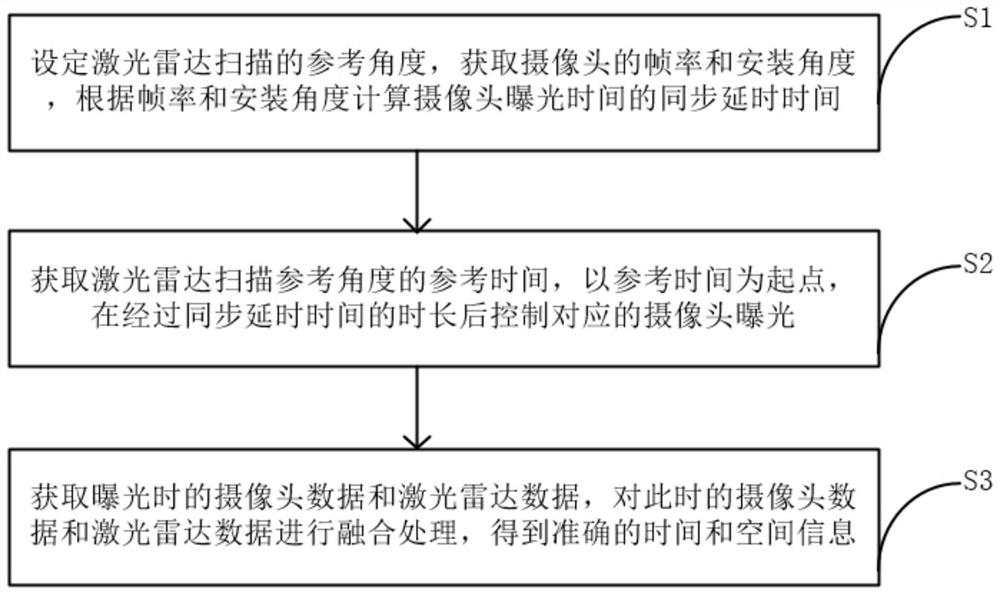

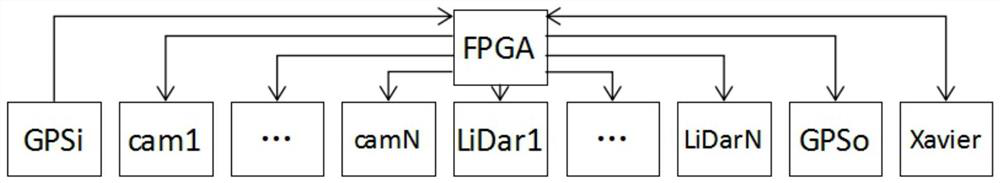

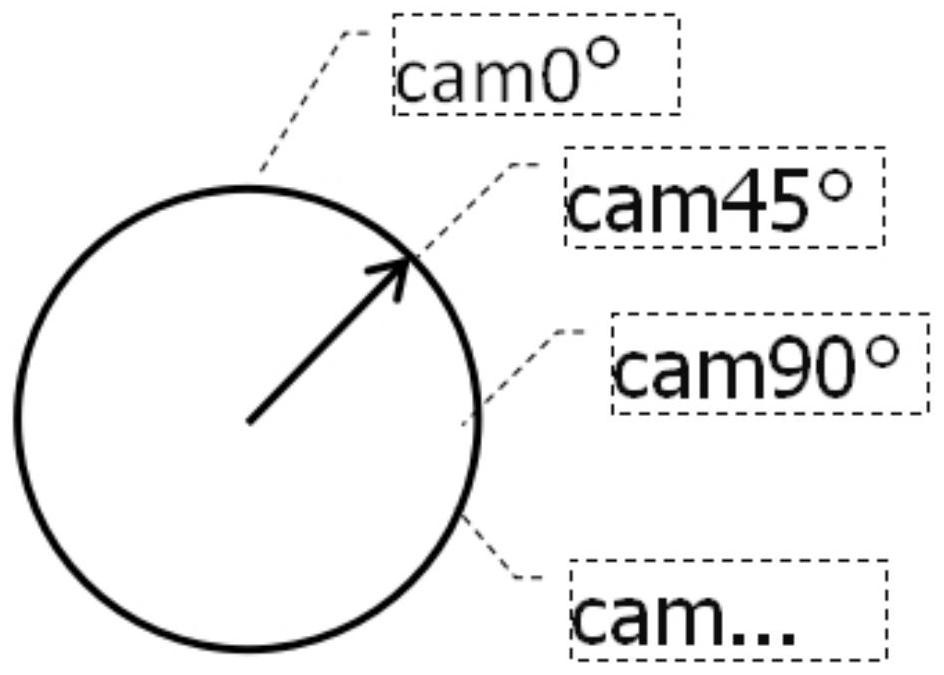

Camera and laser radar synchronization method and system of intelligent driving control system

The invention provides a camera and laser radar synchronization method and system of an intelligent driving control system, and the method comprises the steps: calculating the synchronization delay time of the exposure time of the camera according to the frame rate and the installation angle of the camera, and enabling the exposure time to be just the same as the time when the laser radar scans the angle; at the moment, laser radar data and camera data can be subjected to fusion processing, and accurate time and space information is obtained.

Owner:环宇智行科技(苏州)有限公司

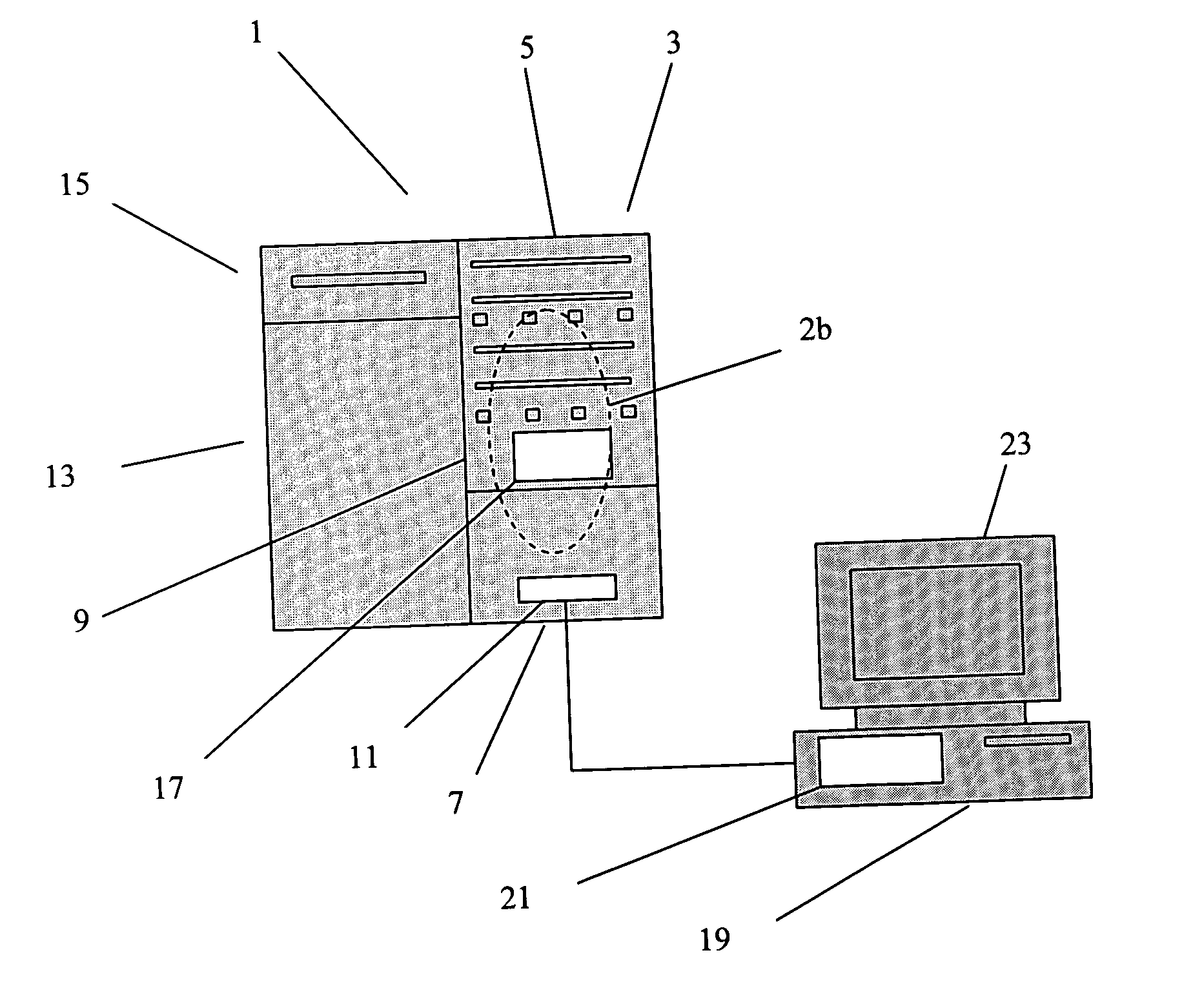

System and method for feature allignment

ActiveUS20070045190A1Reduce overall retention time deviationSmall sizeIon-exchange process apparatusComponent separationComputer scienceSeparation column

In a system and method for feature alignment in chromatographic systems, the system runs a first sample through a first separation column. The system determines a first set of features for the first sample run. The system runs a second sample through a second separation column and detects a second set of features for the second sample run. The system estimates a systematic shift in features between the first sample run through the first separation column and the second sample run through the second separation column. The system adjusts the second set of features detected for the second sample run through the second separation column based on the estimated systematic shift to obtain a third set of adjusted features.

Owner:AGILENT TECH INC

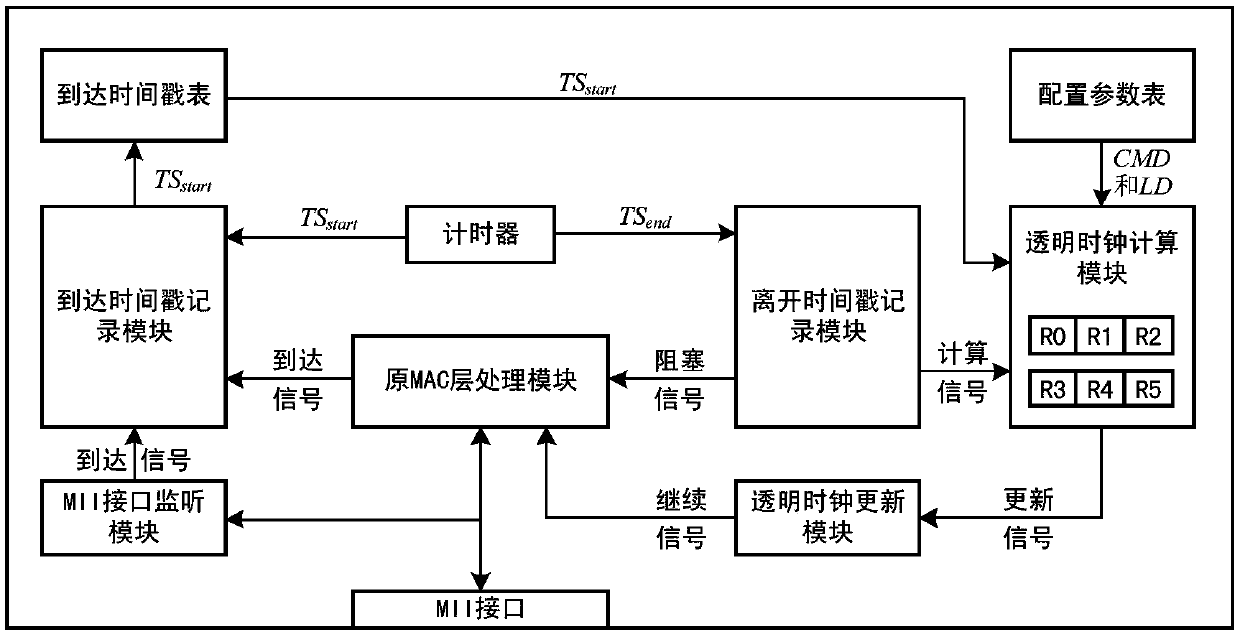

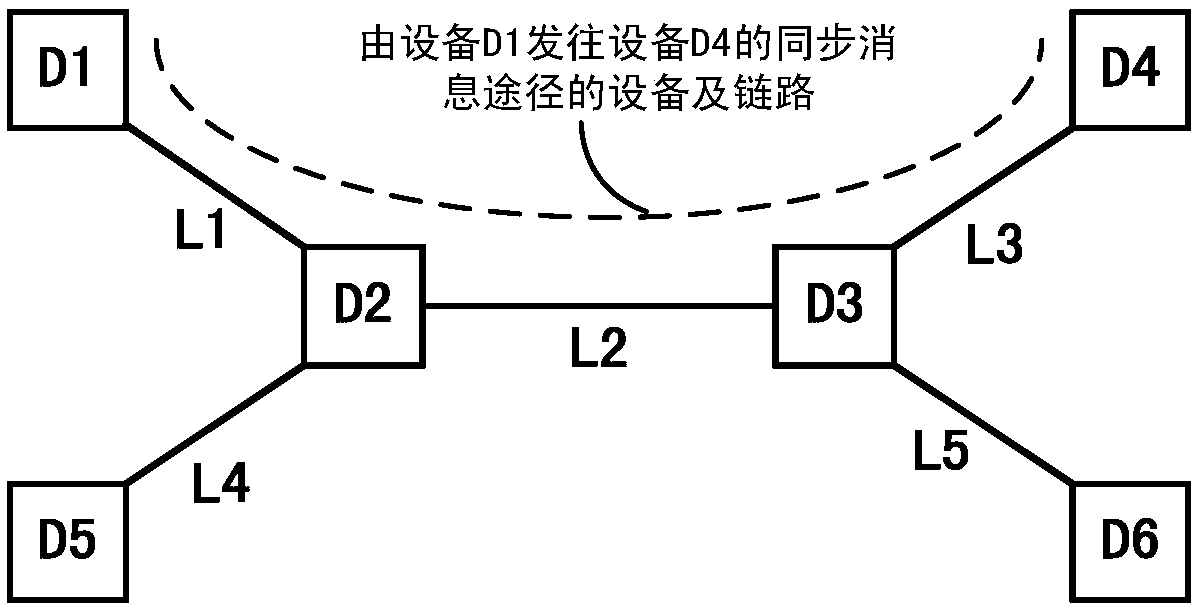

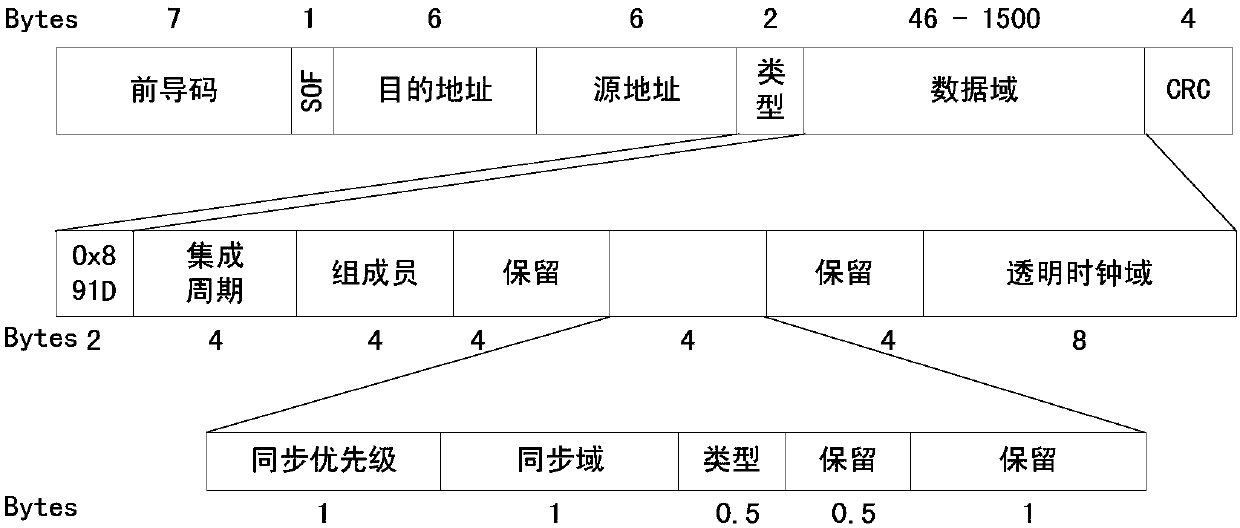

Circuit and method for acquiring and updating transparent clock

Disclosed are a circuit and method for acquiring and updating a transparent clock. The circuit includes an MII interface monitoring module, an arrival timestamp recording module, a timer, an MAC layerprocessing module, a departure timestamp recording module, a transparent clock calculating module, a transparent clock updating module, an arrival timestamp table, and a configuration parameter table. Clock synchronization is one of key technologies in time-triggered Ethernet. The clock synchronization is to maintain the synchronization of clocks of distributed equipment, and the transparent clock technology is one of methods to achieve the clock synchronization. The invention provides a circuit realization method for acquiring and updating the transparent clock. The circuit and method have advantages of being able to quickly acquire a precise transparent clock and timely modify a transparent clock value in a synchronization message, and can provide a basic guarantee for high precision clock synchronization.

Owner:BEIJING INST OF CONTROL ENG

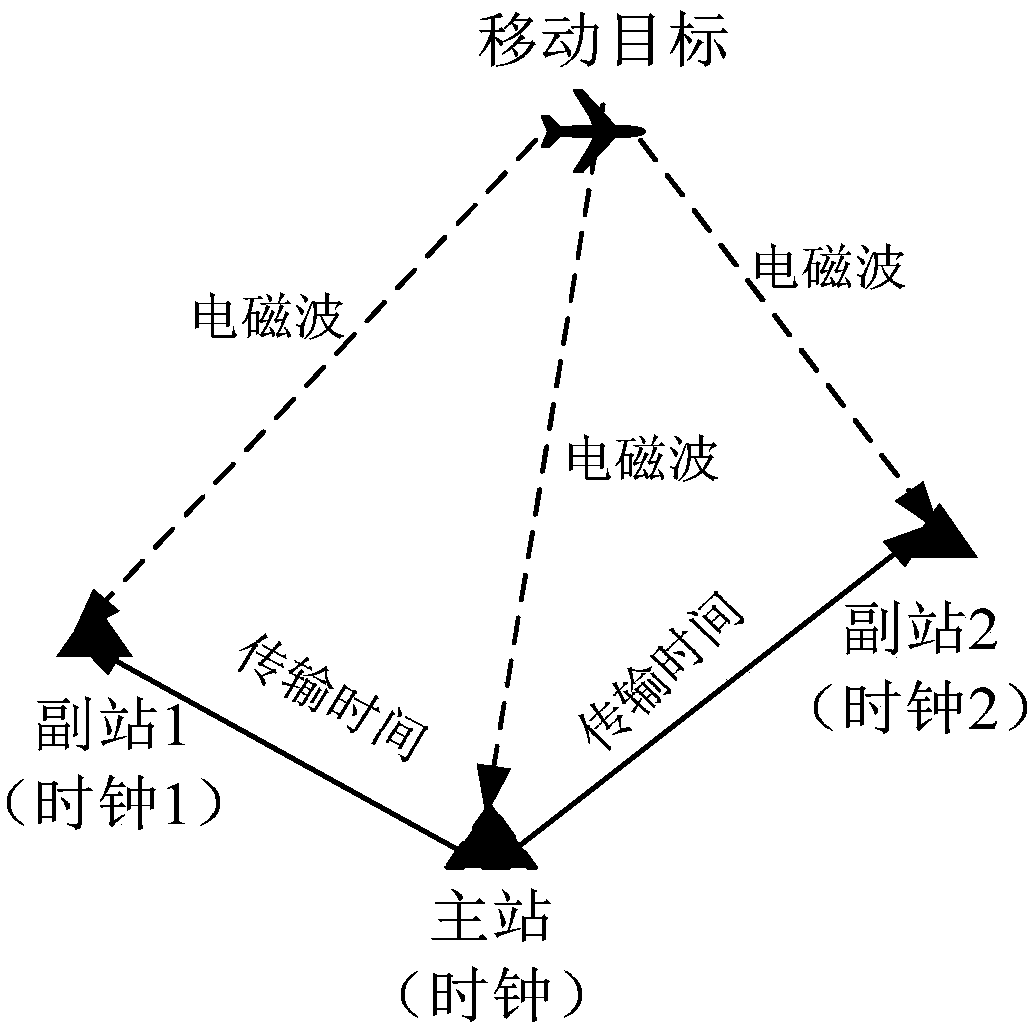

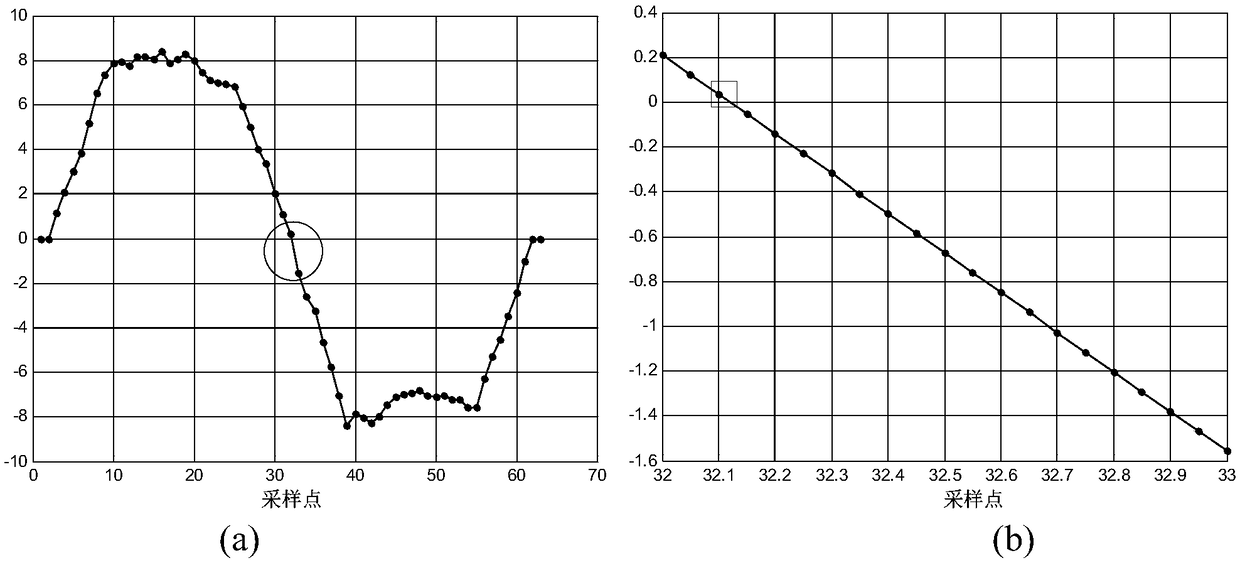

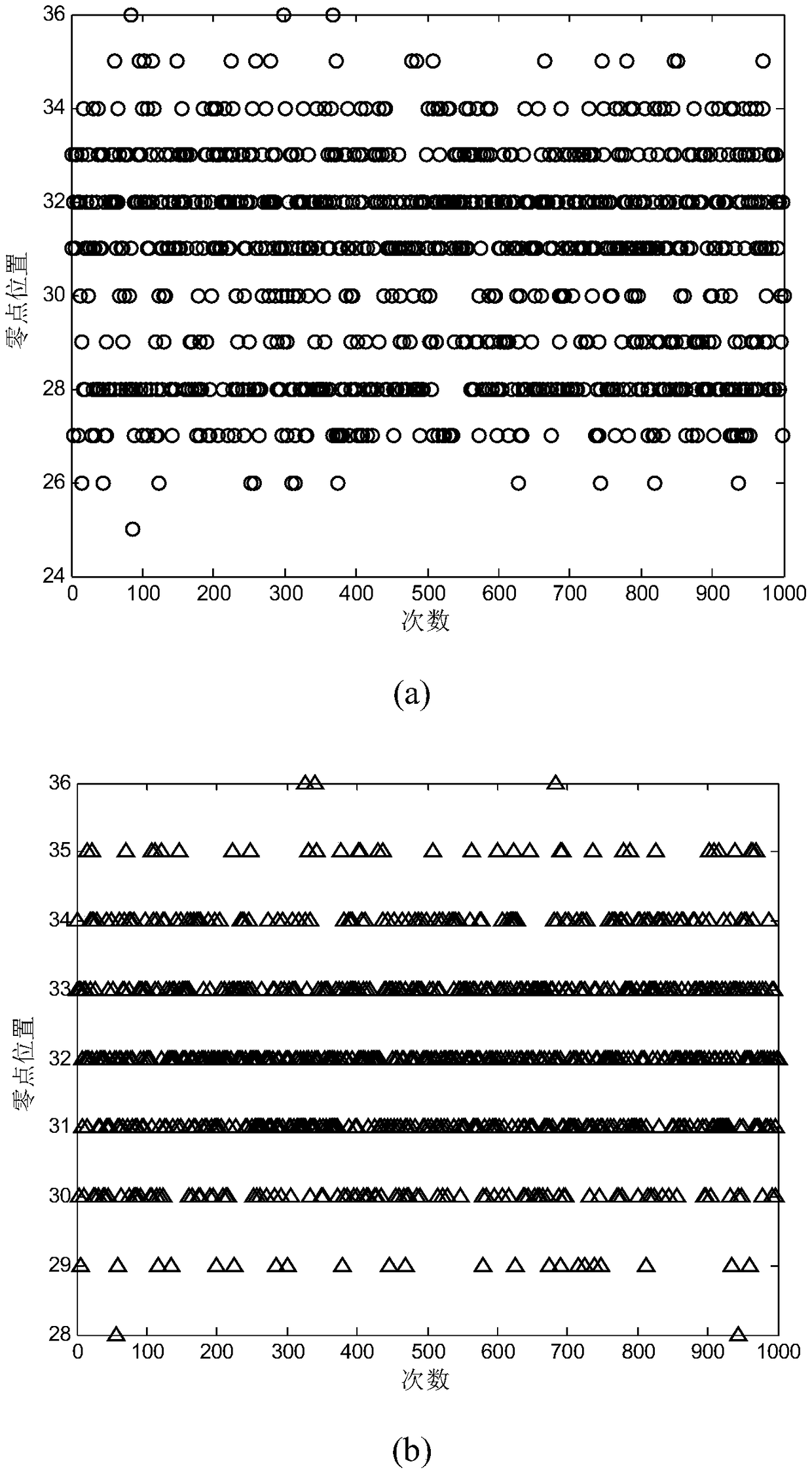

Pulse arrival time stamp marking method based on secondary zero crossing point detection and judgment

InactiveCN108924743AHigh precisionReduce time skewParticular environment based servicesFor mass transport vehiclesSignal-to-noise ratio (imaging)Zero crossing

The invention provides a pulse arrival timestamp marking method based on secondary zero crossing point detection and judgment. According to the method, a time synchronization-based time difference measurement principle is adopted, each of a main station and various secondary stations sets a high-stability and unified time reference, receives a target response signal, detects, judges and digitalizes the target response signal, searches for a signal crossing point, marks a time stamp and acquires the time of arrival of the target response signal, and the main station and the various secondary stations calculate the time of arrival of the target response signal according to the respective time stamps and then transmit the time of arrival to a data processing center; and the data processing center calculates the time difference of arrival according to the time of arrival, and then the position of a target is estimated. The method has the advantages that the time deviations between the marking positions of the time of arrival and the correct time of arrival (the zero crossing points) can be minimized maximally, the purpose of suppressing time of arrival estimation errors caused by zerocrossing point detection is achieved, and the precision of TOA measurement of the base stations can be significantly improved in the environment which is bad in signal-to-noise ratio.

Owner:CIVIL AVIATION UNIV OF CHINA

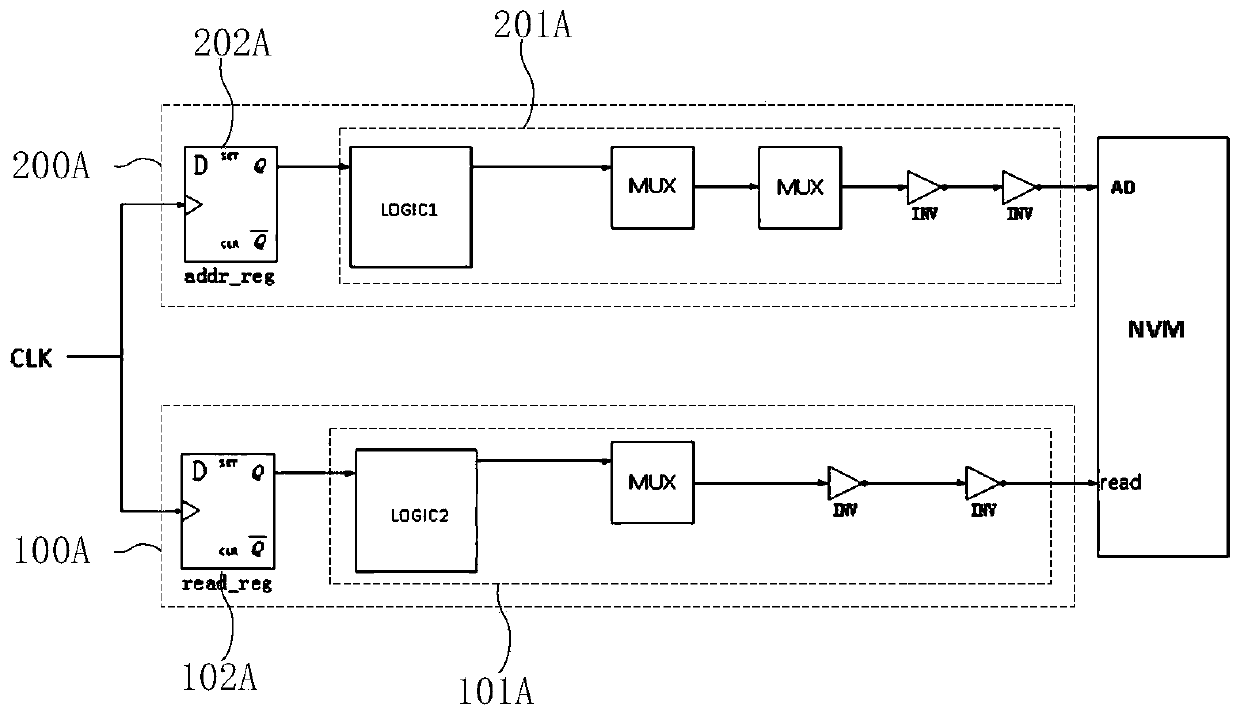

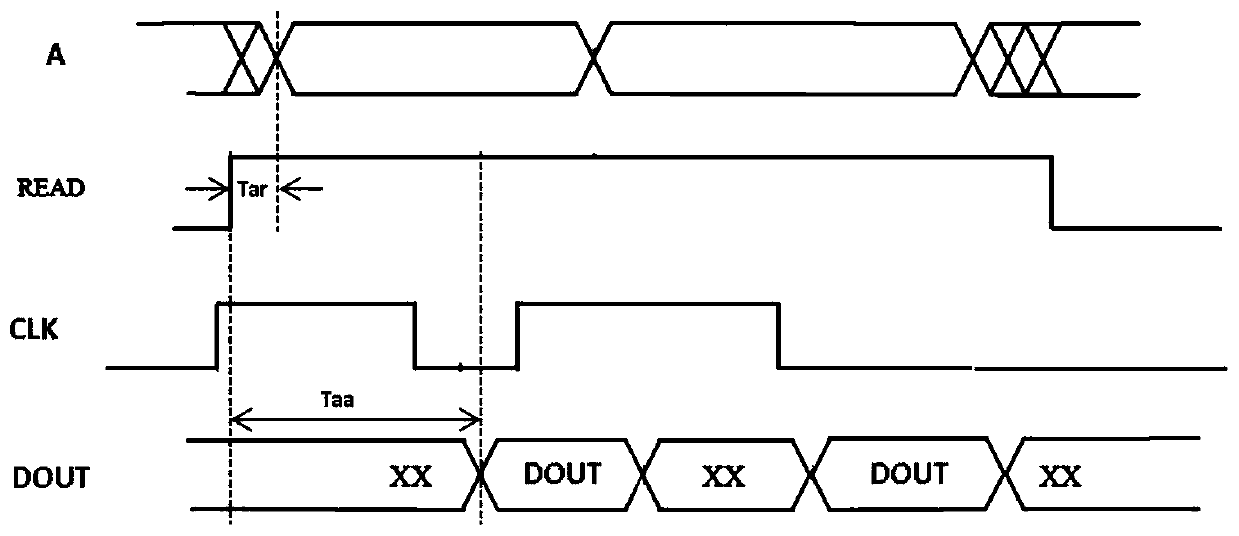

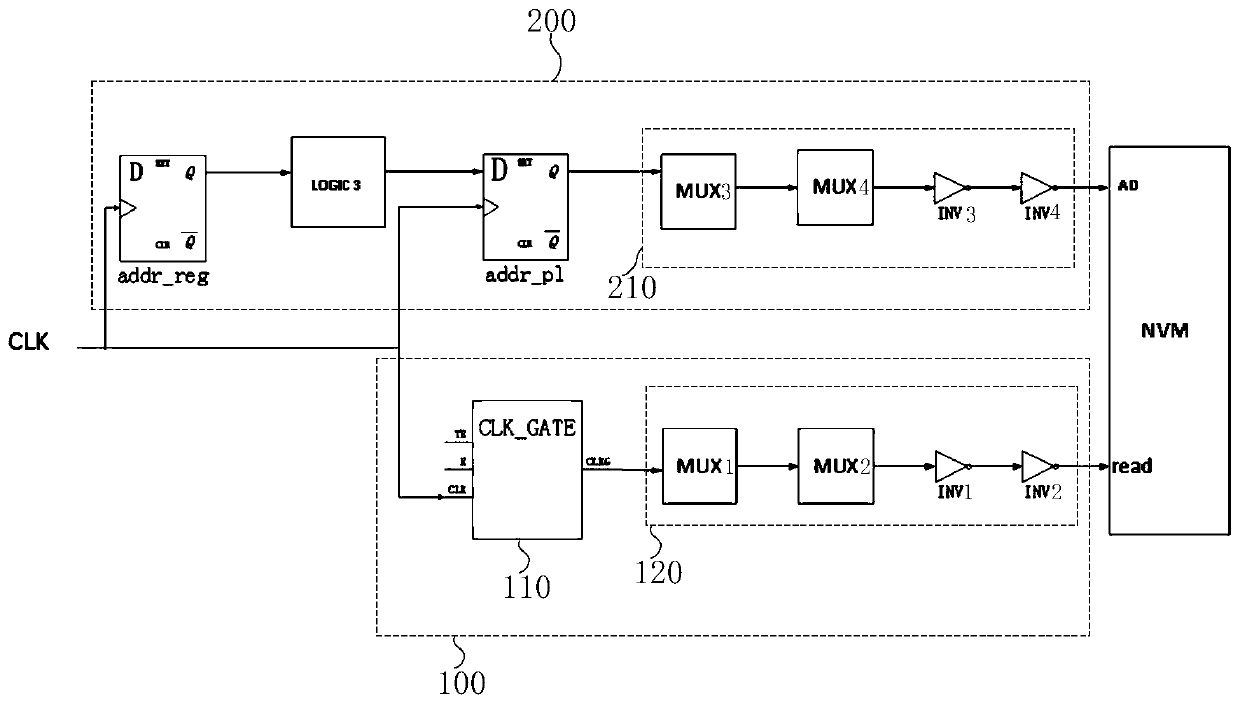

Memory read data test circuit structure and design method thereof

PendingCN111370040AReduce time skewShorten the timeRead-only memoriesDigital storageHemt circuitsControl circuit

The invention relates to the technical field of semiconductor integrated circuits, in particular to a memory read data test circuit structure and a design method thereof. The structure comprises a read signal path which comprises a clock gating unit and a first combinational logic circuit unit; the clock end of the clock gating unit is connected with a synchronous clock signal; the address path comprises an address register unit, a logic control circuit unit, an address latch unit and a second combinational logic circuit unit; wherein the clock end of the address register unit is connected with a synchronous clock signal, the data output end of the address register unit is connected with the input end of the logic control circuit unit, the output end of the logic control circuit unit is connected with the data input end of the address latch unit, and the clock end of the address latch unit is connected with the synchronous clock signal. By means of the read signal generation step, theaddress signal generation step and the address latch step, a synchronous clock is adopted, and the problem that in the related technology, it is complex and difficult to guarantee high-precision timesequence balance can be solved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

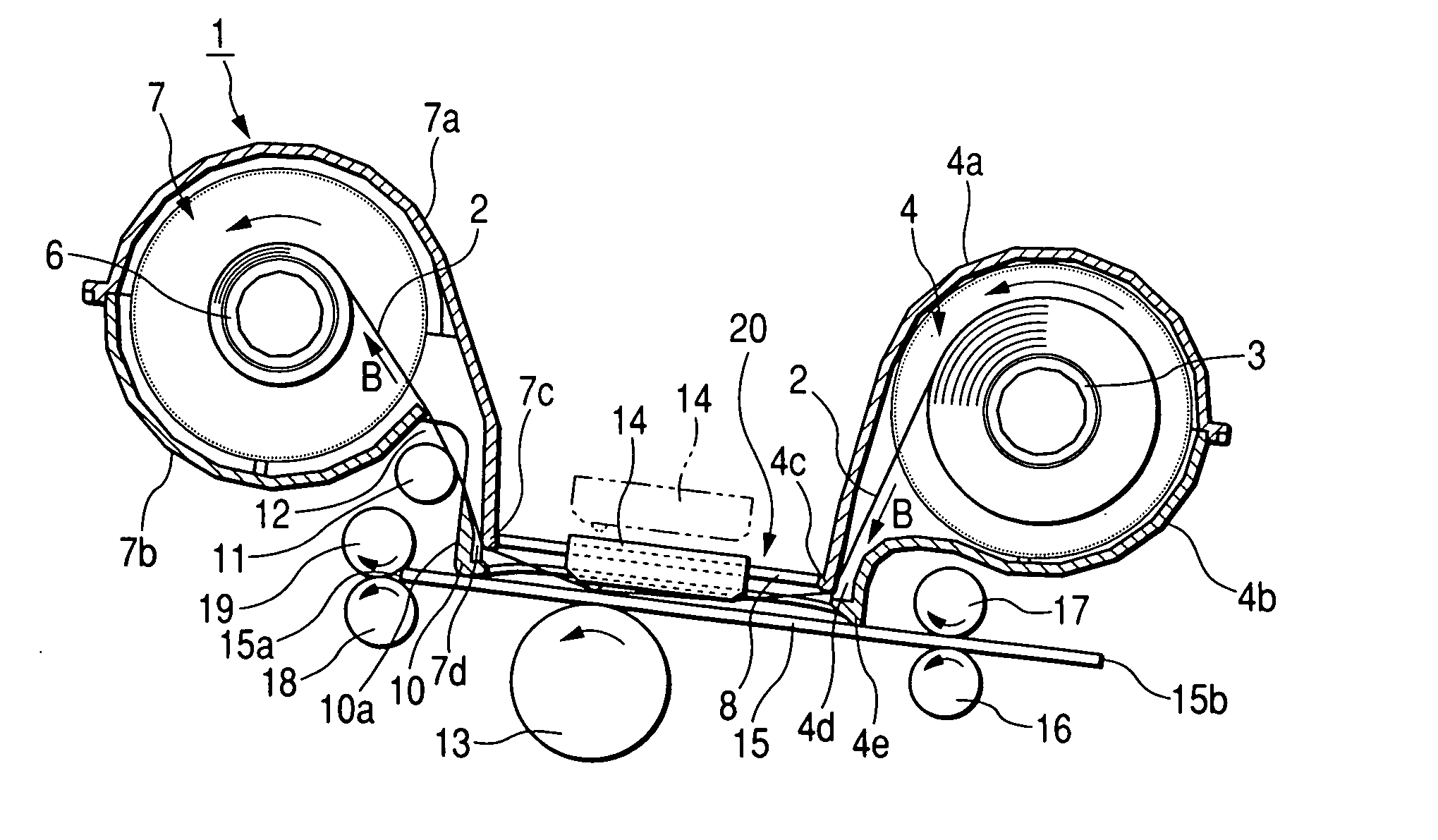

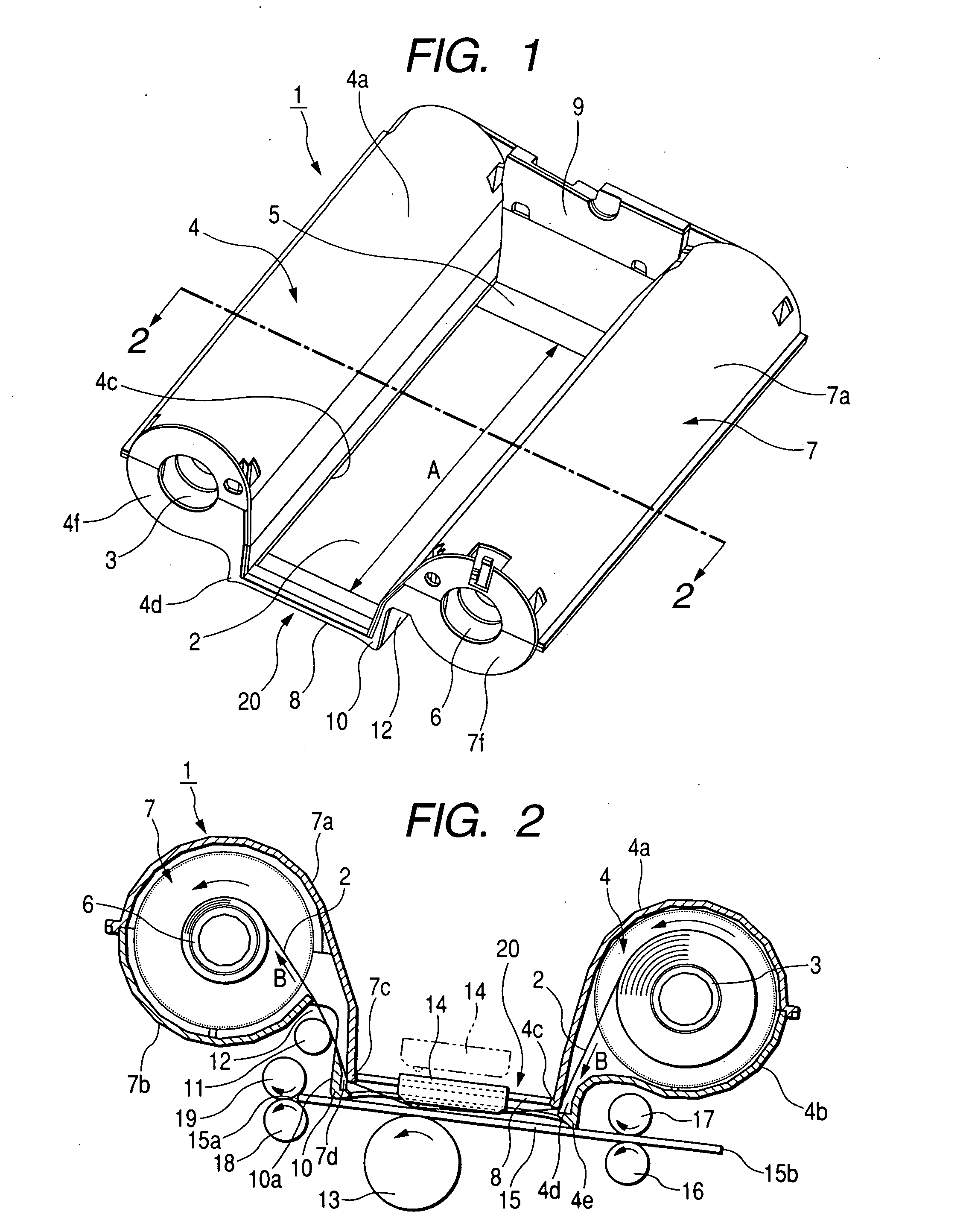

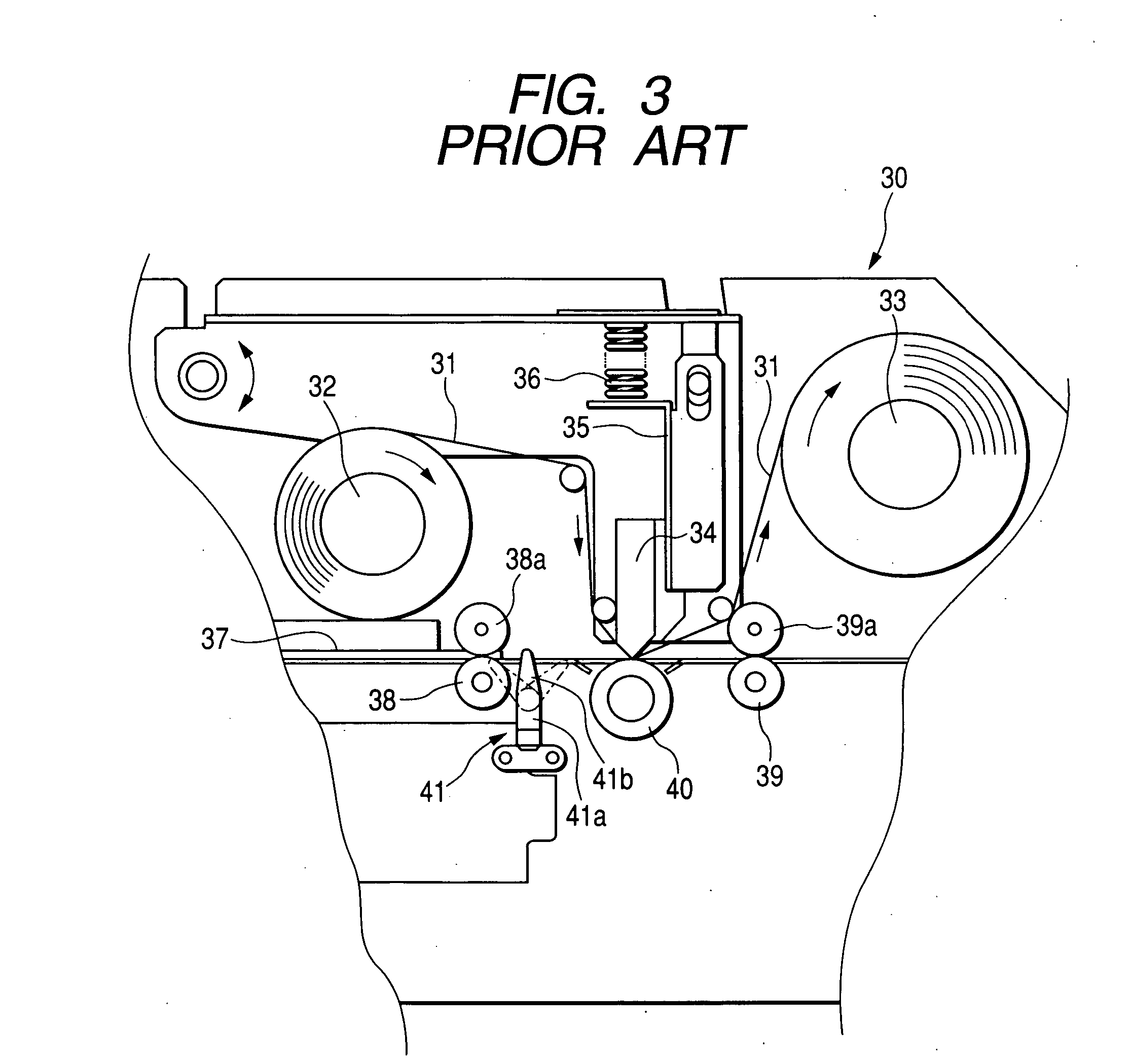

Ink ribbon cassette

InactiveUS20070020010A1Reduces feeding deviationReduce time skewPrinting mechanismsInking apparatusStructural engineeringMechanical engineering

An ink ribbon cassette is provided. The ink ribbon cassette includes a ribbon outlet provided near a first ribbon-receiving part of an ink ribbon cassette of the invention in a head insertion opening. A ribbon winding opening is provided near a second ribbon-receiving part in the head insertion opening. A first paper guide is provided at the ribbon outlet and a second paper guide is provided at the ribbon winding opening so that a recording paper to be fed is guided by the first and second paper guides.

Owner:ALPS ALPINE CO LTD

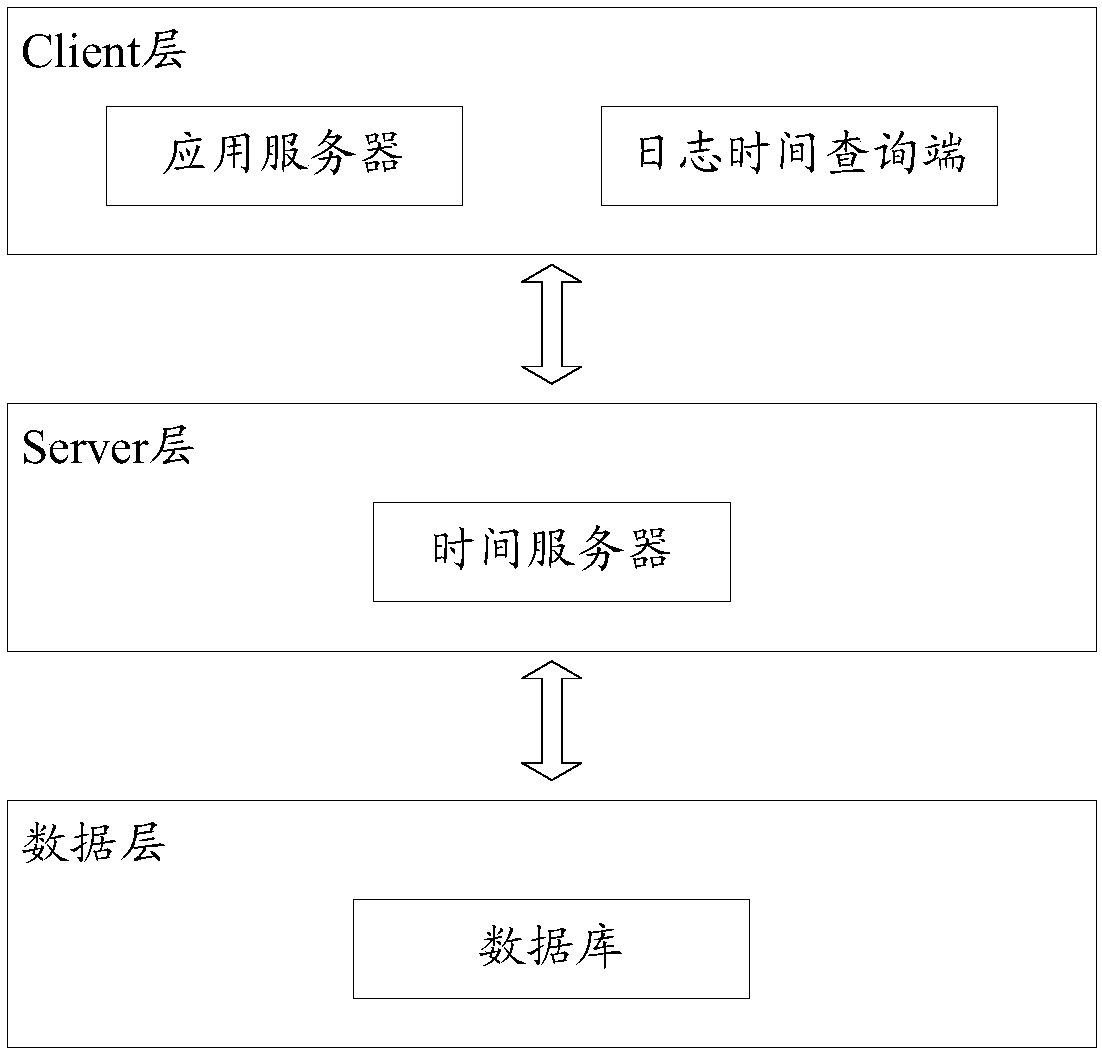

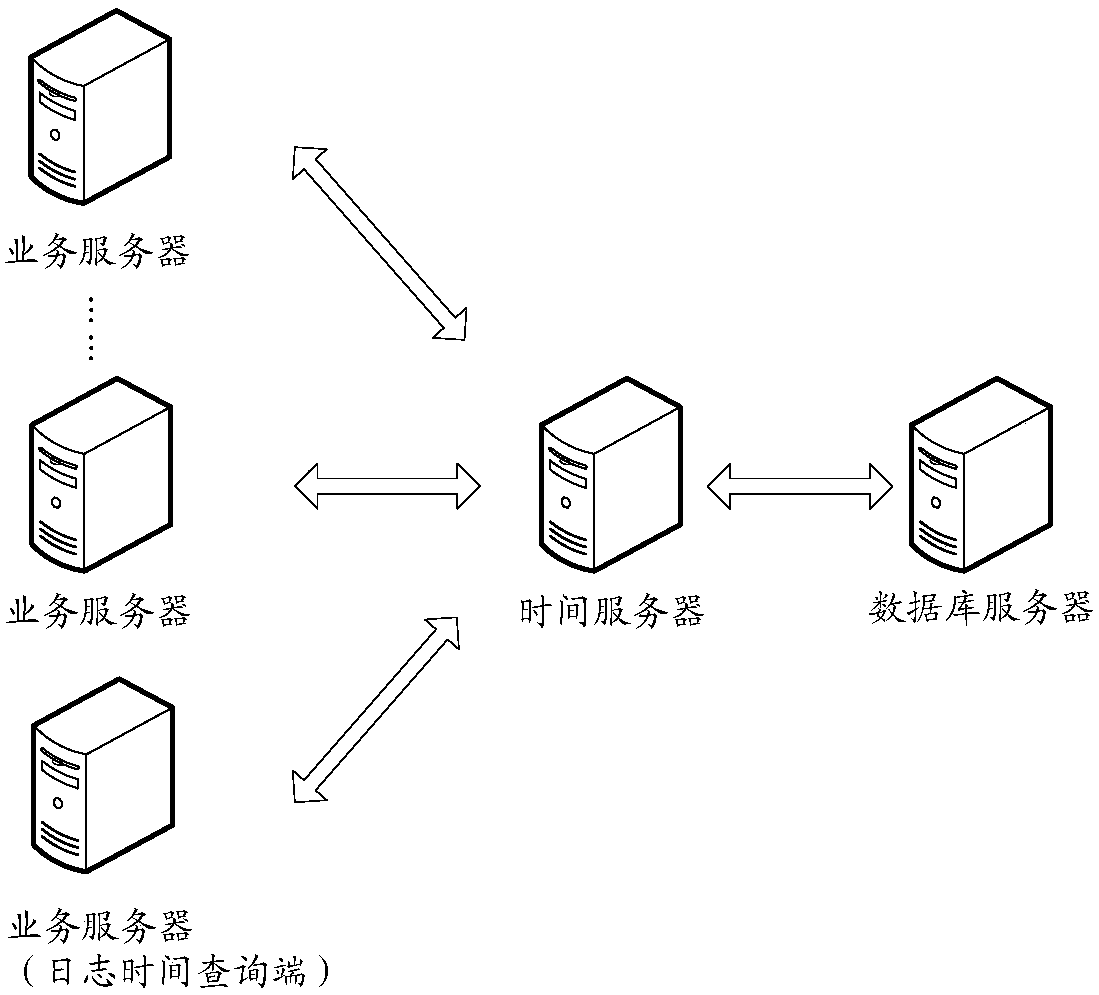

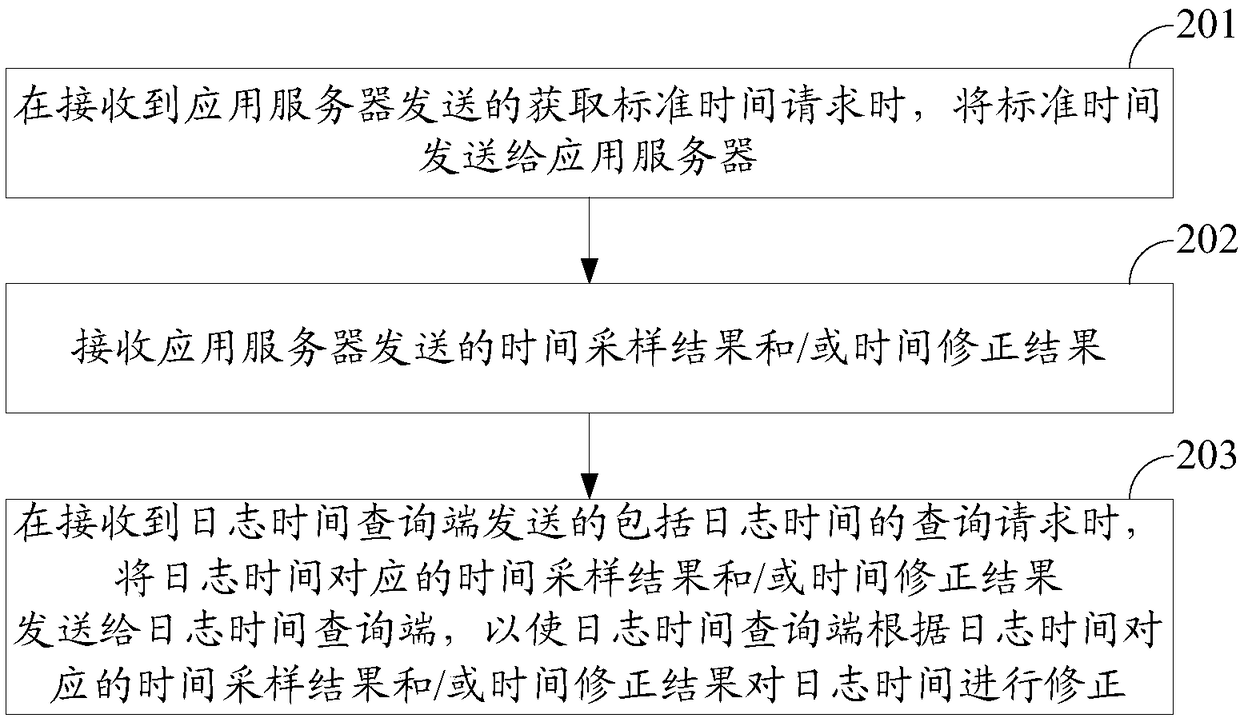

Time calibration method, apparatus and system

ActiveCN108075876AReduce time skewEnsure log time alignmentSynchronisation error correctionData switching networksApplication serverStandard time

The invention discloses a time calibration method, apparatus and system for realizing time alignment of a server. The method is applied to a time server and comprises the following steps: when a standard time obtaining request sent by an application server is received, sending a standard time to the application server; receiving a time sampling result and / or a time correction result sent by the application server, wherein the time sampling result comprises a current server time of the application server and a difference between the current server time and the standard time, the time correctionresult is generated after the application server satisfies a preset condition and corrects a local server time according to the time sampling result, and the time correction result comprises a time before being corrected by the application server and a time corrected by the application server; and when a query result comprising a log time sent by a log time query terminal is received, sending thetime sampling result and / or the time correction result corresponding to the log time to the log time query terminal.

Owner:TENCENT TECH (SHENZHEN) CO LTD

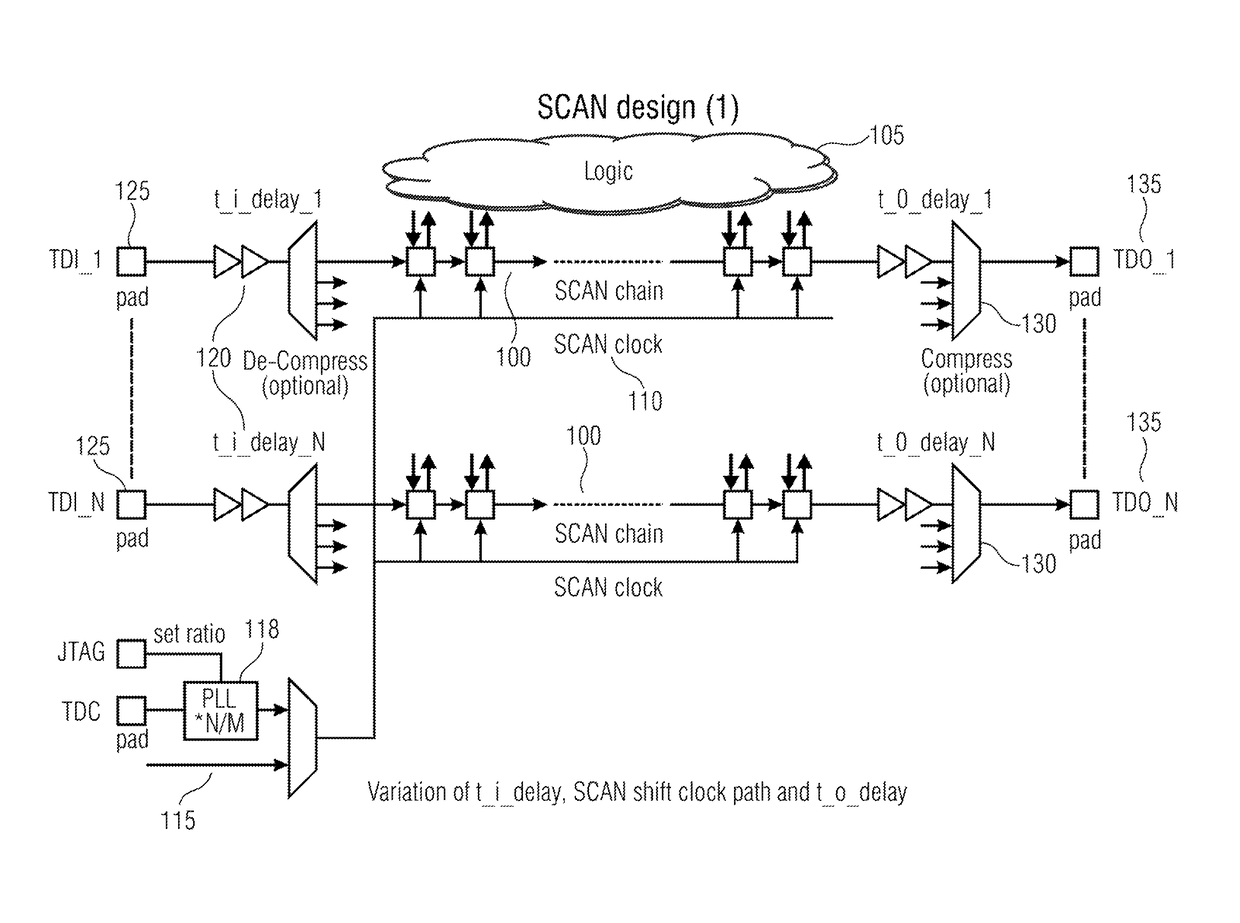

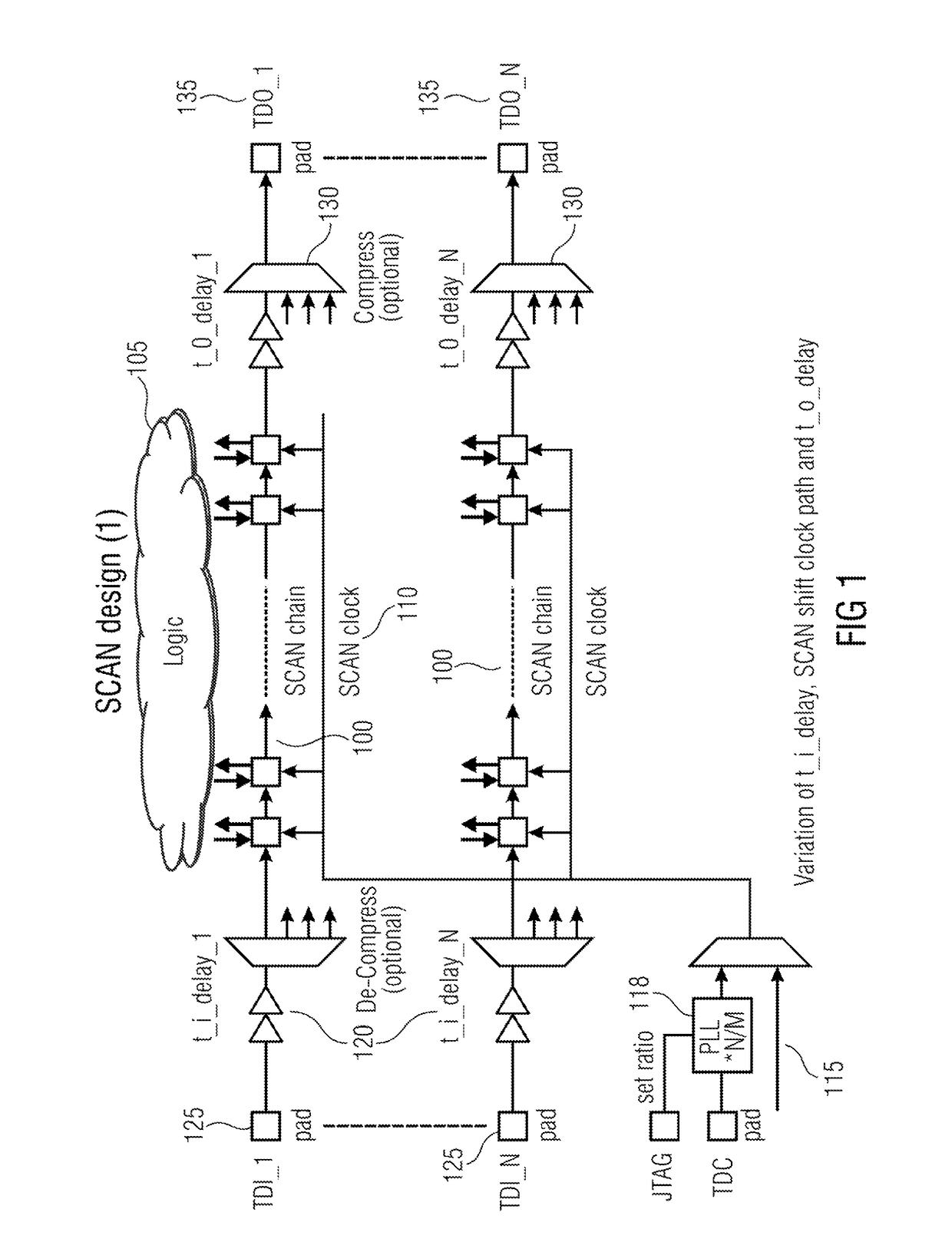

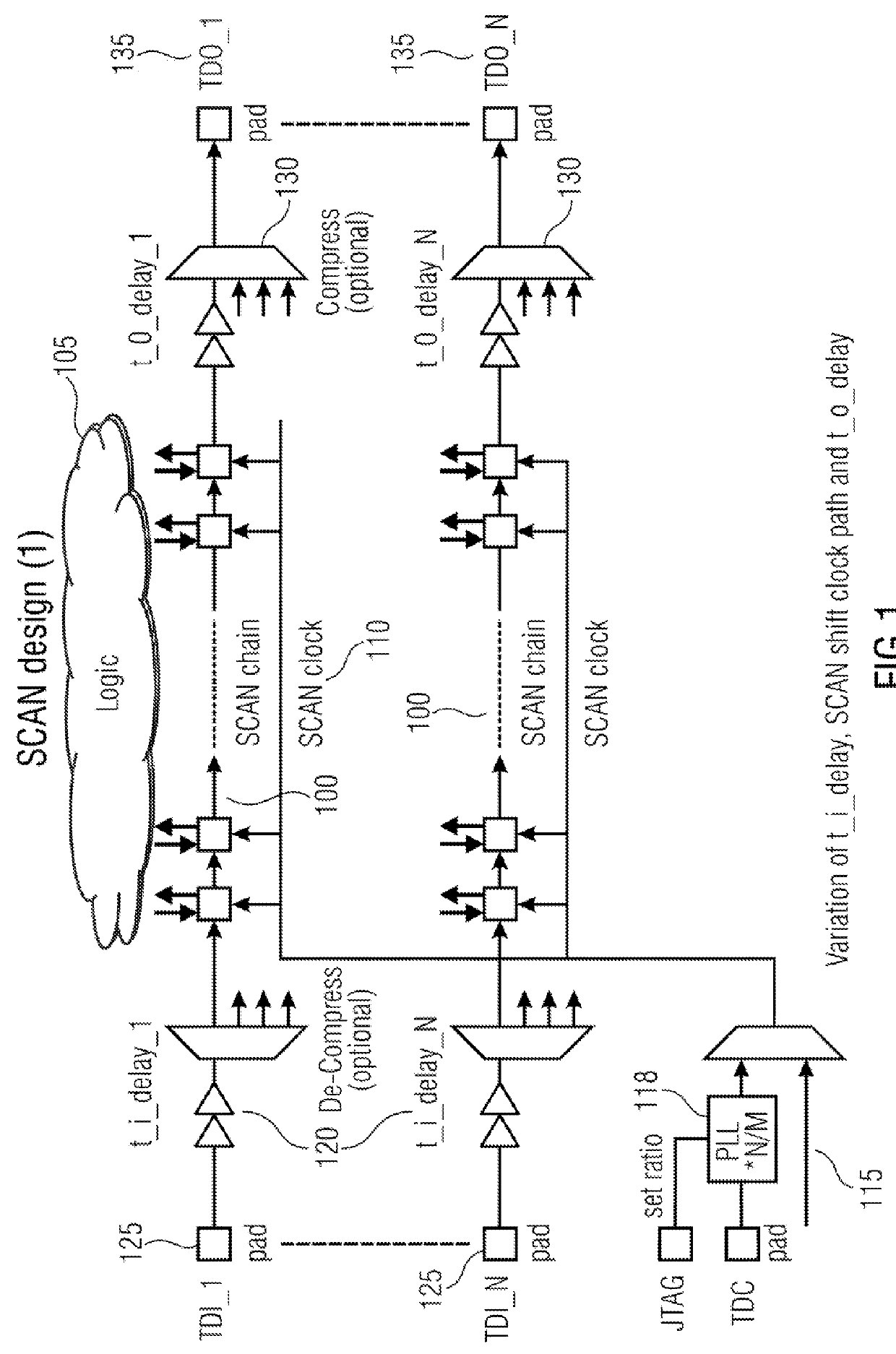

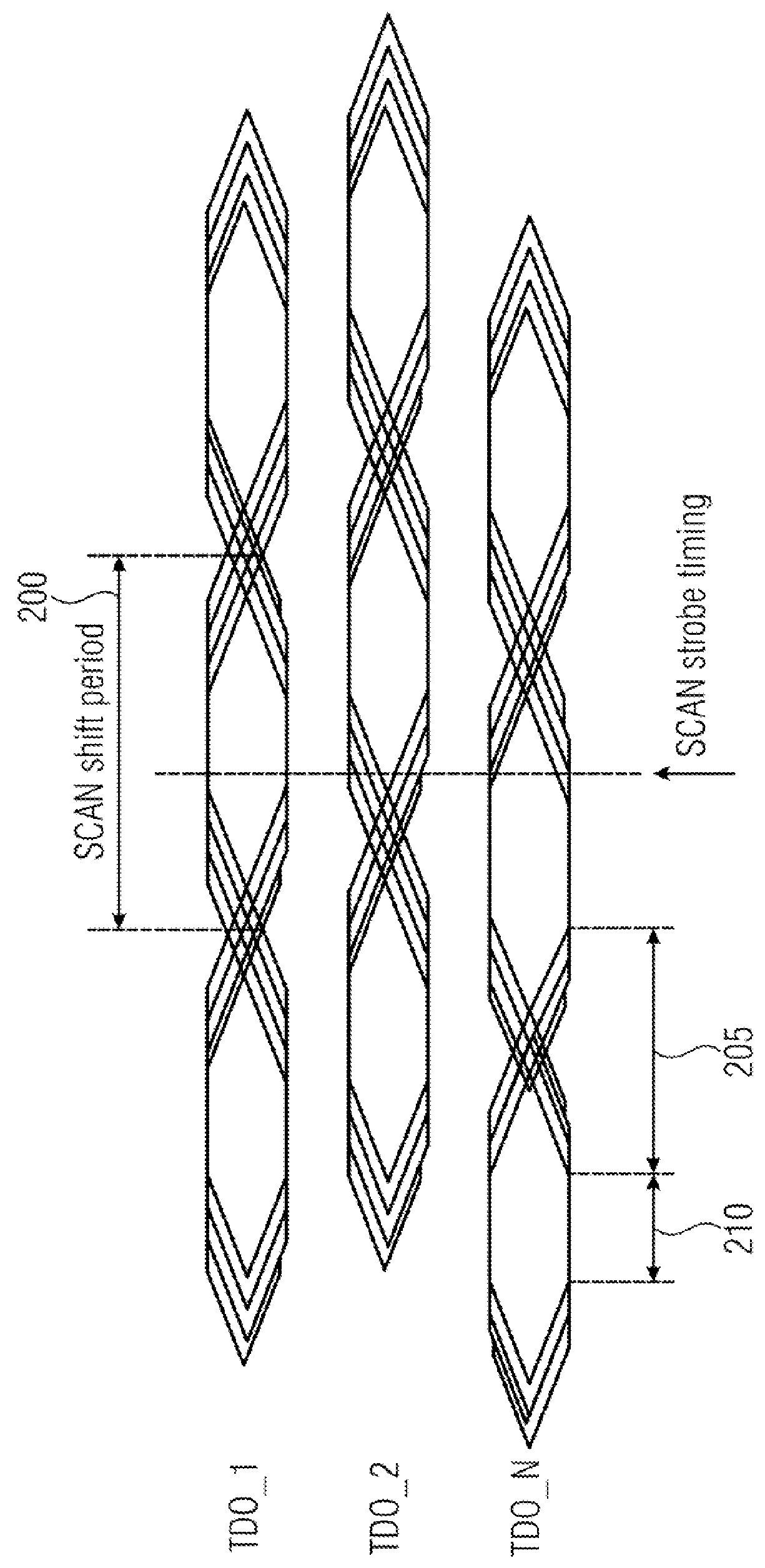

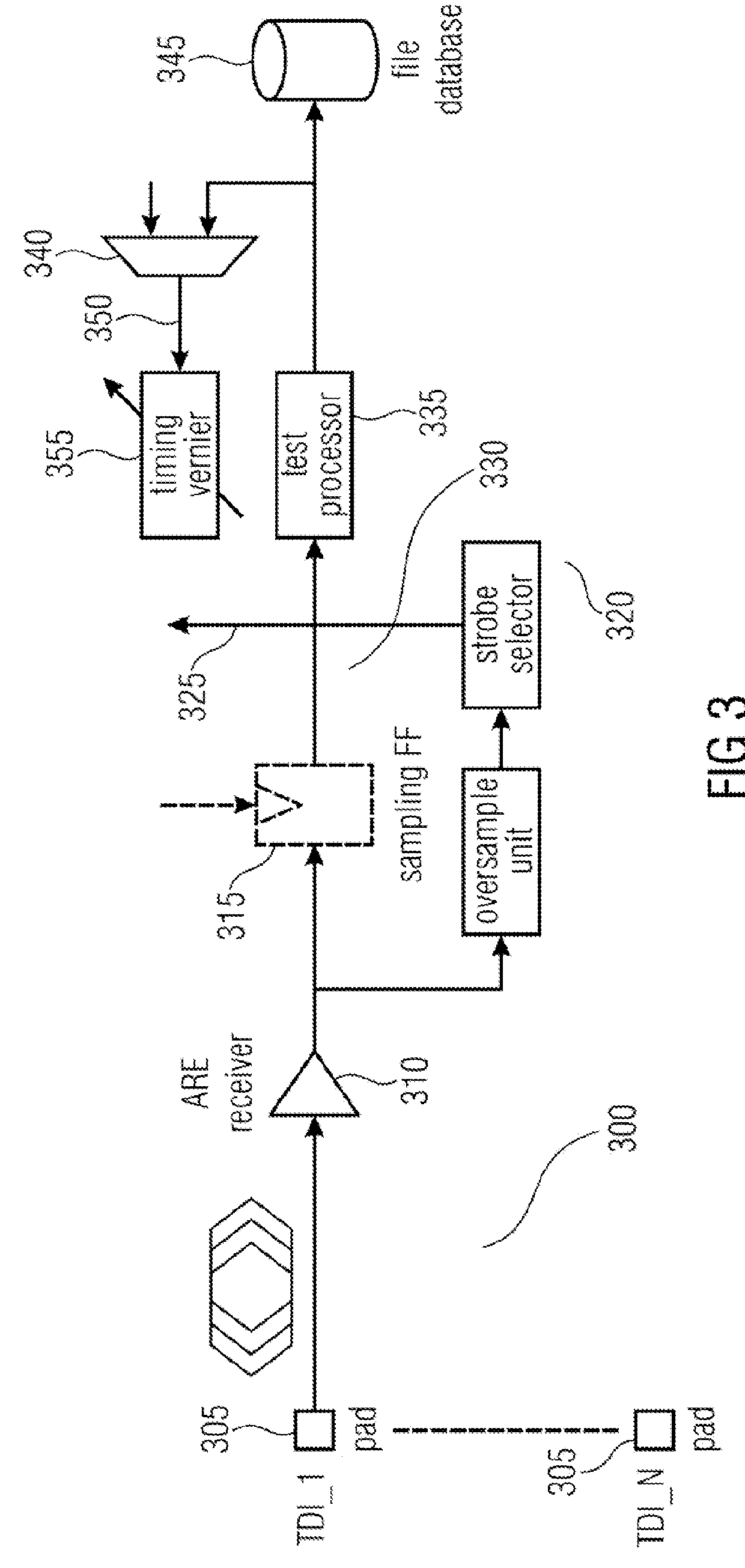

Scan speed optimization of input and output paths

Disclosed herein is a scan optimizer system and method designed to generate optimal ATE input / output timing with small margin but yielding stable results. Therefore the scan test time is greatly improved.

Owner:ADVANTEST CORP

Scan Speed Optimization of Input and Output Paths

Disclosed herein is a scan optimizer system and method designed to generate optimal ATE input / output timing with small margin but yielding stable results. Therefore the scan test time is greatly improved.

Owner:ADVANTEST CORP

System and Method for Feature Alignment

ActiveUS20100057377A1Accurate comparisonReduce probabilityTesting/calibration apparatusComponent separationComputer scienceSeparation column

In a system and method for feature alignment in chromatographic systems, the system runs a first sample through a first separation column. The system determines a first set of features for the first sample run. The system runs a second sample through a second separation column and detects a second set of features for the second sample run. The system estimates a systematic shift in features between the first sample run through the first separation column and the second sample run through the second separation column. The system adjusts the second set of features detected for the second sample run through the second separation column based on the estimated systematic shift to obtain a third set of adjusted features.

Owner:AGILENT TECH INC

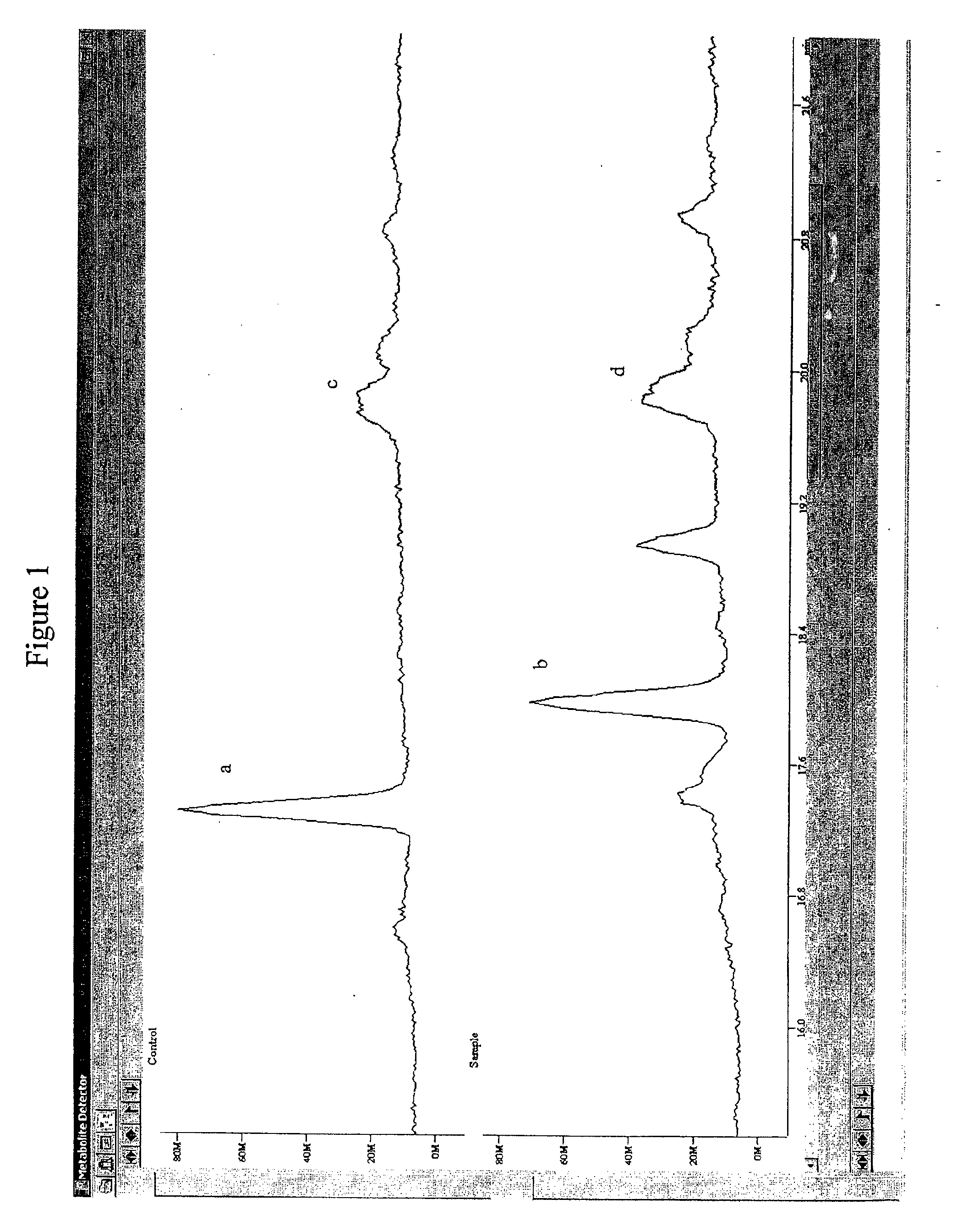

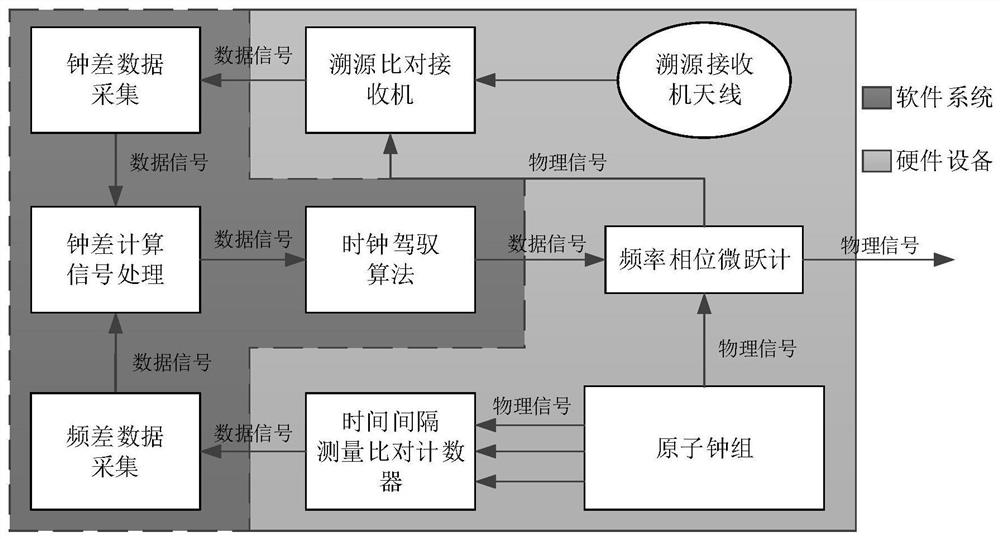

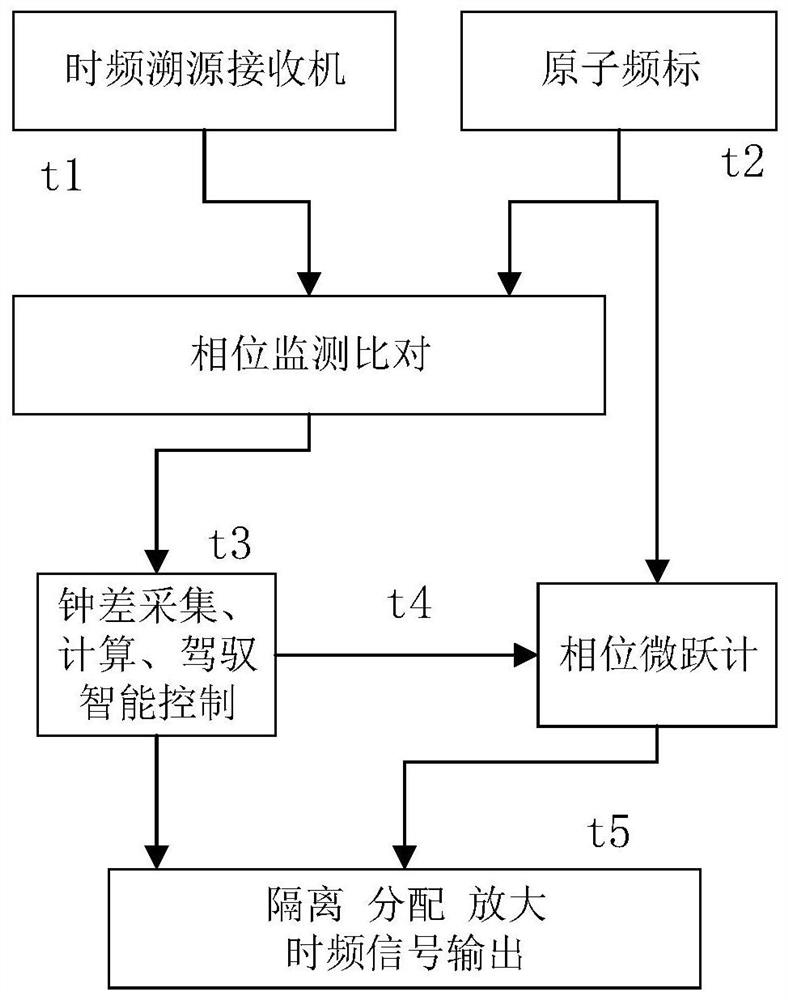

Phase adjustment method and device for cesium and hydrogen atom frequency standard

ActiveCN113377003AReduce time skewLess investmentPulse automatic controlEnsemble learningTime deviationProcess engineering

The invention discloses a phase adjustment method for a cesium and hydrogen atom frequency standard, wherein the method does not adopt a classical mode and method in the industry to regulate and control the phase performance of an atomic clock group and does not need to adopt a plurality of expensive cesium clocks and hydrogen clocks, and can remarkably reduce the time deviation relative to UTC and enable the performance index to reach the nanosecond or subnanosecond level through the method provided by the technical scheme of the invention; and the system investment can be greatly reduced, and similar or higher performance can be obtained only by a million yuan level. The system is small in size, high in performance, suitable for rapid arrangement, capable of being applied to ships, vehicles, common machine rooms and other environments, and wider in application range.

Owner:北京酷鲨科技有限公司

A Method of Multiplying High-Precision Second Pulse to Generate Sampling Pulse Based on FPGA

ActiveCN103941622BReduce time skewHigh speedProgramme controlComputer controlElectric power systemFpga chip

The invention discloses a method for adopting high-accuracy pulse per second frequency multiplication to produce sampling pulses based on an FPGA in the technical field of electric power system measurement and control and aims at solving the technical problem that sampling pulses provided by an oscillator in the prior art enable the sampling accuracy to be low. In the method, an actual synchronous pulse per second counting value is compared with an ideal synchronous pulse per second counting value, deviations and sampling frequencies are subjected to accumulation calculation, the correction situation of a pulse counter is judged according to an accumulation calculation result, accordingly total deviations of actual synchronous pulses per second are averagely distributed in actual sampling pulses, sampling pulse errors are remarkably decreased, and reliable and stable sampling pulse signals are provided for analog-digital signal acquisition. In addition, the method is simple and easy to operate, occupied FPGA chip resources are decreased, and the running speed and reliability of the FPGA are improved.

Owner:STATE GRID CORP OF CHINA +4

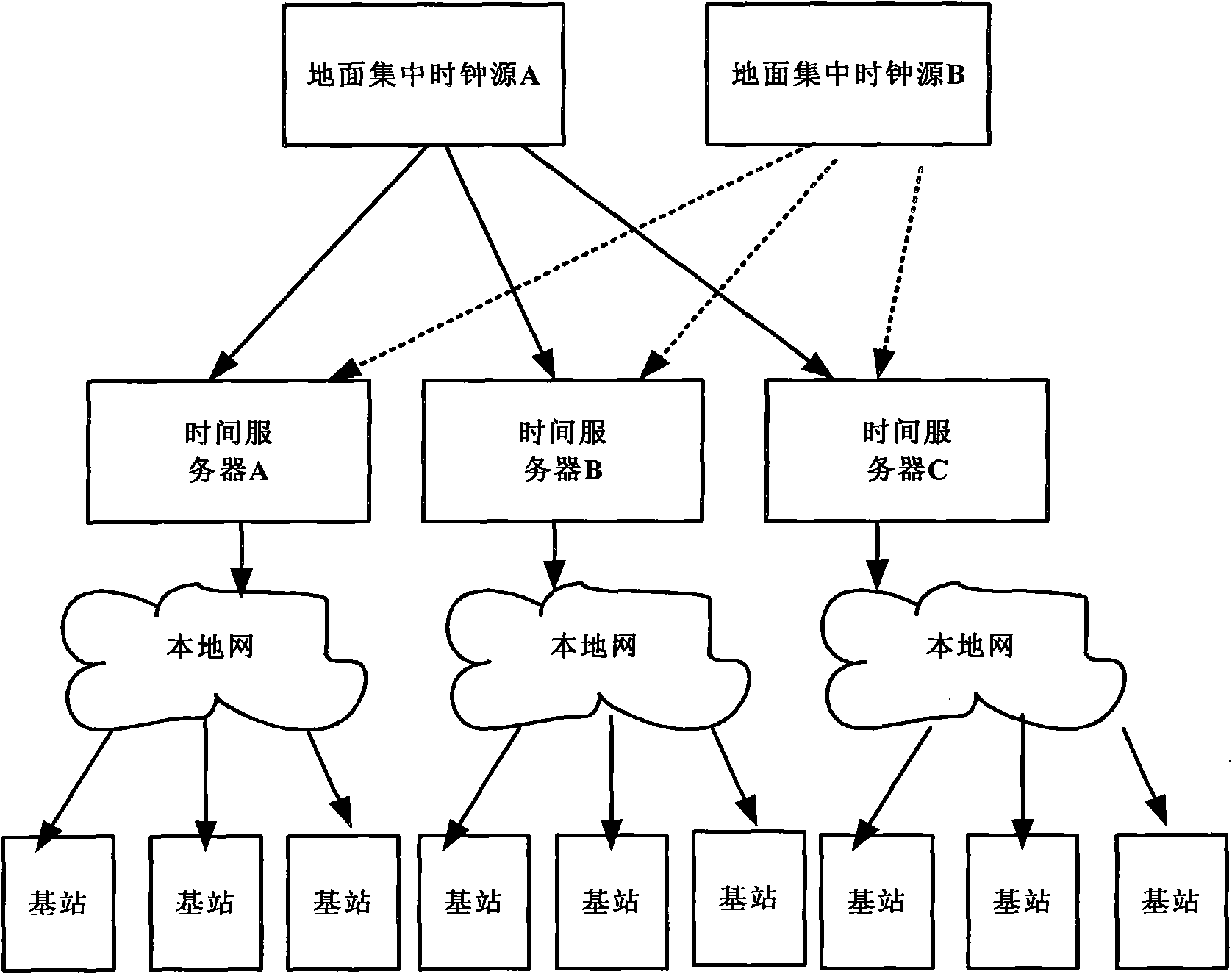

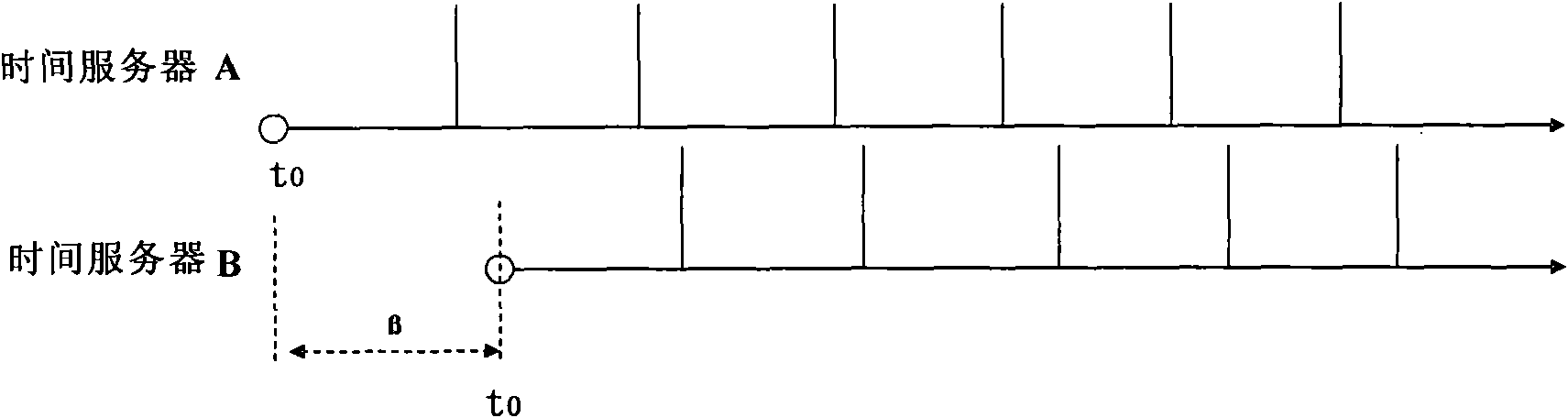

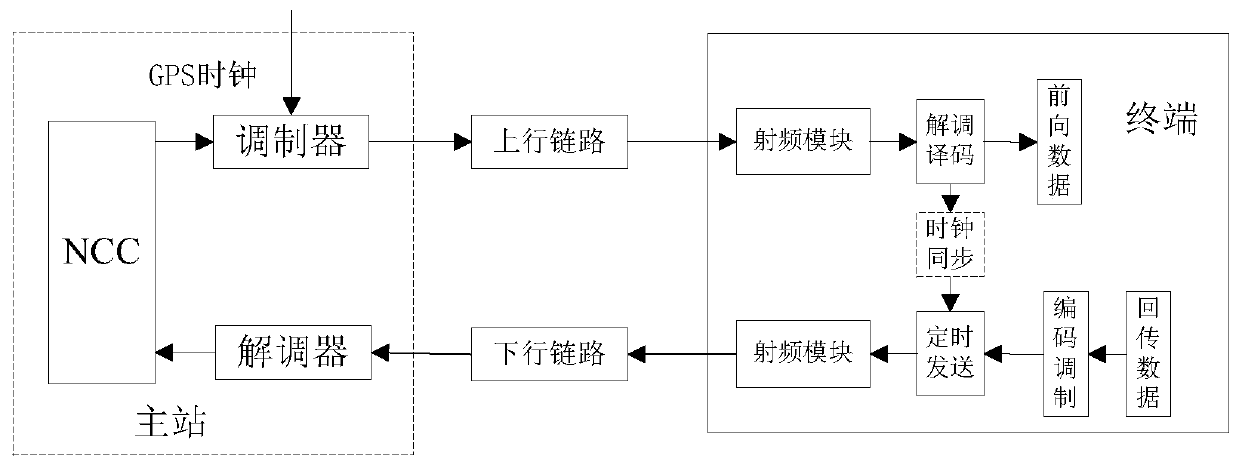

Time synchronization method, server and system

ActiveCN102378350BTime synchronizationReduce time skewSynchronisation arrangementTime informationSatellite

The invention discloses a time synchronization method, server and system. The method comprises the following steps that: a time server receives frequency information sent by a ground centralized clock source; and the time server calculates time according to the frequency information and the initial time, and sends the time information to a downstream base station. Through the method, the server and the system, the defect of low reliability of time synchronization in the prior art can be solved, and time synchronization still can be realized when a satellite is failed for a long time.

Owner:CHINA MOBILE COMM GRP CO LTD

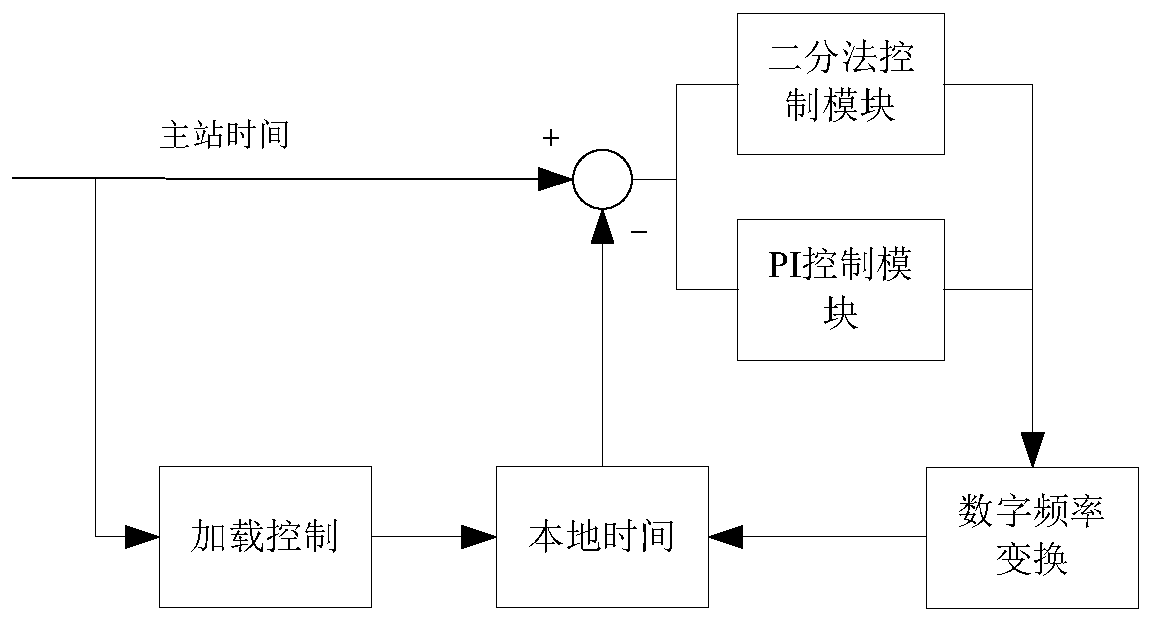

A digital clock synchronization method and device for a satellite communication terminal

ActiveCN108199799BEliminate adverse effects such as phase mutationsReduce expensesTime-division multiplexTime informationFrequency conversion

Owner:SPACE STAR TECH CO LTD