Methods and apparatus for reducing timing skew

a timing skew and apparatus technology, applied in the direction of cad circuit design, program control, instruments, etc., can solve the problems of increasing complexity and performance of system on a chip design, signal to signal timing skew typically exceeding the capabilities of existing routing tools, and the use of current tools is not adequate to route these critical interface paths with minimum skew. , to reduce the layout distance of each signal path, reduce timing skew, and reduce timing skew

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will now be described more fully with reference to the accompanying drawings, in which several embodiments and various aspects of the invention are shown. This invention may, however, be embodied in various forms and should not be construed as being limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art.

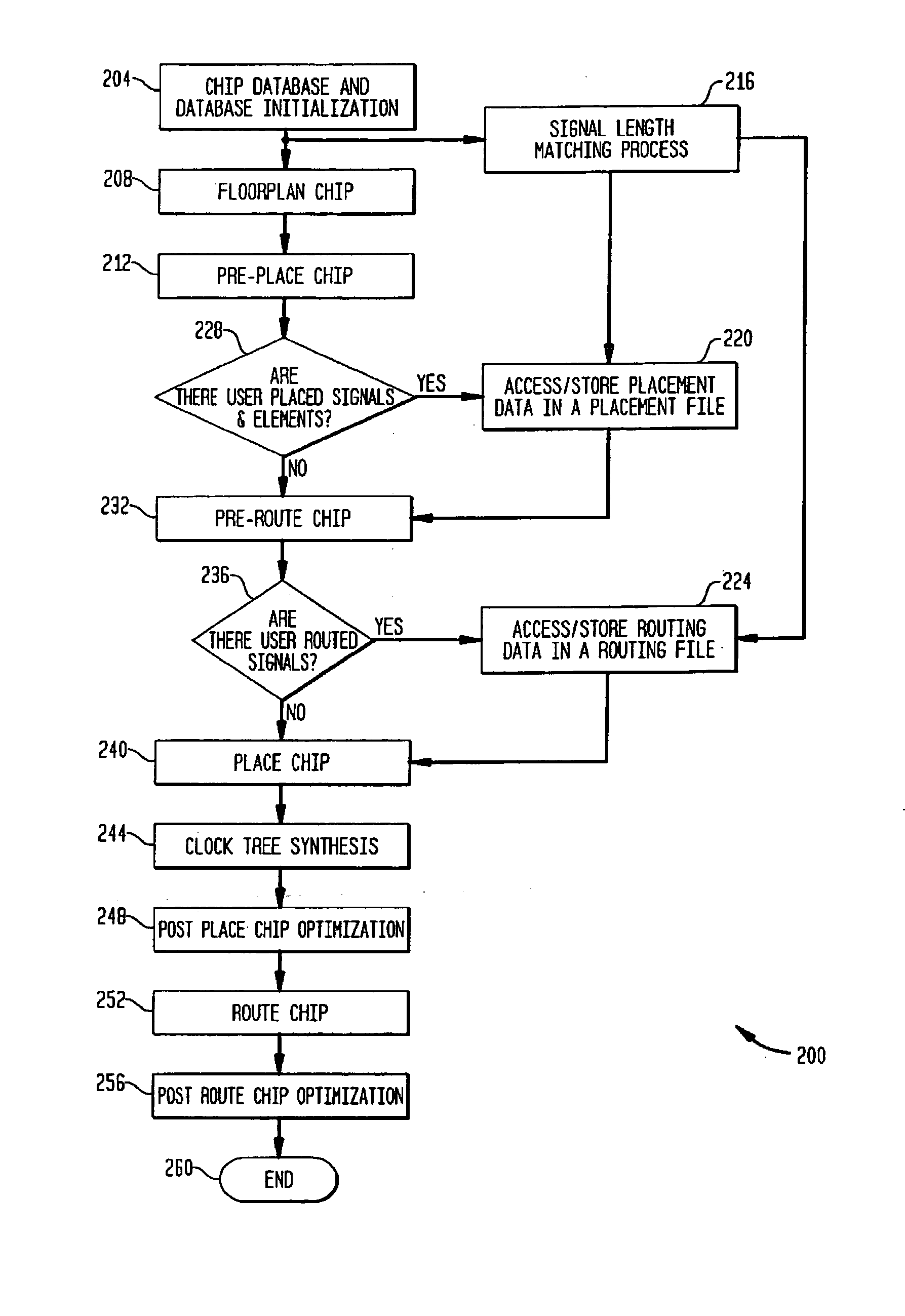

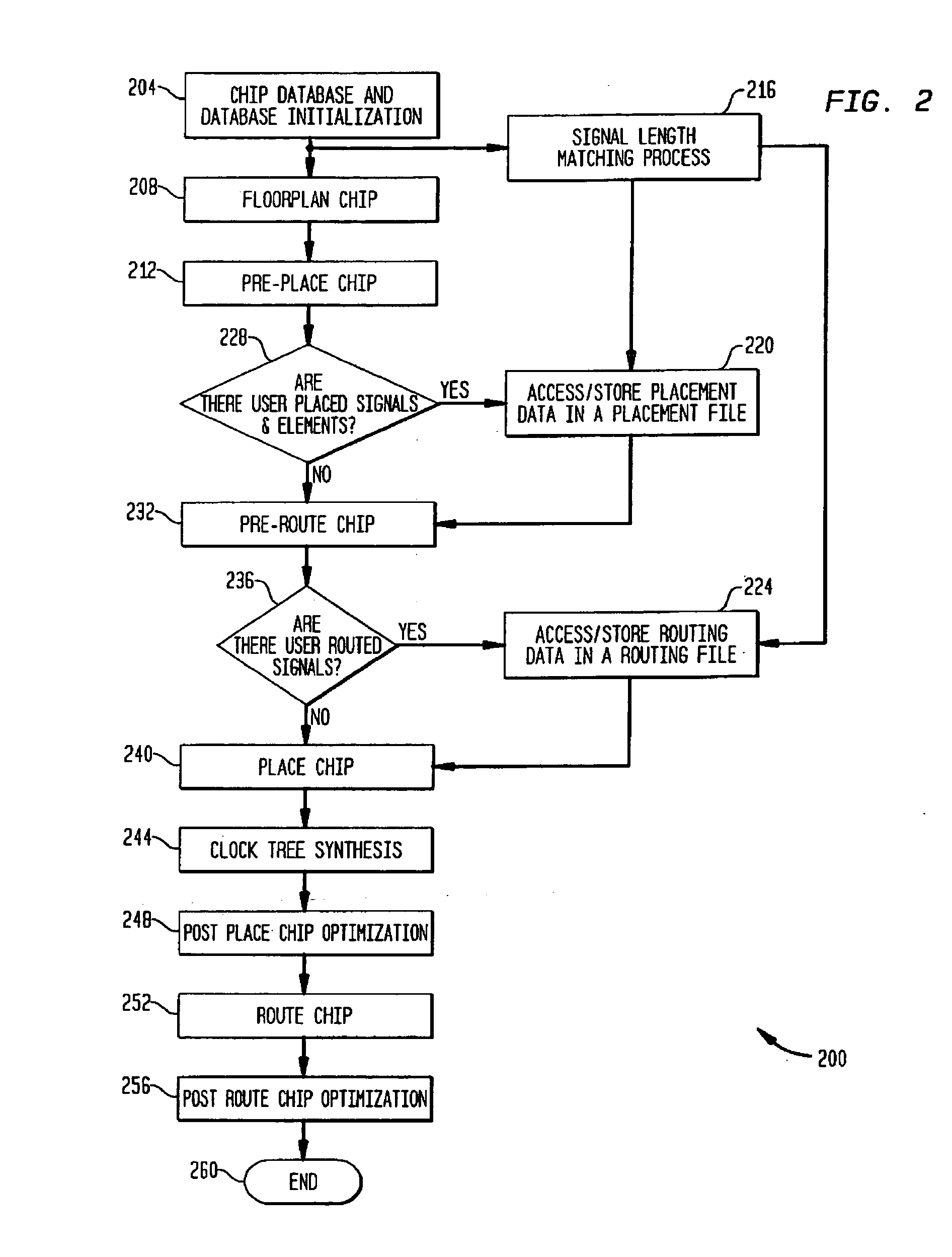

[0017]FIG. 1 illustrates a chip routing system 100 in accordance with the present invention. The chip routing system 100 uses a processor 104 which has a storage unit 108 for storing a chip database 109, a tools database 110, and the like, and interfaces with a monitor 112, keyboard 116, and printer 120. The processor 104 runs a high level place and route process and a signal length matching process as described in more detail below. While other programming languages, compilers, operating systems...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More