A ddr2-sdram controller and its low-latency optimization method

A technology of DDR2-SDRAM and controller, which is applied in the field of automatic test platform design to achieve the effect of improving real-time performance, avoiding address correlation, and reducing memory access delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The technical solution of the present invention will be described in detail below in conjunction with the accompanying drawings.

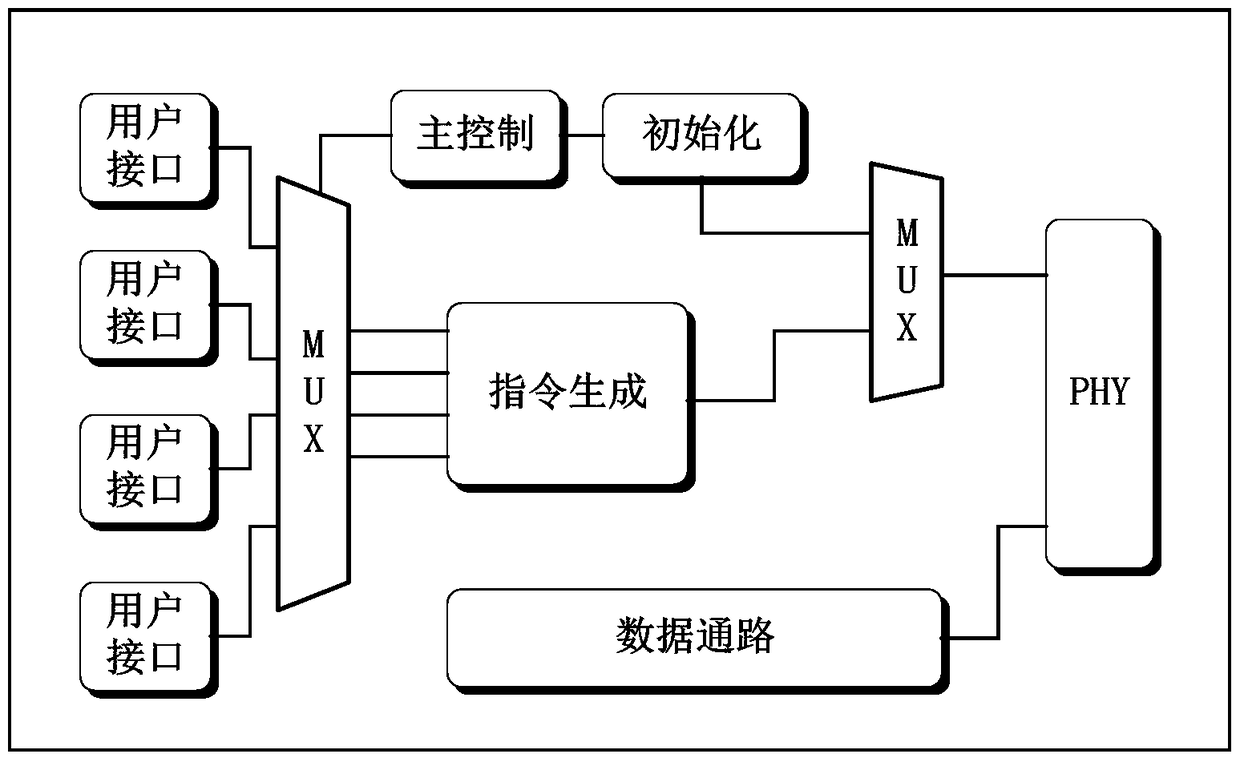

[0028] Such as figure 1 As shown, for the functions to be realized by the DDR2-SDRAM controller, using the concept of modularization, the control logic of the entire controller can be divided into 5 modules, which are initialization module, user interface module, instruction generation module, main control module and Data path module.

[0029] The AD / DA data acquisition and sending system in the RF automatic test platform targeted by the present invention requires at least 4 data paths that can work in parallel, so the controller is designed with 4 user interfaces for serving the front-end ADC / DAC memory access requests. When collecting work, each AD occupies a user interface to achieve parallel access to the memory. AD collection is a continuous data stream, and the data is stored in a continuous logical address space, and the priority of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More