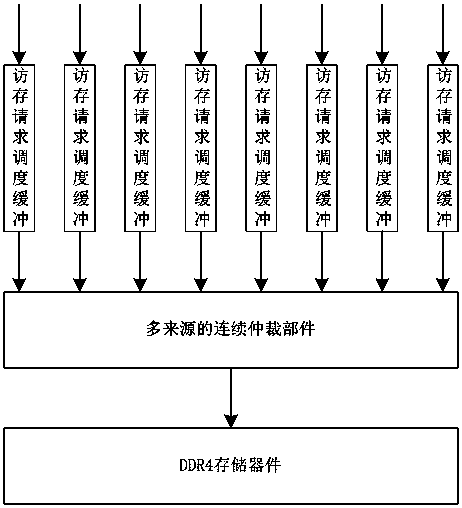

DDR4 performance balance scheduling structure and method for multiple request sources

A scheduling method and multi-request technology, applied in resource allocation, multi-program device, program startup/switching, etc., can solve problems such as unfavorable chip overall performance and insufficient consideration of source characteristics, so as to reduce the impact of memory access delay and improve Memory access bandwidth and the effect of improving comprehensive memory access performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

[0050] In the second embodiment, on the basis of the first embodiment, the memory access request scheduling buffer includes a bandwidth-sensitive memory access scheduling buffer and a delay-sensitive memory access scheduling buffer.

[0051] Among them, the bandwidth-sensitive memory access scheduling buffer includes

[0052] Storage entry, used to record the information of the fetch request. The information of the fetch request includes the fetch request information, the left sub-pointer of the entry, and the right sub-pointer of the entry

[0053] Empty entry queue, used to mount storage entries in the form of a queue.

[0054] The scheduling binary tree is used to organize storage entries in the form of a binary tree.

[0055] First, each storage entry in the bandwidth-sensitive memory fetch scheduling buffer includes three pieces of information: fetch request information, the left sub-pointer of the entry, and the right sub-pointer of the entry. These storage entries are organized...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More