Currency detector test method and apparatus, and ATM

A test method and test device technology, applied in the direction of electrical test/monitoring, test/monitoring control systems, instruments, etc., can solve the problems of single test means and incomparable scene diversification tests, etc., to achieve strong adaptability and flexible testing Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

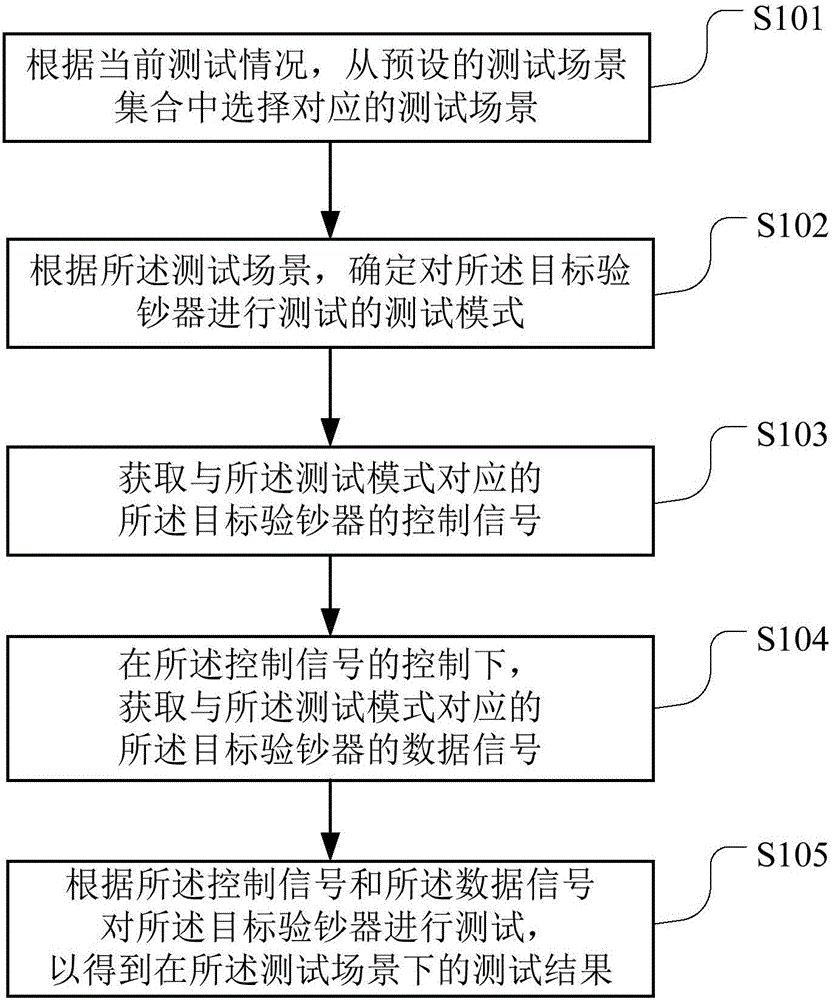

[0030] Such as figure 1 As shown, it is a schematic flowchart of a banknote validator testing method provided by an embodiment of the present invention, and the banknote validator testing method may include:

[0031] Step S101, selecting a corresponding test scenario from a preset test scenario set according to the current test situation.

[0032] In this embodiment, the set of test scenarios includes four different test scenarios:

[0033] Test scenario 1, normal currency inspection;

[0034] Test scenario 2, dynamic collection of fixed data;

[0035] Test scenario three, statically collect sensor data;

[0036] Test scenario four, static collection of fixed data.

[0037] Step S102, determining a test mode for testing the target banknote validator according to the test scenario.

[0038] If it is the test scene one of normal banknote checking, then the test mode determined to be adopted is the first mode of True Ctrl+True Data;

[0039] If it is the test scenario 2 of ...

Embodiment 2

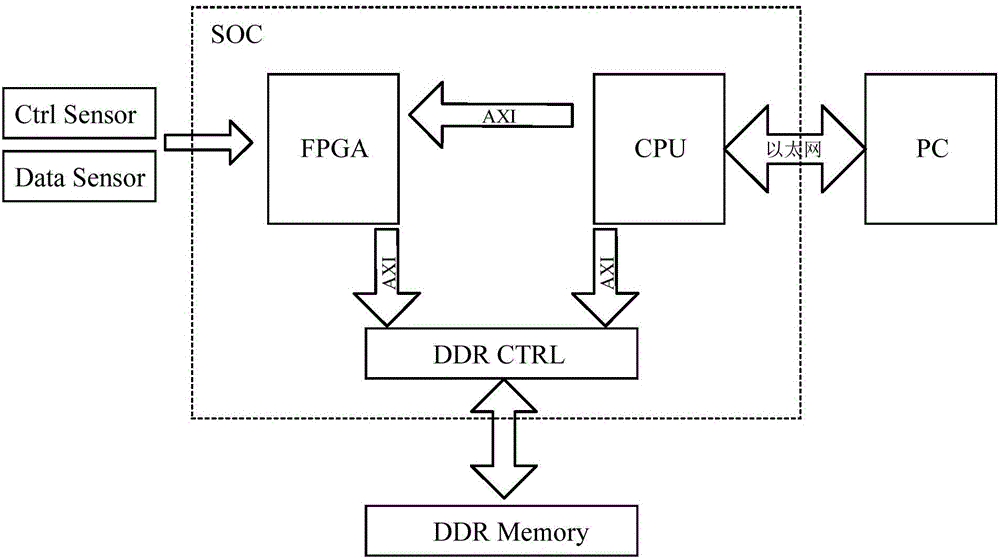

[0068] Such as figure 2 As shown, it is a schematic block diagram of a banknote validator testing device provided by an embodiment of the present invention, and the banknote validator testing device may include: FPGA, CPU and host computer;

[0069] The upper computer is connected with the CPU, and is used to select a corresponding test scene from a preset test scene set according to the current test situation, and determine the test mode for testing the target banknote validator according to the test scene, and send The CPU issues the test mode;

[0070] The CPU is connected to the FPGA for receiving the test mode issued by the host computer, and configuring the test mode to the FPGA;

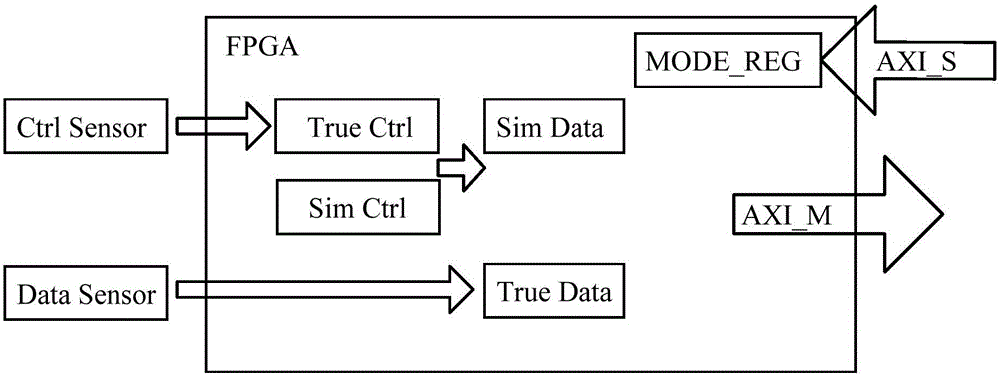

[0071] The FPGA is connected to the target banknote validator for obtaining the control signal of the target banknote validator corresponding to the test mode, and under the control of the control signal, obtains the corresponding banknote validator of the test mode. The data signal of the ...

Embodiment 3

[0088] Such as Figure 4 As shown, it is a schematic block diagram of a banknote validator testing device provided by an embodiment of the present invention, and the banknote validator testing device may include:

[0089] The test scene selection module 401 is used to select a corresponding test scene from a preset test scene set according to the current test situation;

[0090] A test mode determination module 402, configured to determine a test mode for testing the target banknote validator according to the test scenario;

[0091] A control signal acquisition module 403, configured to acquire a control signal of the target banknote validator corresponding to the test mode;

[0092] Data signal acquisition module 404, for under the control of described control signal, obtain the data signal of described target money validator corresponding to described test pattern; The data signal; when the control signal indicates that it is currently in a non-acquisition state, stop obta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More