Abnormal logic business simulating test device

A simulation test and logic technology, which is applied in the direction of logic operation inspection and detection of faulty computer hardware, etc., can solve the problems of unreusable code, difficult test automation, low test efficiency, etc., to achieve multiple functions, high test efficiency, modification and maintenance convenient effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be described in further detail below in conjunction with the accompanying drawings.

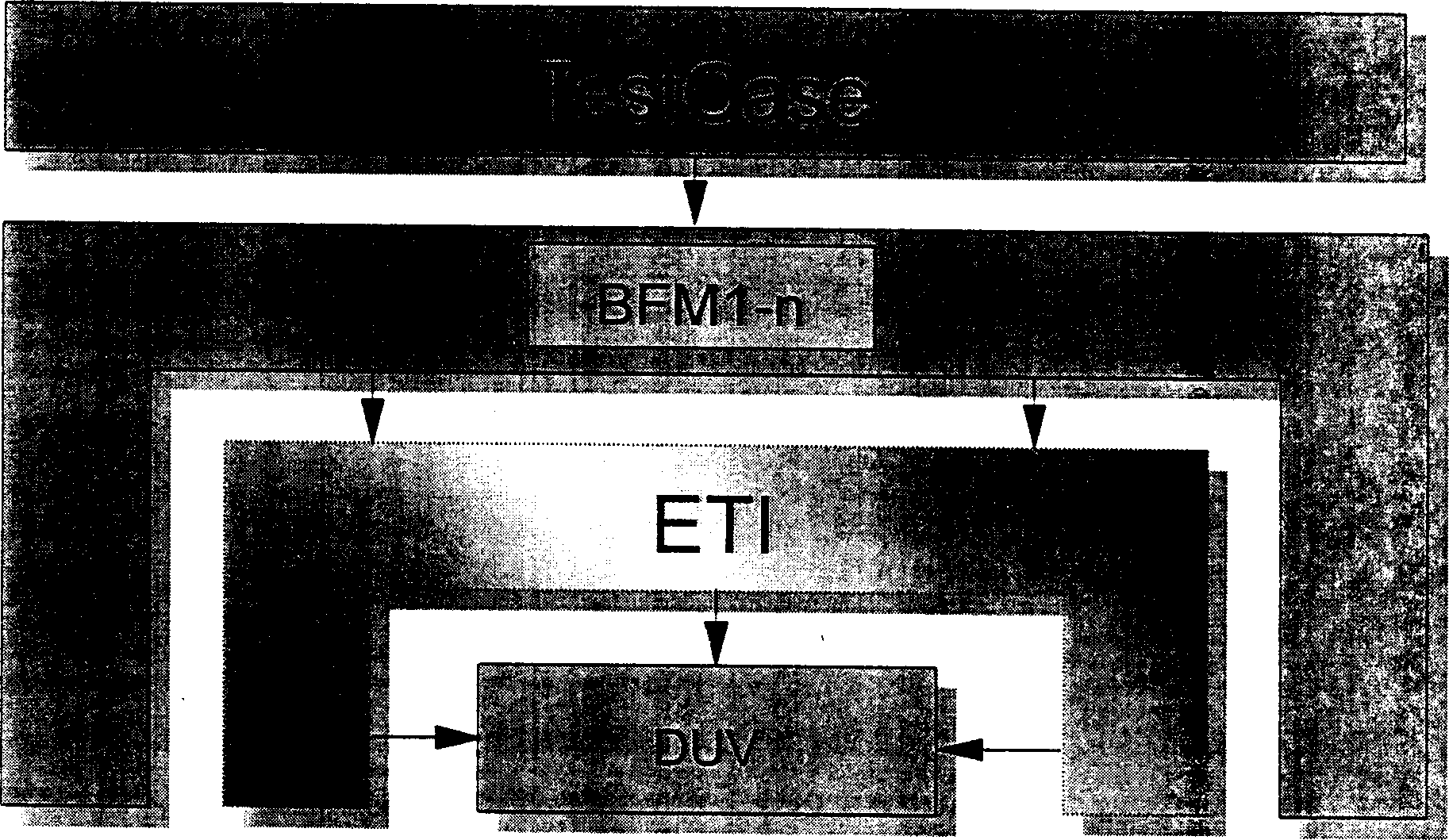

[0027] The abnormal simulation test interface (ETI: Exception Test Interface) provided by the present invention is an independent module, and can be used together with the existing logic simulation test platform (TestBench) to form a four-layer hierarchical structure, refer to figure 1 . figure 1 Among them, the excitation signal applied to the logic under test by the BFM module layer passes through the ETI interface of the present invention first, and then is applied to the logic under test after implementing fault insertion. Therefore, the ETI interface provided by the present invention is like a fault insertion board, which implements fault insertion for the interface signal of the logic to be tested.

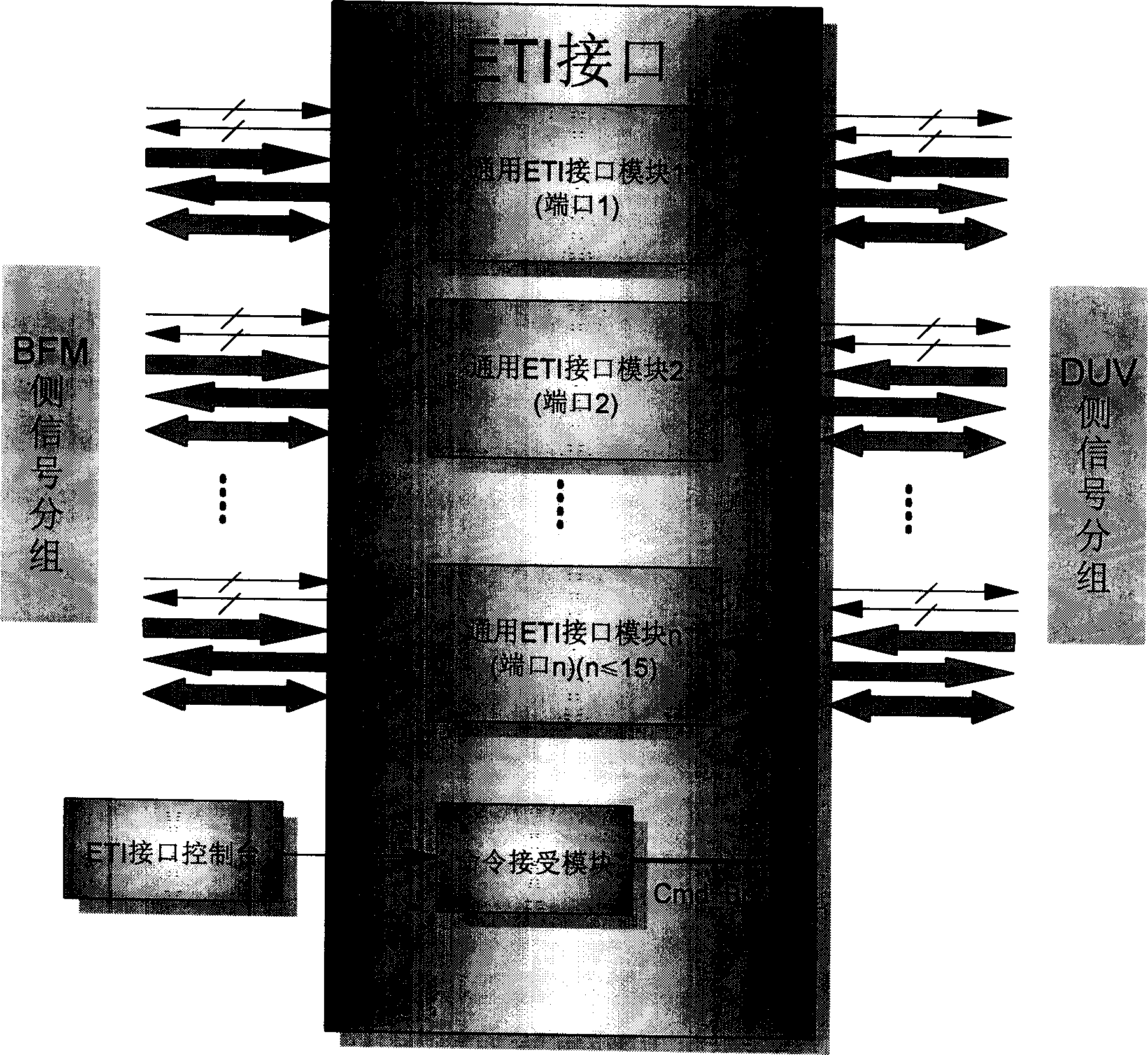

[0028] As needed for fault insertion testing, figure 1 During the actual design of the ETI interface in , for different logic simulation projects, corres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More