Reversible flip-flop with configurable logic function and configuration method thereof

A technology of logic function and configuration method, which is applied in the direction of pulse generation, electrical components, and electric pulse generation, and can solve the problem that D flip-flops cannot be converted.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

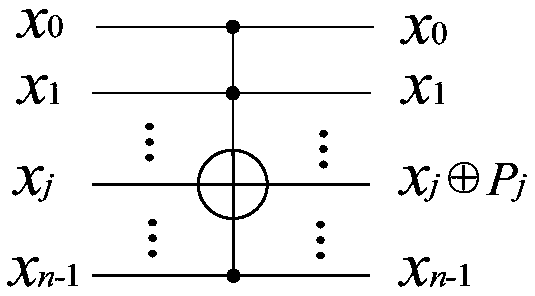

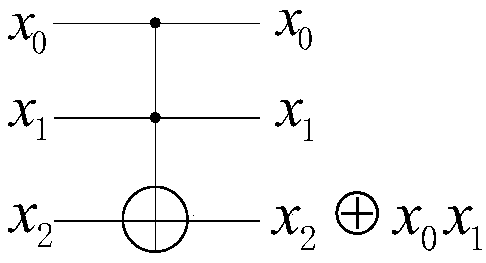

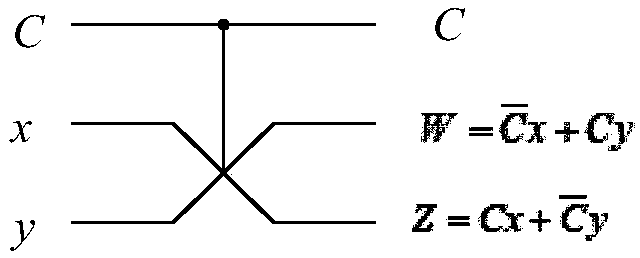

[0022] In the present invention, Toffoli reversible logic gates and Fredkin reversible logic gates are mainly used. Figure 1a A schematic diagram of an n-bit Toffoli reversible logic gate with only 1 target bit is given. The logic function of the n-bit Toffoli reversible logic gate can be expressed as TOF(Ctrl,T), Wherein, Ctrl represents control bit input set, Ctrl={x 0 ,...,x j-1 ,x j+1 ,...,x n-1}, T represents the target bit input set, T={x j}, and satisfy Ctrl∪T=I, "∩" is the set intersection operation symbol, "∪" is the set union operation symbol, Represents an empty set, I represents a set of n input variables, x 0 ,...,x j-1 ,x j+1 ,...,x n-1 Input for n-1 control bits, x j Input for 1 target bit, 0≤j≤(n-1), ie x j is any one of the n input variables, and the rest of the input variables are control bit inputs, P j =Πx ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More