Soc test code programming method, ip test method and device

A technology for testing codes and codes, which is applied in the direction of software testing/debugging, architecture with a single central processing unit, and general-purpose stored program computers, etc. It can solve the problems of low chip test coverage and achieve insufficient test coverage and save money. Effect of time, simplified process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

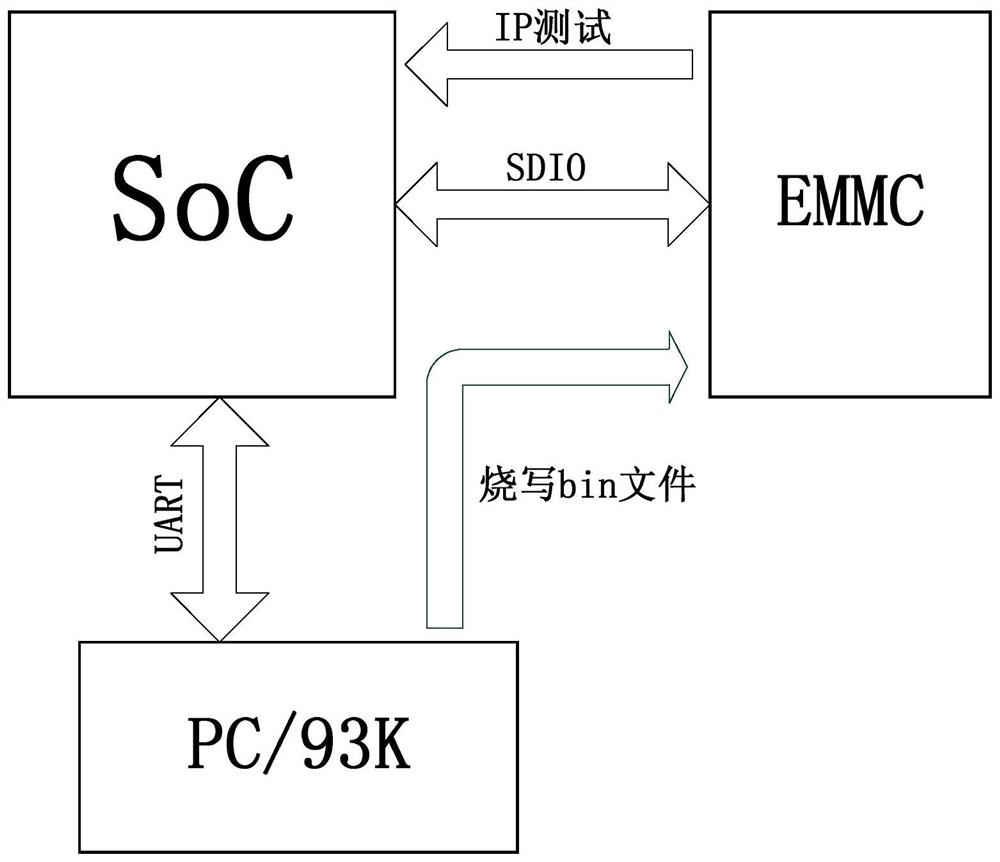

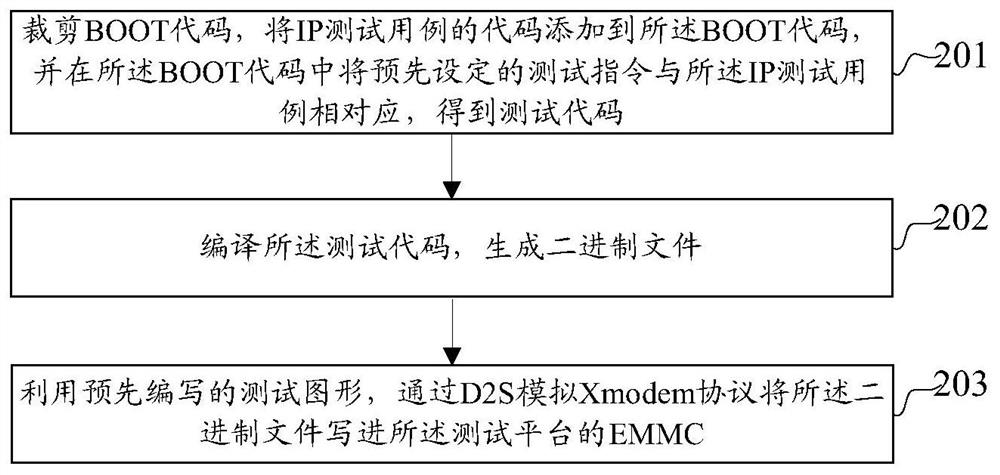

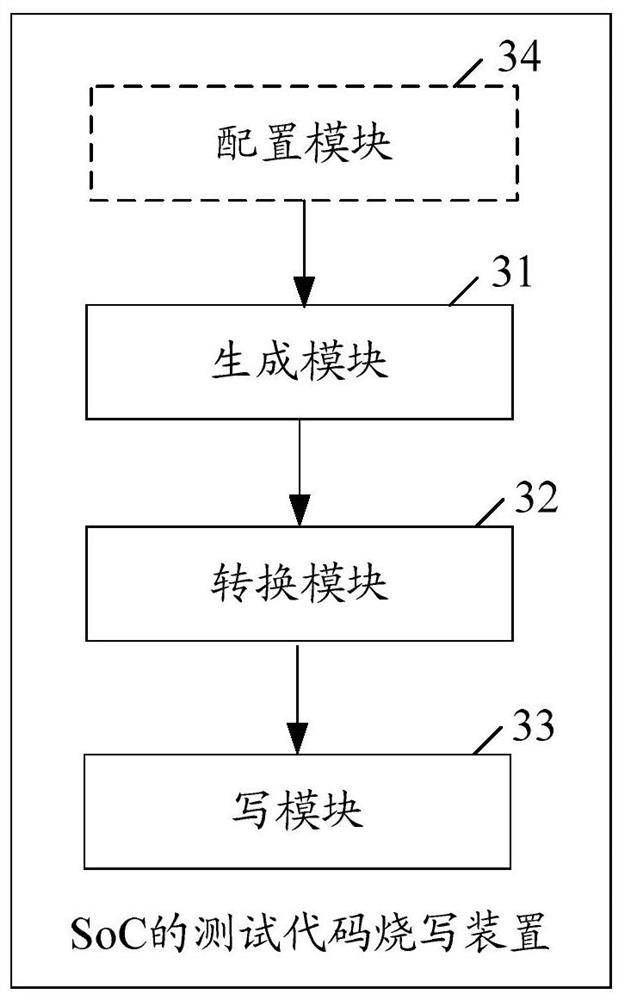

[0063] A kind of test code burning method of SoC, such as figure 2 As shown, can include:

[0064] Step 201, cutting out the BOOT code, adding the code of the IP test case to the BOOT code, and corresponding the preset test instructions to the IP test case in the BOOT code, to obtain the test code;

[0065] Step 202, compiling the test code to generate a binary file;

[0066] Step 203, utilize the pre-written test pattern to write the binary file into the EMMC of the test platform by dynamic to static structure (Dynamic to Static, D2S) simulation Xmodem protocol, and the test pattern can include predefined combination information , the combined information includes predefined timing information and level information.

[0067] In this embodiment, the cutting BOOT code, before adding the code of the IP test case to the BOOT code, may also include: pre-configuring a test instruction set for SoC chip IP testing, the test instruction set includes at least one The test instructi...

Embodiment 2

[0100] The present embodiment provides a kind of IP test method of SoC chip, such as Figure 6 As shown, can include:

[0101] Step 601, the SoC chip obtains the test instruction from the test platform through the UART interface;

[0102] Step 602, the SoC chip loads the test code in the EMMC by the BOOT CPU, calls the corresponding IP test case of the test instruction and configures the registers, and completes the IP test;

[0103] Wherein, the test code includes IP test cases and corresponding test instructions.

[0104] In an implementation mode, the exemplary implementation process of the IP testing method of the above-mentioned SoC chip, such as Figure 7 As shown, can include:

[0105] Step 701, define a test instruction set, different instructions correspond to different IP test items, and different test cases can be invoked by sending instructions to the SoC during the test.

[0106] For example, taking High Definition Multimedia Interface (HDMI, High Definition M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More