Chip dormancy control method and device

A control method and chip technology, applied in program control devices, program control design, instruments, etc., can solve problems such as poor definition of waiting time, affecting chip response speed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Specific embodiments of the present disclosure will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present disclosure, and are not intended to limit the present disclosure.

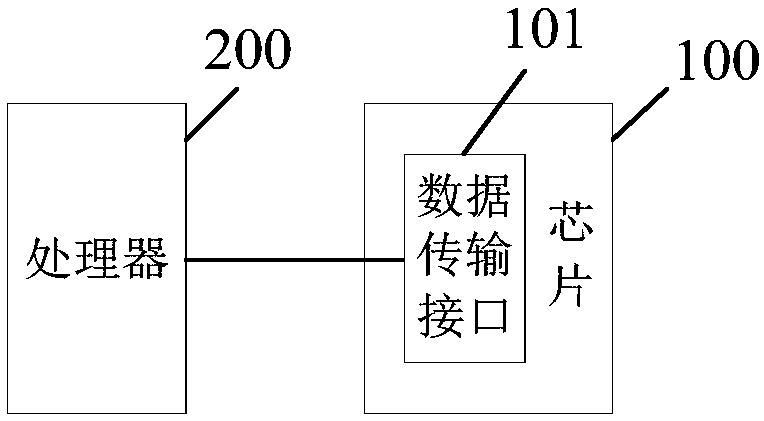

[0057] see figure 1 , is a schematic diagram of the connection between the chip and the processor according to the embodiment of the present disclosure. The chip 100 is connected to the processor 200 or a host (host) through a data transmission interface 101 (for example, a high-speed data interface) for data transmission. In one embodiment, the chip 100 may be a storage device, such as a solid state disk.

[0058] In the embodiment of the present disclosure, by detecting and recording the data transmission status of the data transmission interface 101, the dormancy of the chip is dynamically adjusted, and the response speed of the chip is improved.

[0059]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More