Digital background correction method based on least mean square algorithm

A calibration method and digital technology, applied in the direction of analog/digital conversion calibration/test, analog/digital conversion, signal transmission system, etc., can solve the problems of invalid correction, no highest-order capacitance correction, and inability to correct the mismatch direction, etc. achieve the effect of ensuring correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0051] Below in conjunction with accompanying drawing, further illustrate the present invention through embodiment.

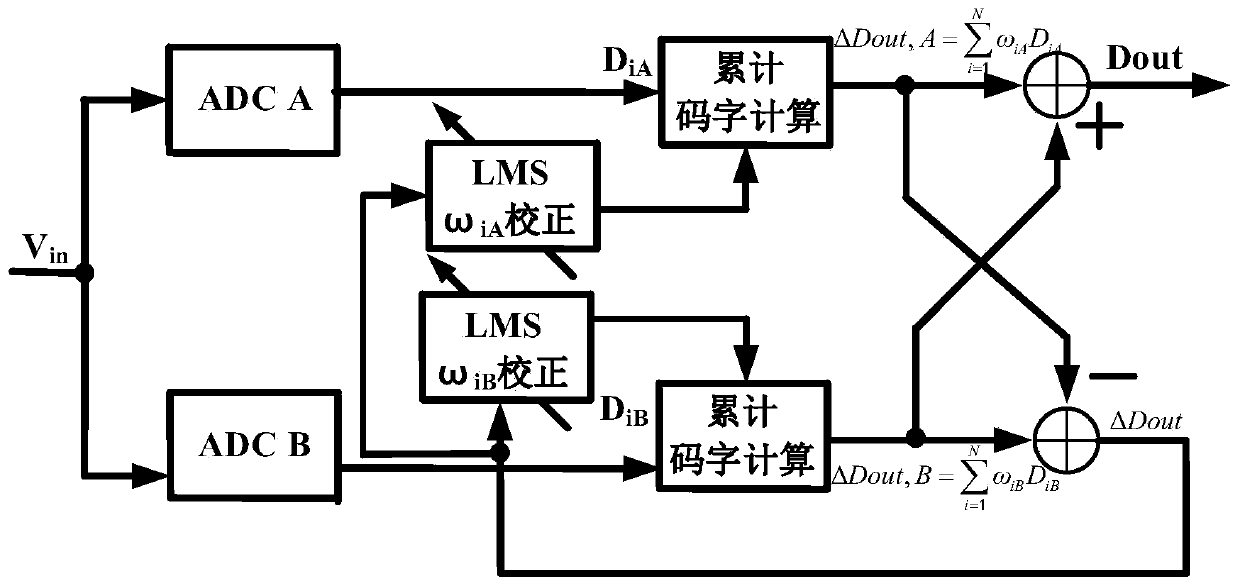

[0052] Such as figure 1 Shown is a frame diagram of a digital background correction method based on the least mean square algorithm proposed by the present invention, and the structure that adopts the method of the present invention to correct includes split SAR ADC, LMSω iA Calibration module, LMSω iB Correction module, the first cumulative codeword calculation module and the second cumulative codeword calculation module, the split SAR ADC includes the first analog-to-digital conversion module ADC A and the second analog-to-digital conversion module ADC B, the first analog-to-digital conversion module ADC A Connect the input signal V with the input terminal of the second analog-to-digital conversion module ADC B module in , the output end of the first analog-to-digital conversion module ADC A module is connected to the first input end of the first accumulate...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More