Embedded multi-CPU interconnection circuit based on SDIO interface, interconnection method and driving method

An embedded, interface technology, applied in the field of network isolation, which can solve problems such as reducing data transmission performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0088] In order to have a clearer understanding of the technical features, purposes and effects of the present invention, the specific implementation manners of the present invention will now be described with reference to the accompanying drawings.

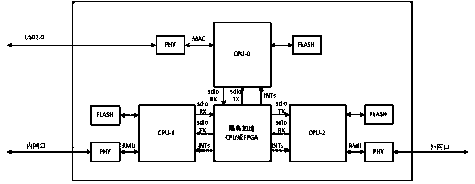

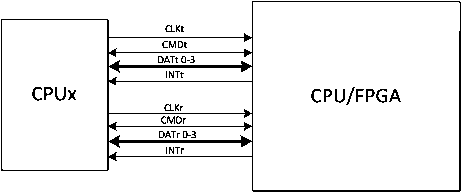

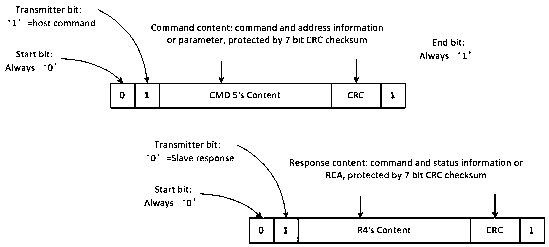

[0089] Such as figure 1 The embedded multi-CPU interconnection circuit based on the SDIO interface shown includes a CPU group composed of multiple CPUs and an isolation acceleration unit. Each CPU and the isolation acceleration unit are connected by two sets of independent SDIO channels for receiving and sending and dedicated The connection of receiving and sending is interrupted, and the CPU group is connected with the host machine, the internal network and the external network.

[0090] The isolation acceleration unit is an isolation acceleration CPU or FPGA; the CPU is an embedded CPU, and the CPU group includes CPU-0, CPU-1 and CPU-2, and the CPU-0 communicates with the host computer through a USB interface, Complete the pol...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap