Array substrate and manufacturing method thereof

A technology of array substrates and array substrate rows, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as wide frame, high production cost, and complicated production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

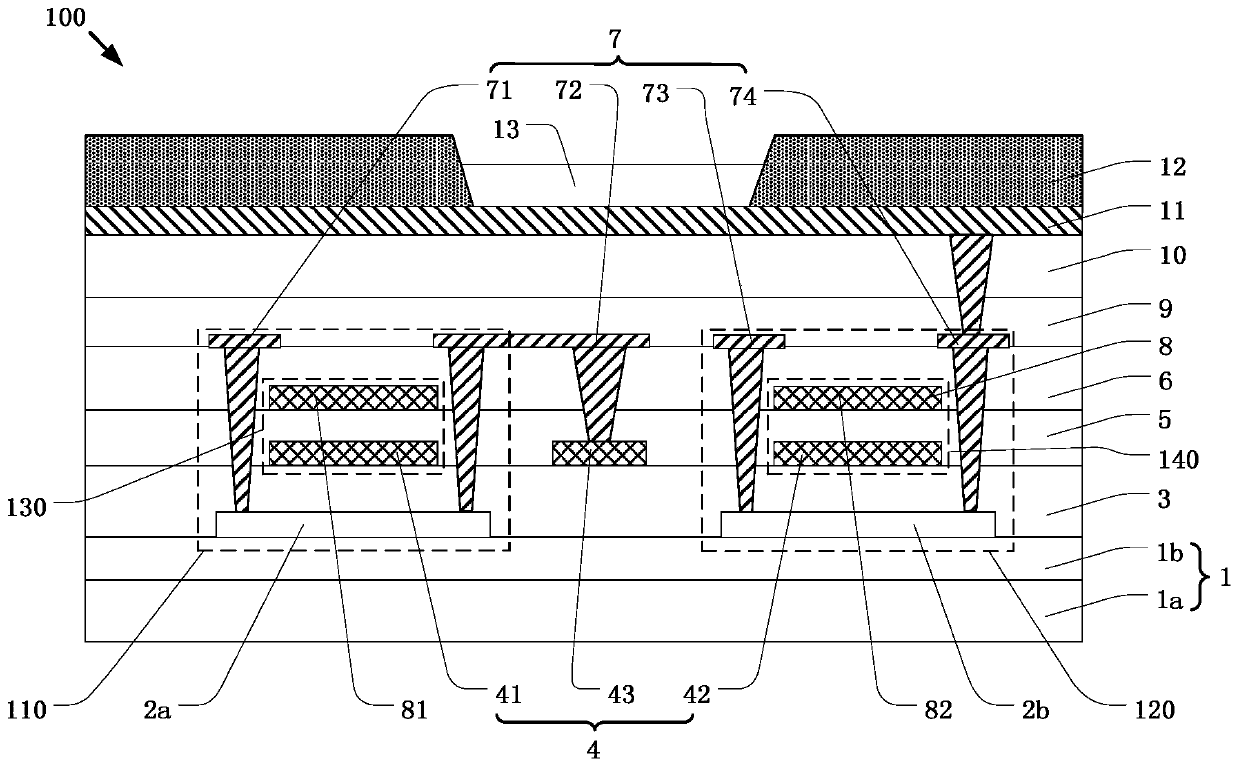

[0050] The following descriptions of the various embodiments refer to the accompanying drawings to illustrate specific embodiments in which the invention may be practiced. The directional terms mentioned in the present invention, such as [top], [bottom], [front], [back], [left], [right], [inside], [outside], [side], etc., are only for reference The orientation of the attached schema. Therefore, the directional terms used are used to illustrate and understand the present invention, but not to limit the present invention. In the figures, structurally similar elements are denoted by the same reference numerals.

[0051] The accompanying drawings of the present invention are only used to illustrate the relative positional relationship and electrical connection relationship. The layer thickness of some parts is drawn in an exaggerated way for easy understanding. The layer thickness in the drawings does not represent the proportional relationship of the actual layer thickness.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com