Bus address expansion method and device

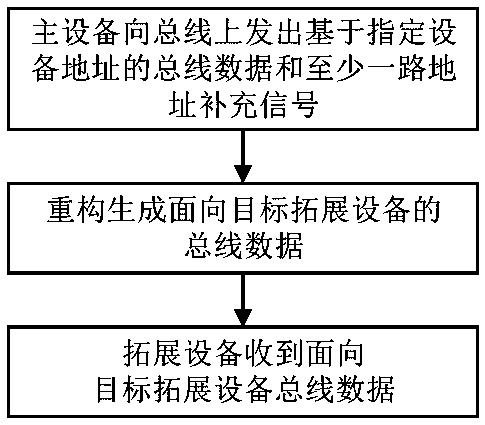

A bus address and address technology, applied in the computer field, can solve the problems of increasing equipment capacity, insufficient equipment address of equipment flags, incomplete bus address coverage, etc., to achieve the effect of expanding the scope and increasing the number of equipment mounted.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

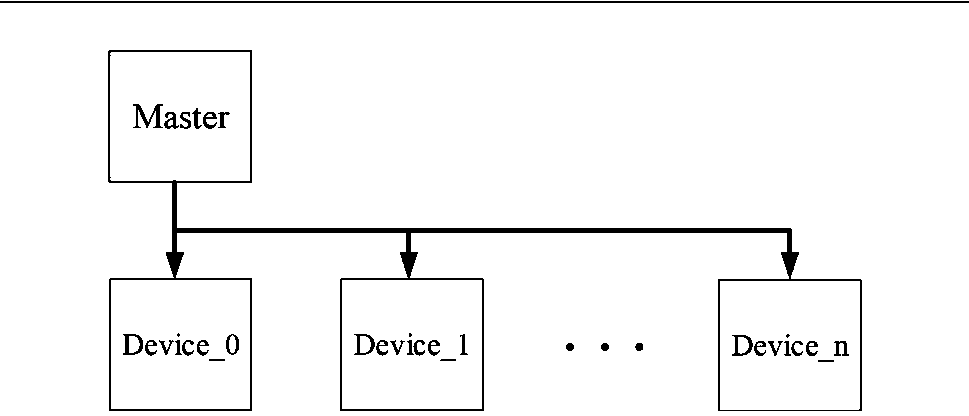

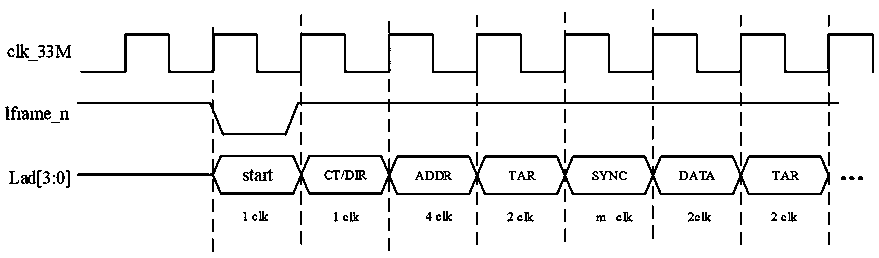

[0031] Hereinafter, taking the LPC bus as an example, the method and device for expanding the bus address of the present invention will be further described in detail. It should be noted that the bus address extension method and device of the present invention are not limited to the LPC bus, but also applicable to other types of buses. LPC (Low Pin Count) is a 33MHz 4 bit parallel bus protocol based on the Intel standard. This interface is used to replace the previous ISA bus protocol to connect South Bridge and Super I / O chips, FLASH BIOS, EC and other devices. The signal lines of the LPC bus have a total of 7 mandatory signals and 6 optional signals. The mandatory signals are LCLK, LRESET#, LFRAME#, LAD[3:0]. The optional signal distributions are LDRQ#, SERIRQ, CLKRUN#, LPME#, LPCPD#, LSMI#. Since the optional signals do not affect the function of interface communication, only the mandatory signals will be described in detail later. Among the mandatory signals, LCLK is th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More