Impedance optimization method for circuit board via hole and circuit board

An optimization method and circuit board technology, applied in printed circuit, printed circuit manufacturing, computer design circuit, etc., can solve problems such as high process cost, inability to completely remove via stubs, and affect transmission signal integrity, etc., to achieve optimal impedance , Optimize the effect of impedance continuity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

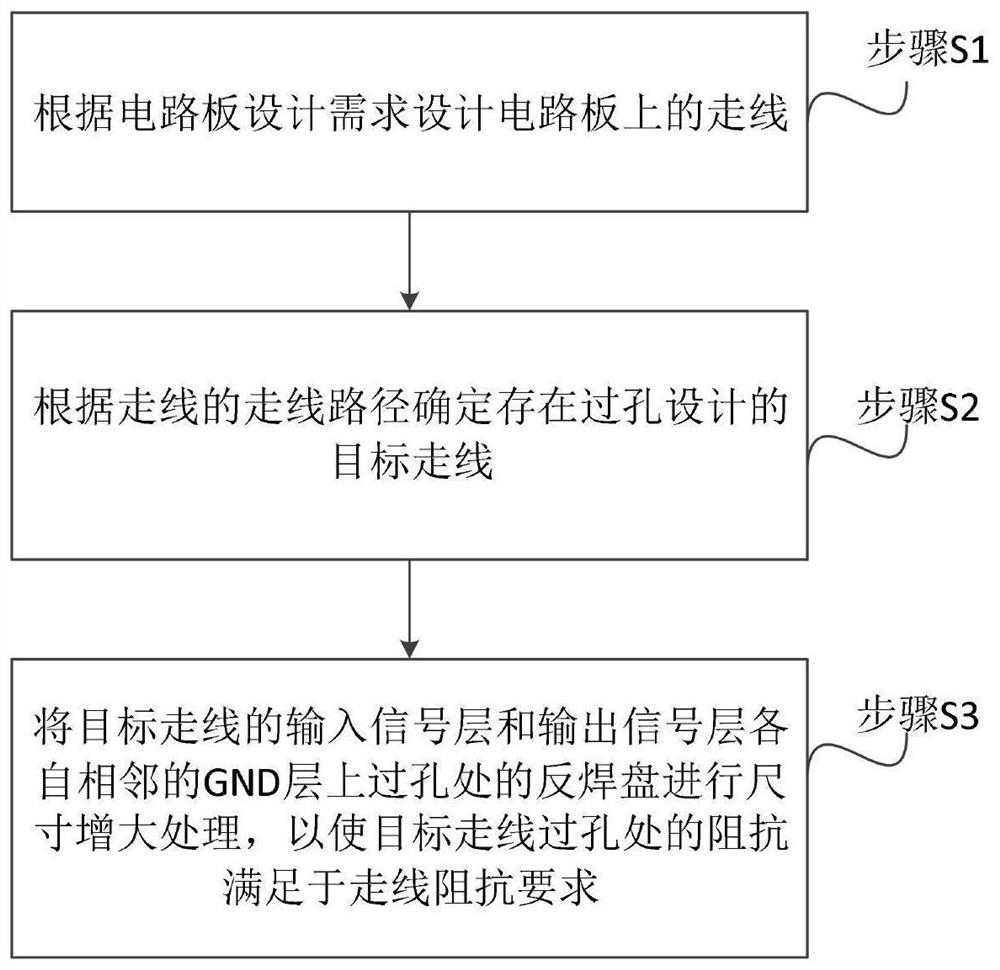

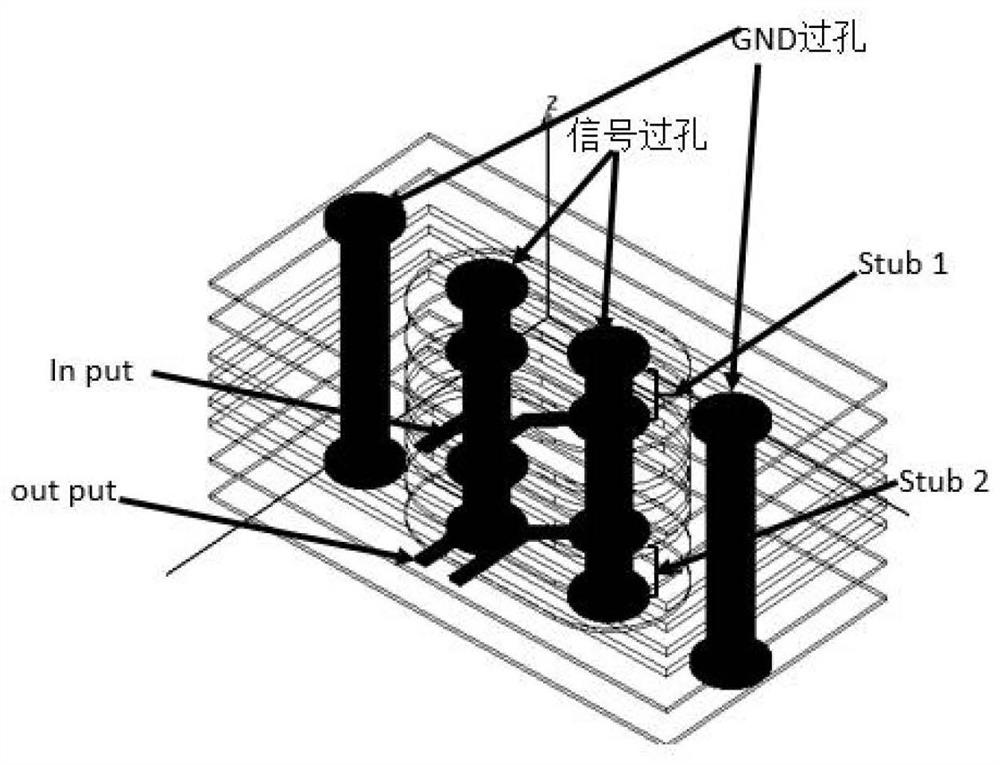

[0037] The core of the present invention is to provide a circuit board via impedance optimization method and a circuit board, by changing the shape of the anti-pad at the via hole to optimize the impedance continuity at the via hole, so as not to increase the process cost To meet the integrity requirements of the transmission signal; moreover, what this application changes is the shape of the anti-pad at the via hole on the adjacent GND layer of the input signal layer and the output signal layer of the wiring, while optimizing the impedance at the via hole Does not affect the impedance of the trace.

[0038] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More