A dbbc synchronous acquisition time delay control method

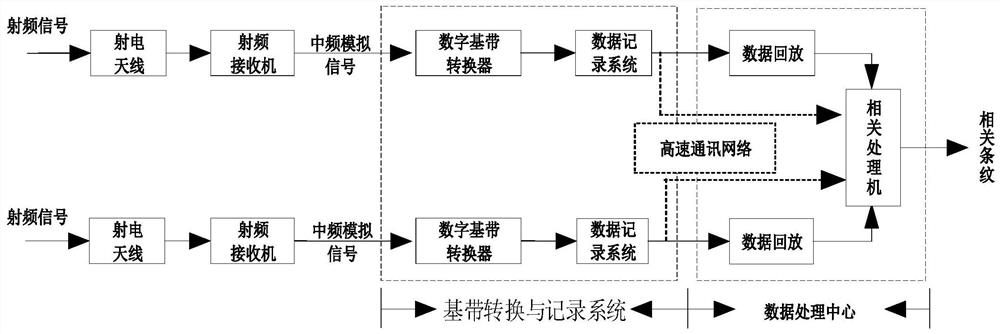

A control method and synchronous acquisition technology, applied in the direction of analog/digital conversion, code conversion, electrical components, etc., can solve problems such as unfavorable delay changes, occupied observation time, inconsistent synchronous acquisition delay, etc., to achieve high stability control, Improve observation efficiency and solve the effect of delay zero value uncertainty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] The present invention will be described in detail below with reference to the accompanying drawings and examples.

[0060] This embodiment provides a DBBC synchronous acquisition delay control method. First, the principle and implementation steps of the method of the present invention are described in detail. Finally, an experimental system is built to test the stability of the synchronous acquisition delay of the proposed method through measured data. .

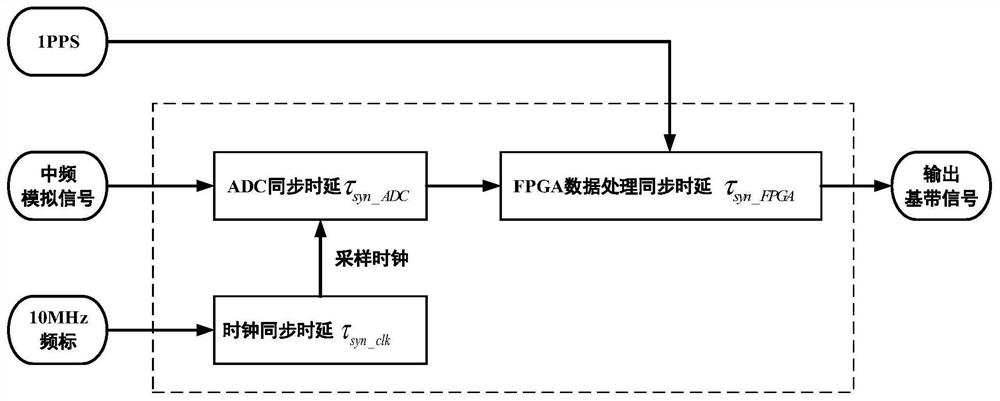

[0061] The synchronous acquisition delay control method proposed in this embodiment adopts a synchronous acquisition delay control system with high stability, and the realization structure diagram of the system is as follows Figure 5 shown. In the VLBI observation station, the 1PPS second pulse signal and the 10MHz frequency standard signal are generated by the hydrogen atomic clock in the station and the GPS common-view receiver (time system equipment), and the delay difference between the two is consistent and mea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More